Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 64/80-Pin High-Performance, 256 Kbit to 1 Mbit Enhanced Flash Microcontrollers with A/D

#### **High-Performance RISC CPU:**

- C compiler optimized architecture/instruction set:

- Source code compatible with the PIC16 and PIC17 instruction sets

- Linear program memory addressing to 128 Kbytes

- · Linear data memory addressing to 3840 bytes

- 1 Kbyte of data EEPROM

- · Up to 10 MIPs operation:

- DC 40 MHz osc./clock input

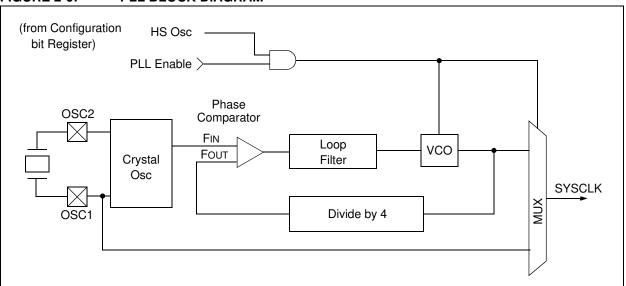

- 4 MHz 10 MHz osc./clock input with PLL active

- · 16-bit wide instructions, 8-bit wide data path

- · Priority levels for interrupts

- 31-level, software accessible hardware stack

- 8 x 8 Single Cycle Hardware Multiplier

# External Memory Interface (PIC18F8X20 Devices Only):

- · Address capability of up to 2 Mbytes

- · 16-bit interface

#### **Peripheral Features:**

- High current sink/source 25 mA/25 mA

- · Four external interrupt pins

- Timer0 module: 8-bit/16-bit timer/counter

- Timer1 module: 16-bit timer/counter

- Timer2 module: 8-bit timer/counter

- Timer3 module: 16-bit timer/counter

- · Timer4 module: 8-bit timer/counter

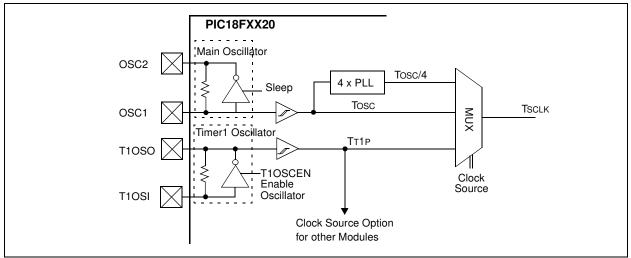

- Secondary oscillator clock option Timer1/Timer3

- Five Capture/Compare/PWM (CCP) modules:

- Capture is 16-bit, max. resolution 6.25 ns (Tcy/16)

- Compare is 16-bit, max. resolution 100 ns (Tcy)

- PWM output: PWM resolution is 1 to 10-bit

- Master Synchronous Serial Port (MSSP) module with two modes of operation:

- 3-wire SPI (supports all 4 SPI modes)

- I<sup>2</sup>C™ Master and Slave mode

- Two Addressable USART modules:

- Supports RS-485 and RS-232

- · Parallel Slave Port (PSP) module

#### Analog Features:

- 10-bit, up to 16-channel Analog-to-Digital Converter (A/D):

- Conversion available during Sleep

- Programmable 16-level Low-Voltage Detection (LVD) module:

- Supports interrupt on Low-Voltage Detection

- Programmable Brown-out Reset (PBOR)

- · Dual analog comparators:

- Programmable input/output configuration

#### **Special Microcontroller Features:**

- 100,000 erase/write cycle Enhanced Flash program memory typical

- 1,000,000 erase/write cycle Data EEPROM memory typical

- · 1 second programming time

- Flash/Data EEPROM Retention: > 40 years

- · Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own On-Chip RC Oscillator for reliable operation

- · Programmable code protection

- Power saving Sleep mode

- · Selectable oscillator options including:

- 4X Phase Lock Loop (of primary oscillator)

- Secondary Oscillator (32 kHz) clock input

- In-Circuit Serial Programming™ (ICSP™) via two pins

- MPLAB® In-Circuit Debug (ICD) via two pins

#### **CMOS Technology:**

- · Low-power, high-speed Flash technology

- · Fully static design

- Wide operating voltage range (2.0V to 5.5V)

- · Industrial and Extended temperature ranges

|            | Prog  | gram Memory                | Data            | Memory         |     | 10-bit CCP  |       | MSSP |                            |       | Timers       | Ext | Max           |

|------------|-------|----------------------------|-----------------|----------------|-----|-------------|-------|------|----------------------------|-------|--------------|-----|---------------|

| Device     | Bytes | # Single-Word Instructions | SRAM<br>(bytes) | EEPROM (bytes) | I/O | A/D<br>(ch) | (PWM) | SPI  | Master<br>I <sup>2</sup> C | USART | 8-bit/16-bit | Bus | Fosc<br>(MHz) |

| PIC18F6520 | 32K   | 16384                      | 2048            | 1024           | 52  | 12          | 5     | Υ    | Υ                          | 2     | 2/3          | N   | 40            |

| PIC18F6620 | 64K   | 32768                      | 3840            | 1024           | 52  | 12          | 5     | Υ    | Υ                          | 2     | 2/3          | N   | 25            |

| PIC18F6720 | 128K  | 65536                      | 3840            | 1024           | 52  | 12          | 5     | Υ    | Υ                          | 2     | 2/3          | N   | 25            |

| PIC18F8520 | 32K   | 16384                      | 2048            | 1024           | 68  | 16          | 5     | Υ    | Υ                          | 2     | 2/3          | Υ   | 40            |

| PIC18F8620 | 64K   | 32768                      | 3840            | 1024           | 68  | 16          | 5     | Υ    | Υ                          | 2     | 2/3          | Υ   | 25            |

| PIC18F8720 | 128K  | 65536                      | 3840            | 1024           | 68  | 16          | 5     | Υ    | Υ                          | 2     | 2/3          | Υ   | 25            |

### **Table of Contents**

| 1.0   | Device Overview                                                             | 7   |

|-------|-----------------------------------------------------------------------------|-----|

| 2.0   | Oscillator Configurations                                                   | 21  |

| 3.0   | Reset                                                                       | 29  |

| 4.0   | Memory Organization                                                         | 39  |

| 5.0   | Flash Program Memory                                                        | 61  |

| 6.0   | External Memory Interface                                                   | 71  |

| 7.0   | Data EEPROM Memory                                                          | 79  |

| 8.0   | 8 X 8 Hardware Multiplier                                                   | 85  |

| 9.0   | Interrupts                                                                  | 87  |

| 10.0  | I/O Ports                                                                   | 103 |

| 11.0  | Timer0 Module                                                               | 131 |

| 12.0  | Timer1 Module                                                               | 135 |

| 13.0  | Timer2 Module                                                               | 141 |

| 14.0  | Timer3 Module                                                               | 143 |

| 15.0  | Timer4 Module                                                               | 147 |

| 16.0  | Capture/Compare/PWM (CCP) Modules                                           | 149 |

|       | Master Synchronous Serial Port (MSSP) Module                                |     |

|       | Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 19.0  | 10-Bit Analog-to-Digital Converter (A/D) Module                             | 213 |

| 20.0  | Comparator Module                                                           | 223 |

| 21.0  |                                                                             |     |

| 22.0  | Low-Voltage Detect                                                          | 233 |

| 23.0  | Special Features of the CPU                                                 | 239 |

| 24.0  | Instruction Set Summary                                                     | 259 |

| 25.0  | Development Support                                                         | 301 |

| 26.0  | Electrical Characteristics                                                  | 305 |

|       | DC and AC Characteristics Graphs and Tables                                 |     |

| 28.0  | Packaging Information                                                       | 355 |

| Appe  | endix A: Revision History                                                   | 361 |

| Appe  | endix B: Device Differences                                                 | 361 |

| Appe  | endix C: Conversion Considerations                                          | 362 |

| Appe  | endix D: Migration from Mid-range to Enhanced Devices                       | 362 |

|       | endix E: Migration from High-end to Enhanced Devices                        |     |

| The I | Microchip Web Site                                                          | 375 |

| Cust  | omer Change Notification Service                                            | 375 |

| Cust  | omer Support                                                                | 375 |

| Read  | der Response                                                                | 376 |

| PIC1  | 18F6520/8520/6620/8620/6720/8720 Product Identification System              | 377 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

**NOTES:**

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

PIC18F6520

PIC18F6620

PIC18F6620

PIC18F8720

PIC18F8720

This family offers the same advantages of all PIC18 microcontrollers — namely, high computational performance at an economical price — with the addition of high endurance Enhanced Flash program memory. The PIC18FXX20 family also provides an enhanced range of program memory options and versatile analog features that make it ideal for complex, high-performance applications.

### 1.1 Key Features

### 1.1.1 EXPANDED MEMORY

The PIC18FXX20 family introduces the widest range of on-chip, Enhanced Flash program memory available on PIC® microcontrollers – up to 128 Kbyte (or 65,536 words), the largest ever offered by Microchip. For users with more modest code requirements, the family also includes members with 32 Kbyte or 64 Kbyte.

Other memory features are:

- Data RAM and Data EEPROM: The PIC18FXX20 family also provides plenty of room for application data. Depending on the device, either 2048 or 3840 bytes of data RAM are available. All devices have 1024 bytes of data EEPROM for long-term retention of nonvolatile data

- Memory Endurance: The Enhanced Flash cells for both program memory and data EEPROM are rated to last for many thousands of erase/write cycles – up to 100,000 for program memory and 1,000,000 for EEPROM. Data retention without refresh is conservatively estimated to be greater than 40 years.

#### 1.1.2 EXTERNAL MEMORY INTERFACE

In the event that 128 Kbytes of program memory is inadequate for an application, the PIC18F8X20 members of the family also implement an External Memory Interface. This allows the controller's internal program counter to address a memory space of up to 2 Mbytes, permitting a level of data access that few 8-bit devices can claim.

With the addition of new operating modes, the External Memory Interface offers many new options, including:

- Operating the microcontroller entirely from external memory

- Using combinations of on-chip and external memory, up to the 2-Mbyte limit

- Using external Flash memory for reprogrammable application code, or large data tables

- Using external RAM devices for storing large amounts of variable data

#### 1.1.3 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

#### 1.1.4 OTHER SPECIAL FEATURES

- Communications: The PIC18FXX20 family incorporates a range of serial communications peripherals, including 2 independent USARTs and a Master SSP module, capable of both SPI and I<sup>2</sup>C (Master and Slave) modes of operation. For PIC18F8X20 devices, one of the general purpose I/O ports can be reconfigured as an 8-bit Parallel Slave Port for direct processor-to-processor communications.

- CCP Modules: All devices in the family incorporate five Capture/Compare/PWM modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once.

- Analog Features: All devices in the family feature 10-bit A/D converters, with up to 16 input channels, as well as the ability to perform conversions during Sleep mode. Also included are dual analog comparators with programmable input and output configuration, a programmable Low-Voltage Detect module and a programmable Brown-out Reset module.

- Self-programmability: These devices can write

to their own program memory spaces under internal software control. By using a bootloader routine

located in the protected Boot Block at the top of

program memory, it becomes possible to create

an application that can update itself in the field.

# 1.2 Details on Individual Family Members

The PIC18FXX20 devices are available in 64-pin and 80-pin packages. They are differentiated from each other in five ways:

- Flash program memory (32 Kbytes for PIC18FX520 devices, 64 Kbytes for PIC18FX620 devices and 128 Kbytes for PIC18FX720 devices)

- 2. Data RAM (2048 bytes for PIC18FX520 devices, 3840 bytes for PIC18FX620 and PIC18FX720 devices)

- 3. A/D channels (12 for PIC18F6X20 devices, 16 for PIC18F8X20)

- 4. I/O pins (52 on PIC18F6X20 devices, 68 on PIC18F8X20)

- External program memory interface (present only on PIC18F8X20 devices)

All other features for devices in the PIC18FXX20 family are identical. These are summarized in Table 1-1.

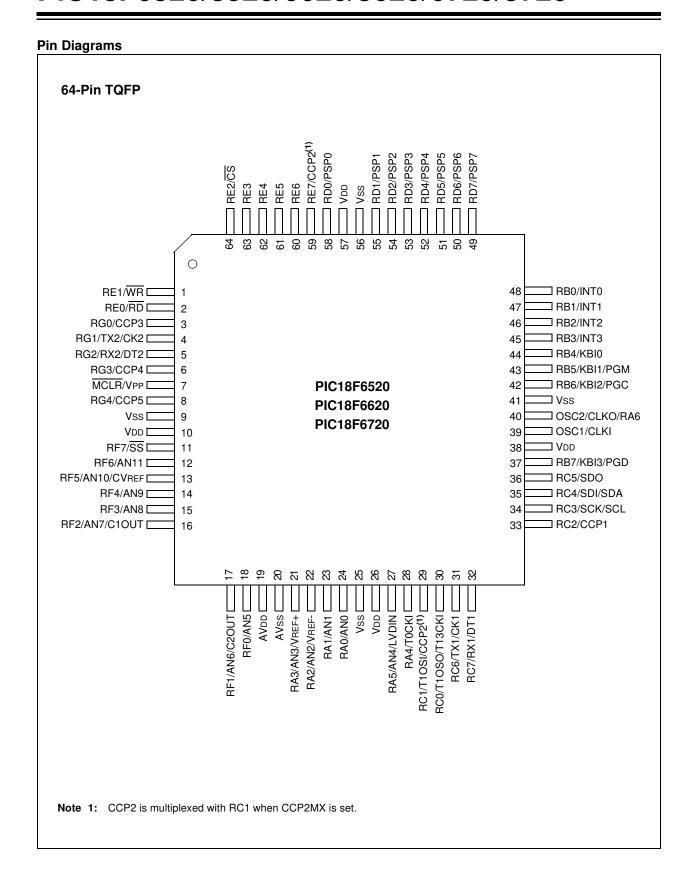

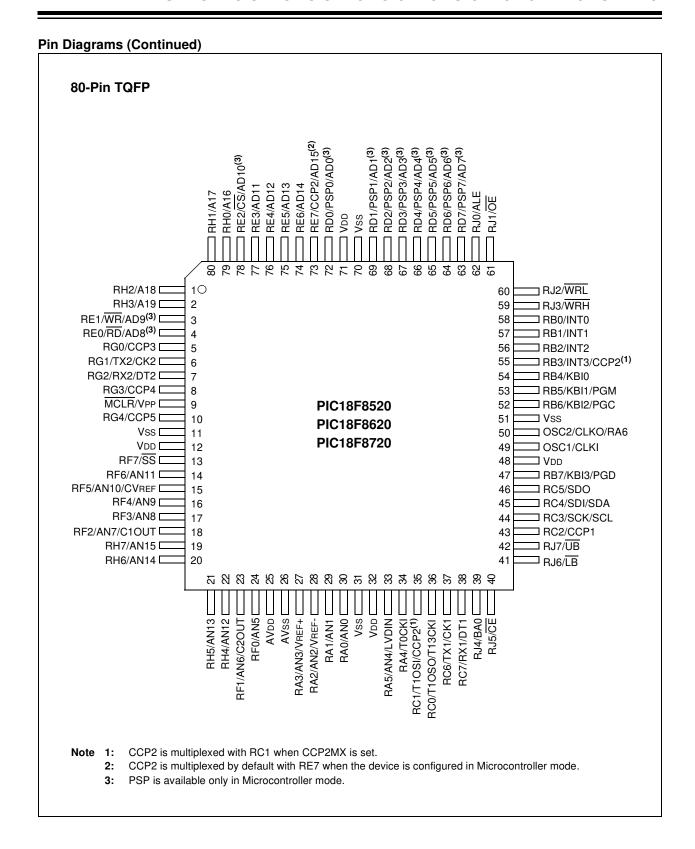

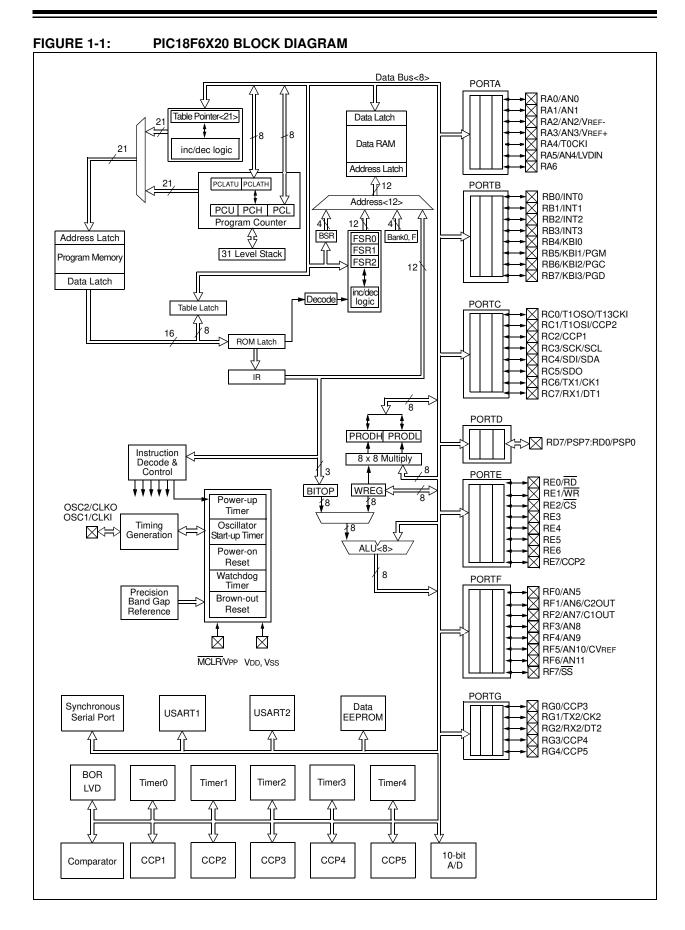

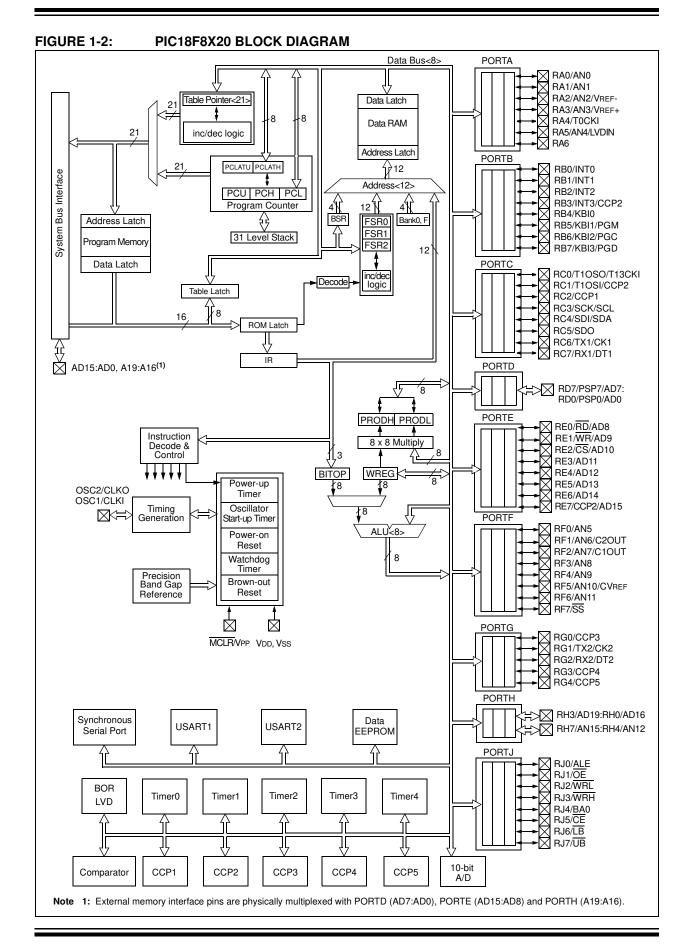

Block diagrams of the PIC18F6X20 and PIC18F8X20 devices are provided in Figure 1-1 and Figure 1-2, respectively. The pinouts for these device families are listed in Table 1-2.

TABLE 1-1: PIC18FXX20 DEVICE FEATURES

| Features                           | PIC18F6520                                                                          | PIC18F6620                                                                          | PIC18F6720                                                                          | PIC18F8520                                                                          | PIC18F8620                                                                          | PIC18F8720                                                                          |

|------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Operating Frequency                | DC – 40 MHz                                                                         | DC – 25 MHz                                                                         | DC – 25 MHz                                                                         | DC – 40 MHz                                                                         | DC – 25 MHz                                                                         | DC – 25 MHz                                                                         |

| Program Memory<br>(Bytes)          | 32K                                                                                 | 64K                                                                                 | 128K                                                                                | 32K                                                                                 | 64K                                                                                 | 128K                                                                                |

| Program Memory (Instructions)      | 16384                                                                               | 32768                                                                               | 65536                                                                               | 16384                                                                               | 32768                                                                               | 65536                                                                               |

| Data Memory<br>(Bytes)             | 2048                                                                                | 3840                                                                                | 3840                                                                                | 2048                                                                                | 3840                                                                                | 3840                                                                                |

| Data EEPROM<br>Memory (Bytes)      | 1024                                                                                | 1024                                                                                | 1024                                                                                | 1024                                                                                | 1024                                                                                | 1024                                                                                |

| External Memory<br>Interface       | No                                                                                  | No                                                                                  | No                                                                                  | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 |

| Interrupt Sources                  | 17                                                                                  | 17                                                                                  | 17                                                                                  | 18                                                                                  | 18                                                                                  | 18                                                                                  |

| I/O Ports                          | Ports A, B, C,<br>D, E, F, G                                                        | Ports A, B, C, D,<br>E, F, G                                                        | Ports A, B, C, D,<br>E, F, G                                                        | Ports A, B, C,<br>D, E, F, G, H, J                                                  | Ports A, B, C,<br>D, E, F, G, H, J                                                  | Ports A, B, C,<br>D, E, F, G, H, J                                                  |

| Timers                             | 5                                                                                   | 5                                                                                   | 5                                                                                   | 5                                                                                   | 5                                                                                   | 5                                                                                   |

| Capture/Compare/<br>PWM Modules    | 5                                                                                   | 5                                                                                   | 5                                                                                   | 5                                                                                   | 5                                                                                   | 5                                                                                   |

| Serial Communications              | MSSP,<br>Addressable<br>USART (2)                                                   |

| Parallel Communications            | PSP                                                                                 | PSP                                                                                 | PSP                                                                                 | PSP                                                                                 | PSP                                                                                 | PSP                                                                                 |

| 10-bit Analog-to-Digital<br>Module | 12 input<br>channels                                                                | 12 input<br>channels                                                                | 12 input<br>channels                                                                | 16 input channels                                                                   | 16 input<br>channels                                                                | 16 input<br>channels                                                                |

| Resets (and Delays)                | POR, BOR,<br>RESET<br>Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST) |

| Programmable<br>Low-Voltage Detect | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 |

| Programmable<br>Brown-out Reset    | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 | Yes                                                                                 |

| Instruction Set                    | 77 Instructions                                                                     |

| Package                            | 64-pin TQFP                                                                         | 64-pin TQFP                                                                         | 64-pin TQFP                                                                         | 80-pin TQFP                                                                         | 80-pin TQFP                                                                         | 80-pin TQFP                                                                         |

**TABLE 1-2:** PIC18FXX20 PINOUT I/O DESCRIPTIONS

| Pin Name              | Pin Number |            | Pin  | Buffer  | Description                                                                                                                              |  |

|-----------------------|------------|------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pili Name             | PIC18F6X20 | PIC18F8X20 | Туре | Туре    | Description                                                                                                                              |  |

| MCLR/VPP              | 7          | 9          |      |         | Master Clear (input) or programming voltage (output).                                                                                    |  |

| MCLR                  |            |            | I    | ST      | Master Clear (Reset) input. This pin is an active-low Reset to the device.                                                               |  |

| VPP                   |            |            | Р    |         | Programming voltage input.                                                                                                               |  |

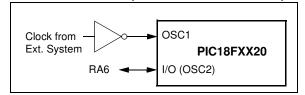

| OSC1/CLKI<br>OSC1     | 39         | 49         | I    | CMOS/ST | Oscillator crystal or external clock input. Oscillator crystal input or external clock source input. ST buffer when configured           |  |

| CLKI                  |            |            | I    | CMOS    | in RC mode; otherwise CMOS. External clock source input. Always associated with pin function OSC1 (see OSC1/CLKI, OSC2/CLKO pins).       |  |

| OSC2/CLKO/RA6<br>OSC2 | 40         | 50         | 0    | _       | Oscillator crystal or clock output. Oscillator crystal output. Connects to crystal or resonator in                                       |  |

| CLKO                  |            |            | 0    | _       | Crystal Oscillator mode.  In RC mode, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate. |  |

| RA6                   |            |            | I/O  | TTL     | General purpose I/O pin.                                                                                                                 |  |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input = Input 0 = Output

= Power OD = Open-Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- 4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- 6: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name             | Pin Number |            | Pin      | Buffer        | Description                                         |

|----------------------|------------|------------|----------|---------------|-----------------------------------------------------|

| Pili Name            | PIC18F6X20 | PIC18F8X20 | Туре     | Type          | Description                                         |

|                      |            |            |          |               | PORTA is a bidirectional I/O port.                  |

| RA0/AN0              | 24         | 30         |          |               |                                                     |

| RA0                  |            |            | I/O      | TTL           | Digital I/O.                                        |

| AN0                  |            |            | I        | Analog        | Analog input 0.                                     |

| RA1/AN1              | 23         | 29         |          |               |                                                     |

| RA1                  |            |            | I/O      | TTL           | Digital I/O.                                        |

| AN1                  |            |            | ı        | Analog        | Analog input 1.                                     |

| RA2/AN2/VREF-        | 22         | 28         | 1/0      | TT1           | Digital I/O                                         |

| RA2<br>AN2           |            |            | I/O      | TTL<br>Analog | Digital I/O. Analog input 2.                        |

| VREF-                |            |            | i        | Analog        | Analog input 2.  A/D reference voltage (Low) input. |

| RA3/AN3/VREF+        | 21         | 27         |          | ,a.og         | 1 1 2 Total and a rating (2011) Impati              |

| RA3                  |            |            | I/O      | TTL           | Digital I/O.                                        |

| AN3                  |            |            | 1        | Analog        | Analog input 3.                                     |

| VREF+                |            |            | - 1      | Analog        | A/D reference voltage (High) input.                 |

| RA4/T0CKI            | 28         | 34         |          |               |                                                     |

| RA4                  |            |            | I/O      | ST/OD         | Digital I/O – Open-drain when                       |

| T00//I               |            |            |          | ОТ            | configured as output.                               |

| TOCKI                |            |            | I        | ST            | Timer0 external clock input.                        |

| RA5/AN4/LVDIN<br>RA5 | 27         | 33         | 1/0      | TTL           | Digital I/O                                         |

| AN4                  |            |            | I/O<br>I | Analog        | Digital I/O. Analog input 4.                        |

| LVDIN                |            |            |          | Analog        | Low-Voltage Detect input.                           |

| RA6                  |            |            |          |               | See the OSC2/CLKO/RA6 pin.                          |

**Legend:** TTL = TTL compatible input

= Power

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

= Input

OD = Open-Drain (no P diode to VDD)

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- **4:** CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                            | Pin N      | umber      | Pin               | Buffer          | Pagazintian                                                                                                   |

|-----------------------------------------------------|------------|------------|-------------------|-----------------|---------------------------------------------------------------------------------------------------------------|

| Pin Name                                            | PIC18F6X20 | PIC18F8X20 | Туре              | Туре            | Description                                                                                                   |

|                                                     |            |            |                   |                 | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0<br>RB0<br>INT0                             | 48         | 58         | I/O<br>I          | TTL<br>ST       | Digital I/O.<br>External interrupt 0.                                                                         |

| RB1/INT1<br>RB1<br>INT1                             | 47         | 57         | I/O<br>I          | TTL<br>ST       | Digital I/O.<br>External interrupt 1.                                                                         |

| RB2/INT2<br>RB2<br>INT2                             | 46         | 56         | I/O<br>I          | TTL<br>ST       | Digital I/O.<br>External interrupt 2.                                                                         |

| RB3/INT3/CCP2<br>RB3<br>INT3<br>CCP2 <sup>(1)</sup> | 45         | 55         | I/O<br>I/O<br>I/O | TTL<br>ST<br>ST | Digital I/O. External interrupt 3. Capture2 input, Compare2 output, PWM2 output.                              |

| RB4/KBI0<br>RB4<br>KBI0                             | 44         | 54         | I/O<br>I          | TTL<br>ST       | Digital I/O.<br>Interrupt-on-change pin.                                                                      |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                  | 43         | 53         | I/O<br> <br> /O   | TTL<br>ST<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP Programming enable<br>pin.                       |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                  | 42         | 52         | I/O<br> <br> /O   | TTL<br>ST<br>ST | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and<br>ICSP programming clock.                |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                  | 37         | 47         | I/O<br>I/O        | TTL<br>ST       | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and<br>ICSP programming data.                 |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

I = Input

O = Output

P = Power

OD = Open-Drain (no P diode to VDD)

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- **4:** CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Nama                                              | Pin N      | umber      | Pin             | Buffer           | Description                                                                                                                       |

|-------------------------------------------------------|------------|------------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                              | PIC18F6X20 | PIC18F8X20 | Type            | Type             | Description                                                                                                                       |

|                                                       |            |            |                 |                  | PORTC is a bidirectional I/O port.                                                                                                |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI            | 30         | 36         | I/O<br>O<br>I   | ST<br>—<br>ST    | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                  |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup> | 29         | 35         | I/O<br>I<br>I/O | ST<br>CMOS<br>ST | Digital I/O. Timer1 oscillator input. Capture2 input/Compare2 output/ PWM2 output.                                                |

| RC2/CCP1<br>RC2<br>CCP1                               | 33         | 43         | I/O<br>I/O      | ST<br>ST         | Digital I/O.<br>Capture1 input/Compare1 output/<br>PWM1 output.                                                                   |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                      | 34         | 44         | I/O<br>I/O      | ST<br>ST         | Digital I/O. Synchronous serial clock input/output for SPI mode. Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                      | 35         | 45         | I/O<br>I<br>I/O | ST<br>ST<br>ST   | Digital I/O. SPI data in. I <sup>2</sup> C data I/O.                                                                              |

| RC5/SDO<br>RC5<br>SDO                                 | 36         | 46         | I/O<br>O        | ST<br>—          | Digital I/O.<br>SPI data out.                                                                                                     |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                      | 31         | 37         | I/O<br>O<br>I/O | ST<br>—<br>ST    | Digital I/O. USART 1 asynchronous transmit. USART 1 synchronous clock (see RX1/DT1).                                              |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                      | 32         | 38         | I/O<br>I<br>I/O | ST<br>ST<br>ST   | Digital I/O. USART 1 asynchronous receive. USART 1 synchronous data (see TX1/CK1).                                                |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

= Input

O = Output

P = Power

OD = Open-Drain (no P diode to VDD)

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- **4:** CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                          | Pin Number |            | Pin Buffer        |                  | Pagazintian                                                                                           |

|---------------------------------------------------|------------|------------|-------------------|------------------|-------------------------------------------------------------------------------------------------------|

| Pin Name                                          | PIC18F6X20 | PIC18F8X20 | Туре              | Туре             | Description                                                                                           |

|                                                   |            |            |                   |                  | PORTD is a bidirectional I/O port. These pins have TTL input buffers when external memory is enabled. |

| RD0/PSP0/AD0<br>RD0<br>PSP0<br>AD0 <sup>(3)</sup> | 58         | 72         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 0.                          |

| RD1/PSP1/AD1<br>RD1<br>PSP1<br>AD1 <sup>(3)</sup> | 55         | 69         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 1.                          |

| RD2/PSP2/AD2<br>RD2<br>PSP2<br>AD2 <sup>(3)</sup> | 54         | 68         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 2.                          |

| RD3/PSP3/AD3<br>RD3<br>PSP3<br>AD3 <sup>(3)</sup> | 53         | 67         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 3.                          |

| RD4/PSP4/AD4<br>RD4<br>PSP4<br>AD4 <sup>(3)</sup> | 52         | 66         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 4.                          |

| RD5/PSP5/AD5<br>RD5<br>PSP5<br>AD5 <sup>(3)</sup> | 51         | 65         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 5.                          |

| RD6/PSP6/AD6<br>RD6<br>PSP6<br>AD6 <sup>(3)</sup> | 50         | 64         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 6.                          |

| RD7/PSP7/AD7<br>RD7<br>PSP7<br>AD7 <sup>(3)</sup> | 49         | 63         | I/O<br>I/O<br>I/O | ST<br>TTL<br>TTL | Digital I/O.<br>Parallel Slave Port data.<br>External memory address/data 7.                          |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

= Input P = Power

OD = Open-Drain (no P diode to VDD)

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- **4:** CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Name                   | Pin N      | umber      | Pin        | Buffer    | Description                                                                                      |

|----------------------------|------------|------------|------------|-----------|--------------------------------------------------------------------------------------------------|

| Pin Name                   | PIC18F6X20 | PIC18F8X20 | Type       | Туре      | Description                                                                                      |

|                            |            |            |            |           | PORTE is a bidirectional I/O port.                                                               |

| RE0/RD/AD8                 | 2          | 4          |            |           |                                                                                                  |

| RE0                        |            |            | I/O        | ST        | Digital I/O.                                                                                     |

| RD                         |            |            | ı          | TTL       | Read control for Parallel Slave Port (see WR and CS pins).                                       |

| AD8 <sup>(3)</sup>         |            |            | I/O        | TTL       | External memory address/data 8.                                                                  |

| RE1/WR/AD9                 | 1          | 3          |            |           | ·                                                                                                |

| RE1                        |            |            | I/O        | ST        | Digital I/O.                                                                                     |

| WR                         |            |            | I          | TTL       | Write control for Parallel Slave Port                                                            |

| AD9 <sup>(3)</sup>         |            |            | I/O        | TTL       | (see $\overline{\text{CS}}$ and $\overline{\text{RD}}$ pins).<br>External memory address/data 9. |

| RE2/CS/AD10                | 64         | 78         | 1/0        | 111       | External memory address/data 9.                                                                  |

| RE2                        | 04         | 70         | I/O        | ST        | Digital I/O.                                                                                     |

| CS                         |            |            | ľ          | TTL       | Chip select control for Parallel Slave                                                           |

| (2)                        |            |            |            |           | Port (see RD and WR).                                                                            |

| AD10 <sup>(3)</sup>        |            |            | I/O        | TTL       | External memory address/data 10.                                                                 |

| RE3/AD11                   | 63         | 77         |            |           | 51.11.11.0                                                                                       |

| RE3<br>AD11 <sup>(3)</sup> |            |            | I/O<br>I/O | ST<br>TTL | Digital I/O.                                                                                     |

|                            | 60         | 76         | 1/0        | IIL       | External memory address/data 11.                                                                 |

| RE4/AD12<br>RE4            | 62         | 76         | I/O        | ST        | Digital I/O.                                                                                     |

| AD12                       |            |            | I/O        | TTL       | External memory address/data 12.                                                                 |

| RE5/AD13                   | 61         | 75         |            |           | ,                                                                                                |

| RE5                        |            |            | I/O        | ST        | Digital I/O.                                                                                     |

| AD13 <sup>(3)</sup>        |            |            | I/O        | TTL       | External memory address/data 13.                                                                 |

| RE6/AD14                   | 60         | 74         |            |           | D. 1. 11/2                                                                                       |

| RE6<br>AD14 <sup>(3)</sup> |            |            | 1/0        | ST        | Digital I/O.                                                                                     |

|                            | F0         | 70         | I/O        | TTL       | External memory address/data 14.                                                                 |

| RE7/CCP2/AD15<br>RE7       | 59         | 73         | I/O        | ST        | Digital I/O.                                                                                     |

| CCP2 <sup>(1,4)</sup>      |            |            | I/O        | ST        | Capture2 input/Compare2 output/                                                                  |

|                            |            |            |            |           | PWM2 output.                                                                                     |

| AD15 <sup>(3)</sup>        |            |            | I/O        | TTL       | External memory address/data 15.                                                                 |

**Legend:** TTL = TTL compatible input

= Power

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

= Input

OD = Open-Drain (no P diode to VDD)

- 2: Default assignment when CCP2MX is set.

- **3:** External memory interface functions are only available on PIC18F8X20 devices.

- **4:** CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

**TABLE 1-2:** PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name       | Pin Number |            | Pin  | Buffer       | Description                        |  |

|----------------|------------|------------|------|--------------|------------------------------------|--|

| Pili Naille    | PIC18F6X20 | PIC18F8X20 | Туре | Type         | Description                        |  |

|                |            |            |      |              | PORTF is a bidirectional I/O port. |  |

| RF0/AN5        | 18         | 24         |      |              |                                    |  |

| RF0            |            |            | I/O  | ST           | Digital I/O.                       |  |

| AN5            |            |            | I    | Analog       | Analog input 5.                    |  |

| RF1/AN6/C2OUT  | 17         | 23         |      |              |                                    |  |

| RF1            |            |            | I/O  | ST           | Digital I/O.                       |  |

| AN6            |            |            | I    | Analog       | Analog input 6.                    |  |

| C2OUT          |            |            | 0    | ST           | Comparator 2 output.               |  |

| RF2/AN7/C1OUT  | 16         | 18         |      |              |                                    |  |

| RF2            |            |            | I/O  | ST           | Digital I/O.                       |  |

| AN7<br>C1OUT   |            |            | 0    | Analog<br>ST | Analog input 7.                    |  |

|                | 4-         | 4-         |      | 31           | Comparator 1 output.               |  |

| RF3/AN8<br>RF1 | 15         | 17         | 1/0  | ST           | District I/O                       |  |

| AN8            |            |            | I/O  | Analog       | Digital I/O.<br>Analog input 8.    |  |

|                | 1.4        | 10         | '    | Analog       | Analog input o.                    |  |

| RF4/AN9<br>RF1 | 14         | 16         | I/O  | ST           | Digital I/O.                       |  |

| AN9            |            |            | 1/0  | Analog       | Analog input 9.                    |  |

| RF5/AN10/CVREF | 13         | 15         | •    | 7 1110109    | / maiog input o.                   |  |

| RF1            | 13         | 15         | I/O  | ST           | Digital I/O.                       |  |

| AN10           |            |            | ., 0 | Analog       | Analog input 10.                   |  |

| CVREF          |            |            | 0    | Analog       | Comparator VREF output.            |  |

| RF6/AN11       | 12         | 14         |      | · ·          |                                    |  |

| RF6            |            |            | I/O  | ST           | Digital I/O.                       |  |

| AN11           |            |            | ı    | Analog       | Analog input 11.                   |  |

| RF7/SS         | 11         | 13         |      | _            |                                    |  |

| RF7            |            |            | I/O  | ST           | Digital I/O.                       |  |

| SS             |            |            | 1    | TTL          | SPI slave select input.            |  |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

= Input = Power 0 = Output

CMOS = CMOS compatible input or output

OD = Open-Drain (no P diode to VDD)

Note 1: Alternate assignment for CCP2 when CCP2MX is not selected (all operating modes except Microcontroller).

2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- 4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- 6: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

**TABLE 1-2:** PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                         | Pin Number |            | Pin Buffer      | Buffer         | Description                                                                          |

|----------------------------------|------------|------------|-----------------|----------------|--------------------------------------------------------------------------------------|

| Pin Name                         | PIC18F6X20 | PIC18F8X20 | Туре            | Type           | Description                                                                          |

|                                  |            |            |                 |                | PORTG is a bidirectional I/O port.                                                   |

| RG0/CCP3<br>RG0<br>CCP3          | 3          | 5          | I/O<br>I/O      | ST<br>ST       | Digital I/O. Capture3 input/Compare3 output/ PWM3 output.                            |

| RG1/TX2/CK2<br>RG1<br>TX2<br>CK2 | 4          | 6          | I/O<br>O<br>I/O | ST<br>—<br>ST  | Digital I/O. USART 2 asynchronous transmit. USART 2 synchronous clock (see RX2/DT2). |

| RG2/RX2/DT2<br>RG2<br>RX2<br>DT2 | 5          | 7          | I/O<br>I<br>I/O | ST<br>ST<br>ST | Digital I/O. USART 2 asynchronous receive. USART 2 synchronous data (see TX2/CK2).   |

| RG3/CCP4<br>RG3<br>CCP4          | 6          | 8          | I/O<br>I/O      | ST<br>ST       | Digital I/O. Capture4 input/Compare4 output/ PWM4 output.                            |

| RG4/CCP5<br>RG4<br>CCP5          | 8          | 10         | I/O<br>I/O      | ST<br>ST       | Digital I/O. Capture5 input/Compare5 output/ PWM5 output.                            |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

= Input 0 = Output

= Power OD = Open-Drain (no P diode to VDD)

CMOS = CMOS compatible input or output

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- 4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- 6: AVDD must be connected to a positive supply and AVss must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

TABLE 1-2: PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                | Pin N      | umber      | Pin      | Buffer       | Description                                        |

|-------------------------|------------|------------|----------|--------------|----------------------------------------------------|

| Pili Name               | PIC18F6X20 | PIC18F8X20 | Type     | Type         | Description                                        |

|                         |            |            |          |              | PORTH is a bidirectional I/O port <sup>(5)</sup> . |

| RH0/A16<br>RH0<br>A16   | _          | 79         | I/O<br>O | ST<br>TTL    | Digital I/O.<br>External memory address 16.        |

| RH1/A17<br>RH1<br>A17   | _          | 80         | I/O<br>O | ST<br>TTL    | Digital I/O.<br>External memory address 17.        |

| RH2/A18<br>RH2<br>A18   | _          | 1          | I/O<br>O | ST<br>TTL    | Digital I/O.<br>External memory address 18.        |

| RH3/A19<br>RH3<br>A19   | _          | 2          | I/O<br>O | ST<br>TTL    | Digital I/O.<br>External memory address 19.        |

| RH4/AN12<br>RH4<br>AN12 | _          | 22         | I/O<br>I | ST<br>Analog | Digital I/O.<br>Analog input 12.                   |

| RH5/AN13<br>RH5<br>AN13 | _          | 21         | I/O<br>I | ST<br>Analog | Digital I/O.<br>Analog input 13.                   |

| RH6/AN14<br>RH6<br>AN14 | _          | 20         | I/O<br>I | ST<br>Analog | Digital I/O.<br>Analog input 14.                   |

| RH7/AN15<br>RH7<br>AN15 | _          | 19         | I/O<br>I | ST<br>Analog | Digital I/O.<br>Analog input 15.                   |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

O = Output

I = Input P = Power

OD = Open-Drain (no P diode to VDD)

- 2: Default assignment when CCP2MX is set.

- 3: External memory interface functions are only available on PIC18F8X20 devices.

- **4:** CCP2 is multiplexed with this pin by default when configured in Microcontroller mode. Otherwise, it is multiplexed with either RB3 or RC1.

- 5: PORTH and PORTJ are only available on PIC18F8X20 (80-pin) devices.

- **6:** AVDD must be connected to a positive supply and AVSS must be connected to a ground reference for proper operation of the part in user or ICSP modes. See parameter D001A for details.

**TABLE 1-2:** PIC18FXX20 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name            | Pin Number |            | Pin      | Buffer    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|---------------------|------------|------------|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| riii Naille         | PIC18F6X20 | PIC18F8X20 | Туре     | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                     |            |            |          |           | PORTJ is a bidirectional I/O port <sup>(5)</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| RJ0/ALE             | _          | 62         |          |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| RJ0                 |            |            | I/O      | ST        | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| ALE                 |            |            | 0        | TTL       | External memory address latch enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

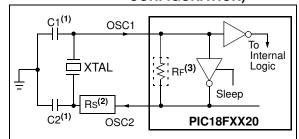

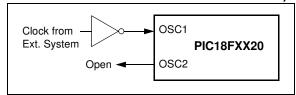

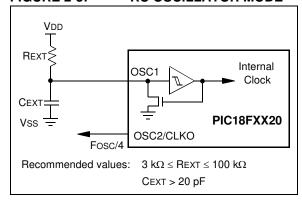

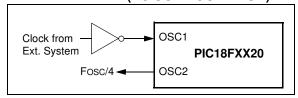

| RJ1/OE<br>RJ1       | _          | 61         | I/O      | ST        | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |