Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 32-Bit Flash Microcontroller with MIPS32<sup>®</sup> microAptiv™ UC Core with Low Power and Low Pin Count

## **Operating Conditions**

2.0V to 3.6V, -40°C to +85°C, DC to 25 MHz

## **Low-Power Modes**

- · Low-Power modes:

- Idle: CPU off, peripherals run from system clock

- Sleep: CPU and peripherals off:

- Fast wake-up Sleep with retention

- Low-power Sleep with retention

- 0.5 μA Sleep Current for Regulator Retention mode and 5 μA for Regulator Standby mode

- On-Chip 1.8V Voltage Regulator (VREG)

- · On-Chip Ultra Low-Power Retention Regulator

## **High-Performance 32-Bit RISC CPU**

- microAptiv™ UC 32-Bit Core with 5-Stage Pipeline

- microMIPS™ Instruction Set for 35% Smaller Code and 98% Performance compared to MIPS32 Instructions

- DC-25 MHz Operating Frequency

- 3.17 CoreMark®/MHz (79 CoreMark) Performance

- 1.53 DMIPS/MHz (37 DMIPS) (Dhrystone 2.1) Performance

- 16-Bit/32-Bit Wide Instructions with 32-Bit Wide Data Path

- Two Sets of 32 Core Register Files (32-bit) to Reduce Interrupt Latency

- Single-Cycle 32x16 Multiply and Two-Cycle 32x32 Multiply

- · Hardware Divide Unit

- 64-Bit, Zero Wait State Flash with ECC to Maximize Endurance/Retention

#### Microcontroller Features

- Low Pin Count Packages, Ranging from 20 to 36 Pins, including UQFN as Small as 4x4 mm

- Up to 64K Flash Memory:

- 20,000 erase/write cycle endurance

- 20 years minimum data retention

- Self-programmable under software control

- · Up to 8K Data Memory

- Pin-Compatible with Most PIC24 MCU/dsPIC<sup>®</sup> DSC Devices

- Multiple Interrupt Vectors with Individually Programmable Priority

- · Fail-Safe Clock Monitor mode

- Configurable Watchdog Timer with On-Chip, Low-Power RC Oscillator

- · Programmable Code Protection

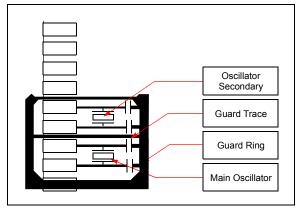

- · Selectable Oscillator Options including:

- High-precision, 8 MHz internal Fast RC (FRC) oscillator

- High-speed crystal/resonator oscillator or external clock

- 2x/3x/4x/6x/12x/24x PLL, which can be clocked from the FRC or primary oscillator

## **Peripheral Features**

- Atomic Set, Clear and Invert Operation on Select Peripheral Registers

- High-Current Sink/Source 11 mA/16 mA on All Ports

- Independent, Low-Power 32 kHz Timer Oscillator

- · Two 4-Wire SPI modules (up to 25 Mbps):

- 16-byte FIFO

- I<sup>2</sup>S mode

- Two UARTs:

- RS-232, RS-485 and LIN/J2602 support

- IrDA® with on-chip hardware encoder and decoder

- · External Edge and Level Change Interrupt on All Ports

- · CRC module

- · Hardware Real-Time Clock and Calendar (RTCC)

- · Up to 20 Peripheral Pin Select (PPS) Remappable Pins

- · Seven Total 16-Bit Timers:

- Timer1: Dedicated 16-bit timer/counter

- Two additional 16-bit timers in each MCCP and SCCP module

- Capture/Compare/PWM/Timer modules:

- Two 16-bit timers or one 32-bit timer in each module

- PWM resolution down to 21 ns

- One Multiple Output (MCCP) module:

- Flexible configuration as PWM, input capture, output compare or timers

- Six PWM outputs

- Programmable dead time

- Auto-shutdown

- Two Single Output (SCCP) modules:

- Flexible configuration as PWM, input capture, output compare or timers

- Single PWM output

- · Reference Clock Output (REFO)

- Two Configurable Logic Cells (CLC) with Internal Connections to Select Peripherals and PPS

## **Debug Features**

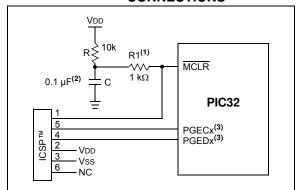

- · Two Programming and Debugging Interfaces:

- 2-wire ICSP™ interface with non-intrusive access and real-time data exchange with application

- 4-wire MIPS® standard Enhanced JTAG interface

- IEEE Standard 1149.2 Compatible (JTAG) Boundary Scan

## **Analog Features**

- Two Analog Comparators with Input Multiplexing

- Programmable High/Low-Voltage Detect (HLVD)

- 5-Bit DAC with Output Pin

- Up to 14-Channel, Software-Selectable 10/12-Bit SAR Analog-to-Digital Converter (ADC):

- 12-bit, 200K samples/second conversion rate (single Sample-and-Hold)

- 10-bit, 300K samples/second conversion rate (single Sample-and-Hold)

- Sleep mode operation

- Band gap reference input feature

- Windowed threshold compare feature

- Auto-scan feature

- Brown-out Reset (BOR)

TABLE 1: PIC32MM0064GPL036 FAMILY DEVICES

|                   |       | bytes)                  | (Kbytes)         | I/O/PPS             | Maximum            | mnm                 |                                |               |                     | ppat<br>hera        |     |                                      | (Channels)          |             |     |      |      |                                  |  |

|-------------------|-------|-------------------------|------------------|---------------------|--------------------|---------------------|--------------------------------|---------------|---------------------|---------------------|-----|--------------------------------------|---------------------|-------------|-----|------|------|----------------------------------|--|

| Device            | Pins  | Program Memory (Kbytes) | Data Memory (Kb) | General Purpose I/( | 16-Bit Timers Maxi | PWM Outputs Maximum | UART <sup>(1)</sup> /LIN/J2602 | 16-Bit Timers | MCCP <sup>(3)</sup> | SCCP <sup>(4)</sup> | CLC | SPI <sup>(2)</sup> /I <sup>2</sup> S | 10/12-Bit ADC (Chai | Comparators | CRC | RTCC | JTAG | Packages                         |  |

| PIC32MM0016GPL020 | 20    | 16                      | 4                | 16/16               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                  | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |  |

| PIC32MM0032GPL020 | 20    | 32                      | 8                | 16/16               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                  | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |  |

| PIC32MM0064GPL020 | 20    | 64                      | 8                | 16/16               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 11                  | 2           | Yes | Yes  | Yes  | SSOP/QFN                         |  |

| PIC32MM0016GPL028 | 28    | 16                      | 4                | 22/19               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                  | 2           | Yes | Yes  | Yes  | SSOP/SOIC/<br>QFN/UQFN           |  |

| PIC32MM0032GPL028 | 28    | 32                      | 8                | 22/19               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                  | 2           | Yes | Yes  | Yes  | SSOP/ SOIC/<br>QFN/UQFN          |  |

| PIC32MM0064GPL028 | 28    | 64                      | 8                | 22/19               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 12                  | 2           | Yes | Yes  | Yes  | SPDIP/SSOP/<br>SOIC/QFN/<br>UQFN |  |

| PIC32MM0016GPL036 | 36/40 | 16                      | 4                | 29/20               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                  | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |  |

| PIC32MM0032GPL036 | 36/40 | 32                      | 8                | 29/20               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                  | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |  |

| PIC32MM0064GPL036 | 36/40 | 64                      | 8                | 29/20               | 7                  | 8                   | 2                              | 1             | 1                   | 2                   | 2   | 2                                    | 14                  | 2           | Yes | Yes  | Yes  | VQFN/UQFN                        |  |

- Note 1: UART1 has assigned pins. UART2 is remappable.

- 2: SPI1 has assigned pins. SPI2 is remappable.

- **3:** MCCP can be configured as a PWM with up to 6 outputs, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

- 4: SCCP can be configured as a PWM with 1 output, input capture, output compare, 2 x 16-bit timers or 1 x 32-bit timer.

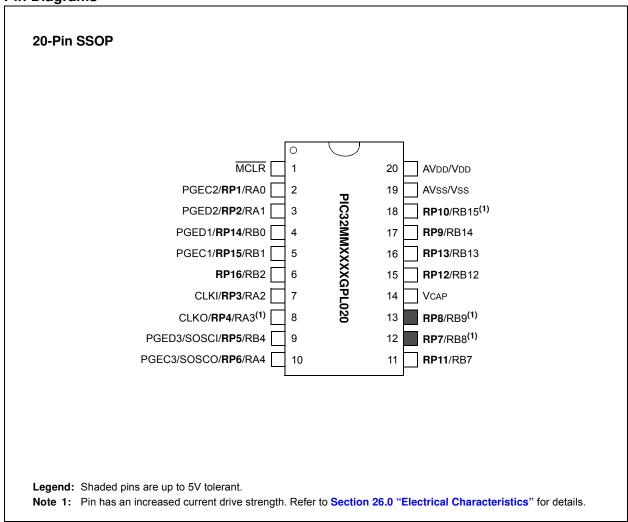

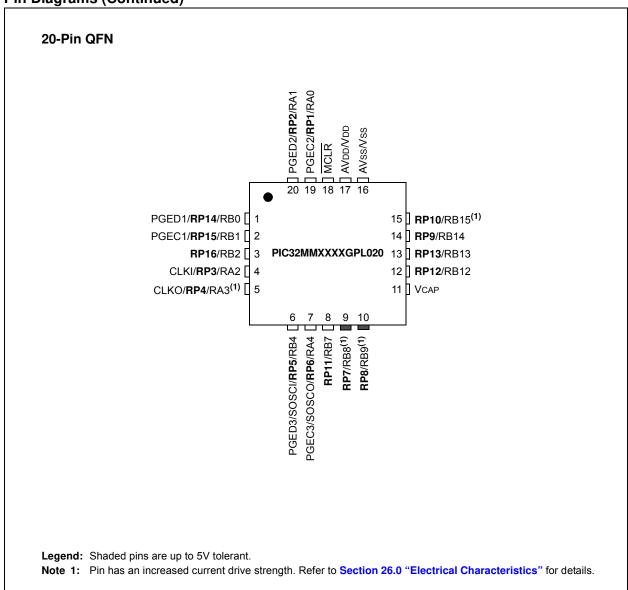

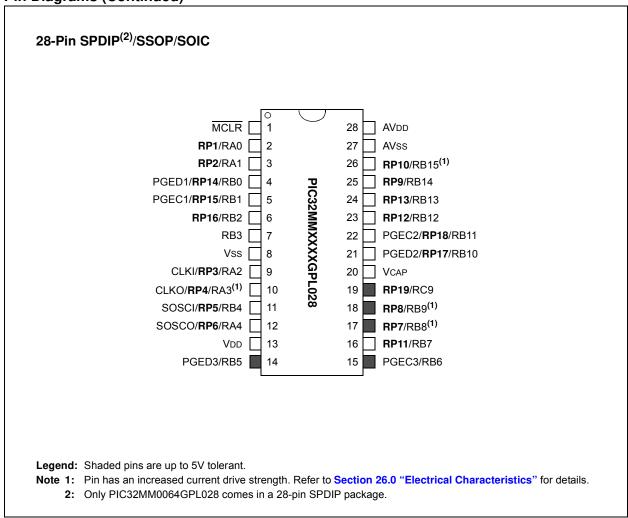

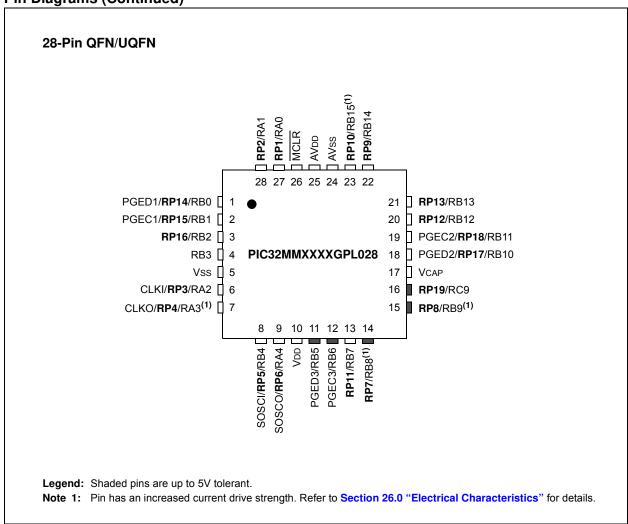

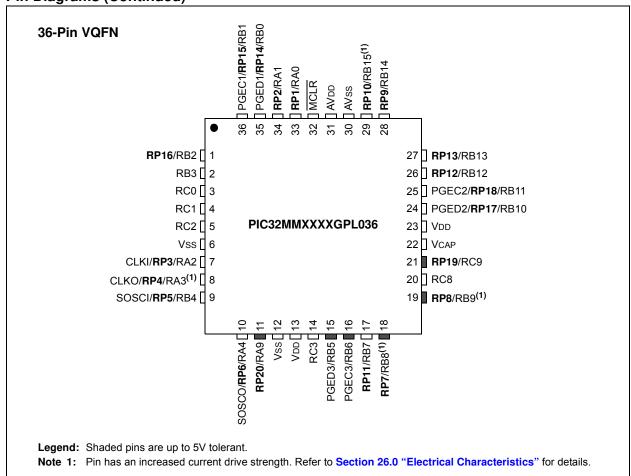

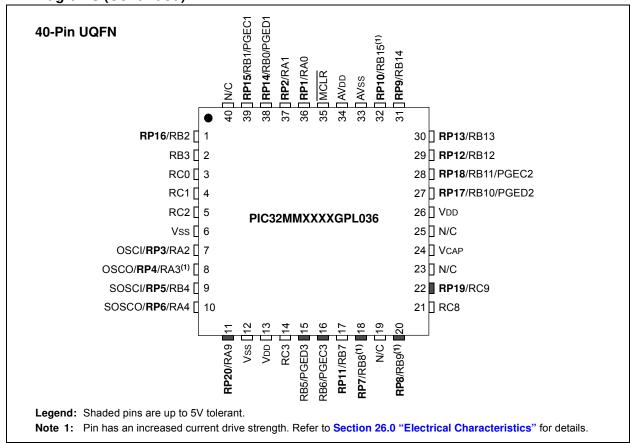

## **Pin Diagrams**

## TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 20-PIN SSOP DEVICES

| Pin | Function                                                  | Pin | Function                                                                                             |

|-----|-----------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------|

| 1   | MCLR                                                      | 11  | RP11/RB7                                                                                             |

| 2   | PGEC2/VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0               | 12  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                          |

| 3   | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                    | 13  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <del>U1RTS</del> /U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 4   | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                   | 14  | VCAP                                                                                                 |

| 5   | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                   | 15  | TDO/AN7/LVDIN/ <b>RP12</b> /RB12                                                                     |

| 6   | AN4/ <b>RP16</b> /RB2                                     | 16  | TDI/AN8/ <b>RP13</b> /RB13                                                                           |

| 7   | OSC1/CLKI/AN5/C1INB/ <b>RP3</b> /OCM1C/RA2                | 17  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                                |

| 8   | OSC2/CLKO/AN6/C1INA/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 18  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                                  |

| 9   | PGED3/SOSCI/ <b>RP5</b> /RB4                              | 19  | AVss/Vss                                                                                             |

| 10  | PGEC3/SOSCO/SCLKI/RP6/PWRLCLK/RA4                         | 20  | AVDD/VDD                                                                                             |

TABLE 3: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 20-PIN QFN DEVICES

| Pin | Function                                                                                                 | Pin | Function                                                   |  |  |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------|--|--|--|--|--|

| 1   | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                                                                  | 11  | VCAP                                                       |  |  |  |  |  |

| 2   | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                                                                  | 12  | TDO/AN7/LVDIN/ <b>RP12</b> /RB12                           |  |  |  |  |  |

| 3   | AN4/ <b>RP16</b> /RB2                                                                                    | 13  | TDI/AN8/ <b>RP13</b> /RB13                                 |  |  |  |  |  |

| 4   | OSC1/CLKI/AN5/C1INB/RP3/OCM1C/RA2                                                                        | 14  | CDAC1/AN9/RP9/RTCC/U1TX/SDI1/C1OUT/INT1/RB14               |  |  |  |  |  |

| 5   | OSC2/CLKO/AN6/C1INA/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup>                                                | 15  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup> |  |  |  |  |  |

| 6   | PGED3/SOSCI/ <b>RP5</b> /RB4                                                                             | 16  | AVss/Vss                                                   |  |  |  |  |  |

| 7   | PGEC3/SOSCO/SCLKI/RP6/PWRLCLK/RA4                                                                        | 17  | AVDD/VDD                                                   |  |  |  |  |  |

| 8   | <b>RP11</b> /RB7                                                                                         | 18  | MCLR                                                       |  |  |  |  |  |

| 9   | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                              | 19  | PGEC2/VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                |  |  |  |  |  |

| 10  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <del>U1RTS</del> /U1BCLK/SDO1/<br>C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> | 20  | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                     |  |  |  |  |  |

## TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN SPDIP/SSOP/SOIC DEVICES

| Pin | Function                                            | Pin | Function                                                           |

|-----|-----------------------------------------------------|-----|--------------------------------------------------------------------|

| 1   | MCLR                                                | 15  | PGEC3/RB6                                                          |

| 2   | VREF+/AN0/RP1/OCM1E/INT3/RA0                        | 16  | <b>RP11</b> /RB7                                                   |

| 3   | VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                    | 17  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                        |

| 4   | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0             | 18  | TMS/REFCLKI/RP8/T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9(1) |

| 5   | PGEC1/AN3/C1INC/C2INA/RP15/RB1                      | 19  | RP19/RC9                                                           |

| 6   | AN4/C1INB/ <b>RP16</b> /RB2                         | 20  | VCAP                                                               |

| 7   | AN11/C1INA/RB3                                      | 21  | PGED2/TDO/ <b>RP17</b> /RB10                                       |

| 8   | Vss                                                 | 22  | PGEC2/TDI/ <b>RP18</b> /RB11                                       |

| 9   | OSC1/CLKI/AN5/ <b>RP3</b> /OCM1C/RA2                | 23  | AN7/LVDIN/ <b>RP12</b> /RB12                                       |

| 10  | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 24  | AN8/ <b>RP13</b> /RB13                                             |

| 11  | SOSCI/ <b>RP5</b> /RB4                              | 25  | CDAC1/AN9/RP9/RTCC/U1TX/SDI1/C1OUT/INT1/RB14                       |

| 12  | SOSCO/SCLKI/RP6/PWRLCLK/RA4                         | 26  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>         |

| 13  | VDD                                                 | 27  | AVss                                                               |

| 14  | PGED3/RB5                                           | 28  | AVDD                                                               |

TABLE 5: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN QFN/UQFN DEVICES

| Pin | Function                                            | Pin | Function                                                                                             |  |  |  |  |  |  |

|-----|-----------------------------------------------------|-----|------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1   | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0             | 15  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <del>U1RTS</del> /U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |  |  |  |  |  |  |

| 2   | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1             | 16  | RP19/RC9                                                                                             |  |  |  |  |  |  |

| 3   | AN4/C1INB/ <b>RP16</b> /RB2                         | 17  | VCAP                                                                                                 |  |  |  |  |  |  |

| 4   | AN11/C1INA/RB3                                      | 18  | PGED2/TDO/ <b>RP17</b> /RB10                                                                         |  |  |  |  |  |  |

| 5   | Vss                                                 | 19  | PGEC2/TDI/ <b>RP18</b> /RB11                                                                         |  |  |  |  |  |  |

| 6   | OSC1/CLKI/AN5/ <b>RP3</b> /OCM1C/RA2                | 20  | AN7/LVDIN/ <b>RP12</b> /RB12                                                                         |  |  |  |  |  |  |

| 7   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 21  | AN8/ <b>RP13</b> /RB13                                                                               |  |  |  |  |  |  |

| 8   | SOSCI/ <b>RP5</b> /RB4                              | 22  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                                                |  |  |  |  |  |  |

| 9   | SOSCO/SCLKI/RP6/PWRLCLK/RA4                         | 23  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>                                           |  |  |  |  |  |  |

| 10  | VDD                                                 | 24  | AVss                                                                                                 |  |  |  |  |  |  |

| 11  | PGED3/RB5                                           | 25  | AVDD                                                                                                 |  |  |  |  |  |  |

| 12  | PGEC3/RB6                                           | 26  | MCLR                                                                                                 |  |  |  |  |  |  |

| 13  | RP11/RB7                                            | 27  | VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                                                                |  |  |  |  |  |  |

| 14  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>         | 28  | VREF-/AN1/RP2/OCM1F/RA1                                                                              |  |  |  |  |  |  |

TABLE 6: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN VQFN DEVICES

| Pin | Function                                            | Pin | Function                                                                       |

|-----|-----------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/ <b>RP16</b> /RB2                         | 19  | TMS/REFCLKI/RP8/T1CK/T1G/U1RTS/U1BCLK/SDO1/C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | AN11/C1INA/RB3                                      | 20  | RC8                                                                            |

| 3   | AN12/RC0                                            | 21  | RP19/RC9                                                                       |

| 4   | AN13/RC1                                            | 22  | VCAP                                                                           |

| 5   | RC2                                                 | 23  | VDD                                                                            |

| 6   | Vss                                                 | 24  | PGED2/TDO/ <b>RP17</b> /RB10                                                   |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                         | 25  | PGEC2/TDI/ <b>RP18</b> /RB11                                                   |

| 8   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup> | 26  | AN7/LVDIN/ <b>RP12</b> /RB12                                                   |

| 9   | SOSCI/ <b>RP5</b> /RB4                              | 27  | AN8/ <b>RP13</b> /RB13                                                         |

| 10  | SOSCO/SCLKI/RP6/PWRLCLK/RA4                         | 28  | CDAC1/AN9/ <b>RP9</b> /RTCC/U1TX/SDI1/C1OUT/INT1/RB14                          |

| 11  | <b>RP20</b> /RA9                                    | 29  | AN10/REFCLKO/ <b>RP10</b> /U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup>            |

| 12  | Vss                                                 | 30  | AVss                                                                           |

| 13  | VDD                                                 | 31  | AVDD                                                                           |

| 14  | RC3                                                 | 32  | MCLR                                                                           |

| 15  | PGED3/RB5                                           | 33  | VREF+/AN0/RP1/OCM1E/INT3/RA0                                                   |

| 16  | PGEC3/RB6                                           | 34  | VREF-/AN1/RP2/OCM1F/RA1                                                        |

| 17  | RP11/RB7                                            | 35  | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                                        |

| 18  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>         | 36  | PGEC1/AN3/C1INC/C2INA/ <b>RP15</b> /RB1                                        |

## Pin Diagrams (Continued)

TABLE 7: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 40-PIN UQFN DEVICES

| Pin | Function                                                                                                 | Pin | Function                                                   |

|-----|----------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------|

| 1   | AN4/C1INB/ <b>RP16</b> /RB2                                                                              | 21  | RC8                                                        |

| 2   | AN11/C1INA/RB3                                                                                           | 22  | RP19/RC9                                                   |

| 3   | AN12/RC0                                                                                                 | 23  | N/C                                                        |

| 4   | AN13/RC1                                                                                                 | 24  | VCAP                                                       |

| 5   | RC2                                                                                                      | 25  | N/C                                                        |

| 6   | Vss                                                                                                      | 26  | VDD                                                        |

| 7   | OSC1/CLKI/AN5/ <b>RP3</b> /OCM1C/RA2                                                                     | 27  | PGED2/TDO/ <b>RP17</b> /RB10                               |

| 8   | OSC2/CLKO/AN6/ <b>RP4</b> /OCM1D/RA3 <sup>(1)</sup>                                                      | 28  | PGEC2/TDI/ <b>RP18</b> /RB11                               |

| 9   | SOSCI/ <b>RP5</b> /RB4                                                                                   | 29  | AN7/LVDIN/ <b>RP12</b> /RB12                               |

| 10  | SOSCO/SCLKI/RP6/PWRLCLK/RA4                                                                              | 30  | AN8/ <b>RP13</b> /RB13                                     |

| 11  | <b>RP20</b> /RA9                                                                                         | 31  | CDAC1/AN9/RP9/RTCC/U1TX/SDI1/C1OUT/INT1/RB14               |

| 12  | Vss                                                                                                      | 32  | AN10/REFCLKO/RP10/U1RX/SS1/FSYNC1/INT0/RB15 <sup>(1)</sup> |

| 13  | VDD                                                                                                      | 33  | AVss                                                       |

| 14  | RC3                                                                                                      | 34  | AVDD                                                       |

| 15  | PGED3/RB5                                                                                                | 35  | MCLR                                                       |

| 16  | PGEC3/RB6                                                                                                | 36  | VREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                      |

| 17  | RP11/RB7                                                                                                 | 37  | VREF-/AN1/RP2/OCM1F/RA1                                    |

| 18  | TCK/RP7/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                                              | 38  | PGED1/AN2/C1IND/C2INB/ <b>RP14</b> /RB0                    |

| 19  | N/C                                                                                                      | 39  | PGEC1/AN3/C1INC/C2INA/RP15/RB1                             |

| 20  | TMS/REFCLKI/ <b>RP8</b> /T1CK/T1G/ <del>U1RTS</del> /U1BCLK/SDO1/<br>C2OUT/OCM1B/INT2/RB9 <sup>(1)</sup> | 40  | N/C                                                        |

## **Table of Contents**

| 1.0   | Device Overview                                                         | 13  |

|-------|-------------------------------------------------------------------------|-----|

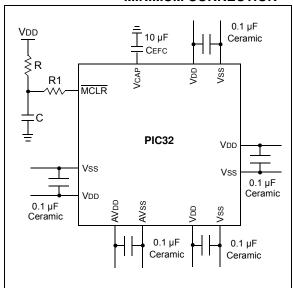

| 2.0   | Guidelines for Getting Started with 32-Bit Microcontrollers             | 19  |

| 3.0   | CPU                                                                     | 23  |

| 4.0   | Memory Organization                                                     | 33  |

| 5.0   | Flash Program Memory                                                    | 37  |

| 6.0   | Resets                                                                  | 45  |

| 7.0   | CPU Exceptions and Interrupt Controller                                 | 51  |

| 8.0   | Oscillator Configuration                                                | 65  |

| 9.0   | I/O Ports                                                               | 77  |

| 10.0  | Timer1                                                                  | 87  |

| 11.0  |                                                                         |     |

| 12.0  | Capture/Compare/PWM/Timer Modules (MCCP and SCCP)                       | 95  |

| 13.0  | Serial Peripheral Interface (SPI) and Inter-IC Sound (I <sup>2</sup> S) | 109 |

| 14.0  | Universal Asynchronous Receiver Transmitter (UART)                      | 117 |

| 15.0  | Real-Time Clock and Calendar (RTCC)                                     | 123 |

| 16.0  | 12-Bit Analog-to-Digital Converter with Threshold Detect                | 133 |

| 17.0  | 32-Bit Programmable Cyclic Redundancy Check (CRC) Generator             | 147 |

| 18.0  | Configurable Logic Cell (CLC)                                           | 151 |

| 19.0  | Comparator                                                              |     |

| 20.0  | Control Digital-to-Analog Converter (CDAC)                              | 169 |

| 21.0  | High/Low-Voltage Detect (HLVD)                                          | 173 |

| 22.0  | Power-Saving Features                                                   | 177 |

| 23.0  | Special Features                                                        | 181 |

| 24.0  | Development Support                                                     | 199 |

| 25.0  | Instruction Set                                                         | 203 |

| 26.0  | Electrical Characteristics                                              | 205 |

| 27.0  | Packaging Information                                                   | 233 |

| Appe  | endix A: Revision History                                               | 257 |

| Index | X                                                                       | 259 |

| The I | Microchip Web Site                                                      | 263 |

| Custo | omer Change Notification Service                                        | 263 |

| Custo | omer Support                                                            | 263 |

| Prod  | luct Identification System                                              | 265 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; <a href="http://www.microchip.com">http://www.microchip.com</a>

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## **Referenced Sources**

This device data sheet is based on the following individual sections of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

**Note:** To access the documents listed below, browse the documentation section of the Microchip web site (www.microchip.com).

- Section 1. "Introduction" (DS60001127)

- Section 5. "Flash Programming" (DS60001121)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupts" (DS60001108)

- Section 10. "Power-Saving Modes" (DS60001130)

- Section 14. "Timers" (DS60001105)

- Section 19. "Comparator" (DS60001110)

- Section 21. "UART" (DS61107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS61106)

- Section 25. "12-Bit Analog-to-Digital Converter (ADC) with Threshold Detect" (DS60001359)

- Section 28. "RTCC with Timestamp" (DS60001362)

- Section 30. "Capture/Compare/PWM/Timer (MCCP and SCCP)" (DS60001381)

- Section 33. "Programming and Diagnostics" (DS61129)

- Section 36. "Configurable Logic Cell" (DS60001363)

- Section 45. "Control Digital-to-Analog Converter (CDAC)" (DS60001327)

- Section 50. "CPU for Devices with MIPS32® microAptiv™ and M-Class Cores" (DS60001192)

- Section 59. "Oscillators with DCO" (DS60001329)

- Section 60. "32-Bit Programmable Cyclic Redundancy Check (CRC)" (DS60001336)

- · Section 62. "Dual Watchdog Timer" (DS60001365)

| NOTES: |  |  |  |

|--------|--|--|--|

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

|        |  |  |  |

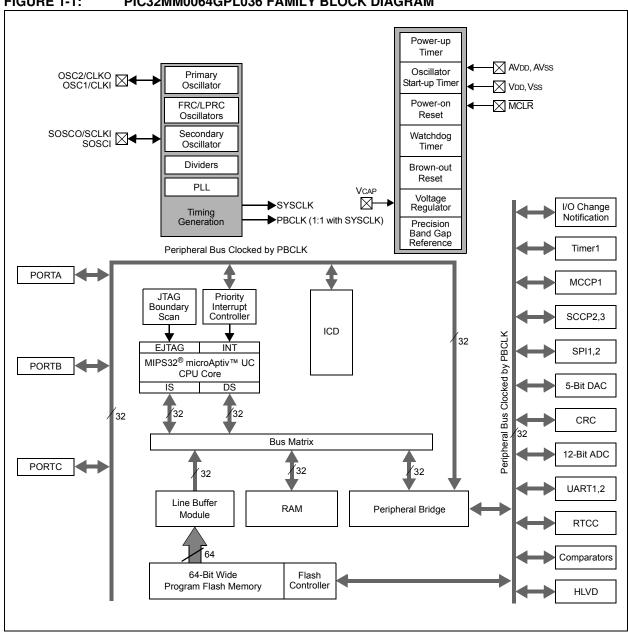

#### 1.0 **DEVICE OVERVIEW**

Note:

This data sheet summarizes the features of the PIC32MM0064GPL036 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

This data sheet contains device-specific information for the PIC32MM0064GPL036 family devices.

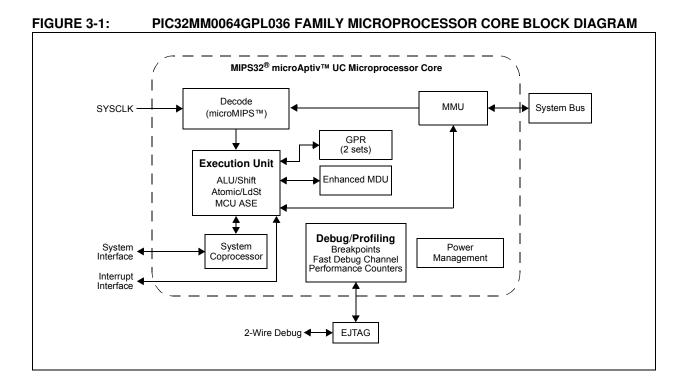

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0064GPL036 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

FIGURE 1-1: PIC32MM0064GPL036 FAMILY BLOCK DIAGRAM

TABLE 1-1: PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION

|          |               |                | Pin                    | Number                        |                |                |             |                |                                            |

|----------|---------------|----------------|------------------------|-------------------------------|----------------|----------------|-------------|----------------|--------------------------------------------|

| Pin Name | 20-Pin<br>QFN | 20-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 28-Pin<br>SPDIP/<br>SSOP/SOIC | 36-Pin<br>VQFN | 40-Pin<br>UQFN | Pin<br>Type | Buffer<br>Type | Description                                |

| AN0      | 19            | 2              | 27                     | 2                             | 33             | 36             | ı           | ANA            | Analog-to-Digital Converter input channels |

| AN1      | 20            | 3              | 28                     | 3                             | 34             | 37             | ı           | ANA            |                                            |

| AN2      | 1             | 4              | 1                      | 4                             | 35             | 38             | ı           | ANA            |                                            |

| AN3      | 2             | 5              | 2                      | 5                             | 36             | 39             | - 1         | ANA            |                                            |

| AN4      | 3             | 6              | 3                      | 6                             | 1              | 1              | -           | ANA            |                                            |

| AN5      | 4             | 7              | 6                      | 9                             | 7              | 7              | -           | ANA            |                                            |

| AN6      | 5             | 8              | 7                      | 10                            | 8              | 8              | I           | ANA            |                                            |

| AN7      | 12            | 15             | 20                     | 23                            | 26             | 29             | ı           | ANA            |                                            |

| AN8      | 13            | 16             | 21                     | 24                            | 27             | 30             | 1           | ANA            |                                            |

| AN9      | 14            | 17             | 22                     | 25                            | 28             | 31             | I           | ANA            |                                            |

| AN10     | 15            | 18             | 23                     | 26                            | 29             | 32             | I           | ANA            |                                            |

| AN11     | _             | _              | 4                      | 7                             | 2              | 2              | I           | ANA            |                                            |

| AN12     | _             | _              | _                      | _                             | 3              | 3              | I           | ANA            |                                            |

| AN13     |               | _              | _                      | _                             | 4              | 4              | I           | ANA            |                                            |

| AVDD     | 17            | 20             | 25                     | 28                            | 31             | 34             | Р           | _              | Analog modules power supply                |

| AVss     | 16            | 19             | 24                     | 27                            | 30             | 33             | Р           | _              | Analog modules ground                      |

| C1INA    | 5             | 8              | 4                      | 7                             | 2              | 2              | I           | ANA            | Comparator 1 Input A                       |

| C1INB    | 4             | 7              | 3                      | 6                             | 1              | 1              | -           | ANA            | Comparator 1 Input B                       |

| C1INC    | 2             | 5              | 2                      | 5                             | 36             | 39             | -           | ANA            | Comparator 1 Input C                       |

| C1IND    | 1             | 4              | 1                      | 4                             | 35             | 38             | I           | ANA            | Comparator 1 Input D                       |

| C1OUT    | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | DIG            | Comparator 1 output                        |

| C2INA    | 2             | 5              | 2                      | 5                             | 36             | 39             | I           | ANA            | Comparator 2 Input A                       |

| C2INB    | 1             | 4              | 1                      | 4                             | 35             | 38             | I           | ANA            | Comparator 2 Input B                       |

| C2OUT    | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | Comparator 2 output                        |

| CLKI     | 4             | 7              | 6                      | 9                             | 7              | 7              | I           | ST             | External Clock input (EC mode)             |

| CLKO     | 5             | 8              | 7                      | 10                            | 8              | 8              | 0           | DIG            | System clock output                        |

| CDAC1    | 14            | 17             | 22                     | 25                            | 28             | 31             | 0           | ANA            | Digital-to-Analog Converter output         |

| FSYNC1   | 15            | 18             | 23                     | 26                            | 29             | 32             | I/O         | ST/DIG         | SPI1 frame signal input or output          |

| INT0     | 15            | 18             | 23                     | 26                            | 29             | 32             | I           | ST             | External Interrupt 0                       |

| INT1     | 14            | 17             | 22                     | 25                            | 28             | 31             | I           | ST             | External Interrupt 1                       |

| INT2     | 10            | 13             | 15                     | 18                            | 19             | 20             | 1           | ST             | External Interrupt 2                       |

| INT3     | 19            | 2              | 27                     | 2                             | 33             | 36             | I           | ST             | External Interrupt 3                       |

| LVDIN    | 12            | 15             | 20                     | 23                            | 26             | 29             | I           | ANA            | High/Low-Voltage Detect input              |

| MCLR     | 18            | 1              | 26                     | 1                             | 32             | 35             | I           | ST             | Master Clear (device Reset)                |

| OCM1A    | 9             | 12             | 14                     | 17                            | 18             | 18             | 0           | DIG            | MCCP1 Output A                             |

| OCM1B    | 10            | 13             | 15                     | 18                            | 19             | 20             | 0           | DIG            | MCCP1 Output B                             |

| OCM1C    | 4             | 7              | 6                      | 9                             | 7              | 7              | 0           | DIG            | MCCP1 Output C                             |

| OCM1D    | 5             | 8              | 7                      | 10                            | 8              | 8              | 0           | DIG            | MCCP1 Output D                             |

| OCM1E    | 19            | 2              | 27                     | 2                             | 33             | 36             | 0           | DIG            | MCCP1 Output E                             |

| OCM1F    | 20            | 3              | 28                     | 3                             | 34             | 37             | 0           | DIG            | MCCP1 Output F                             |

| OSC1     | 4             | 7              | 6                      | 9                             | 7              | 7              | _           | <u> </u>       | Primary Oscillator crystal                 |

| OSC2     | 5             | 8              | 7                      | 10                            | 8              | 8              |             | _              | Primary Oscillator crystal                 |

|          |               |                | aor innut              |                               | DIC - Dic      |                |             | 1              | ANA = Analog lovel input/output            |

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

ANA = Analog level input/output

TABLE 1-1: PIC32MM0064GPL036 FAMILY PINOUT DESCRIPTION (CONTINUED)

| RB14         14         17         22         25         28         31         I/O         ST/DIG         PORTB digital I/O           RB15         15         18         23         26         29         32         I/O         ST/DIG         PORTB digital I/O           RC0         —         —         —         3         3         I/O         ST/DIG         PORTC digital I/O           RC1         —         —         4         4         I/O         ST/DIG         PORTC digital I/O           RC2         —         —         5         5         I/O         ST/DIG         PORTC digital I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |    |    | Pin  | Number |    |    |     |        |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|----|------|--------|----|----|-----|--------|--------------------------------------|

| PGEC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin Name |    |    | QFN/ | SPDIP/ |    |    |     |        | Description                          |

| PGEC3         7         10         12         15         16         16         I         ST         ICSP Port 3 programming clock input           PGED1         1         4         1         4         35         38         I/O         ST/DIG ICSP Port 1 programming data           PGED2         20         3         18         21         24         27         I/O         ST/DIG ICSP Port 1 programming data           PGED3         6         9         11         14         15         15         I/O         ST/DIG ICSP Port 2 programming data           PWRLCLK         7         10         9         12         10         10         I         ST         Real-Time Clock 50/60 Hz clock input           RAD         19         2         27         2         33         36         I/O         ST/DIG PORTA digital I/O           RA1         20         3         28         3         34         37         I/O         ST/DIG PORTA digital I/O           RA2         4         7         6         9         7         7         I/O         ST/DIG PORTA digital I/O           RA3         5         8         7         10         8         8         I/O <t< td=""><td>PGEC1</td><td>2</td><td>5</td><td>2</td><td>5</td><td>36</td><td>39</td><td>I</td><td>ST</td><td>ICSP Port 1 programming clock input</td></t<> | PGEC1    | 2  | 5  | 2    | 5      | 36 | 39 | I   | ST     | ICSP Port 1 programming clock input  |

| PGED1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PGEC2    | 19 | 2  | 19   | 22     | 25 | 28 | I   | ST     | ICSP Port 2 programming clock input  |

| PGED2   20   3   18   21   24   27   1/0   ST/DIG   ICSP Port 2 programming data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PGEC3    | 7  | 10 | 12   | 15     | 16 | 16 | I   | ST     | ICSP Port 3 programming clock input  |

| PGED3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PGED1    | 1  | 4  | 1    | 4      | 35 | 38 | I/O | ST/DIG | ICSP Port 1 programming data         |

| PWRLCLK   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PGED2    | 20 | 3  | 18   | 21     | 24 | 27 | I/O | ST/DIG | ICSP Port 2 programming data         |

| RAO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PGED3    | 6  | 9  | 11   | 14     | 15 | 15 | I/O | ST/DIG | ICSP Port 3 programming data         |

| RA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PWRLCLK  | 7  | 10 | 9    | 12     | 10 | 10 | I   | ST     | Real-Time Clock 50/60 Hz clock input |

| RA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA0      | 19 | 2  | 27   | 2      | 33 | 36 | I/O | ST/DIG | PORTA digital I/O                    |

| RA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA1      | 20 | 3  | 28   | 3      | 34 | 37 | I/O | ST/DIG | PORTA digital I/O                    |

| RA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA2      | 4  | 7  | 6    | 9      | 7  | 7  | I/O | ST/DIG | PORTA digital I/O                    |

| RA9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA3      | 5  | 8  | 7    | 10     | 8  | 8  | I/O | ST/DIG | PORTA digital I/O                    |

| RB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA4      | 7  | 10 | 9    | 12     | 10 | 10 | I/O | ST/DIG | PORTA digital I/O                    |

| RB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RA9      |    | _  |      | _      | 11 | 11 | I/O | ST/DIG | PORTA digital I/O                    |

| RB2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RB0      | 1  | 4  | 1    | 4      | 35 | 38 | I/O | ST/DIG | PORTB digital I/O                    |

| RB3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RB1      | 2  | 5  | 2    | 5      | 36 | 39 | I/O | ST/DIG | PORTB digital I/O                    |

| RB4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RB2      | 3  | 6  | 3    | 6      | 1  | 1  | I/O | ST/DIG | PORTB digital I/O                    |

| RB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RB3      |    | _  | 4    | 7      | 2  | 2  | I/O | ST/DIG | PORTB digital I/O                    |

| RB6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RB4      | 6  | 9  | 8    | 11     | 9  | 9  | I/O | ST/DIG | PORTB digital I/O                    |

| RB7 8 11 13 16 17 17 1/O ST/DIG PORTB digital I/O RB8 9 12 14 17 18 18 18 I/O ST/DIG PORTB digital I/O RB9 10 13 15 18 19 20 I/O ST/DIG PORTB digital I/O RB10 — 18 21 24 27 I/O ST/DIG PORTB digital I/O RB11 — 19 22 25 28 I/O ST/DIG PORTB digital I/O RB12 12 15 20 23 26 29 I/O ST/DIG PORTB digital I/O RB13 13 16 21 24 27 30 I/O ST/DIG PORTB digital I/O RB14 14 17 22 25 28 31 I/O ST/DIG PORTB digital I/O RB15 15 18 23 26 29 32 I/O ST/DIG PORTB digital I/O RC0 — — — 3 3 1 I/O ST/DIG PORTB digital I/O RC1 — — — 4 4 I/O ST/DIG PORTB digital I/O RC2 — — — 5 5 5 I/O ST/DIG PORTC digital I/O RC3 — — — 14 14 I/O ST/DIG PORTC digital I/O RC6 — — — 20 21 I/O ST/DIG PORTC digital I/O RC9 — — 16 19 21 22 I/O ST/DIG PORTC digital I/O REFCLKI 10 13 15 18 19 20 I ST Reference clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RB5      |    | _  | 11   | 14     | 15 | 15 | I/O | ST/DIG | PORTB digital I/O                    |

| RB8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RB6      |    | _  | 12   | 15     | 16 | 16 | I/O | ST/DIG | PORTB digital I/O                    |