# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- Frequency Range 10MHz to 220MHz •

- Zero input output delay.

- Low output-to-output skew.

- Optional Drive Strength: Standard (8mA) PL123E-05 High (12mA) PL123E-05H

- 2.5V or 3.3V, ±10% operation.

- Available in 8-pin SOP packaging.

### DESCRIPTION

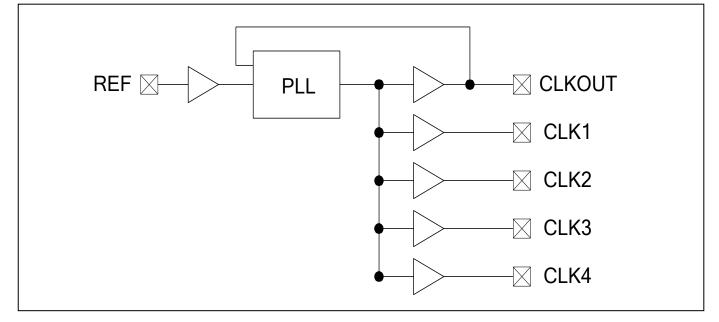

The PL123E-05 (-05H for High Drive) is a high performance, low skew, low jitter zero delay buffer designed to distribute high speed clocks. It has five low-skew outputs that are synchronized with the input. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than  $\pm 100$  ps, the device acts as a zero delay buffer. The input output propagation delay can be advanced or delayed by adjusting the load on the CLKOUT pin.

These parts are not intended for 5V input-tolerant applications.

#### **BLOCK DIAGRAM**

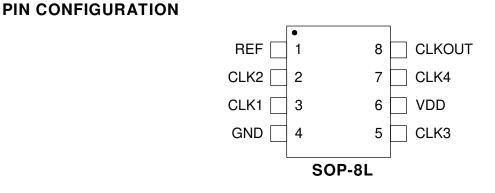

#### **PIN DESCRIPTION**

| Name                    | Package Type<br>SOP-8L | Туре | Description                                            |  |

|-------------------------|------------------------|------|--------------------------------------------------------|--|

| REF <sup>[1]</sup>      | 1                      | I    | Input reference frequency.                             |  |

| CLK2 <sup>[2]</sup>     | 2                      | 0    | Buffered clock output.                                 |  |

| CLK1 <sup>[2]</sup>     | 3                      | 0    | Buffered clock output.                                 |  |

| GND                     | 4                      | Р    | Ground connection.                                     |  |

| CLK3 <sup>[2]</sup>     | 5                      | 0    | Buffered clock output.                                 |  |

| VDD                     | 6                      | Р    | VDD connection.                                        |  |

| CLK4 <sup>[2]</sup>     | 7                      | 0    | Buffered clock output.                                 |  |

| CLKOUT <sup>[2,3]</sup> | 8                      | 0    | Buffered clock output. Internal feed back on this pin. |  |

Notes: 1: Weak pull-down. 2: Weak pull-down on all outputs.

3. This output is driven and has an internal feedback for the PLL. The load on this output can be adjusted to change the skew between the reference and output.

#### **INPUT / OUTPUT SKEW CONTROL**

The PL123E-05 will achieve Zero Delay from input to output when all the outputs are loaded equally. Adjustments to the input/output delay can be made by adjusting the loading on the CLKOUT pin. Please contact Micrel for more information.

### Low Skew Zero Delay Buffer

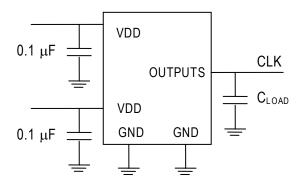

### LAYOUT RECOMMENDATIONS

The following guidelines are to assist you with a performance optimized PCB design:

## Signal Integrity and Termination Considerations

- Keep traces short!

- Trace = Inductor. With a capacitive load this equals ringing!

- Long trace = Transmission Line. Without proper termination this will cause reflections (looks like ringing).

- Design long traces as "striplines" or "microstrips" with defined impedance.

- Match trace at one side to avoid reflections bouncing back and forth.

#### Decoupling and Power Supply Considerations

- Place decoupling capacitors as close as possible to the VDD pin(s) to limit noise from the power supply

- Addition of a ferrite bead in series with VDD can help prevent noise from other board sources

- Value of decoupling capacitor is frequency dependant. Typical values to use are 0.1μF for designs using frequencies < 50MHz and 0.01μF for designs using frequencies > 50MHz.

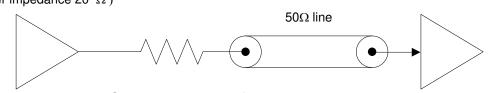

To CMOS Input

### **Typical CMOS termination**

#### Place Series Resistor as close as possible to CMOS output

CMOS Output Buffer (Typical buffer impedance 20  $\Omega$ )

Connect a 33 Ω series resistor at each of the output clocks to enhance the stability of the output signal

#### **Absolute Maximum Conditions**

### Low Skew Zero Delay Buffer

| Supply Voltage to Ground Potential0.5V to 4.6V |  |

|------------------------------------------------|--|

| DC Input VoltageV <sub>SS</sub> – 0.5V to 4.6V |  |

| Storage Temperature65°C to 150°C               |  |

| Junction Temperature           | 150°C   |

|--------------------------------|---------|

| Static Discharge Voltage       |         |

| (per MIL-STD-883, Method 3015) | > 2000V |

### **Operating Condition**

| Description                                                                                          | Parameter                     | Min  | Max  | Unit |

|------------------------------------------------------------------------------------------------------|-------------------------------|------|------|------|

| Supply Voltage                                                                                       | V <sub>dd</sub>               | 2.25 | 3.63 | V    |

| Load Capacitance, <100 MHz, 3.3V                                                                     | C <sub>L</sub> <sup>[4]</sup> | _    | 30   | pF   |

| Load Capacitance, <100 MHz, 2.5V with High Drive                                                     |                               | _    | 30   | pF   |

| Load Capacitance, <133.3 MHz, 3.3V                                                                   |                               | _    | 22   | pF   |

| Load Capacitance, <133.3 MHz, 2.5V with High Drive                                                   |                               | _    | 22   | pF   |

| Load Capacitance, <133.3 MHz, 2.5V with Standard Drive                                               |                               | _    | 15   | pF   |

| Load Capacitance, >133.3 MHz, 3.3V                                                                   |                               | _    | 15   | pF   |

| Load Capacitance, >133.3 MHz, 2.5V with High Drive                                                   |                               | _    | 15   | pF   |

| Input Capacitance <sup>[5]</sup>                                                                     | C <sub>IN</sub>               | _    | 5    | pF   |

| Closed-loop bandwidth (typical), 3.3V                                                                | BW                            | 1    |      | MHz  |

| Closed-loop bandwidth (typical), 2.5V                                                                |                               | 0.5  |      | MHz  |

| Output Impedance (typical), 3.3V High Drive                                                          | Rout                          | 23   |      | Ω    |

| Output Impedance (typical), 3.3V Standard Drive                                                      |                               | 33   |      | Ω    |

| Output Impedance (typical), 2.5V High Drive                                                          |                               | 26   |      | Ω    |

| Output Impedance (typical), 2.5V Standard Drive                                                      |                               | 3    | 9    | Ω    |

| Power-up time for all $V_{DD}$ 's to reach minimum specified voltage (power ramps must be monotonic) | t <sub>PU</sub>               | 0.01 | 250  | ms   |

#### Notes:

4. Applies to Test Circuit #1.

5. Applies to both REF Clock and internal feedback path on CLKOUT.

6. Theta Ja, EIA JEDEC 51 test board conditions, 2S2P; Theta Jc Mil-Spec 883E Method 1012.1.

### Low Skew Zero Delay Buffer

#### 3.3V DC Electrical Specifications

| Description           | Parameter       | Test Conditions                                                     | Min        | Max                   | Unit   |

|-----------------------|-----------------|---------------------------------------------------------------------|------------|-----------------------|--------|

| Supply Voltage        | V <sub>DD</sub> |                                                                     | 2.97       | 3.63                  | V      |

| Input LOW Voltage     | V <sub>IL</sub> |                                                                     | -          | 0.8                   | V      |

| Input HIGH Voltage    | V <sub>IH</sub> |                                                                     | 2.5        | V <sub>DD</sub> + 0.3 | V      |

| Input Leakage Current | I <sub>IL</sub> | $0 < V_{IN} < V_{IL}$                                               | -          | ±10                   | μA     |

| Input HIGH Current    | I <sub>IH</sub> | V <sub>IN</sub> = V <sub>DD</sub>                                   | -          | 100                   | μA     |

| Output LOW Voltage    | V <sub>OL</sub> | $I_{OL}$ = 8 mA (Standard Drive)<br>$I_{OL}$ = 12 mA (High Drive)   | -          | 0.4<br>0.4            | V<br>V |

| Output HIGH Voltage   | V <sub>OH</sub> | $I_{OH}$ = -8 mA (Standard Drive)<br>$I_{OH}$ = -12 mA (High Drive) | 2.4<br>2.4 |                       | V<br>V |

| Supply Current        | I <sub>DD</sub> | Unloaded outputs, 66-MHz REF                                        | -          | 45                    | mA     |

### 2.5V DC Electrical Specifications

| Description           | Parameter       | Test Conditions                                                     | Min                                            | Max            | Unit |

|-----------------------|-----------------|---------------------------------------------------------------------|------------------------------------------------|----------------|------|

| Supply Voltage        | $V_{DD}$        |                                                                     | 2.25                                           | 2.75           | V    |

| Input LOW Voltage     | VIL             |                                                                     | -                                              | 0.7            | V    |

| Input HIGH Voltage    | V <sub>IH</sub> |                                                                     | 1.7                                            | $V_{DD}$ + 0.3 | V    |

| Input Leakage Current | ۱ <sub>۱L</sub> | 0 <v<sub>IN &lt; V<sub>DD</sub></v<sub>                             | -                                              | 10             | μA   |

| Input HIGH Current    | I <sub>IH</sub> | $V_{IN} = V_{DD}$                                                   | -                                              | 100            | μA   |

| Output LOW Voltage    | V <sub>OL</sub> | $I_{OL}$ = 8 mA (Standard Drive)<br>$I_{OL}$ = 12 mA (High Drive)   |                                                | 0.5<br>0.5     | V    |

| Output HIGH Voltage   | V <sub>он</sub> | $I_{OH}$ = -8 mA (Standard Drive)<br>$I_{OH}$ = -12 mA (High Drive) | V <sub>DD</sub> – 0.6<br>V <sub>DD</sub> – 0.6 |                | V    |

| Supply Current        | I <sub>DD</sub> | Unloaded outputs, 66-MHz REF                                        | -                                              | 30             | mA   |

### Low Skew Zero Delay Buffer

### 3.3V and 2.5V AC Electrical Specifications

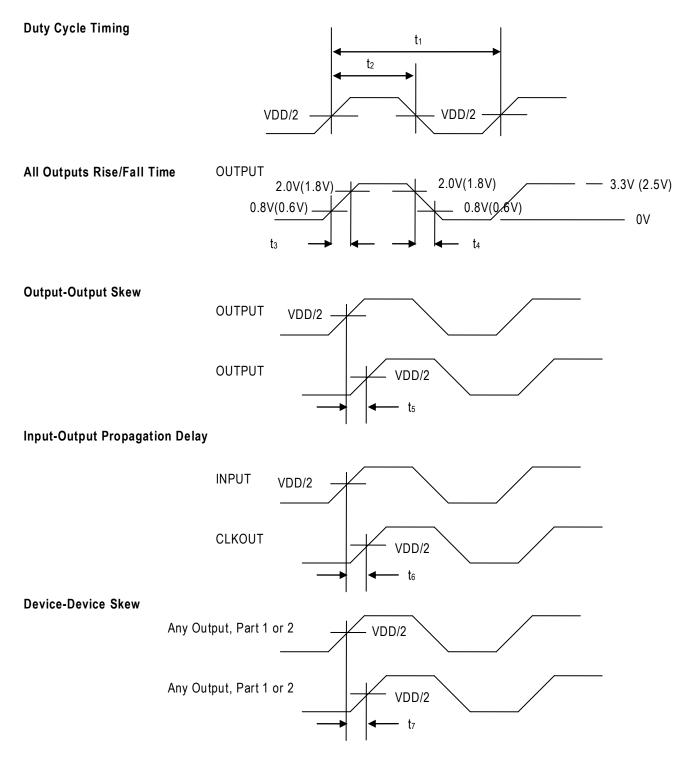

| Description                           | Parameter         | Test Conditions                                                         | Min  | Тур | Max  | Unit |

|---------------------------------------|-------------------|-------------------------------------------------------------------------|------|-----|------|------|

|                                       |                   | 3.3V High Drive                                                         | 10   | I   | 220  | MHz  |

| Maximum Frequency <sup>[7]</sup>      |                   | 3.3V Standard Drive                                                     | 10   | I   | 167  | MHz  |

| (Input/Output)                        | 1/t1              | 2.5V High Drive                                                         | 10   | I   | 200  | MHz  |

|                                       |                   | 2.5V Standard Drive                                                     | 10   | I   | 134  | MHz  |

| Input Duty Cycle                      | Ŧ                 | <133.3 MHz                                                              | 25   | -   | 75   | %    |

| (PLL Mode only)                       | TIDC              | >133.3 MHz                                                              | 40   | -   | 60   | %    |

|                                       | 4 • 4             | <133.3 MHz                                                              | 47   | -   | 53   | %    |

| Output Duty Cycle <sup>[8]</sup>      | $t_2 \div t_1$    | >133.3 MHz                                                              | 45   | -   | 55   | %    |

|                                       |                   | Standard Drive, CL = 30pF, <100 MHz                                     | -    | 1.6 | -    | ns   |

|                                       |                   | Standard Drive, CL = 22pF, <133.3 MHz                                   | -    | 1.6 | -    | ns   |

| Diag Fall Time $(2, 2)$ ()[8]         |                   | Standard Drive, CL = 15pF, <167 MHz                                     | -    | 0.6 | -    | ns   |

| Rise, Fall Time (3.3V) <sup>[8]</sup> | $t_3, t_4$        | High Drive, CL = 30pF, <100 MHz                                         | -    | 1.2 | -    | ns   |

|                                       |                   | High Drive, CL = 22pF, <133.3 MHz                                       | -    | 1.2 | -    | ns   |

|                                       |                   | High Drive, CL = 15pF, >133.3 MHz                                       | -    | 0.5 | -    | ns   |

|                                       | t3, t4            | Standard Drive, CL = 15pF, <133.33 MHz                                  | -    | 1.5 | -    | ns   |

| Dian Fall Time (2 5)()[8]             |                   | High Drive, CL = 30pF, <100 MHz                                         | -    | 2.1 | -    | ns   |

| Rise, Fall Time (2.5V) <sup>[8]</sup> |                   | High Drive, CL = 22pF, <133.3 MHz                                       | -    | 1.3 | -    | ns   |

|                                       |                   | High Drive, CL = 15pF, >133.3 MHz                                       | -    | 1.2 | _    | ns   |

| Output to Output Skew [8]             | t <sub>5</sub>    | All outputs equally loaded                                              | -    | -   | 100  | ps   |

| Delay, REF Rising Edge                | ] t <sub>6</sub>  | PLL enabled @ 3.3V                                                      | -100 | -   | 100  | ps   |

| to CLKOUT Rising Edge <sup>[8]</sup>  |                   | PLL enabled @2.5V                                                       | -200 | -   | 200  | ps   |

| Part to Part Skew <sup>[8]</sup>      | t <sub>7</sub>    | Measured at $V_{DD}/2$ .<br>Any output to any output, 3.3V supply       | -    | -   | ±150 | ps   |

| Fait to Fait Skewton                  |                   | Measured at $V_{DD}/2$ .<br>Any output to any output, 2.5V supply       | -    | -   | ±300 | ps   |

| PLL Lock Time <sup>[8]</sup>          | t <sub>LOCK</sub> | Stable power supply, valid clocks pre-<br>sented on REF and CLKOUT pins | -    | -   | 1.0  | ms   |

| Cycle-to-Cycle Jitter,                | TJCC              | 3.3V, >66 MHz, <15pF                                                    | -    | -   | 55   | ps   |

|                                       |                   | 3.3V, >66 MHz, <30pF, Standard. Drive                                   | -    | -   | 125  | ps   |

|                                       |                   | 3.3V, >66 MHz, <30pF, High Drive                                        | -    | -   | 100  | ps   |

| Peak <sup>[8,9]</sup>                 |                   | 2.5V, >66 MHz, <15pF, Standard. Drive                                   | -    | -   | 100  | ps   |

|                                       |                   | 2.5V, >66 MHz, <15pF, High Drive                                        | -    | -   | 80   | ps   |

|                                       |                   | 2.5V, >66 MHz, <30pF, High Drive                                        | -    | -   | 125  | ps   |

### Low Skew Zero Delay Buffer

#### **3.3V and 2.5V AC Electrical Specifications** (continued)

| Description                                              | Parameter                          | Test Conditions                        | Min | Тур | Max | Unit |

|----------------------------------------------------------|------------------------------------|----------------------------------------|-----|-----|-----|------|

|                                                          |                                    | 3.3V, 66–100 MHz, <15 pF               | -   | _   | 60  | ps   |

|                                                          |                                    | 3.3V, >100 MHz, <15 pF                 | -   | _   | 35  | ps   |

| Period Jitter, T <sub>PER</sub><br>Peak <sup>[8,9]</sup> |                                    | 3.3V, >66 MHz, <30 pF, Standard Drive  | -   | _   | 75  | ps   |

|                                                          | T <sub>PER</sub>                   | 3.3V, >66 MHz, <30 pF, High Drive      | -   | _   | 70  | ps   |

|                                                          |                                    | 2.5V, >66 MHz, <15 pF, Standard. Drive | -   | _   | 60  | ps   |

|                                                          |                                    | 2.5V, 66–100 MHz, <15 pF, High Drive   | -   | _   | 60  | ps   |

|                                                          | 2.5V, >100 MHz, <15 pF, High Drive | -                                      | _   | 45  | ps  |      |

#### Notes:

7. For the given maximum loading conditions. See  $C_L$  in Operating Conditions Table.

8. Parameter is guaranteed by design and characterization. Not 100% tested in production.

9. Typical jitter is measured at 3.3V or 2.5V, 29°C, with all outputs driven into the maximum specified load.

### Low Skew Zero Delay Buffer

#### SWITCHING WAVEFORMS

### **TEST CIRCUITS**

#### Test Circuit #1

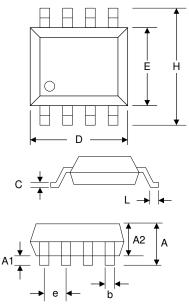

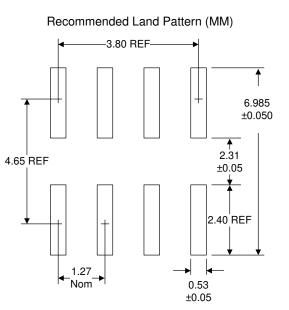

### PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

SOP-8L

| Cumb al | Dimension (MM) |      |  |

|---------|----------------|------|--|

| Symbol  | Min            | Max  |  |

| А       | 1.35           | 1.75 |  |

| A1      | 0.10           | 0.25 |  |

| A2      | 1.25           | 1.50 |  |

| b       | 0.33           | 0.53 |  |

| С       | 0.19           | 0.27 |  |

| D       | 4.80           | 5.00 |  |

| Е       | 3.80           | 4.00 |  |

| Н       | 5.80           | 6.20 |  |

| L       | 0.40           | 0.89 |  |

| е       | 1.27 BSC       |      |  |

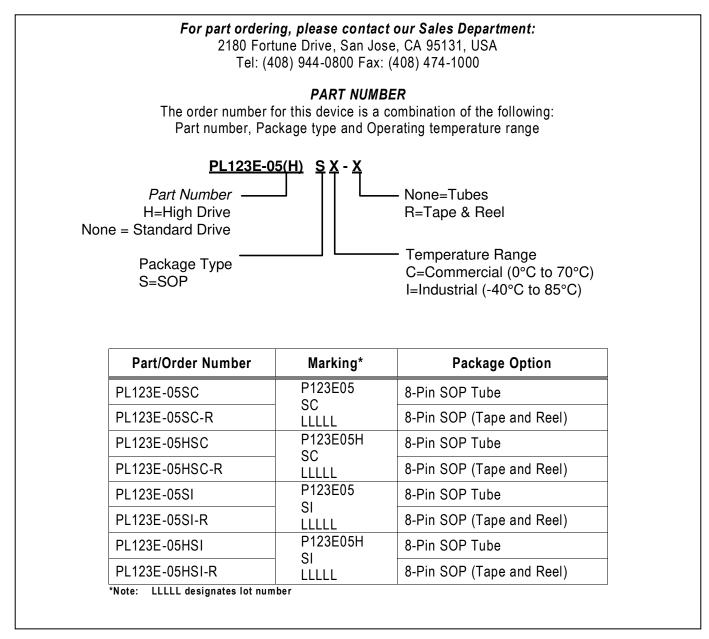

### **ORDERING INFORMATION (GREEN PACKAGE COMPLIANT)**

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.