Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- 1:9 LVCMOS output fanout buffer for DC to 150MHz

- 8mA Output Drive Strength

- Low power consumption for portable applications

- Low input-output delay

- Output-Output skew less than 250ps

- Low Additive Phase Jitter of 60fs RMS

- 2.5V to 3.3V, ±10% operation

- 1.8V ± 10% operation up to 67MHz

- Operating temperature range from -40°C to 85°C

- Available in 16-Pin QFN GREEN/RoHS package

#### **DESCRIPTION**

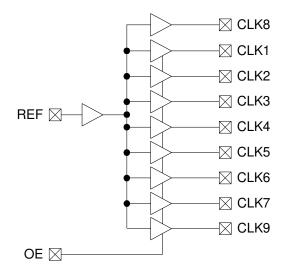

The PL133-97 is an advanced fanout buffer design for high performance, low-power, small form factor applications. The PL133-97 accepts a reference clock input from DC to 150MHz and provides 6 outputs of the same frequency.

The PL133-97 is offered in a QFN-16L 3x3mm package and it offers the best phase noise, additive jitter performance, and lowest power consumption of any comparable IC.

The PL133-97 outputs can be disabled to a high impedance (tri-state) by pulling low the OE pin. When the OE pin is high, the outputs are enabled and follow the REF input signal. When the OE pin is left open, a pull-up resistor on the chip will default the OE pin to logic 1 so the outputs are enabled.

CLK8 is a free running output that remains enabled when the OE pin is pulled low.

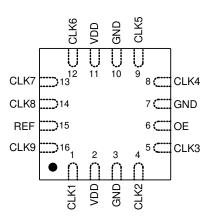

#### **BLOCK DIAGRAM AND PACKAGE PINOUT**

QFN-16L

## **PIN DESCRIPTIONS**

| Name | QFN-16L  | Туре | Description                                                    |

|------|----------|------|----------------------------------------------------------------|

| REF  | 15       | I    | Input reference frequency.                                     |

| CLK1 | 1        | 0    | Buffered clock output                                          |

| CLK2 | 4        | 0    | Buffered clock output                                          |

| CLK3 | 5        | 0    | Buffered clock output                                          |

| CLK4 | 8        | 0    | Buffered clock output                                          |

| CLK5 | 9        | 0    | Buffered clock output                                          |

| CLK6 | 12       | 0    | Buffered clock output                                          |

| CLK7 | 13       | 0    | Buffered clock output                                          |

| CLK8 | 14       | 0    | Buffered clock output, free running, does not disable with OE. |

| CLK9 | 16       | 0    | Buffered clock output                                          |

| VDD  | 2, 11    | Р    | VDD connection                                                 |

| GND  | 3, 7, 10 | Р    | GND connection                                                 |

| OE   | 6        | I    | Output Enable Control Input with 130KΩ Pull-Up                 |

| ePad | -        | -    | Center Pad for Thermal Relief. Connect to GND.                 |

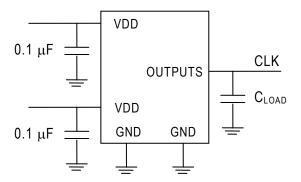

#### LAYOUT RECOMMENDATIONS

The following guidelines are to assist you with a performance optimized PCB design:

# Signal Integrity and Termination Considerations

- Keep traces short!

- Trace = Inductor. With a capacitive load this equals ringing!

- Long trace = Transmission Line. Without proper termination this will cause reflections (looks like ringing).

- Design long traces (> 1 inch) as "striplines" or "microstrips" with defined impedance.

- Match trace at one side to avoid reflections bouncing back and forth.

# Decoupling and Power Supply Considerations

- Place decoupling capacitors as close as possible to the VDD pin(s) to limit noise from the power supply

- Addition of a ferrite bead in series with VDD can help prevent noise from other board sources

- Value of decoupling capacitor is frequency dependant. Typical values to use are  $0.1\mu F$  for designs using frequencies < 50MHz and  $0.01\mu F$  for designs using frequencies > 50MHz.

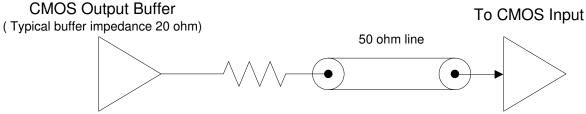

## **Typical CMOS termination**

Place Series Resistor as close as possible to CMOS output

Connect a 33 ohm series resistor at each of the output clocks to enhance the stability of the output signal

# **ABSOLUTE MAXIMUM CONDITIONS**

| Supply Voltage to Ground Potential –0.5V to 4.6V |

|--------------------------------------------------|

| DC Input VoltageV <sub>SS</sub> – 0.5V to 4.6V   |

| Storage Temperature –65°C to 150°C               |

| Junction Temperature            | 150°C |

|---------------------------------|-------|

| Static Discharge Voltage        |       |

| (per MIL-STD-883, Method 3015)> | 2000V |

## **OPERATING CONDITIONS**

| Parameter       | Description                                                                                                |      | Max. | Unit |

|-----------------|------------------------------------------------------------------------------------------------------------|------|------|------|

| $V_{DD}$        | Supply Voltage                                                                                             | 1.62 | 3.63 | V    |

| _               | Commercial Operating Temperature (ambient temperature)                                                     | 0    | 70   | °C   |

| T <sub>A</sub>  | Industrial Operating Temperature (ambient temperature)                                                     | -40  | 85   | °C   |

|                 | Load Capacitance, below 100 MHz, V <sub>DD</sub> > 2.25V                                                   | _    | 30   | pF   |

| 0               | Load Capacitance between 100 MHz and 134 MHz, $V_{DD}$ > 2.25V                                             | _    | 10   | pF   |

| CL              | Load Capacitance, above 134 MHz, V <sub>DD</sub> > 2.25V                                                   | _    | 5    | pF   |

|                 | Load Capacitance, below 67MHz, 1.62V < V <sub>DD</sub> < 2.25V                                             | _    | 15   | pF   |

| C <sub>IN</sub> | Input Capacitance                                                                                          | _    | 7    | pF   |

| REF, CLK[1:9]   | Operating Frequency, Input=Output                                                                          | DC   | 150  | MHz  |

| t <sub>PU</sub> | Power-up time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | 50   | ms   |

# **ELECTRICAL CHARACTERISTICS** (Commercial and Industrial Temperature Devices)

| Parameter       | Description               | Test Conditions                | Min. | Max. | Unit |

|-----------------|---------------------------|--------------------------------|------|------|------|

| $V_{IL}$        | Input LOW Voltage [1]     | V <sub>DD</sub> > 2.25V        | _    | 0.8  | V    |

| V <sub>IH</sub> | Input HIGH Voltage [1]    | V <sub>DD</sub> > 2.25V        | 2.0  | -    | V    |

| I <sub>IL</sub> | Input LOW Current         | V <sub>IN</sub> = 0V           | _    | 50   | μA   |

| I <sub>IH</sub> | Input HIGH Current        | $V_{IN} = V_{DD}$              | _    | 100  | μA   |

| V <sub>OL</sub> | Output LOW Voltage [2]    | I <sub>OL</sub> = 8 mA         | _    | 0.4  | V    |

| V <sub>OH</sub> | Output HIGH Voltage [2]   | I <sub>OH</sub> = -8 mA        | 2.4  | -    | V    |

| I <sub>DD</sub> | Supply Current            | 66.67MHz with unloaded outputs | _    | 32   | mA   |

| R <sub>PU</sub> | OE Pin Pull-Up Resistance |                                | 100  | _    | ΚΩ   |

# SWITCHING CHARACTERISTICS (Commercial and Industrial Temperature Devices) [3]

| Parameter      | Description                                                | Test Conditions                                    | Min. | Тур. | Max. | Unit |

|----------------|------------------------------------------------------------|----------------------------------------------------|------|------|------|------|

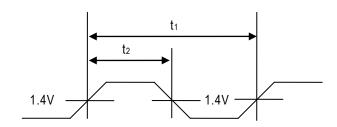

|                | Duty Ovela [2] = 40 + 44                                   | Measured at 1.4V, V <sub>DD</sub> =3.3V, Input=50% | 40   | 50   | 60   | %    |

|                | Duty Cycle [2] = t2 ÷ t1                                   | Measured at V <sub>DD</sub> /2 , Input = 50%       | 40   | 50   | 60   | %    |

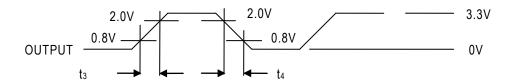

|                |                                                            | 0.8V → 2.0V , V <sub>DD</sub> =3.3V , 30pF Load    | -    | -    | 1.5  | ns   |

| $t_3$          | Rise Time [2]                                              | 10% → 90% , $V_{DD}$ =2.5V , 15pF Load             | -    | -    | 2.5  | ns   |

|                |                                                            | 10% → 90% , V <sub>DD</sub> =1.8V , 15pF Load      | _    | -    | 4.5  | ns   |

| t <sub>4</sub> | Fall Time [2]                                              | 2.0V → 0.8V , V <sub>DD</sub> =3.3V , 30pF Load    | _    | -    | 1.5  | ns   |

|                |                                                            | 90% → 10% , V <sub>DD</sub> =2.5V , 15pF Load      | _    | -    | 2.5  | ns   |

|                |                                                            | 90% → 10% , V <sub>DD</sub> =1.8V , 15pF Load      | _    | -    | 4.5  | ns   |

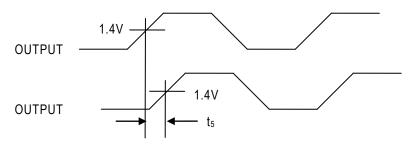

| t <sub>5</sub> | Output to Output Skew [2]                                  | All outputs equally loaded                         | _    | -    | 250  | ps   |

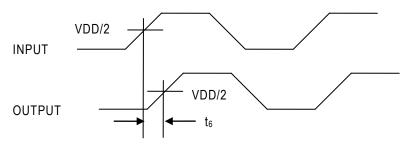

| t <sub>6</sub> | Propagation Delay, REF Rising Edge to CLKX Rising Edge [2] | Measured at V <sub>DD</sub> /2                     | 1    | 5    | 9.2  | ns   |

#### Notes:

- 1. REF input has a threshold voltage of  $V_{\text{DD}}/2$

- 2. Parameter is guaranteed by design and characterization. Not 100% tested in production.

- 3. All parameters are specified with loaded outputs.

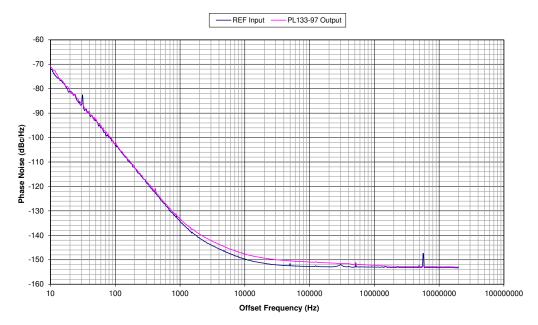

## NOISE CHARACTERISTICS (Commercial and Industrial Temperature Devices)

| Parameter | Description           | Test Conditions                                                 | Min. | Тур. | Max. | Unit |

|-----------|-----------------------|-----------------------------------------------------------------|------|------|------|------|

|           | Additive Phase Jitter | V <sub>DD</sub> =3.3V, Frequency=100MHz<br>Offset=12KHz ~ 20MHz |      | 60   |      | fs   |

PL133-97 Additive Phase Jitter: VDD=3.3V, CLK=100MHz, Integration Range 12KHz to 20MHz: 0.059ps typical.

When a buffer is used to pass a signal then the buffer will add a little bit of its own noise. The phase noise on the output of the buffer will be a little bit more than the phase noise in the input signal. To quantify the noise addition in the buffer we compare the Phase Jitter numbers from the input and the output. The difference is called "Additive Phase Jitter". The formula for the Additive Phase Jitter is as follows:

Additive Phase Jitter =  $\sqrt{\text{(Output Phase Jitter)}^2 - \text{(Input Phase Jitter)}^2}$

# **SWITCHING WAVEFORMS**

**Duty Cycle Timing**

## All Outputs Rise/Fall Time

## **Output-Output Skew**

## **Input-Output Propagation Delay**

# **TEST CIRCUIT**

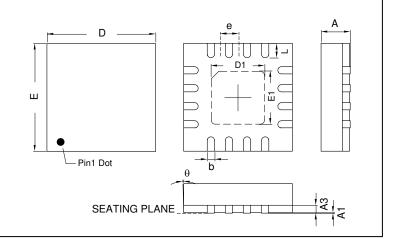

# **PACKAGE DRAWING**

# QFN-16L

| Symbol | Dimension in MM |      |  |

|--------|-----------------|------|--|

| Symbol | Min.            | Max. |  |

| Α      | 0.7             | 0.8  |  |

| A1     | 0.05            | 0.05 |  |

| A3     | 0.              | 20   |  |

| b      | 0.18            | 0.30 |  |

| D      | 3.00 BSC        |      |  |

| Е      | 3.00            | BSC  |  |

| D1     | 1               | 1.70 |  |

| E1     |                 | 1.70 |  |

| Ĺ      | 0.30            | 0.50 |  |

| е      | 0.50 BSC        |      |  |

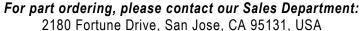

#### ORDERING INFORMATION

Tel: (408) 944-0800 Fax: (408) 474-1000

#### **PART NUMBER**

The order number for this device is a combination of the following: Part number. Package type and Operating temperature range

| Part/Order Number         | Marking            | Package Option             |  |  |  |

|---------------------------|--------------------|----------------------------|--|--|--|

| Green (Lead-Free) Package |                    |                            |  |  |  |

| PL133-97QC-R              | P133<br>97<br>LLL  | 16-Pin QFN (Tape and Reel) |  |  |  |

| PL133-97QI-R              | P133<br>97I<br>LLL | 16-Pin QFN (Tape and Reel) |  |  |  |

\*Note: LLL designates lot number

# MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.