Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- Two differential 2.5V/3.3V LVPECL output pairs.

- Output Frequency: ≤ 1 GHz.

- Translates any standard single-ended or differential input format to LVPECL output. It can accept the following standard input formats and more:

- o LVPECL, LVCMOS, LVDS, HCSL, SSTL, LVHSTL, CML.

- Output Skew: 25ps (typ.).

- Part-to-part skew: 140ps (typ.).

- Propagation delay: 1.5ns (typ.).

- Additive Jitter: <100 fs (typ.).

- Operating Supply Voltage: 2.375V ~ 3.63V.

- Operating temperature range from -40°C to 85°C.

- Package availability: SOP-8L and TSSOP-8L.

#### **DESCRIPTION**

The PL138-28 is a high performance low-cost 1: 2 outputs Differential PECL fanout buffer.

The family of Differential LVPECL buffers are designed to operate from a single power supply of  $2.5V\pm5\%$  or  $3.3V\pm10\%$ . The differential input pair is designed to accept most standard input signal levels, using an appropriate resistor bias network, and produce a high quality set of outputs with the lowest possible skew on the outputs, which is guaranteed for part-to-part or lot-to lot skew.

Designed to fit in a small form-factor package, PL138 family offers up to 1GHz of output operation with very low-power consumption, and lowest additive jitter of any comparable device. The Output Enable feature, when activated, allows the IC to consume less than  $10\mu A$  of current.

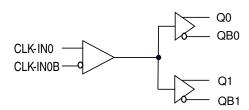

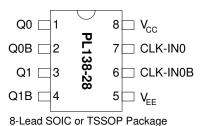

#### **BLOCK DIAGRAM**

#### **PIN DESCRIPTIONS**

| Name            | Package Pin #<br>SOIC-8L / TSSOP-8L | Туре | Description                                           |

|-----------------|-------------------------------------|------|-------------------------------------------------------|

| Q0 ~ Q1         | 1, 3                                | 0    | LVPECL True output                                    |

| QB0 ~ QB1       | 2, 4                                | 0    | LVPECL Complementary output                           |

| V <sub>EE</sub> | 5                                   | Р    | Power Supply pin connection                           |

| CLK-IN0B        | 6                                   | I    | Complementary part of differential clock input signal |

| CLK-IN0         | 7                                   | I    | True part of differential clock input signal          |

| Vcc             | 8                                   | Р    | Power Supply pin connection                           |

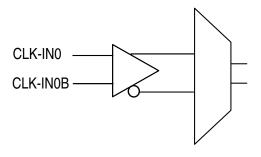

### **INPUT LOGIC BLOCK DIAGRAM**

#### **ELECTRICAL SPECIFICATIONS**

#### **Absolute Maximum Ratings**

| PARAMETERS                        | SYMBOL         | MIN. | MAX.                 | UNITS |

|-----------------------------------|----------------|------|----------------------|-------|

| Supply Voltage                    | $V_{DD}$       |      | 4.6                  | V     |

| Input Voltage, dc                 | Vı             | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                | Vo             | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature               | Ts             | -65  | 150                  | °C    |

| Ambient Operating Temperature*    | T <sub>A</sub> | -40  | 85                   | °C    |

| Junction Temperature              | TJ             |      | 110                  | °C    |

| Lead Temperature (soldering, 10s) |                |      | 260                  | °C    |

| ESD Protection, Human Body Model  | 2              |      |                      | kV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

## DC CHARACTERISTICS, VCC = 3.3V; VEE = 0V

| Dovometer                       | Parameter     |      | Symbol -40°C |       | 25°C  |       |       | 80°C  |       |       | Units |       |

|---------------------------------|---------------|------|--------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Parameter                       |               |      | Min          | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Units |

| Output High Vo                  | oltage*       | Vон  | 2.215        | 2.320 | 2.420 | 2.275 | 2.350 | 2.420 | 2.275 | 2.35  | 2.420 | V     |

| Output Low Vo                   | Itage*        | Vol  | 1.470        | 1.610 | 1.745 | 1.490 | 1.585 | 1.680 | 1.490 | 1.585 | 1.680 | V     |

| Input High Voltag               | ge            | VIH  | 2.075        |       | 2.420 | 2.135 |       | 2.420 | 2.135 |       | 2.420 | V     |

| Input Low Volta                 | age           | VIL  | 1.470        |       | 1.890 | 1.490 |       | 1.825 | 1.490 |       | 1.825 | V     |

| Peak-to-Peak I                  | nput Voltage  | VPP  | 150          | 800   | 1200  | 150   | 800   | 1200  | 150   | 800   | 1200  | V     |

| Input High Voltage<br>Range † # | e Common Mode | VCMR | 1.2          |       | 3.3   | 1.2   |       | 3.3   | 1.2   |       | 3.3   | V     |

| Input High<br>Current           | CLK-IN0,      | Іін  |              |       | 75    |       |       | 75    |       |       | 75    | μΑ    |

| Input Low<br>Current            | CLK-IN1       | lıL  | -75          |       |       | -75   |       |       | -75   |       |       | μΑ    |

Input and output parameters vary 1:1 with VCC VEE can vary +0.925V to -0.5V.

†† For single-ended applications, the maximum input voltage for CLK-INx, CLK-INxB is V<sub>CC</sub> + 0.3V

<sup>\*</sup> Note: Operating Temperature is guaranteed by design for all parts (COMMERCIAL and INDUSTRIAL), but tested for COMMERCIAL grade only.

<sup>\*</sup> Outputs terminated with  $50\Omega$  to VCCO – 2V.

<sup>\*\*</sup> Single-ended input operation is limited. VCC≥3V in LVPECL mode.

<sup>†</sup> Common mode voltage is defined as VIH

### DC CHARACTERISTICS, VCC = 2.5V; VEE = 0V

| Dozomotor                                |               | Symbol | -40°C |       | 25°C  |       |       | 80°C  |       |       | Units |       |

|------------------------------------------|---------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Parameter                                | Parameter     |        | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Units |

| Output High Vo                           | oltage*       | Vон    | 1.415 | 1.520 | 1.620 | 1.475 | 1.550 | 1.620 | 1.475 | 1.55  | 1.620 | V     |

| Output Low Vo                            | ltage*        | Vol    | 0.670 | 0.810 | 0.945 | 0.690 | 0.785 | 0.880 | 0.690 | 0.785 | 0.880 | V     |

| Input High Voltag                        | ge            | VIH    | 1.275 |       | 1.620 | 1.335 |       | 1.620 | 1.335 |       | 1.620 | V     |

| Input Low Volta                          | age           | VIL    | 0.670 |       | 1.090 | 0.690 |       | 1.025 | 0.690 |       | 1.025 | V     |

| Peak-to-Peak I                           | nput Voltage  | VPP    | 150   | 800   | 1200  | 150   | 800   | 1200  | 150   | 800   | 1200  | V     |

| Input High Voltage<br>Range <sup>†</sup> | e Common Mode | VCMR   | 1.2   |       | 2.5   | 1.2   |       | 2.5   | 1.2   |       | 2.5   | V     |

| Input High<br>Current                    | CLK-IN0,      | Іін    |       |       | 60    |       |       | 60    |       |       | 60    | μΑ    |

| Input Low<br>Current                     | CLK-IN1       | lıL    | -60   |       |       | -60   |       |       | -60   |       |       | μΑ    |

Input and output parameters vary 1:1 with VCC VEE can vary +0.925V to -0.5V.

#### **AC Electrical Characteristics**

$V_{CC} = -3.8V$  to -2.375V or,  $V_{CC} = 2.375V$  to 3.8V;  $V_{EE} = 0V$ ,  $T_A = -40^{\circ}C$  to 85°C

| Parameter                                                     |            | Cymbol                          | -40°C |      | 25°C |     | 80°C |     |     | Units |     |        |

|---------------------------------------------------------------|------------|---------------------------------|-------|------|------|-----|------|-----|-----|-------|-----|--------|

| Parameter                                                     |            | Symbol                          | Min   | Тур  | Max  | Min | Тур  | Max | Min | Тур   | Max | Ullits |

| Output Frequency                                              |            | $f_{MAX}$                       |       |      | 700  |     |      | 700 |     |       | 700 | MHz    |

| Propagation Delay*                                            |            | $t_{PD}$                        | 600   | 680  | 750  | 650 | 725  | 790 | 690 | 790   | 890 | ps     |

| Output Skew ** †                                              |            | tsk(o)                          |       | 25   | 37   |     | 25   | 37  |     | 25    | 37  | ps     |

| Part-to-Part Skew *** †                                       |            | tsk(pp)                         |       | 85   | 225  |     | 85   | 225 |     | 85    | 225 | ps     |

| Buffer Additive Phase Jitter,<br>to Additive Phase Jitter Sec | ,          | t <sub>APJ</sub>                |       | 0.10 |      |     | 0.10 |     |     | 0.10  |     | ps     |

| Output Rise/Fall Time                                         | 20% to 80% | t <sub>R</sub> / t <sub>F</sub> | 200   |      | 700  | 200 |      | 700 | 200 |       | 700 | ps     |

All parameters are measured at  $f \le 1000MHz$ , unless otherwise noted.

<sup>\*</sup> Outputs terminated with  $50\Omega$  to VCCO – 2V.

<sup>\*\*</sup> Common mode voltage is defined as VIH

$<sup>\</sup>dagger$  For single-ended applications, the maximum input voltage for CLK-INx, CLK-INxB is  $V_{CC} + 0.3V$

<sup>\*</sup> Measured from the differential input crossing point to the differential output crossing point.

<sup>\*\*</sup> Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential cross points.

<sup>\*\*\*</sup> Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

<sup>†</sup>This parameter is defined in accordance with JEDEC Standard 65.

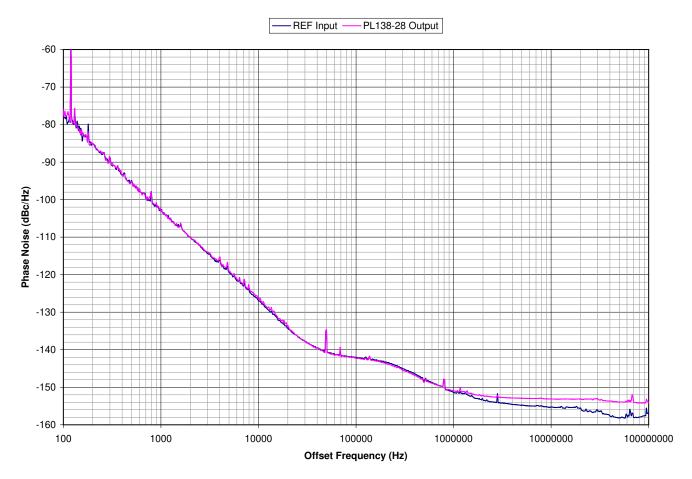

### NOISE CHARACTERISTICS (Commercial and Industrial Temperature Devices)

| Parameter        | Description           | Test Conditions                                                    | Min. | Тур. | Max. | Unit |

|------------------|-----------------------|--------------------------------------------------------------------|------|------|------|------|

| t <sub>APJ</sub> | Additive Phase Jitter | V <sub>DD</sub> =3.3V, Frequency=622.08MHz<br>Offset=12KHz ~ 20MHz |      | 21   |      | fs   |

When a buffer is used to pass a signal then the buffer will add a little bit of its own noise. The phase noise on the output of the buffer will be a little bit more than the phase noise in the input signal. To quantify the noise addition in the buffer we compare the Phase Jitter numbers from the input and the output. The difference is called "Additive Phase Jitter". The formula for the Additive Phase Jitter is as follows:

Additive Phase Jitter =  $\sqrt{\text{(Output Phase Jitter)}^2 - \text{(Input Phase Jitter)}^2}$

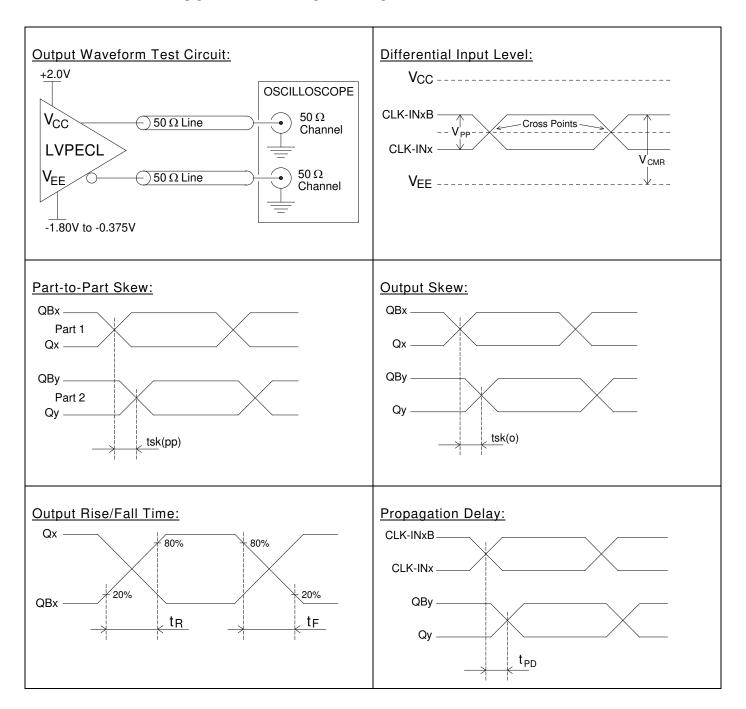

#### PARAMETER MEASUREMENT INFORMATION

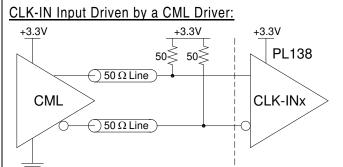

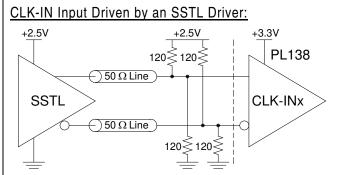

#### **APPLICATION INFORMATION**

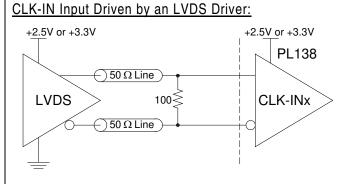

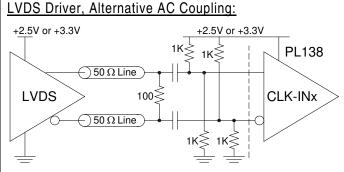

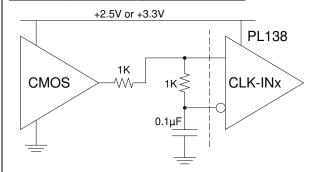

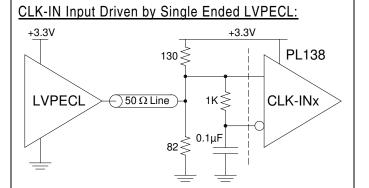

The following circuits show different configurations for different input logic type signals. For good signal integrity at the PL138 input, the signals need to be properly terminated according to the logic type requirements. The signals need to be presented at the PL138 input according to  $V_{CMB}$ ,  $V_{PP}$  and other input requirements.

###

This circuit is for compatibility only. AC coupling is not really required for LVDS. The  $V_{\text{CMR}}$  range of the PL138 reaches low enough that LVDS signals can be connected directly to the PL138 input like in the circuit to the left.

### CLK-IN Input Driven by a CMOS Driver:

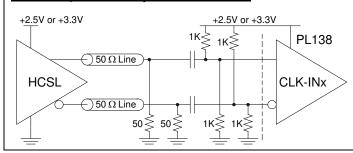

#### CLK-IN Input Driven by an HCSL Driver:

HCSL presents its signals very close to the ground rail, below the  $V_{\text{CMR}}$  range, so the HCSL signals can not be connected to the PL138 input directly. AC coupling is required for HCSL signals on the PL138 input.

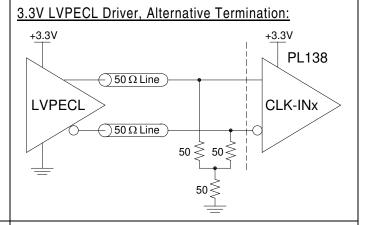

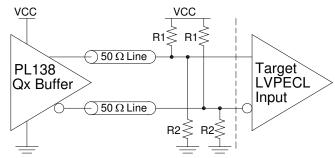

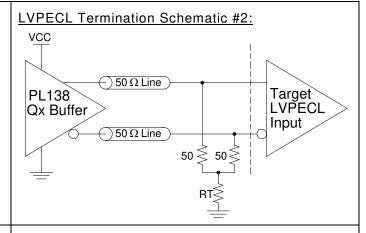

#### TERMINATION FOR LVPECL OUTPUTS

The required termination for LVPECL is  $50\Omega$  to a V<sub>CC</sub>-2V DC voltage level. Below are two schematics to implement this termination.

### LVPECL Termination Schematic #1:

VCC=3.3V, Ideal values: R1=127 $\Omega$  , R2=82.5 $\Omega$  Commercial values (E24): R1=130 $\Omega$  , R2=82 $\Omega$

VCC=2.5V, Ideal values: R1=250 $\Omega$  , R2=62.5 $\Omega$

Commercial values (E24): R1=240 $\!\Omega$  , R2=62 $\!\Omega$

Schematic #2 is an alternative simplified termination.

VCC=3.3V, Ideal value: RT=48.7 $\Omega$ Commercial value: RT=50 $\Omega$  (E24: 51 $\Omega$ ) VCC=2.5V, Ideal value: RT=18.7 $\Omega$

Commercial value: RT=18 $\Omega$

#### **POWER CONSIDERATIONS**

Driving LVPECL outputs requires an amount of power that can warm up the chip significantly.

The general requirement for the chip is that the junction temperature should not exceed +110°C.

The power consumption can be divided into two parts:

- 1) Core power dissipation

- 2) Output buffers power dissipation

#### **CORE POWER DISSIPATION**

The chip core power is equal to VCC×IEE. With a worst case VCC and IEE the power dissipation in the core is 3.63V×45mA=163mW.

#### **OUTPUT BUFFER POWER DISSIPATION**

The output buffers are not exposed to the full VCC-VEE voltage. On the differential output, one line is at logic 1 with a small voltage across the buffer and a large output current. The other line is at logic 0 with a larger voltage across the buffer and a smaller output current. The power dissipation per output buffer is 32mW. Only buffers that are loaded will have power dissipation. With both buffers loaded the worst case output buffer power dissipation will be 64mW.

Total Chip Power Dissipation, worst case, is 163mW + 64mW = 227mW.

#### **JUNCTION TEMPERATURE**

How much the chip is warmed up from the power dissipation depends upon the thermal resistance from the chip to the environment, also known as "junction to ambient". The thermal resistance depends upon the type of package, how the package is assembled to the PCB and if there is additional air flow for improved cooling. For the LQFP package with use of the Thermal Relief pad, the thermal resistance is as follows:

| JEDEC Standard Multi Layer PCB | Air Flow Velocity in Linear Feet per Minute |                                        |                                       |  |  |

|--------------------------------|---------------------------------------------|----------------------------------------|---------------------------------------|--|--|

|                                | 0                                           | 200                                    | 500                                   |  |  |

| SOIC 8-pin Package             | $\theta_{JA} = 97^{\circ} \text{C/W}$       | $\theta_{JA} = 85^{\circ} \text{C/W}$  | $\theta_{JA} = 77^{\circ} \text{C/W}$ |  |  |

| TSSOP 8-pin Package            | $\theta_{JA} = 120^{\circ} \text{C/W}$      | $\theta_{JA} = 105^{\circ} \text{C/W}$ | $\theta_{JA} = 95^{\circ} \text{C/W}$ |  |  |

#### SOIC 8-pin:

The temperature of the chip (junction) will be higher than the environment (ambient) with an amount equal to  $\theta_{JA} \times Power$ . For an ambient temperature of +85°C, all outputs loaded and no air flow, the junction temperature  $T_J = 85^{\circ}C + 97 \times 0.227 = 107^{\circ}C$ .

#### TSSOP 8-pin:

For an ambient temperature of +85°C, all outputs loaded and 200LFM air flow, the junction temperature  $T_J = 85^{\circ}C + 105 \times 0.227 = 109^{\circ}C$ . It is recommended to use at least 200LFM air flow to prevent the junction temperature from increasing above +110°C.

For use up to  $+80^{\circ}$ C or lower no air flow is needed:  $T_J = 80^{\circ}$ C+ $120 \times 0.227 = 107^{\circ}$ C.

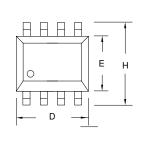

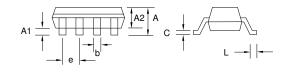

## PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

## 8 Pin (dimensions in mm)

| Symbol   | SC   | OIC  | TSSOP |      |  |

|----------|------|------|-------|------|--|

| Syllibol | Min. | Max. | Min.  | Max. |  |

| Α        | 1.35 | 1.75 | -     | 1.20 |  |

| A1       | 0.10 | 0.25 | 0.05  | 0.15 |  |

| A2       | 1.25 | 1.50 | ı     | 1.05 |  |

| В        | 0.33 | 0.53 | 0.19  | 0.30 |  |

| С        | 0.19 | 0.27 | 0.09  | 0.20 |  |

| D        | 4.80 | 5.00 | 2.90  | 3.10 |  |

| Е        | 3.80 | 4.00 | 4.30  | 4.50 |  |

| Н        | 5.80 | 6.20 | 6.20  | 6.60 |  |

| L        | 0.40 | 0.89 | 0.45  | 0.75 |  |

| е        | 1.27 | BSC  | 0.65  | BSC  |  |

### ORDERING INFORMATION (GREEN PACKAGE)

For part ordering, please contact our Sales Department: 2180 Fortune Drive, San Jose, CA 95131, USA Tel: (408) 944-0800 Fax: (408) 474-1000

#### **PART NUMBER**

The order number for this device is a combination of the following: Part number, Package type and Operating temperature range

Part Number — R=Tape and Reel

Package Type S=SOP-8 C= Commercial (0°C to +70°C)

O=TSSOP-8 I= Industrial (-40°C to +85°C)

PL138-28 X X - R

| Part/Order Number | Marking                | Package Option              |

|-------------------|------------------------|-----------------------------|

| PL138-28SC-R      | P138-28<br>SC<br>LLLLL | 8-Pin SOP (Tape and Reel)   |

| PL138-28OC-R      | P138-28<br>OC<br>LLLLL | 8-Pin TSSOP (Tape and Reel) |

\*Note: LLLLL designates lot number

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.