# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### PL565-68 VCXO

#### **PRODUCT DESCRIPTION**

The Analog Frequency Multiplier (AFM) is the industry's first 'Balanced Oscillator' utilizing analog multiplication of the fundamental frequency (at quadruple frequency), combined with an attenuation of the fundamental of the reference crystal, without the use of a phase-locked loop (PLL), in CMOS technology.

Micrel's world's best performing AFM products can achieve up to 800 MHz output frequency with little jitter or phase noise deterioration. In addition, the low frequency input crystal requirement makes the AFM the most affordable high-performance timingsource in the market.

PL565-68 product utilizes low-power CMOS technology and is housed in Green / RoHS compliant 16-pin TSSOP, and 16-pin 3x3 QFN packages.

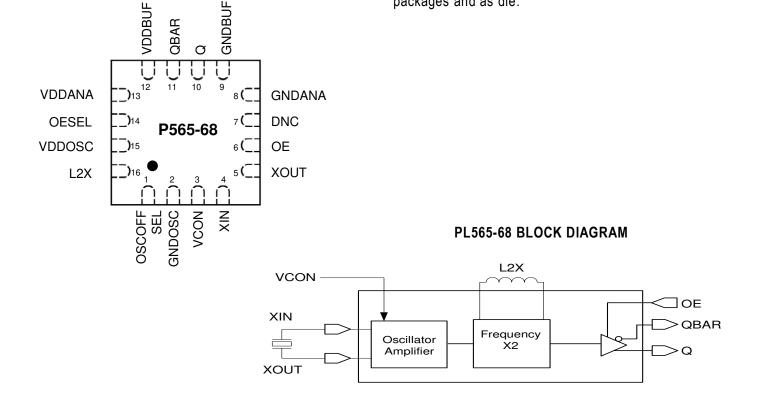

#### **QFN PACKAGE PIN-OUT**

#### FEATURES

- Non-PLL frequency multiplication by 2.

- Input frequency from 62.5-160 MHz

- Output frequency

- o PL565-68: 125-320MHz

- Low phase noise and jitter (equivalent to fundamental crystal at the output frequency)

- Ultra-low jitter

RMS phase jitter < 100 fs (12kHz-20MHz)</li>

RMS random period jitter < 2 ps</li>

- Low phase noise

- $_{\odot}$  -142 dBc/Hz @100kHz offset from the carrier  $_{\odot}$  -155 dBc/Hz @10MHz offset from the carrier

- High linearity pull range (typ. 5%)

- VCXO, set pullability ±100ppm ~ ±200ppm

- Low input frequency eliminates the need for expensive crystals

- Differential output levels: LVPECL

- Single 3.3V, ±10% power supply

- Optional industrial temperature range (-40°C to +85°C)

- Available in 16-pin Green/RoHS compliant 3x3 QFN packages and as die.

## PL565-68 VCXO

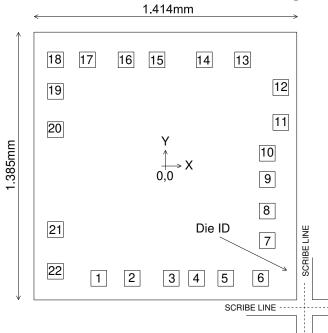

| Chip size, active area       | 1.414mm x 1.385mm    |

|------------------------------|----------------------|

| Chip thickness               | 200µm ± 20µm         |

| PAD size                     | 80µm x 80µm          |

| Scribe Line Dimension        | X = 80µm<br>Y = 80µm |

| Chip Base                    | GND level            |

| <u>Die ID:</u><br>PL565-68DC | C561A BBBBBBB        |

#### PAD/PIN ASSIGNMENT AND DESCRIPTION (The X/Y coordinates indicate pad centers)

|           | Pad   | Assignm | ent*   | QFN   | _    |                              |

|-----------|-------|---------|--------|-------|------|------------------------------|

| Name      | Pad # | Χ (μm)  | Υ (μm) | Pin # | Туре | Description                  |

| GNDOSC    | 1     | -352    | -557   | -     | Р    | GND connection               |

| DNC       | 2     | -183    | -557   | 7     | Р    | Do Not Connect               |

| GNDANA    | 3     | +15     | -557   |       | Р    | GND connection               |

| GNDSHD    | 4     | +144    | -557   | 8     | Р    | GND connection               |

| GNDSHD    | 5     | +292    | -557   |       | Р    | GND connection               |

| GNDBUF    | 6     | +469    | -557   | 9     | Р    | GND connection               |

| GNDBUF    | 7     | +502    | -365   | 9     | Р    | GND connection               |

| PECL      | 8     | +502    | -215   | 10    | 0    | LVPECL output                |

| PECLB     | 9     | +502    | -54    | 11    | 0    | LVPECL complementary output  |

| VDDBUF    | 10    | +502    | +79    | 12    | Р    | VDD connection               |

| VDDBUF    | 11    | +571    | +236   | 12    | Р    | VDD connection               |

| VDDANA    | 12    | +571    | +413   | 13    | Р    | VDD connection               |

| DNC       | 13    | +377    | +554   | -     |      | Do Not Connect               |

| OESEL     | 14    | +183    | +554   | 14    | I    | OE style selection pin       |

| VDDOSC    | 15    | -57     | +554   | 15    | Р    | VDD connection               |

| L2X       | 16    | -214    | +554   | 16    | I    | External inductor connection |

| OSCOFFSEL | 17    | -410    | +554   | 1     | I    | Oscillator Off selection pin |

| GNDOSC    | 18    | -572    | +554   | 2     | Р    | GND connection               |

| VCON      | 19    | -572    | +394   | 3     | I    | Control voltage input        |

| XIN       | 20    | -572    | +199   | 4     | I    | Crystal Input pad            |

| XOUT      | 21    | -572    | -309   | 5     | 0    | Crystal Output pad           |

| OE        | 22    | -572    | -521   | 6     | I    | Output Enable input          |

\* Note: Pad coordinates referenced to the center of the die.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1(408) 944-0800 • fax +1(408) 474-1000 • www.micrel.com Rev 12/08/11 Page 2

#### **DIE SPECIFICATIONS**

## PL565-68 VCXO

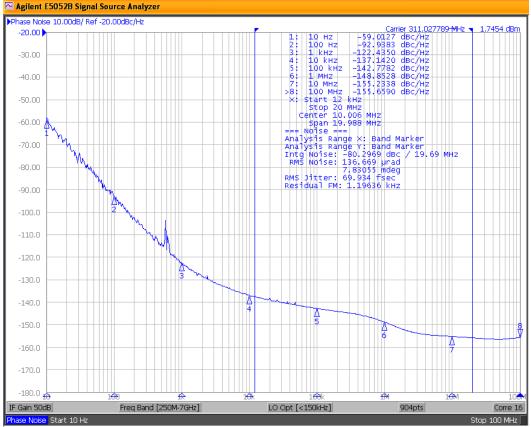

AFM Phase Noise at 311.04MHz, using 155.52MHz crystal

The analog frequency multiplication preserves the low phase noise of the quartz crystal oscillator while keeping unwanted sub harmonics from the multiplication at very low levels. Sub harmonics appear only at large distance from the carrier, far outside the loop bandwidth of a PLL that uses the AFM signal to multiply up further to a multiple GHz network clock. This means that the impact of the sub harmonics on the application is negligible.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1(408) 944-0800 • fax +1(408) 474-1000 • www.micrel.com Rev 12/08/11 Page 3

### **PL565-68 VCXO**

#### PHASE NOISE PERFORMANCE

| Part     | Input<br>Freg. | Output<br>Freg. | Phase Noi                 | se at F  | requen    | cy Offs  | et Fron   | n Carri    | er (dB   | c/Hz)     | Phase<br>Jitter          |

|----------|----------------|-----------------|---------------------------|----------|-----------|----------|-----------|------------|----------|-----------|--------------------------|

| Number   | Range<br>(MHz) | Range<br>(MHz)  | Carrier<br>Freq.<br>(MHz) | 10<br>Hz | 100<br>Hz | 1<br>kHz | 10<br>kHz | 100<br>kHz | 1<br>MHz | 10<br>MHz | 12KHz ~<br>20MHz<br>(ps) |

| PL565-68 | 62.5 - 160     | 125 - 320       | 311.04                    | -59      | -93       | -122     | -137      | -143       | -149     | -155      | 0.07                     |

Phase noise was measured using Agilent E5052B.

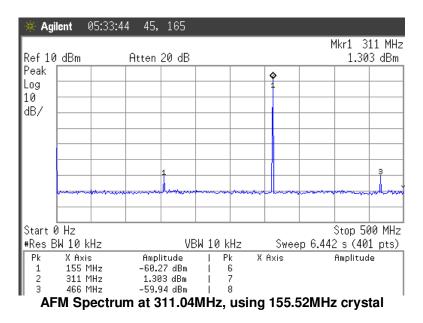

#### SUB-HARMONIC PERFORMANCE

| Part     | Input<br>Frequency | Output<br>Frequency | Spectral Specification    | ons / Sub-harmonic Con | tent (dBc), Freq. (MHz) |

|----------|--------------------|---------------------|---------------------------|------------------------|-------------------------|

| Number   | (MHz)              | (MHz)               | Carrier Frequency<br>(Fc) | @ -50%<br>(Fc)         | @ +50%<br>(Fc)          |

| PL565-68 | 155.52             | 311.04              | 311.04                    | -60                    | -60                     |

Note: Spectral specifications were obtained using Agilent E7401A

#### AFM MULTIPLYING TECHNIQUE

The analog frequency multiplication is achieved through a "squaring" operation.

The math is as follows:  $SIN^{2}(x) = 0.5 - 0.5 \times COS(2x)$

A very important property of this processing is that the result is a pure sine wave with double frequency. In theory there are no sub harmonics but in practice the squaring operation is not perfect and a low level of sub harmonics is present anyway. The key is that the resulting sub harmonics are very low and simple filtering with only one inductor per squarer is adequate for excellent performance.

### PL565-68 VCXO

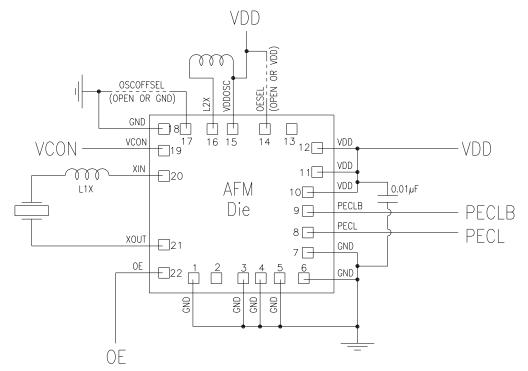

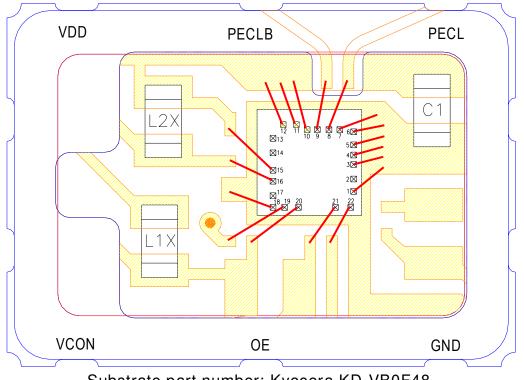

#### **AFM DIE APPLICATION CIRCUIT**

A 7x5mm ceramic substrate was designed to assemble and operate the AFM die at optimum performance:

Substrate part number: Kyocera KD-VB0F48

Please see PL565-68DC Tuning Assistant document for passive component values.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1(408) 944-0800 • fax +1(408) 474-1000 • www.micrel.com Rev 12/08/11 Page 5

### PL565-68 VCXO

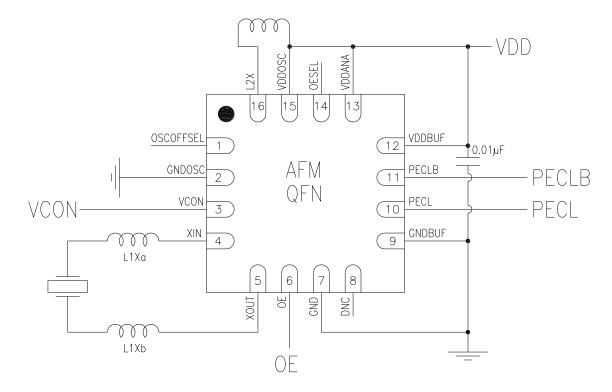

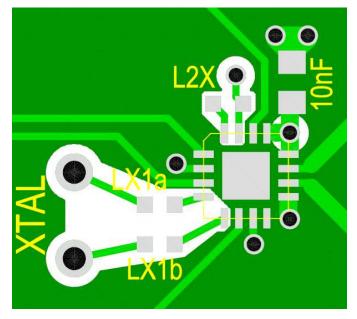

#### AFM QFN PACKAGE APPLICATION CIRCUIT

#### **RECOMMENDED PCB LAYOUT**

- Avoid ground planes underneath the crystal and inductor traces to limit parasitic capacitance.

- Add bypass capacitor close to VDDBUF pin.

- Avoid bypass capacitors near VDDOSC pins to lower cross-talk of unwanted frequencies.

- L1X(a,b) can be used to increase the VCXO pulling range. Using a ferrite core inductor limits the oscillation amplitude which can have a positive effect on phase noise.

- L2X tunes the frequency multiplier tank circuit. L2X needs to be a wire wound inductor with high Q-factor, preferably >20.

- The large center pad is the "thermal relief" pad and can be connected to ground.

### PL565-68 VCXO

#### INDUCTOR VALUE OPTIMIZATION

The required inductor values for the best performance depend on the operating frequency, and the board layout or module specifications. The listed values in this datasheet are based on the calculated parasitic values from Micrel's evaluation board design. These inductor values provide the user with a starting point to determine the optimum inductor values. Additional fine-tuning may be required to determine the optimal solution.

The inductor is recommended to be a high Q small size 0402 or 0603 SMD component, and must be placed between L2X and adjacent VDDOSC pin. Place inductor as close to the IC as possible to minimize parasitic effects and to maintain inductor Q.

To assist with the inductor value optimization, Micrel has developed AFM "Tuning Assistant" documents. You can download these documents from Micrel's web site (www.micrel.com). The documents consist of tables with recommended inductor values for certain output frequency ranges.

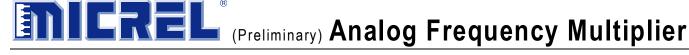

#### Figure 10: Diagram Representation of the Related System Inductance and Capacitance

#### DIE SIDE

- Cinternal at L2X = 7.625 pF

- Cpad = 1.0 pF, Bond pad and its ESD circuitry

- C11 = 0.4 pF, The following amplifier stage

#### PCB side

- LWB1 = 2 nH, (2 places), Stray inductance

- Cstray = 0.5 pF, Stray capacitance

- L2X = 2x inductor

- C2X = range (0.1 to 2.7 pF), Fine tune the tank, if used.

Work out the resonance of this network and you have a good first guess for the required inductor values for optimum performance. Non-linear behavior at large signal amplitudes can shift the tank resonance significantly, especially at the L2X side, to a lower frequency than the calculation suggests. The Tuning Assistant documents are based upon actual lab tests and are corrected for the non-linear behavior.

### PL565-68 VCXO

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| PARAMETERS                                      | SYMBOL           | MIN.    | MAX.                 | UNITS |

|-------------------------------------------------|------------------|---------|----------------------|-------|

| Supply Voltage                                  | $V_{\text{DD}}$  |         | 4.6                  | V     |

| Input Voltage, DC                               | VI               | GND-0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, DC                              | Vo               | GND-0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature                             | Ts               | -65     | 150                  | °C    |

| Ambient Operating Temperature, Industrial       | T <sub>A_I</sub> | -40     | +85                  | °C    |

| Ambient Operating Temperature, Commercial       | $T_{A_C}$        | 0       | +70                  | °C    |

| Junction Temperature                            | TJ               |         | 125                  | °C    |

| Lead Temperature (soldering, 10s)               |                  |         | 260                  | °C    |

| Input Static Discharge Voltage Protection (HBM) |                  |         | 2                    | kV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

#### **VOLTAGE CONTROL SPECIFICATION**

| PARAMETERS              | SYMBOL               | CONDITIONS                                                       | MIN. | TYP. | MAX. | UNITS |

|-------------------------|----------------------|------------------------------------------------------------------|------|------|------|-------|

| VCXO Stabilization Time | T <sub>VCXOSTB</sub> | From power valid                                                 |      |      | 10   | ms    |

| VCXO Tuning Range*      |                      | XTAL C <sub>0</sub> /C <sub>1</sub> <300                         | 200  |      |      | ppm   |

| CLK Output Pullability* |                      | VCON= 1.65V, ± 1.65V<br>XTAL C <sub>0</sub> /C <sub>1</sub> <300 | ±100 | ±120 |      | ppm   |

| Linearity               |                      |                                                                  |      | 5    | 10   | %     |

| VCON Input Impedance    |                      |                                                                  | 10   |      |      | MΩ    |

| VCON Modulation BW      |                      | 0V < VCON < 3.3V, -3dB                                           |      | 40   |      | kHz   |

\* Note: The VCXO Tuning Range and Pullability can be controlled with the value for inductor L1X. See Tuning Assistant document for a guide to chose the L1X value based upon crystal frequency and motional parameters.

# **Intervent** (Preliminary) Analog Frequency Multiplier

## PL565-68 VCXO

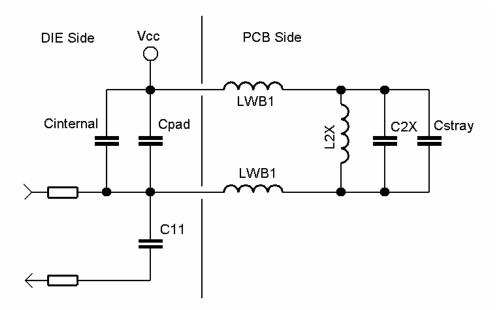

#### LVPECL ELECTRICAL CHARACTERISTICS

| PARAMETERS                     | SYMBOL          | CONDITIONS             | MIN.                   | TYP. | MAX.                   | UNITS |

|--------------------------------|-----------------|------------------------|------------------------|------|------------------------|-------|

| Supply Current, loaded outputs | I <sub>DD</sub> | Fout = 311.04MHz       |                        | 75   | 80                     | mA    |

| Operating Voltage              | V <sub>DD</sub> |                        | 2.97                   |      | 3.63                   | V     |

| Output Clock Duty Cycle        |                 | @V <sub>DD</sub> -1.3V | 45                     | 50   | 65                     | %     |

| Output High Voltage            | V <sub>OH</sub> | $R_L = 50\Omega$ to    | V <sub>DD</sub> -1.025 |      |                        | V     |

| Output Low Voltage             | V <sub>OL</sub> | $(V_{DD} - 2V)$        |                        |      | V <sub>DD</sub> -1.620 | V     |

| Clock Rise Time                | tr              | @ 20/80%               |                        | 0.25 | 0.45                   | ns    |

| Clock Fall Time                | t <sub>f</sub>  | @ 80/20%               |                        | 0.25 | 0.45                   | ns    |

## PL565-68 VCXO

#### **OE LOGIC SELECTION**

| OESEL       | OE          | Output State |

|-------------|-------------|--------------|

| 0 (Default) | 0 (Default) | Enabled      |

| 0 (Default) | 1           | Tri-state    |

| 1           | 0           | Tri-state    |

| I           | 1 (Default) | Enabled      |

0 (Default): Connect to GND or leave floating to set to "0". Internal pull-down. 1 (Default): Connect to VDD or leave floating to set to "1". Internal pull-up. 0: Connect to GND to set to "0". 1: Connect to VDD to set to "1".

#### **OSCOFFSEL LOGIC SELECTION**

| OSCOFFSEL   | Functionality description                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------|

| 0           | The crystal oscillator shuts down when the output is disabled with OE.                                         |

| 1 (Default) | Only the output will disable with OE. All other circuits, including the crystal oscillator are always running. |

1 (Default): Connect to VDD or leave floating to set to "1". Internal pull-up.

0: Connect to GND to set to "0".

## PL565-68 VCXO

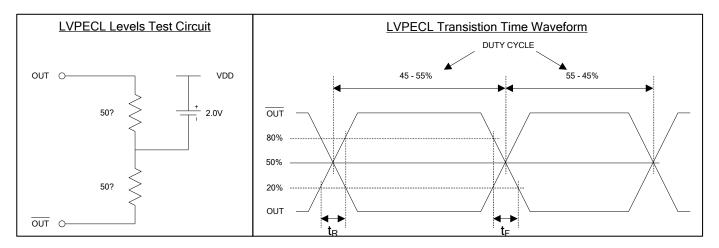

#### **PACKAGE INFORMATION**

#### QFN-16L

|        | Din   | nension (r | nm)   |

|--------|-------|------------|-------|

| Symbol | Min   | Nom        | Max   |

| А      | 0.70  | 0.75       | 0.80  |

| A1     | 0.00  | -          | 0.05  |

| A3     |       | 0.20       |       |

| b      | 0.20  | 0.25       | 0.30  |

| D      | 2.95  | 3.00       | 3.05  |

| Е      | 2.95  | 3.00       | 3.05  |

| D1     | 1.65  | 1.70       | 1.75  |

| E1     | 1.65  | 1.70       | 1.75  |

| L      | 0.250 | 0.300      | 0.350 |

| е      |       | 0.50BSC    |       |

# **Intervent** (Preliminary) Analog Frequency Multiplier

### PL565-68 VCXO

#### **ORDERING INFORMATION**

| 2180                                          | <b>dering, please contac</b> t<br>Fortune Drive, San Jos<br>el: (408) 944-0800 Fax: |                                                                         |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

|                                               |                                                                                     | <b>ER</b><br>combination of the following:<br>erating temperature range |  |

|                                               | <u>PL565-68</u> <u>X</u>                                                            | <u>x</u> x                                                              |  |

| PART NUMBER                                   |                                                                                     | NONE= TUBE<br>R= TAPE AND REEL                                          |  |

| <b>PACKAGE TYPE</b><br>Q= QFN-16L<br>D= Die   |                                                                                     | C=COMMERCIAL<br>I=INDUSTRIAL                                            |  |

| Order Number                                  | Marking                                                                             | Package Option*                                                         |  |

| PL565-68DC                                    | -                                                                                   | Waffle Pack (Die)                                                       |  |

| PL565-68QC                                    | P565                                                                                | QFN – Tape                                                              |  |

| PL565-68QC-R 68(I)<br>LLL QFN – Tape and Reel |                                                                                     |                                                                         |  |

| Marking Notes : "LLL", "LLL                   | LL" represents the produc                                                           | tion lot number                                                         |  |

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.