Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Combined E1/T1/J1 Transceiver/Framer

### **FEATURES**

- Monolithic 3.3 V device that integrates an E1/T1/J1 Framer and line driver for shorthaul and longhaul applications.

- Software selectable between T1/J1 and E1 operation on a per device basis.

- Provides fully programmable shorthaul and longhaul pulse templates and line build out.

- Meets or exceeds T1, J1, and E1 shorthaul and longhaul network access specifications, which include: ANSI T1.102, T1.403, T1.408, AT&T TR 62411, ITU-T G.703 and G.823, as well as the newer G.775 and ETSI 300-011 specifications.

- Supports B8ZS, HDB3, and AMI line codes.

- Provides receive clock recovery and line performance monitoring.

- Provides on-board binary sequence generators and detectors that can be configured with various patterns for error testing, including those conforming to ITU-T 0.151.

- Provides transmit and receive jitter attenuation.

- Provides three full-featured HDLC controllers, each with 128-byte transmit and receive FIFOs, enabling dual compliance to the V5.1 and V5.2 interface standards.

- Supports an IEEE P1149.1 JTAG test port.

- Automatically generates DS1 performance report messages to ANSI T1.231 and other specifications.

- Compatible with Mitel ST<sup>®</sup>-bus, AT&T CHI<sup>®</sup>, and MVIP PCM backplanes supporting rates of 1.544 Mbit/s, 2.048 Mbit/s, 4.096 Mbit/s and 8.192 Mbit/s.

- Provides an 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power +3.3 V CMOS technology.

- Available in an 80-pin PQFP (14 mm by 14 mm) and an 81-pin CABGA (9 mm by 9 mm) package.

- Provides a -40 °C to +85 °C industrial temperature operating range.

### RECEIVE

- Provides single-rail digital PCM and signaling outputs for 1.544 Mbit/s, 2.048 Mbit/s, 4.096 Mbit/s, or 8.192 Mbit/s backplane buses.

- Guaranteed signal recovery of up to -36 dB at 1024 kHz (E1) and 772 kHz (T1/J1) under production test conditions (VDD = 3.069 V, 25 °C) using PIC-22 gauge cable emulation.

- Frames to a G.704 E1 signal.

- Frames to a JT-G704 J1 signal.

- Frames to a DSX/DS-1 signal in D4, SF, ESF, or SLC<sup>®</sup>96 formats.

- Accommodates up to 0.4 UI peak-topeak, high frequency jitter as required by AT&T TR 62411.

- Supports line and path performance monitoring to AT&T and ANSI specifications and ITU-T recommendations.

- Detects both programmable in-band loopback activate and deactivate code sequences received in the DS1/E1 data stream.

#### **TRANSMIT**

- Supports transfer of transmitted PCM and signaling data from 1.544 Mbit/s, 2.048 Mbit/s, 4.096 Mbit/s, or 8.192 Mbit/s backplane buses.

- · Supports tristate line outputs.

- Generates DSX-1 T1 shorthaul- and T1 longhaul-compatible pulses with programmable pulse shape to AT&T and ANSI specifications and ITU-T recommendations.

- · Generates G.703 E1 pulses.

- Detects violations of the ANSI T1.403 12.5% pulse density rule over a moving 192-bit window.

- Allows insertion of in-band loopback code sequences.

- Supports transmission of the Alarm Indication Signal (AIS) or the yellow alarm signal in all formats.

- Provides a FIFO for jitter attenuation in the transmit path.

- Complies to all jitter attenuation, jitter transfer and residual jitter specifications required by AT&T TR 62411 and ETSI TBR12/13.

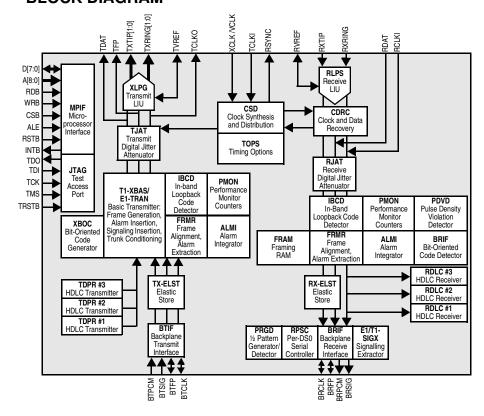

## **BLOCK DIAGRAM**

# Combined E1/T1/J1 Transceiver/Framer

### **APPLICATIONS**

- Wireless Base Transceiver Station and Digital LoopCarriers (DLCs).

- · BITS Timing Systems.

- Integrated Access Device (IAD).

- Channel and Data Service Units (CSU/DSU).

- Enterprise Routers.

- V5.1/V5.2 Interfaces.

### TYPICAL APPLICATIONS

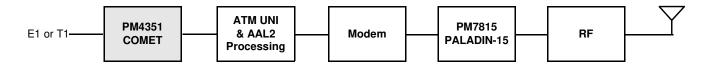

### WIRELESS BASE TRANSCEIVER STATION (BTS)

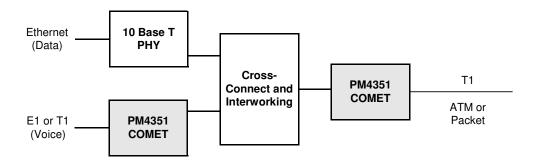

### INTEGRATED ACCESS DEVICE (IAD)

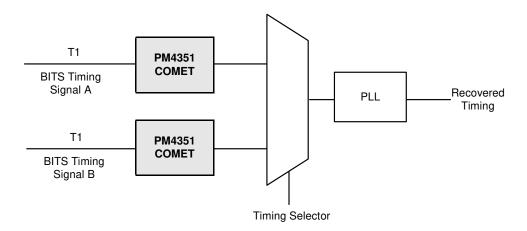

### **BITS TIMING APPLICATION**

Head Office: PMC-Sierra, Inc. 8555 Baxter Place Burnaby, B.C. V5A 4V7 Canada

Tel: 604.415.6000 Fax: 604.415.6200 To order documentation, send email to: document@pmc-sierra.com or contact the head office, Attn: Document Coordinator

All product documentation is available on our web site at: http://www.pmc-sierra.com

For corporate information, send email to: info@pmc-sierra.com

PMC-1961230 (R3) © Copyright PMC-Sierra, Inc. 2001. All rights reserved. July 2001.

SLC<sup>®</sup>96, ST, and CHI are registered trademarks of AT&T.

COMET, PALADIN-15, and PMC-Sierra are trademarks of PMC-Sierra, Inc.