Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **PM6680**

No Rsense dual step-down controller with adjustable voltages for notebook system power

#### **Features**

- 6 V to 28 V input voltage range

- Adjustable output voltages

- 5 V always voltage available deliver 100 mA peak current

- 1.237 V ± 1% reference voltage available

- Lossless current sensing using low side MOSFETs R<sub>DS(on)</sub>

- Negative current limit

- Soft-start internally fixed at 2ms

- Soft output discharge

- Latched OVP and UVP

- Selectable pulse skipping at light loads

- Selectable minimum frequency (33 kHz) in pulse skip mode

- 4 mW maximum quiescent power

- Independent power good signals

- Output voltage ripple compensation

## **Applications**

- Notebook computers

- Tablet PC or slates

- Mobile system power supply

- 3-4 cells Li+ battery powered devices

## **Description**

PM6680 is a dual step-down controller specifically designed to provide extremely high efficiency conversion, with lossless current sensing technique. The constant on-time architecture assures fast load transient response and the embedded voltage feed-forward provides nearly constant switching frequency operation. An embedded integrator control loop compensates the DC voltage error due to the output ripple. Pulse skipping technique increases efficiency at very light load. Moreover a minimum switching frequency of 33kHz is selectable to avoid audio noise issues. The PM6680 provides a selectable switching frequency, allowing three different values of switching frequencies for the two switching sections. The output voltages OUT1 and OUT2 can be adjusted from 0.9 V to 5.5 V and from 0.9 V to 3.3 V respectively.

Table 1. Device summary

| Order codes | Package                                     | Packaging     |  |

|-------------|---------------------------------------------|---------------|--|

| PM6680      | VFQFPN-32 5mm x 5mm (Exposed pad)           | Tray          |  |

| PM6680TR    | VI QI I IV-32 SIIIII X SIIIII (Exposed pad) | Tape and reel |  |

Contents PM6680

# **Contents**

| 1 | Simp  | olified application schematic                 |

|---|-------|-----------------------------------------------|

| 2 | Elect | rical data5                                   |

|   | 2.1   | Maximum rating 5                              |

|   | 2.2   | Thermal data 5                                |

| 3 | Pin s | ettings 6                                     |

|   | 3.1   | Connections                                   |

|   | 3.2   | Functions                                     |

| 4 | Elect | rical characteristics10                       |

| 5 | Туріс | cal operating characteristics13               |

| 6 | Bloc  | k diagram18                                   |

| 7 | Devi  | ce description                                |

|   | 7.1   | Constant On time PWM control                  |

|   | 7.2   | Constant on time architecture                 |

|   | 7.3   | Output ripple compensation and loop stability |

|   | 7.4   | Pulse skip mode                               |

|   | 7.5   | No-audible skip mode                          |

|   | 7.6   | Current limit                                 |

|   | 7.7   | Soft start and soft end                       |

|   | 7.8   | Gate drivers                                  |

|   | 7.9   | Reference voltage and bandgap                 |

|   | 7.10  | Internal linear regulator                     |

|   | 7.11  | Power up sequencing and operative modes       |

|   | 7.12  | Monitoring and protections                    |

|   |       | 7.12.1 Power good signals                     |

|   |       | 7.12.2 Thermal protection                     |

|   |       | 7.12.3 Overvoltage protection                 |

|   |       | 7.12.4 Undervoltage protection                |

| PM6680 | Contents |

|--------|----------|

|        |          |

|   | 7.13  | Design   | guidelines                  | . 30 |

|---|-------|----------|-----------------------------|------|

|   |       | 7.13.1   | Switching frequency         | . 30 |

|   |       | 7.13.2   | Inductor selection          | . 30 |

|   |       | 7.13.3   | Output capacitor            | . 31 |

|   |       | 7.13.4   | Input capacitors selection  | . 32 |

|   |       | 7.13.5   | Power MOSFETs               | . 33 |

|   |       | 7.13.6   | Closing the integrator loop | . 35 |

|   |       | 7.13.7   | Other parts design          | . 38 |

|   |       | 7.13.8   | Design example              | . 40 |

| 8 | Pack  | age me   | chanical data               | . 44 |

| 9 | Revis | sion his | tory                        | 46   |

List of figures PM6680

# **List of figures**

| Figure 1.  | Simplified application schematic                          |     |

|------------|-----------------------------------------------------------|-----|

| Figure 2.  | Pin connection (Through top view)                         | . 8 |

| Figure 3.  | 1.5V output efficiency vs load current                    | 15  |

| Figure 4.  | 1.05V output efficiency vs load current                   | 15  |

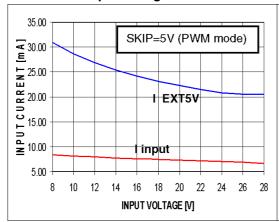

| Figure 5.  | PWM no load input battery vs input voltage                | 15  |

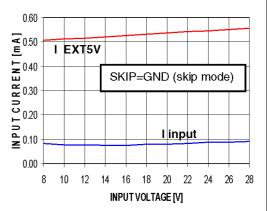

| Figure 6.  | Skip no load battery current                              | 15  |

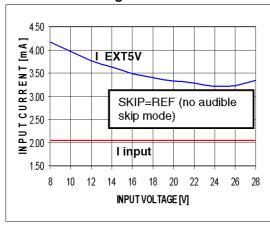

| Figure 7.  | No-audible skip no load battery current vs input voltage  | 16  |

| Figure 8.  | Stand-by mode input battery current vs input voltage      | 16  |

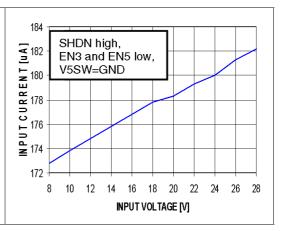

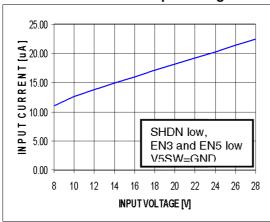

| Figure 9.  | Shutdown mode input battery current vs input voltage      | 16  |

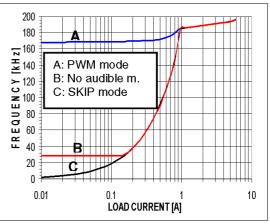

| Figure 10. | 1.5V switching frequency vs load current                  |     |

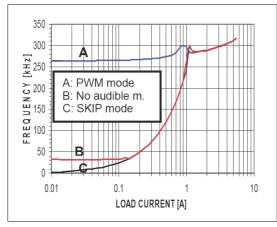

| Figure 11. | 1.05V switching frequency vs load current                 |     |

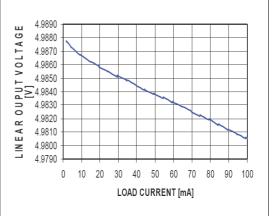

| Figure 12. | LDO5 vs output current                                    |     |

| Figure 13. | 1.5V voltage regulation vs load current                   | 17  |

| Figure 14. | 1.05V voltage regulation vs load current                  | 17  |

| Figure 15. | Voltage reference vs load current                         | 17  |

| Figure 16. | OUT1, OUT2 and LDO5 power-up                              | 17  |

| Figure 17. | 1.5V load transient                                       | 17  |

| Figure 18. | 1.05V load transient                                      |     |

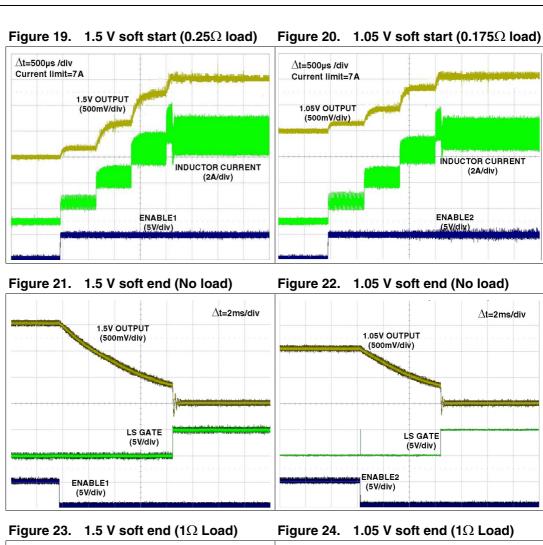

| Figure 19. | 1.5V soft start (0.25 $\Omega$ load)                      |     |

| Figure 20. | 1.05V soft start (0.175 $\Omega$ load)                    |     |

| Figure 21. | 1.5V soft end (No load)                                   |     |

| Figure 22. | 1.05V soft end (No load)                                  |     |

| Figure 23. | 1.5V soft end (1 $\Omega$ Load)                           |     |

| Figure 24. | 1.05V soft end (1 $\Omega$ Load)                          |     |

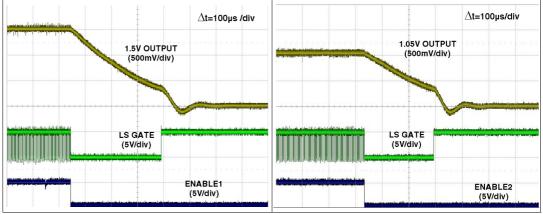

| Figure 25. | 1.5V no-audible skip mode                                 |     |

| Figure 26. | 1.05V no-audible skip mode                                |     |

| Figure 27. | Functional block diagram                                  |     |

| Figure 28. | Constant ON time PWM control                              |     |

| Figure 29. | Constant on-time block diagram                            |     |

| Figure 30. | Circuitry for output ripple compensation                  |     |

| Figure 31. | PWM and pulse skip mode inductor current                  |     |

| Figure 32. | No audible skip mode                                      |     |

| Figure 33. | RDSON sensing technique                                   |     |

| Figure 34. | Current waveforms in current limit conditions             |     |

| Figure 35. | Soft start waveforms                                      |     |

| Figure 36. | Circuitry for output ripple compensation                  |     |

| Figure 37. | Virtual ESR network                                       |     |

| Figure 38. | VIN pin filter                                            |     |

| Figure 39. | Inductor current waveforms                                |     |

| Figure 40. | Bootstrap circuit                                         |     |

| Figure 41. | Current paths, ground connection and driver traces layout |     |

| Figure 42. | Package dimensions                                        | 47  |

PM6680 List of tables

# List of tables

| Table 1.  | Device summary                                  | . 1 |

|-----------|-------------------------------------------------|-----|

| Table 2.  | Absolute maximum ratings                        | . 7 |

| Table 3.  | Thermal data                                    | . 7 |

| Table 4.  | Pin functions                                   | . 9 |

| Table 5.  | Electrical characteristics                      | 12  |

| Table 6.  | FSEL pin selection: typical switching frequency | 22  |

| Table 7.  | V5SW multifunction pin                          | 30  |

| Table 8.  | Operatives modes                                | 30  |

| Table 9.  | Protections and operatives modes                | 31  |

| Table 10. | Inductor manufacturer                           | 33  |

| Table 11. | Output capacitor manufacturer                   | 34  |

| Table 12. | Input capacitor manufacturer                    | 34  |

| Table 13. | High side MOSFET manufacturer                   | 35  |

| Table 14. | Low side MOSFET manufacturer                    | 36  |

| Table 15. | Dual MOSFET manufacturer                        | 36  |

| Table 16. | Shottky diode manufacturer                      | 36  |

| Table 17. | VFQFPN 5x5x1.0 32L Pitch 0.50                   |     |

| Table 18. | Exposed pad variations                          | 46  |

| Table 19. | Document revision history                       | 48  |

**577**

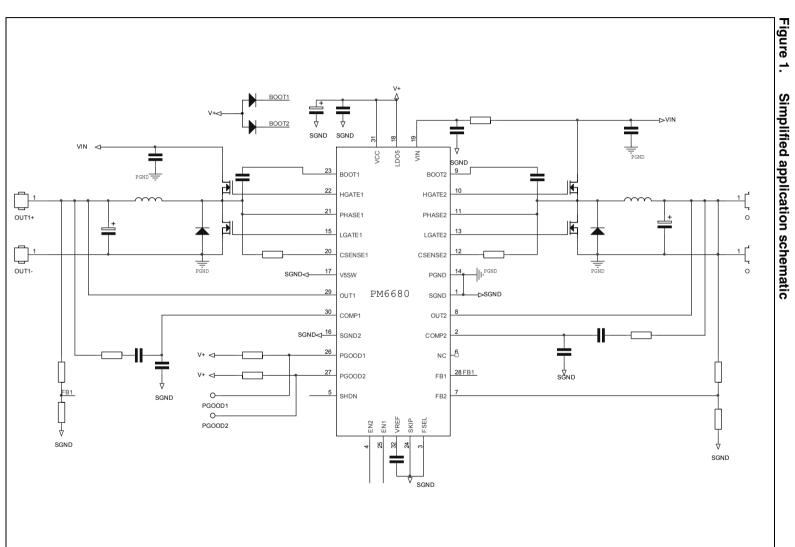

# Simplified application schematic

PM6680 Electrical data

# 2 Electrical data

# 2.1 Maximum rating

Table 2. Absolute maximum ratings

| Parameter                                                                      | Value      | Unit                             |    |

|--------------------------------------------------------------------------------|------------|----------------------------------|----|

| V5SW, LDO5 to PGND                                                             | -0.3 to 6  | ٧                                |    |

| VIN to PGND                                                                    | -0.3 to 36 | ٧                                |    |

| HGATEx and BOOTx, to PHASEx                                                    |            | -0.3 to 6                        | ٧  |

| PHASEx to PGND                                                                 |            | -0.6 <sup>(1)</sup> to36         | ٧  |

| CSENSEx , to PGND                                                              |            | -0.6 to 42                       | ٧  |

| CSENSEx to BOOTx                                                               | -6 to 0.3  | ٧                                |    |

| LGATEx to PGND                                                                 |            | -0.3 <sup>(2)</sup> to LDO5 +0.3 | ٧  |

| FBx, COMPx, SKIP, , FSEL, VREF to SGND1, SGND2                                 | 2          | -0.3 to Vcc +0.3                 | ٧  |

| PGND to SGND1,SGND2                                                            |            | -0.3 to 0.3                      | ٧  |

| SHDN,PGOODx, OUTx, VCC, ENx to SGND1,SGND                                      | )2         | -0.3 to 6                        | ٧  |

| Power dissipation at T <sub>A</sub> = 25°C                                     | 2.8        | W                                |    |

| Maximum withstanding voltage range test condition: VIN                         |            | ±1000                            | ., |

| CDF-AEC-Q100-002- "Human Body Model" acceptance criteria: "Normal Performance" | Other pins | ±2000                            | V  |

<sup>1.</sup> PHASE to PGND up to -2.5 V for t<10 ns

## 2.2 Thermal data

Table 3. Thermal data

| Symbol                                                   | Parameter                                           | Value     | Unit |

|----------------------------------------------------------|-----------------------------------------------------|-----------|------|

| R <sub>thJA</sub> Thermal resistance junction to ambient |                                                     | 35        | °C/W |

| T <sub>STG</sub>                                         | T <sub>STG</sub> Storage temperature range          |           | °C   |

| T <sub>J</sub>                                           | T <sub>J</sub> Junction operating temperature range |           | °C   |

| T <sub>A</sub> Operating ambient temperature range       |                                                     | -40 to 85 | °C   |

<sup>2.</sup> LGATEx to PGND up to -1 V for t<40 ns

Pin settings PM6680

# 3 Pin settings

## 3.1 Connections

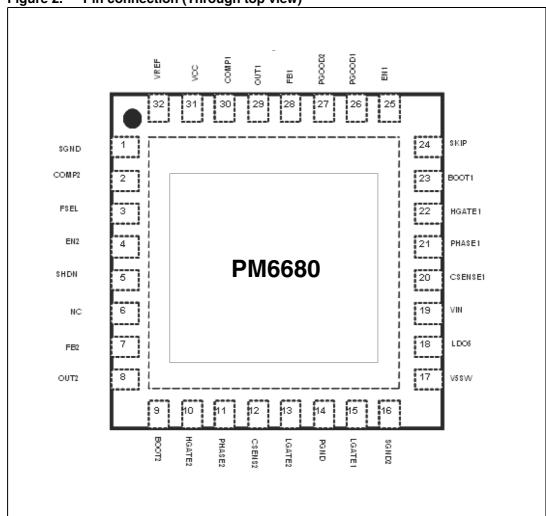

Figure 2. Pin connection (Through top view)

PM6680 Pin settings

# 3.2 Functions

Table 4. Pin functions

| N° | Pin     | Function                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | SGND1   | Signal ground. Reference for internal logic circuitry. It must be connected to the signal ground plan of the power supply. The signal ground plan and the power ground plan must be connected together in one point near the PGND pin.                                                                                                                                                                                           |

| 2  | COMP2   | DC voltage error compensation pin for the switching section 2                                                                                                                                                                                                                                                                                                                                                                    |

| 3  | FSEL    | Frequency selection pin. It provides a selectable switching frequency, allowing three different values of switching frequencies for the switching sections.                                                                                                                                                                                                                                                                      |

| 4  | EN2     | <ul> <li>Enable input for the switching section 2.</li> <li>The section 2 is enabled applying a voltage greater than 2.4 V to this pin.</li> <li>The section 2 is disabled applying a voltage lower than 0.8 V.</li> <li>When the section is disabled the High Side gate driver goes low and Low Side gate driver goes high. If both EN1 and EN2 pins are low and SHDN pin is high the device enters in standby mode.</li> </ul> |

| 5  | SHDN    | Shutdown control input.  The device switch off if the SHDN voltage is lower than the device off threshold (Shutdown mode)  The device switch on if the SHDN voltage is greater than the device on threshold.  The SHDN pin can be connected to the battery through a voltage divider to program an undervoltage lockout. In shutdown mode, the gate drivers of the two switching sections are in high impedance (high-Z).        |

| 6  | NC      | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7  | FB2     | Feedback input for the switching section 2 This pin is connected to a resistive voltage-divider from OUT2 to PGND to adjust the output voltage from 0.9 V to 3.3 V.                                                                                                                                                                                                                                                              |

| 8  | OUT2    | Output voltage sense for the switching section 2. This pin must be directly connected to the output voltage of the switching section.                                                                                                                                                                                                                                                                                            |

| 9  | BOOT2   | Bootstrap capacitor connection for the switching section 2. It supplies the high-side gate driver.                                                                                                                                                                                                                                                                                                                               |

| 10 | HGATE2  | High-side gate driver output for section 2. This is the floating gate driver output.                                                                                                                                                                                                                                                                                                                                             |

| 11 | PHASE2  | Switch node connection and return path for the high side driver for the section 2.It is also used as negative current sense input.                                                                                                                                                                                                                                                                                               |

| 12 | CSENSE2 | Positive current sense input for the switching section 2. This pin must be connected through a resistor to the drain of the synchronous rectifier (R <sub>DSON</sub> sensing) to obtain a positive current limit threshold for the power supply controller.                                                                                                                                                                      |

| 13 | LGATE2  | Low-side gate driver output for the section 2.                                                                                                                                                                                                                                                                                                                                                                                   |

| 14 | PGND    | Power ground. This pin must be connected to the power ground plan of the power supply.                                                                                                                                                                                                                                                                                                                                           |

| 15 | LGATE1  | Low-side gate driver output for the section 1.                                                                                                                                                                                                                                                                                                                                                                                   |

Pin settings PM6680

Table 4. Pin functions (continued)

| N°  | ,       |                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IN* | Pin     | Function                                                                                                                                                                                                                                                                                                                                |  |  |

| 16  | SGND2   | Signal ground for analog circuitry. It must be connected to the signal ground plan of the power supply.                                                                                                                                                                                                                                 |  |  |

| 17  | V5SW    | Internal 5 V regulator bypass connection.<br>• If V5SW is connected to OUT5 (or to an external 5 V supply) and V5SW is greater than 4.9 V, the LDO5 regulator shuts down and the LDO5 pin is directly connected to OUT5 through a 3 $\Omega$ (max) switch.<br>If V5SW is connected to GND, the LDO5 linear regulator is always on.      |  |  |

| 18  | LDO5    | 5 V internal regulator output. It can provide up to 100mA peak current. LDO5 pin supplies embedded low side gate drivers and an external load.                                                                                                                                                                                          |  |  |

| 19  | VIN     | Device supply voltage input $$ and battery voltage sense. A bypass filter (4 $\Omega$ and 4.7 $\mu F)$ between the battery and this pin is recommended.                                                                                                                                                                                 |  |  |

| 20  | CSENSE1 | Positive current sense input for the switching section 1. This pin must be connected through a resistor to the drain of the synchronous rectifier (R <sub>DSON</sub> sensing) to obtain a positive current limit threshold for the power supply controller.                                                                             |  |  |

| 21  | PHASE1  | Switch node connection and return path for the high side driver for the section 1.It is also used as negative current sense input.                                                                                                                                                                                                      |  |  |

| 22  | HGATE1  | High-side gate driver output for section 1. This is the floating gate driver output.                                                                                                                                                                                                                                                    |  |  |

| 23  | BOOT1   | Bootstrap capacitor connection for the switching section 1. It supplies the high-side gate driver.                                                                                                                                                                                                                                      |  |  |

| 24  | SKIP    | Pulse skipping mode control input.  If the pin is connected to LDO5 the PWM mode is enabled.  If the pin is connected to GND, the pulse skip mode is enabled.  If the pin is connected to VREF the pulse skip mode is enabled but the switching frequency is kept higher than 33 kHz (No-audible pulse skip mode).                      |  |  |

| 25  | EN1     | <ul> <li>Enable input for the switching section 1.</li> <li>The section 1 is enabled applying a voltage greater than 2.4 V to this pin.</li> <li>The section 1 is disabled applying a voltage lower than 0.8 V.</li> <li>When the section is disabled the High Side gate driver goes low and Low Side gate driver goes high.</li> </ul> |  |  |

| 26  | PGOOD1  | Power Good output signal for the section 1. This pin is an open drain output and when the output of the switching section 1 is out of +/- 10 % of its nominal value.It is pulled down.                                                                                                                                                  |  |  |

| 27  | PGOOD2  | Power Good output signal for the section 2. This pin is an open drain output and when the output of the switching section 2 is out of +/- 10 % of its nominal value.It is pulled down.                                                                                                                                                  |  |  |

| 28  | FB1     | Feedback input for the switching section 1. This pin is connected to a resistive voltage-divider from OUT1 to PGND to adjust the output voltage from 0.9 V to 5.5 V.                                                                                                                                                                    |  |  |

PM6680 Pin settings

Table 4. Pin functions (continued)

| N° | Pin   | Function                                                                                                                               |  |

|----|-------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| 29 | OUT1  | Output voltage sense for the switching section 1. This pin must be directly connected to the output voltage of the switching section.  |  |

| 30 | COMP1 | OC voltage error compensation pin for the switching section 1.                                                                         |  |

| 31 | VCC   | Device Supply Voltage pin. It supplies all the internal analog circuitry except the gate drivers (see LDO5). Connect this pin to LDO5. |  |

| 32 | VREF  | Internal 1.237 V high accuracy voltage reference. It can deliver 50 uA. Bypass to SGND with a 100 nF capacitor to reduce noise.        |  |

Electrical characteristics PM6680

# 4 Electrical characteristics

Table 5. Electrical characteristics  $V_{IN} = 12 \text{ V}, T_A = 0 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C}, \text{ unless otherwise specified}$  (1)

| Symbol              | Parameter                                                          | Test condition                              | Min | Тур  | Max | Unit |

|---------------------|--------------------------------------------------------------------|---------------------------------------------|-----|------|-----|------|

| Supply sec          | tion                                                               |                                             |     |      |     | _    |

| VIN                 | Input voltage range                                                | Vout = Vref, LDO5 in regulation             | 5.5 |      | 28  | V    |

| Vcc                 | IC supply voltage                                                  |                                             | 4.5 |      | 5.5 | V    |

|                     | Turn-on voltage threshold                                          |                                             |     | 4.8  | 4.9 | V    |

| $V_{V5SW}$          | Turn-off voltage threshold                                         |                                             | 4.6 | 4.75 |     | V    |

|                     | Hysteresis                                                         |                                             | 20  | 50   |     | mV   |

| $V_{V5SW}$          |                                                                    |                                             | 5.5 | V    |     |      |

| Rdson               | LDO5 internal bootstrap switch resistance                          | V5SW > 4.9                                  |     | 1.8  | 3   | Ω    |

|                     | OUTx,OUTx discharge-mode on-resistance                             |                                             |     | 18   | 25  | Ω    |

|                     | OUTx,OUTx discharge-mode<br>synchronous rectifier<br>Turn-on level |                                             | 0.2 | 0.36 | 0.6 | V    |

| Pin                 | Operating power consumption                                        | FBx > VREF, Vref in regulation, V5WS to 5 V |     |      | 4   | mW   |

| Ish                 | Operating current sunk by V <sub>IN</sub>                          | SHDN connected to GND,                      |     | 14   | 18  | μА   |

| Isb                 | Operating current sunk by V <sub>IN</sub>                          | ENx to GND, V5SW to GND                     |     | 190  | 250 | μΑ   |

| Shutdown            | section                                                            |                                             |     |      |     |      |

| .,                  | Device on threshold                                                |                                             | 1.2 | 1.5  | 1.7 | ٧    |

| $V_{SHDN}$          | Device off threshold                                               |                                             | 0.8 | 0.85 | 0.9 | V    |

| Soft start s        | ection                                                             |                                             |     |      |     |      |

|                     | Soft start ramp time                                               |                                             | 2   |      | 3.5 | ms   |

| Current lim         | it and zero crossing comparator                                    |                                             |     |      |     |      |

| I <sub>CSENSE</sub> | Input bias current limit                                           |                                             | 90  | 100  | 110 | μА   |

|                     | Comparator offset                                                  | VCSENSE-VPGND                               | -6  |      | 6   | mV   |

|                     | Zero crossing comparator offset                                    | V <sub>PGND</sub> - V <sub>PHASE</sub>      | -1  |      | 11  | mV   |

|                     | Fixed negative current limit threshold                             | V <sub>PGND</sub> - V <sub>PHASE</sub>      |     | -120 |     | mV   |

Table 5. Electrical characteristics (continued)  $V_{IN} = 12 \text{ V}, T_A = 0 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ , unless otherwise specified (1)

|                     | V <sub>IN</sub> = 12 V, 1 <sub>A</sub> = 0 °C to 85 °C, unless otherwise specified (*) |                                                                      |             |       |       |       |          |

|---------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------|-------|-------|-------|----------|

| Symbol              | Parameter                                                                              | Test condition                                                       |             | Min   | Тур   | Max   | Unit     |

| On time pu          | lse width                                                                              |                                                                      |             |       |       |       |          |

| Ton                 | On time duration                                                                       | FSEL to<br>GND                                                       | OUT1=1.5 V  | 550   | 650   | 750   | ns       |

|                     |                                                                                        |                                                                      | OUT2=1.05 V | 230   | 270   | 315   |          |

|                     |                                                                                        | FSEL to<br>VREF                                                      | OUT1=1.5 V  | 375   | 445   | 515   |          |

|                     |                                                                                        |                                                                      | OUT2=1.05 V | 175   | 210   | 245   |          |

|                     |                                                                                        | FSEL to<br>LDO5                                                      | OUT1=1.5 V  | 285   | 340   | 395   |          |

|                     |                                                                                        |                                                                      | OUT2=1.05 V | 125   | 150   | 175   |          |

| OFF time            |                                                                                        |                                                                      |             |       |       |       |          |

| T <sub>OFFMIN</sub> | Minimum off time                                                                       |                                                                      |             |       | 350   | 500   | ns       |

| Voltage ref         | erence                                                                                 |                                                                      | 1           |       | - 1   |       |          |

| $V_{REF}$           | Voltage accuracy                                                                       | 4 V < V <sub>LDO5</sub> < 5.5 V                                      |             | 1.224 | 1.236 | 1.249 | V        |

|                     | Load regulation                                                                        | -100 μA< I <sub>REF</sub> < 100 μA                                   |             | -4    |       | 4     | mV       |

|                     | Undervoltage lockout fault threshold                                                   | Falling edge of REF                                                  |             |       |       | 0.95  | mV       |

| Integrator          |                                                                                        |                                                                      |             |       | +     |       |          |

| FB                  | Voltage accuracy                                                                       |                                                                      |             | -909  | 900   | 909   | mV       |

| FB                  | Input bias current                                                                     |                                                                      |             |       | 0.1   |       | μΑ       |

| COMP                | Over voltage clamp                                                                     | Normal mode                                                          |             |       | 250   |       | mV       |

|                     |                                                                                        | Pulse skip mode                                                      |             |       | 60    |       |          |

|                     | Under voltage clamp                                                                    |                                                                      |             |       | -150  |       |          |

| Line regula         | ition                                                                                  |                                                                      |             |       |       |       |          |

|                     |                                                                                        | Both SMPS, 6 V <vin<28 v<sup="">(2)</vin<28>                         |             |       | 0.004 |       | %/V      |

| LDO5 linea          | r regulator                                                                            | <u> </u>                                                             | <u>l</u>    |       |       |       |          |

| $V_{LDO5}$          | LDO5 linear output voltage                                                             | 6 V <vin<28 ,<br="" v="">0 &lt; I<sub>LDO5</sub> &lt; 50 mA</vin<28> |             | 4.9   | 5.0   | 5.1   | V        |

|                     | LDO5 line regulation                                                                   | 6 V< VIN < 28 V,<br>I <sub>LDO5</sub> = 20 mA ,                      |             |       |       | 0.004 | %/V      |

| I <sub>LDO5</sub>   | LDO5 Current limit                                                                     | V <sub>LDO5</sub> > UVLO                                             |             | 270   | 330   | 400   | mA       |

| ULVO                | Under Voltage Lockout of LDO5                                                          |                                                                      |             | 3.94  | 4     | 4.13  | <b>V</b> |

**Electrical characteristics** PM6680

Table 5.

Electrical characteristics (continued)  $V_{IN} = 12 \text{ V}, T_A = 0 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ , unless otherwise specified <sup>(1)</sup>

| Symbol                | Parameter                   | Test condition                        | Min                    | Тур | Max                    | Unit |  |

|-----------------------|-----------------------------|---------------------------------------|------------------------|-----|------------------------|------|--|

| High and lo           | w gate drivers              |                                       |                        |     | "                      |      |  |

|                       |                             | HGATEx high state (pullup)            |                        | 2.0 | 3                      | Ω    |  |

|                       | HGATE driver on-resistance  | HGATEx low state (pulldown)           |                        | 1.6 | 2.7                    | Ω    |  |

|                       | LOATE division on marietana | LGATEx high state (pullup)            |                        | 1.4 | 2.1                    | Ω    |  |

|                       | LGATE driver on-resistance  | LGATEx low state (pulldown)           |                        | 0.8 | 1.2                    | Ω    |  |

| PGOOD pin             | s UVP/OVP protections       | ,                                     |                        |     | 1                      |      |  |

| OVP                   | Over voltage threshold      | Both SMPS sections with               | 112                    | 116 | 120                    | %    |  |

| UVP                   | Under voltage threshold     | respect to VREF.                      | 65                     | 68  | 71                     | %    |  |

| PGOOD1,2              | Upper threshold (VFB-VREF)  |                                       | 107                    | 110 | 113                    | %    |  |

|                       | Lower threshold (VFB-VREF)  |                                       | 88                     | 91  | 94                     | %    |  |

| I <sub>PGOOD1,2</sub> | PGOOD leakage current       | V <sub>PGOOD1,2</sub> forced to 5.5 V |                        |     | 1                      | uA   |  |

| V <sub>PGOOD1,2</sub> | Output low voltage          | ISink = 4 mA                          |                        | 150 | 250                    | mV   |  |

| Thermal sh            | utdown                      | ,                                     |                        |     | 1                      |      |  |

| T <sub>SDN</sub>      | Shutdown temperature        |                                       |                        | 150 |                        | °C   |  |

| Power mana            | agement pins                |                                       |                        |     | 1                      |      |  |

|                       | SMPS disabled level         |                                       |                        |     | 0.8                    | V    |  |

| EN1,2                 | SMPS enabled level          |                                       | 2.4                    |     |                        |      |  |

|                       | Frequency selection range   | Low level (3)                         |                        |     | 0.5                    |      |  |

| FSEL                  |                             | Middle level (3)                      | 1.0                    |     | V <sub>LDO5</sub> -1.5 | V    |  |

|                       |                             | High level (3)                        | V <sub>LDO5</sub> -0.8 |     |                        |      |  |

| SKIP                  | Pulse skip mode             | (3)                                   |                        |     | 0.5                    | V    |  |

|                       | Ultrasonic mode             | (3)                                   | 1.0                    |     | V <sub>LDO5</sub> -1.5 |      |  |

|                       | PWM mode                    | (3)                                   | V <sub>LDO5</sub> -0.8 |     |                        |      |  |

|                       | Input leakage current       | V <sub>EN1,2</sub> = 0 to 5 V         |                        |     | 1                      | μΑ   |  |

|                       |                             | V <sub>SKIP</sub> = 0 to 5 V          |                        |     | 1                      |      |  |

|                       |                             | V <sub>SHDN</sub> = 0 to 5 V          |                        |     | 1                      |      |  |

|                       |                             | V <sub>FSEL</sub> = 0 to 5 V          |                        |     | 1                      |      |  |

T<sub>A</sub> = T<sub>J</sub>. All parameters at operating temperature extremes are guaranteed by design and statistical analysis (not production tested).

<sup>2.</sup> by design

<sup>3.</sup> by demoboard test

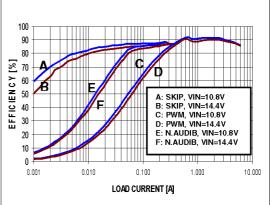

## 5 Typical operating characteristics

FSEL = GND (200/300 kHz), SKIP = GND (skip mode), V5SW = V5SW = EXT5V (external 5 V power supply connected), input voltage VIN = 12 V, SHDN, EN1 and EN2 high, OUT1 = 1.5 V, OUT2 = 1.05 V, no load unless specified)

Figure 3. 1.5 V output efficiency vs load current

100

90

80

80

A: SKIP, VIN=10.8V

B: SKIP, VIN=14.4V

C: PWM, VIN=14.4V

C: PWM, VIN=14.4V

E: N.AUDIB, VIN=10.8V

F: N.AUDIB, VIN=14.4V

E: N.AUDIB, VIN=14.4V

C: PWM, VIN=14.4V

E: N.AUDIB, VIN=14.4V

E:

Figure 4. 1.05 V output efficiency vs load current

Figure 5. PWM no load input battery vs Figure 6. Skip no load battery current input voltage

Figure 7. No-audible skip no load battery current vs input voltage

Figure 8. Stand-by mode input battery current vs input voltage

Figure 9. Shutdown mode input battery Figure 10. 1.5 V switching frequency vs current vs input voltage load current

Figure 11. 1.05 V switching frequency vs Figure 12. LDO5 vs output current load current

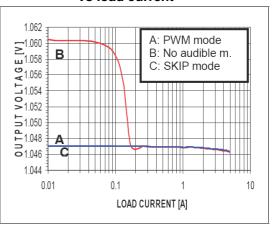

Figure 13. 1.5 V voltage regulation vs load current

1.558

A: PWM mode

B: No audible m.

C: SKIP mode

1.540

1.540

1.540

0.01

0.1

1 10

LOAD CURRENT [A]

Figure 14. 1.05 V voltage regulation vs load current

Figure 15. Voltage reference vs load current

1.2325 1.2320 2.1.2315 2.1.2315 2.1.2315 2.1.2315 2.1.2305 1.2295 1.2290 0 20 40 60 80 100 LOAD CURRENT [uA]

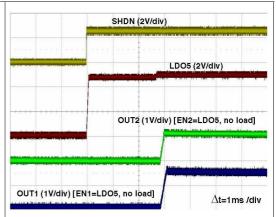

Figure 16. OUT1, OUT2 and LDO5 power-up

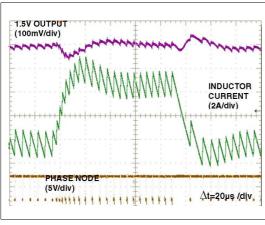

Figure 17. 1.5 V load transient

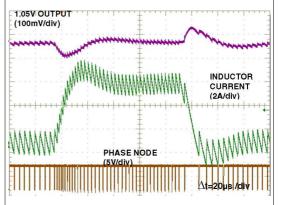

Figure 18. 1.05 V load transient

Figure 25. 1.5 V no-audible skip mode Figure 26. 1.05 V no-audible skip mode

**577**

PM6680 **Block diagram**

#### **Block diagram** 6

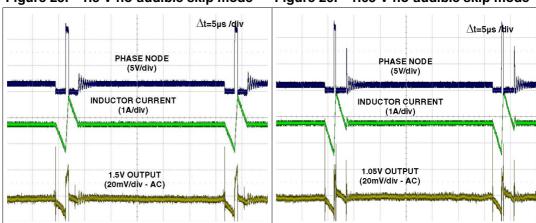

Figure 27. Functional block diagram

PM6680 Device description

## 7 Device description

The PM6680 is a dual step-down controller dedicated to provide logic voltages for notebook computers.

It is based on a Constant On Time control architecture. This type of control offers a very fast load transient response with a minimum external component count. A typical application circuit is shown in *Figure 27*.

The PM6680 regulates two adjustable output voltages: OUT1 and OUT2. The switching frequency of the two sections can be adjusted to 200/300 kHz, 300/400 kHz or 400/500 kHz respectively. In order to maximize the efficiency at light load condition, a pulse skipping mode can be selected.

The PM6680 includes also a 5 V linear regulator (LDO5) that can power the switching drivers. If the output OUT1 regulates 5 V, in order to maximize the efficiency in higher consumption status, the linear regulator can be turned off and their outputs can be supplied directly from the switching outputs. The PM6680 provides protection versus overvoltage, undervoltage and over temperature as well as power good signals for monitoring purposes. An external 1.237 V reference is available.

#### 7.1 Constant On time PWM control

If the SKIP pin is tied to 5 V, the device works in PWM mode. Each power section has an independent on time control. The PM6680 employees a pseudo-fixed switching frequency, Constant On Time (COT) controller as core of the switched mode section. Each power section has an independent COT control.

The COT controller is based on a relatively simple algorithm and uses the ripple voltage due to the output capacitor's ESR to trigger the fixed on-time one-shot generator. In this way, the output capacitor's ESR acts as a current sense resistor providing the appropriate ramp signal to the PWM comparator. On-time one-shot duration is directly proportional to the output voltage, sensed at the OUT1/OUT2 pins, and inversely proportional to the input voltage, sensed at the VIN pin, as follows:

#### **Equation 1**

$$T_{ON} = K \cdot \frac{V_{OUT}}{V_{IN}}$$

This leads to a nearly constant switching frequency, regardless of input and output voltages. When the output voltage goes lower than the regulated voltage Vreg, the on-time one shot generator directly drives the high side MOSFET for a fixed on time allowing the inductor current to increase; after the on time, an off time phase, in which the low side MOSFET is turned on, follows. *Figure 28* shows the inductor current and the output voltage waveforms in PWM mode.

Device description PM6680

Output voltage Vreg DC error

Figure 28. Constant ON time PWM control

The duty cycle of the buck converter in steady state is:

#### **Equation 2**

$$D = \frac{V_{OUT}}{V_{IN}}$$

The PWM control works at a nearly fixed frequency f<sub>SW</sub>:

#### **Equation 3**

$$f_{SW} = \frac{\frac{V_{OUT}}{V_{IN}}}{K_{on} \times \frac{V_{OUT}}{V_{IN}}} = 1/K_{on}$$

As mentioned the steady state switching frequency is theoretically independent from battery voltage and from output voltage.

Actually the frequency depends on parasitic voltage drops that are present during the charging path(high side switch resistance, inductor resistance(DCR)) and discharging path(low side switch resistance, DCR).

As a result the switching frequency increases as a function of the load current.

Standard switching frequency values can be selected for both sections by pin FSEL as shown in the following table:

Table 6. FSEL pin selection: typical switching frequency

|             | Fsw@OUT1 = 1.5 V (kHz) | Fsw@OUT2 = 1.05 V (kHz) |

|-------------|------------------------|-------------------------|

| FSEL = GND  | 200                    | 325                     |

| FSEL = VREF | 290                    | 425                     |

| FSEL = LDO5 | 390                    | 590                     |

PM6680 **Device description**

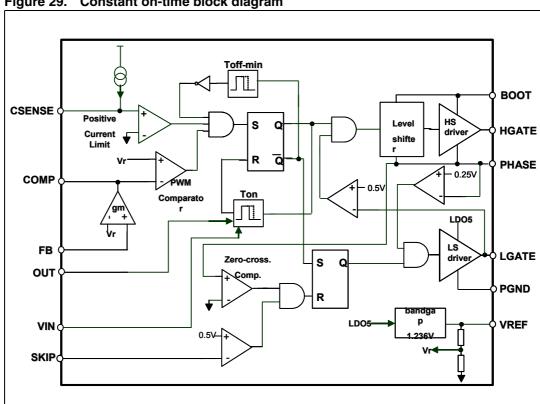

#### 7.2 Constant on time architecture

Figure 29 shows the simplified block diagram of a Constant On Time controller. A minimum off-time constrain (300 ns typ.) is introduced to allow inductor valley current sensing on synchronous switch. A minimum on-time (70 ns) is also introduced to assure the start-up switching sequence.

PM6680 has a one-shot generator for each power section that turns on the high side MOSFET when the following conditions are satisfied simultaneously: the PWM comparator is high, the synchronous rectifier current is below the current limit threshold, and the minimum off-time has timed out.

Once the on-time has timed out, the high side switch is turned off, while the synchronous switch is turned on according to the anti-cross conduction circuitry management.

When the negative input voltage at the PWM comparator (Figure 29), which is a scaleddown replica of the output voltage (see the external R1/R2 divider in Figure 29), reaches the valley limit (determined by internal reference Vr = 0.9 V), the low-side MOSFET is turned off according to the anti-cross conduction logic once again, and a new cycle begins.

Figure 29. Constant on-time block diagram

Device description PM6680

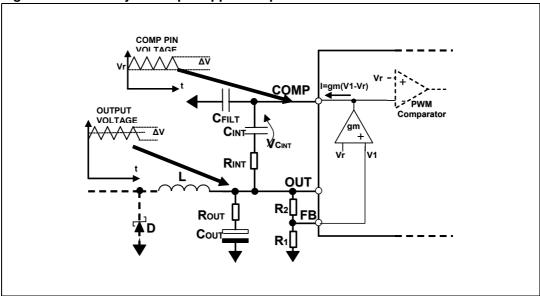

## 7.3 Output ripple compensation and loop stability

In a classic Constant On Time control, the system regulates the valley value of the output voltage and not the average value, as shown in *Figure 28* In this condition, the output voltage ripple is source of a DC static error.

To compensate this error, an integrator network can be introduced in the control loop, by connecting the output voltage to the COMP1/COMP2 (for the OUT1 and OUT2 sections respectively) pin through a capacitor  $C_{\text{INT}}$  as in *Figure 30*

Figure 30. Circuitry for output ripple compensation

The integrator amplifier generates a current, proportional to the DC errors between the FB voltage and Vr, which decreases the output voltage in order to compensate the total static error, including the voltage drop on PCB traces. In addition, C<sub>INT</sub> provides an AC path for the output ripple. In steady state, the voltage on COMP1/COMP2 pin is the sum of the reference voltage Vr and the output ripple (see *Figure 30*). In fact when the voltage on the COMP pin reaches Vr, a fixed Ton begins and the output increases.

For example, we consider Vout = 5 V with an output ripple of  $\Delta V$  = 50 mV. Considering  $C_{INT} >> C_{FILT}$ , the  $C_{INT}$  DC voltage drop  $V_{CINT}$  is about 5 V-Vr+25 mV = 4.125 V.  $C_{INT}$  assures an AC path for the output voltage ripple. Then the COMP pin ripple is a replica of the output ripple, with a DC value of Vr + 25 mV = 925 mV.

For more details about the output ripple compensation network, see the *Section 7.13.6: Closing the integrator loop on page 37* in the Design guidelines.

In steady state the FB pin voltage is about Vr and the regulated output voltage depends on the external divider:

#### **Equation 4**

$$OUT = Vr \times \left(1 + \frac{R_2}{R_1}\right)$$

**577**

PM6680 Device description

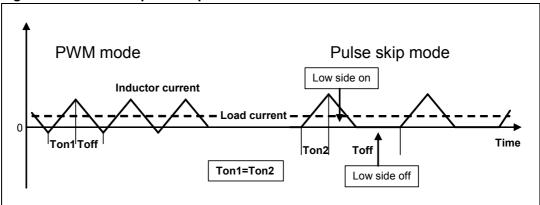

### 7.4 Pulse skip mode

If the SKIP pin is tied to ground, the device works in skip mode.

At light loads a zero-crossing comparator truncates the low-side switch on-time when the inductor current becomes negative. In this condition the section works in discontinuous conduction mode. The threshold between continuous and discontinuous conduction mode is:

#### **Equation 5**

$$ILOAD(SKIP) = \frac{V_{IN} - V_{OUT}}{2 \times L} \times T_{ON}$$

For higher loads the inductor current doesn't cross the zero and the device works in the same way as in PWM mode and the frequency is fixed to the nominal value.

Figure 31. PWM and pulse skip mode inductor current

*Figure 31* shows inductor current waveforms in PWM and SKIP mode. In order to keep average inductor current equal to load current, in SKIP mode some switching cycles are skipped. When the output ripple reaches the regulated voltage Vreg, a new cycle begins. The off cycle duration and the switching frequency depend on the load condition.

As a result of the control technique, losses are reduced at light loads, improving the system efficiency.

## 7.5 No-audible skip mode

If SKIP pin is tied to VREF, a no-audible skip mode with a minimum switching frequency of 33 kHz is enabled. At light load condition, If there is not a new switching cycle within a 30 us (typ.) period, a no-audible skip mode cycle begins.