Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **PN511**

## **Transmission Module**

Rev. 3.3 — 13 June 2007 082733

Product short data sheet

### 1. Introduction

This Product short data sheet describes the functionality of the transceiver IC PN511. It includes functional and electrical specifications. A complete specification is given in the product data sheet.

## 2. General description

The PN511 is a highly integrated transceiver IC for contactless communication at 13.56 MHz. This transceiver IC utilizes an outstanding modulation and demodulation concept completely integrated for different kinds of contactless communication methods and protocols at 13.56 MHz.

The PN511 transceiver ICs support 3 different operating modes

- Reader/Writer mode supporting ISO 14443A/Mifare and FeliCa scheme

- Card Operation mode supporting ISO 14443A/Mifare and FeliCa scheme

- NFCIP-1 mode

Enabled in Reader/Writer mode for ISO 14443A/Mifare, the PN511's internal transmitter part is able to drive a reader/writer antenna designed to communicate with ISO 14443A/Mifare cards and transponders without additional active circuitry. The receiver part provides a robust and efficient implementation of a demodulation and decoding circuitry for signals from ISO 14443A/Mifare compatible cards and transponders. The digital part handles the complete ISO 14443A framing and error detection (Parity & CRC).

The PN511 supports Mifare Classic (e.g. Mifare Standard) products. The PN511 supports contactless communication using Mifare higher transfer speeds up to 424 kbit/s in both directions.

Enabled in Reader/Writer mode for FeliCa, the PN511 transceiver IC supports the FeliCa communication scheme. The receiver part provides a robust and efficient implementation of the demodulation and decoding circuitry for FeliCa coded signals. The digital part handles the FeliCa framing and error detection like CRC. The PN511 supports contactless communication using FeliCa Higher transfer speeds up to 424 kbit/s in both directions.

In Card Operation mode, the PN511 transceiver IC is able to answer to a reader/writer command either according to the FeliCa or ISO 14443A/Mifare card interface scheme. The PN511 generates the digital load modulated signals and in addition with an external circuit the answer can be sent back to the reader/writer. A complete card functionality is only possible in combination with a secure core IC using the S<sup>2</sup>C interface.

#### **Transmission Module**

Additionally, the PN511 transceiver IC offers the possibility to communicate directly to an NFCIP-1 device in the NFCIP-1 mode. The NFCIP-1 mode offers different communication mode and transfer speeds up to 424 kbit/s according to the Ecma 340 and ISO/IEC 18092 NFCIP-1 Standard. The digital part handles the complete NFCIP-1 framing and error detection.

Various host controller interfaces are implemented:

- 8-bit parallel interface1

- SPI interface

- serial UART (similar to RS232 with voltage levels according pad voltage supply)

- I<sup>2</sup>C interface.

<sup>1. 8-</sup>bit parallel Interface only available in HVQFN40 package.

### 3. Features

- Highly integrated analog circuitry to demodulate and decode responses

- Buffered output drivers to connect an antenna with minimum number of external components

**Transmission Module**

- Integrated RF Level detector

- Integrated data mode detector

- ISO 14443A/Mifare support

- Typical operating distance in Reader/Writer mode for communication to a ISO 14443A/ Mifare or FeliCa card up to 50 mm depending on the antenna size, tuning and power supply

- Typical operating distance in NFCIP-1 mode up to 50 mm depending on the antenna size and tuning and power supply

- Typical operating distance in ISO 14443A/Mifare card or FeliCa Card Operation mode of about 100 mm depending on the antenna size and tuning and the external field strength

- Mifare Classic encryption in Reader/Writer mode support

- ISO 14443A higher transfer speed communication at 212 kbit/s and 424 kbit/s

- Contactless communication according to the FeliCa scheme at 212 kbit/s and 424 kbit/s

- Integrated RF interface for NFCIP-1 up to 424 kbit/s

- S<sup>2</sup>C interface

- Supported host controller interfaces

- SPI interface up to 10 Mbit/s

- ◆ I<sup>2</sup>C interface up to 400 kbit/s in Fast mode, up to 3400 kbit/s in High-speed mode

- serial UART in different transfer speeds up to 1228.8 kbit/s, framing according to the RS232 interface with voltage levels according pad voltage supply

- ◆ 8-bit parallel interface with and without Address Latch Enable

- Comfortable 64 byte send and receive FIFO-buffer

- Flexible interrupt modes

- Hard reset with low power function

- Power-down mode per software

- Programmable timer

- Internal oscillator to connect 27.12 MHz quartz

- 2.5-3.6 V power supply

- CRC Co-processor

- Free programmable I/O pins

- Internal self test

#### **Transmission Module**

### 4. Quick reference data

Table 1. Quick reference data

| Symbol                   | Parameter                                    | Conditions                                                             |            | Min | Тур | Max | Unit |

|--------------------------|----------------------------------------------|------------------------------------------------------------------------|------------|-----|-----|-----|------|

| $AV_{DD}$                | Supply Voltage                               | $AV_{SS} = DV_{SS} = PV_{SS} = TV_{SS} = 0 V,$                         | [1][2]     | 2.5 | -   | 3.6 | V    |

| $DV_DD$                  |                                              | $PV_{DD} \leq AV_{DD} = DV_{DD} = TV_{DD}$                             | [1][2]     |     |     |     |      |

| $TV_DD$                  |                                              |                                                                        | [1][2]     |     |     |     |      |

| $PV_{DD}$                |                                              |                                                                        | [3]        | 1.6 | -   | 3.6 | V    |

| I <sub>HPD</sub>         | Hard Power-down Current                      | $AV_{DD} = DV_{DD} = $ $TV_{DD} = PV_{DD} = 3 V,$ $N_{RESET} = LOW$    | [7]        | -   | -   | 5   | μΑ   |

| I <sub>SPD</sub>         | Soft Power-down Current                      | $AV_{DD} = DV_{DD} = TV_{DD} = PV_{DD} =$<br>3 V, RF level detector on | [7]        | -   | -   | 10  | μΑ   |

| I <sub>DVDD</sub>        | Digital Supply Current                       | $DV_{DD} = 3 V$                                                        |            | -   | 6.5 | 9   | mA   |

| I <sub>AVDD</sub>        | Analog Supply Current                        | $AV_{DD} = 3 \text{ V, bit RCVOff} = 0$                                |            | -   | 7   | 10  | mA   |

| I <sub>AVDD,RCVOFF</sub> | Analog Supply Current, receiver switched off | $AV_{DD} = 3 \text{ V, bit RCVOff} = 1$                                |            | -   | 3   | 5   | mA   |

| I <sub>PVDD</sub>        | Pad Supply Current                           |                                                                        | <u>[5]</u> | -   | -   | 40  | mA   |

| I <sub>TVDD</sub>        | Transmitter Supply Current                   | Continuous Wave                                                        | [4][6][8]  | -   | 60  | 100 | mA   |

| T <sub>amb</sub>         | operating ambient temperature                |                                                                        |            | -30 |     | +85 | °C   |

<sup>[1]</sup> Supply voltage below 3 V reduces the performance (e.g. the achievable operating distance).

## 5. Ordering information

Table 2. Ordering information

| Type number    | Package |                                                                                                            |         |  |  |  |  |

|----------------|---------|------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|

|                | Name    | Description                                                                                                | Version |  |  |  |  |

| PN5110A0HN1/C2 | HVQFN32 | Plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85$ mm | SOT617  |  |  |  |  |

| PN5110A0HN/C2  | HVQFN40 | Plastic thermal enhanced very thin quad flat package; no leads; 40 terminals; body 6× 6× 0.85 mm           | SOT618  |  |  |  |  |

<sup>[2]</sup>  $AV_{DD}$ ,  $DV_{DD}$  and  $TV_{DD}$  shall always be on the same voltage level.

<sup>[3]</sup>  $PV_{DD}$  shall always be on the same or lower voltage level than  $DV_{DD}$ .

<sup>[4]</sup>  $I_{TVDD}$  depends on  $TV_{DD}$  and the external circuitry connected to Tx1 and Tx2

<sup>[5]</sup>  $I_{PVDD}$  depends on the overall load at the digital pins.

<sup>[6]</sup> During operation with a typical circuitry the overall current is below 100 mA.

<sup>[7]</sup> I<sub>SPD</sub> and I<sub>HPD</sub> are the total currents over all supplies.

<sup>[8]</sup> Typical value using a complementary driver configuration and an antenna matched to 40 Ω between TX1 and TX2 at 13.56 MHz

### **Transmission Module**

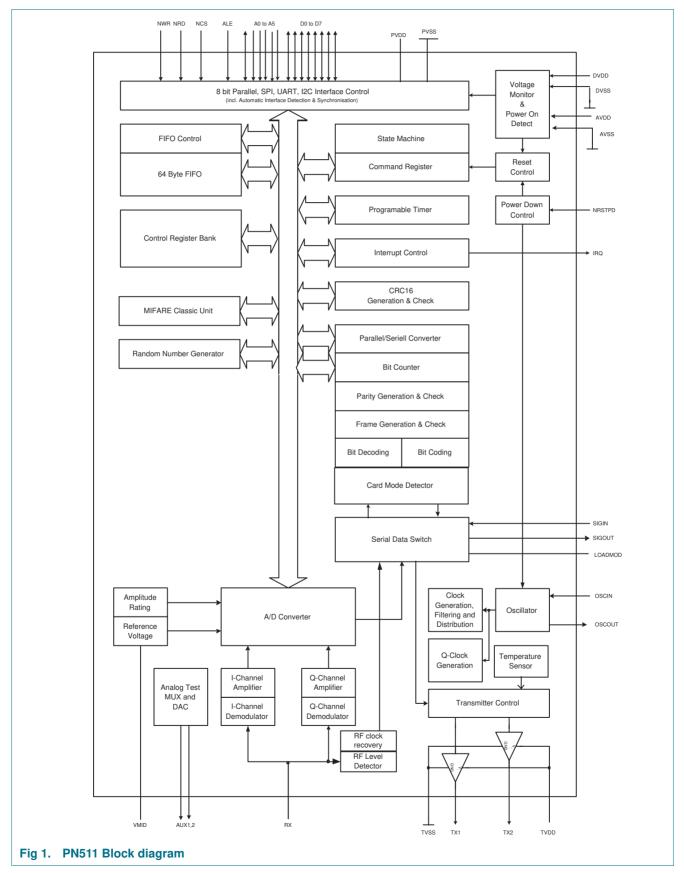

## 6. Block diagram

The Analog interface handles the modulation and demodulation of the analog signals according to the Card Receiving mode, Reader/Writer mode and NFCIP-1 mode communication scheme.

The RF level detector detects the presence of an external RF-field delivered by the antenna to the RX pin.

The Data mode detector detects a Mifare, FeliCa or NFCIP-1 mode in order to prepare the internal receiver to demodulate signals, which are sent to the PN511.

The communication (S<sup>2</sup>C) interface provides digital signals to support communication for transfer speeds above 424 kbit/s and digital signals to communicate to a secure smart card IC.

#### **Transmission Module**

**Transmission Module**

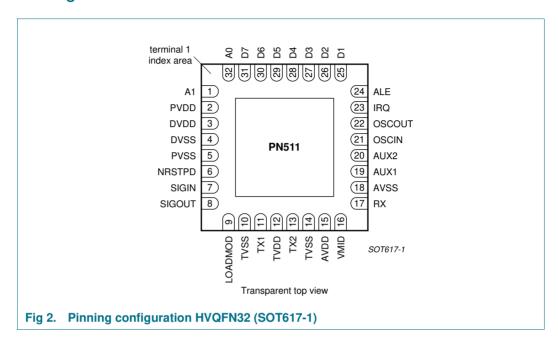

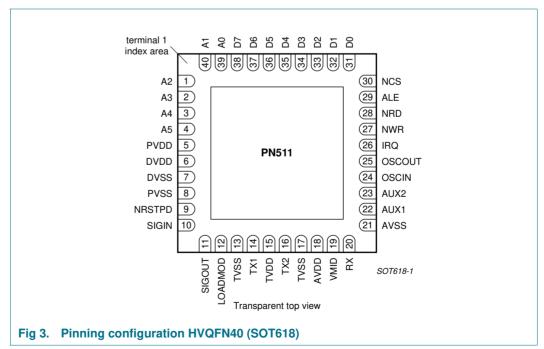

## 7. Pinning information

### 7.1 Pinning

**Transmission Module**

## 7.2 Pin description

Table 3. Pin description HVQFN32

| Table 3. | Pin descrip | uon nvQi | FINOL                                                                                                                                                                                                                                          |

|----------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol   | Pin         | Type     | Description                                                                                                                                                                                                                                    |

| A1       | 1           | 1        | Address Line                                                                                                                                                                                                                                   |

| PVDD     | 2           | PWR      | Pad power supply                                                                                                                                                                                                                               |

| DVDD     | 3           | PWR      | Digital Power Supply                                                                                                                                                                                                                           |

| DVSS     | 4           | PWR      | Digital Ground                                                                                                                                                                                                                                 |

| PVSS     | 5           | PWR      | Pad power supply ground                                                                                                                                                                                                                        |

| NRSTPD   | 6           | I        | <b>Not Reset and Power Down:</b> When LOW, internal current sinks are switched off, the oscillator is inhibited, and the input pads are disconnected from the outside world. With a positive edge on this pin the internal reset phase starts. |

| SIGIN    | 7           | I        | Communication Interface Input: accepts a digital, serial data stream                                                                                                                                                                           |

| SIGOUT   | 8           | 0        | Communication Interface Output: delivers a serial data stream                                                                                                                                                                                  |

| LOADMOD  | 9           | 0        | <b>Load Modulation Output:</b> provides digital signal for FeliCa and Mifare Card Operation mode                                                                                                                                               |

| TVSS     | 10          | PWR      | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                                   |

| TX1      | 11          | 0        | Transmitter 1: delivers the modulated 13.56 MHz energy carrier                                                                                                                                                                                 |

| TVDD     | 12          | PWR      | Transmitter Power Supply: supplies the output stage of TX1 and TX2                                                                                                                                                                             |

| TX2      | 13          | 0        | Transmitter 2: delivers the modulated 13.56 MHz energy carrier                                                                                                                                                                                 |

| TVSS     | 14          | PWR      | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                                   |

| AVDD     | 15          | PWR      | Analog Power Supply                                                                                                                                                                                                                            |

| VMID     | 16          | PWR      | Internal Reference Voltage: This pin delivers the internal reference voltage.                                                                                                                                                                  |

| RX       | 17          | 1        | Receiver Input                                                                                                                                                                                                                                 |

| AVSS     | 18          | PWR      | Analog Ground                                                                                                                                                                                                                                  |

| AUX1     | 19          | 0        | Auxiliary Outputs: These pins are used for testing.                                                                                                                                                                                            |

| AUX2     | 20          | 0        |                                                                                                                                                                                                                                                |

| OSCIN    | 21          | I        | <b>Crystal Oscillator Input:</b> input to the inverting amplifier of the oscillator. This pin is also the input for an externally generated clock ( $f_{osc} = 27.12 \text{ MHz}$ ).                                                           |

| OSCOUT   | 22          | 0        | Crystal Oscillator Output: Output of the inverting amplifier of the oscillator.                                                                                                                                                                |

| IRQ      | 23          | 0        | Interrupt Request: output to signal an interrupt event                                                                                                                                                                                         |

| ALE      | 24          | I        | <b>Address Latch Enable:</b> signal to latch AD0 to AD5 into the internal address latch when HIGH.                                                                                                                                             |

| D1 to D7 | 25 to 31    | I/O      | 8-bit Bi-directional Data Bus.                                                                                                                                                                                                                 |

|          |             |          | Remark: An 8-bit parallel interface is not available.                                                                                                                                                                                          |

|          |             |          | <b>Remark:</b> If the host controller selects $I^2C$ as digital host controller interface, these pins can be used to define the $I^2C$ address.                                                                                                |

|          |             |          | Remark: For serial interfaces this pins can be used for test signals or I/Os.                                                                                                                                                                  |

| A0       | 32          | I        | Address Line                                                                                                                                                                                                                                   |

| A0       | 32          | l        | Address Line                                                                                                                                                                                                                                   |

**Transmission Module**

### Table 4. Pin description HVQFN40

| Symbol    | Pin      | Type | Description                                                                                                                                                                                                                                    |

|-----------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2 to A5  | 1 to 4   | I    | Address Line                                                                                                                                                                                                                                   |

| PVDD      | 5        | PWR  | Pad power supply                                                                                                                                                                                                                               |

| DVDD      | 6        | PWR  | Digital Power Supply                                                                                                                                                                                                                           |

| DVSS      | 7        | PWR  | Digital Ground                                                                                                                                                                                                                                 |

| PVSS      | 8        | PWR  | Pad power supply ground                                                                                                                                                                                                                        |

| NRSTPD    | 9        | I    | <b>Not Reset and Power Down:</b> When LOW, internal current sinks are switched off, the oscillator is inhibited, and the input pads are disconnected from the outside world. With a positive edge on this pin the internal reset phase starts. |

| SIGIN     | 10       | I    | Communication Interface Input: accepts a digital, serial data stream                                                                                                                                                                           |

| SIGOUT    | 11       | 0    | Communication Interface Output: delivers a serial data stream                                                                                                                                                                                  |

| LOADMOD   | 12       | 0    | <b>Load Modulation Output:</b> provides digital signal for FeliCa and Mifare Card Operation mode                                                                                                                                               |

| TVSS      | 13       | PWR  | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                                   |

| TX1       | 14       | 0    | Transmitter 1: delivers the modulated 13.56 MHz energy carrier                                                                                                                                                                                 |

| TVDD      | 15       | PWR  | Transmitter Power Supply: supplies the output stage of TX1 and TX2                                                                                                                                                                             |

| TX2       | 16       | 0    | Transmitter 2: delivers the modulated 13.56 MHz energy carrier                                                                                                                                                                                 |

| TVSS      | 17       | PWR  | Transmitter Ground: supplies the output stage of TX1 and TX2                                                                                                                                                                                   |

| AVDD      | 18       | PWR  | Analog Power Supply                                                                                                                                                                                                                            |

| VMID      | 19       | PWR  | Internal Reference Voltage: This pin delivers the internal reference voltage.                                                                                                                                                                  |

| RX        | 20       | I    | Receiver Input                                                                                                                                                                                                                                 |

| AVSS      | 21       | PWR  | Analog Ground                                                                                                                                                                                                                                  |

| AUX1      | 22       | 0    | Auxiliary Outputs: These pins are used for testing.                                                                                                                                                                                            |

| AUX2      | 23       | 0    |                                                                                                                                                                                                                                                |

| OSCIN     | 24       | I    | <b>Crystal Oscillator Input:</b> input to the inverting amplifier of the oscillator. This pin is also the input for an externally generated clock ( $f_{osc} = 27.12 \text{ MHz}$ ).                                                           |

| OSCOUT    | 25       | 0    | Crystal Oscillator Output: Output of the inverting amplifier of the oscillator.                                                                                                                                                                |

| IRQ       | 26       | 0    | Interrupt Request: output to signal an interrupt event                                                                                                                                                                                         |

| NWR       | 27       | I    | Not Write: strobe to write data (applied on D0 to D7) into the PN511 register                                                                                                                                                                  |

| NRD       | 28       | I    | Not Read: strobe to read data from the PN511 register (applied on D0 to D7)                                                                                                                                                                    |

| ALE       | 29       | I    | <b>Address Latch Enable:</b> signal to latch AD0 to AD5 into the internal address latch when HIGH.                                                                                                                                             |

| NCS       | 30       | I    | Not Chip Select: selects and activates the host controller interface of the PN511                                                                                                                                                              |

| D0 to D7  | 31 to 38 | I/O  | 8-bit Bi-directional Data Bus.                                                                                                                                                                                                                 |

|           |          |      | Remark: For serial interfaces this pins can be used for test signals or I/Os.                                                                                                                                                                  |

|           |          |      | <b>Remark:</b> If the host controller selects $I^2C$ as digital host controller interface, these pins can be used to define the $I^2C$ address.                                                                                                |

| A0 to1 A1 | 39 to 40 | ı    | Address Line                                                                                                                                                                                                                                   |

**Transmission Module**

## 8. Operating modes

PN511 transceiver IC supports the following operating modes:

- Reader/Writer mode supporting ISO 14443A/Mifare and FeliCa scheme

- Card Operation mode supporting ISO 14443A/ Mifare and FeliCa scheme

- NFCIP-1 mode

The modes support different transfer speeds and modulation schemes. The following chapters will explain the different modes in detail.

Note: All indicated modulation indices and modes in this chapter are system parameters. This means that beside the IC settings a suitable antenna tuning is required to achieve the optimum performance.

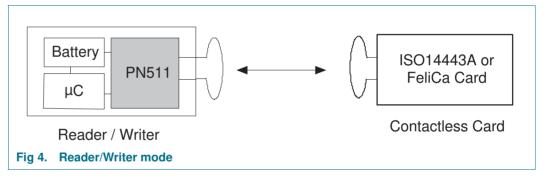

#### 8.1 Reader/Writer mode

Generally 2 Reader/Writer modes are supported. The PN511 can act as a reader/writer for ISO 14443A/Mifare or FeliCa cards.

In the Reader/Writer mode the PN511 enables the communication to a contactless ISO 14443A/Mifare or FeliCa card.

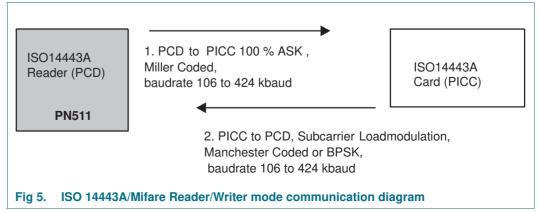

### 8.1.1 ISO 14443A/Mifare reader/writer functionality

The ISO 14443A/Mifare Reader/Writer mode is the general reader to card communication scheme according to the ISO 14443A/Mifare specification. The following diagram describes the communication on a physical level, the communication table describes the physical parameters.

| Table 5. C | ommunication | overview for | <b>ISO 14</b> | 4443A/Mifare | reader/writer |

|------------|--------------|--------------|---------------|--------------|---------------|

|------------|--------------|--------------|---------------|--------------|---------------|

| Communication                                              |                           | ISO 14443A/Mifare          | Mifare Higher tra          | nsfer speeds               |

|------------------------------------------------------------|---------------------------|----------------------------|----------------------------|----------------------------|

| direction                                                  | transfer speed            | 106 kbit/s                 | 212 kbit/s                 | 424 kbit/s                 |

| PN511 → PICC<br>(send data from<br>the PN511 to a<br>card) | Modulation on reader side | 100% ASK                   | 100% ASK                   | 100% ASK                   |

|                                                            | bit coding                | Modified Miller coding     | Modified Miller coding     | Modified Miller coding     |

|                                                            | Bitlength                 | (128/13.56) μs             | (64/13.56) μs              | (32/13.56) μs              |

| PICC → PN511<br>(receive data<br>from a card)              | modulation on card side   | subcarrier load modulation | subcarrier load modulation | subcarrier load modulation |

|                                                            | subcarrier<br>frequency   | 13.56 MHz/16               | 13.56 MHz/16               | 13.56 MHz/16               |

|                                                            | bit coding                | Manchester coding          | BPSK                       | BPSK                       |

The contactless UART of PN511 and a dedicated external host controller are required to handle the complete Mifare/ISO 14443A/Mifare protocol.

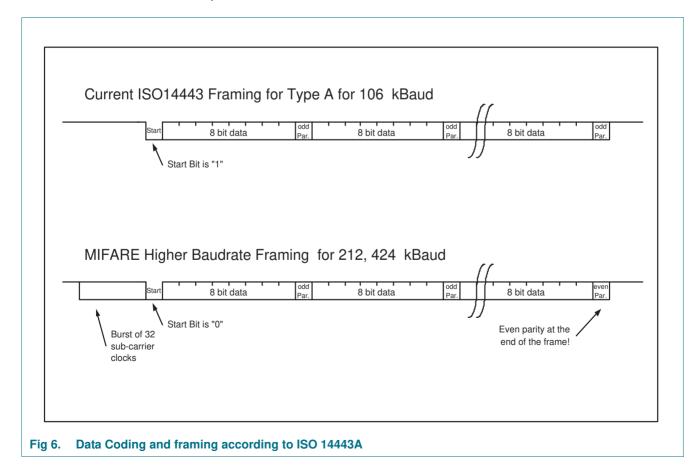

### 8.1.1.1 Data Coding and framing according to ISO 14443A/Mifare

The internal CRC co-processor calculates the CRC value according to the definitions given in the ISO 14443A part 3 and handles parity generation internally according to the transfer speed.

**Transmission Module**

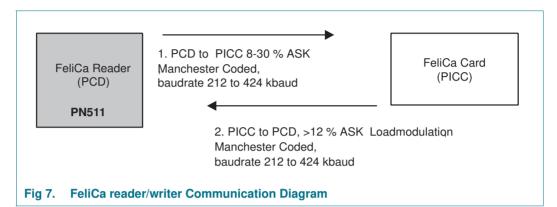

#### 8.1.2 FeliCa reader/writer functionality

The FeliCa mode is the general reader/writer to card communication scheme according to the FeliCa specification. The following diagram describes the communication on a physical level, the communication overview describes the physical parameters.

Table 6. Communication overview for FeliCa reader/writer

| Communication direction |                             | FeliCa            | FeliCa Higher transfer speeds |

|-------------------------|-----------------------------|-------------------|-------------------------------|

|                         | Transfer speed              | 212 kbit/s        | 424 kbit/s                    |

| PN511 → card            | Modulation on reader side   | 8-30% ASK         | 8-30% ASK                     |

|                         | bit coding                  | Manchester Coding | Manchester Coding             |

|                         | Bitlength                   | (64/13.56) μs     | (32/13.56) μs                 |

| card → PN511            | Loadmodulation on card side | >12% ASK          | >12% ASK                      |

|                         | bit coding                  | Manchester coding | Manchester coding             |

The contactless UART of PN511 and a dedicated external host controller are required to handle the complete FeliCa protocol.

#### 8.1.2.1 FeliCa framing and coding

Table 7. FeliCa framing and coding

|     |     | Prea | mble |     |     | Sy  | nc  | Len | n-Data | CRC |

|-----|-----|------|------|-----|-----|-----|-----|-----|--------|-----|

| 00h | 00h | 00h  | 00h  | 00h | 00h | B2h | 4Dh |     |        |     |

To enable the FeliCa communication a 6 byte preamble (00h, 00h, 00h, 00h, 00h, 00h) and 2 bytes Sync bytes (B2h, 4Dh) are sent to synchronize the receiver.

The following Len byte indicates the length of the sent data bytes plus the LEN byte itself. The CRC calculation is done according to the FeliCa definitions with the MSB first.

To transmit data on the RF interface, the host controller has to send the Len- and databytes to the PN511's FIFO buffer. The preamble and the sync bytes are generated by the PN511 automatically and must not be written to the FIFO by the host controller. The PN511 performs internally the CRC calculation and adds the result to the data frame.

Example for FeliCa CRC Calculation:

Table 8. Start Value for the CRC Polynomial: (00h), (00h)

|     | Preamble |     |     |     | Sy  | nc  | Len | 2 Data | Bytes | CF  | RC  |     |

|-----|----------|-----|-----|-----|-----|-----|-----|--------|-------|-----|-----|-----|

| 00h | 00h      | 00h | 00h | 00h | 00h | B2h | 4Dh | 03h    | ABh   | CDh | 90h | 35h |

### **Transmission Module**

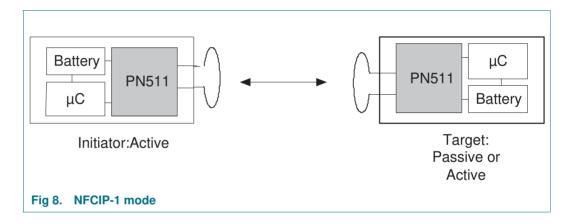

### 8.2 NFCIP-1 mode

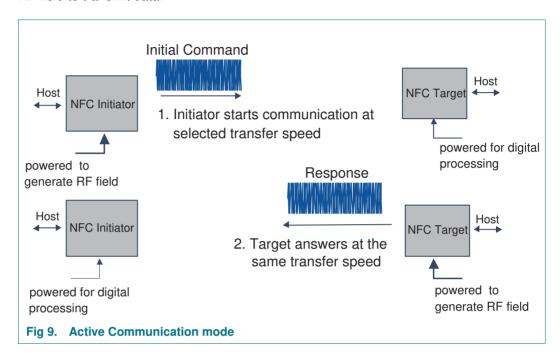

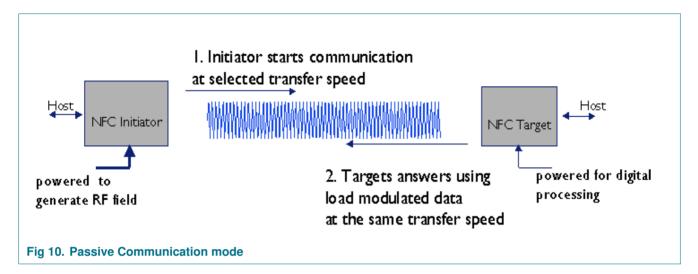

The NFCIP-1 communication differentiates between an active and a Passive Communication mode.

- Active Communication mode means both the initiator and the target are using their own RF field to transmit data.

- Passive Communication mode means that the target answers to an initiator command in a load modulation scheme. The initiator is active in terms of generating the RF field.

- Initiator: generates RF field at 13.56 MHz and starts the NFCIP-1 communication

- Target: responds to initiator command either in a load modulation scheme in Passive Communication mode or using a self generated and self modulated RF field for Active Communication mode.

In order to fully support the NFCIP-1 standard the PN511 supports the Active and Passive Communication mode at the transfer speeds 106 kbit/s, 212 kbit/s and 424 kbit/s as defined in the NFCIP-1 standard.

#### **Transmission Module**

#### 8.2.1 Active Communication mode

Active Communication mode means both the initiator and the target are using their own RF field to transmit data.

Table 9. Communication Overview for Active Communication mode

| Communication direction               | 106 kbit/s                                                          | 212 kbit/s                    | 424 kbit/s | 848 kbit/s                        | 1.69 Mbit/s,<br>3.39 Mbit/s |

|---------------------------------------|---------------------------------------------------------------------|-------------------------------|------------|-----------------------------------|-----------------------------|

| Initiator → Target Target → Initiator | According to<br>ISO 14443A<br>100% ASK,<br>Modified<br>Miller Coded | According to F<br>ASK Manches | ,          | digital capabili<br>this communic | •                           |

The contactless UART of PN511 and a dedicated host controller are required to handle the NFCIP-1 protocol.

Note: Transfer Speeds above 424 kbit/s are not defined in the NFCIP-1 standard. The PN511 supports these transfer speeds only with dedicated external circuits.

#### **Transmission Module**

#### 8.2.2 Passive Communication mode

Passive Communication mode means that the target answers to an initiator command in a load modulation scheme. The initiator is active meaning generating the RF field.

Table 10. Communication Overview for Passive Communication mode

| Communication direction | 106 kbit/s                                                                       | 212 kbit/s                    | 424 kbit/s | 848 kbit/s                       | 1.69 Mbit/s,<br>3.39 Mbit/s |

|-------------------------|----------------------------------------------------------------------------------|-------------------------------|------------|----------------------------------|-----------------------------|

| Initiator → Target      | According to<br>ISO 14443A<br>100% ASK,<br>Modified<br>Miller Coded              | According to F<br>ASK Manches |            | digital capabil<br>this communic | -                           |

| Target → Initiator      | According to<br>ISO 14443A<br>subcarrier load<br>modulation,<br>Manchester Coded | According to F<br>ASK Manches |            |                                  |                             |

The contactless UART of PN511 and a dedicated host controller are required to handle the NFCIP-1 protocol.

Note: Transfer Speeds above 424 kbit/s are not defined in the NFCIP-1 standard. The PN511 supports these transfer speeds only with dedicated external circuits.

#### 8.2.3 NFCIP-1 framing and coding

The NFCIP-1 framing and coding in Active and Passive Communication mode is defined in the NFCIP-1 standard.

**Transmission Module**

Table 11. Framing and Coding Overview

| Transfer speed | Framing and Coding                        |

|----------------|-------------------------------------------|

| 106 kbit/s     | According to the ISO 14443A/Mifare scheme |

| 212 kbit/s     | According to the FeliCa scheme            |

| 424 kbit/s     | According to the FeliCa scheme            |

#### 8.2.4 NFCIP-1 Protocol Support

The NFCIP-1 protocol is not completely described in this document. For detailed explanation of the protocol refer to the NFCIP-1 standard. However the datalink layer is according to the following policy:

- Speed shall not be changed while continuum data exchange in a transaction.

- Transaction includes initialization and anticollision methods and data exchange (in continuous way, meaning no interruption by another transaction).

In order not to disturb current infrastructure based on 13.56 MHz general rules to start NFCIP-1 communication are defined in the following way.

- 1. Per default NFCIP-1 device is in Target mode meaning its RF field is switched off.

- 2. The RF level detector is active.

- 3. Only if application requires the NFCIP-1 device shall switch to Initiator mode.

- 4. Initiator shall only switch on its RF field if no external RF field is detected by RF Level detector during a time of TIDT.

- 5. The initiator performs initialization according to the selected mode.

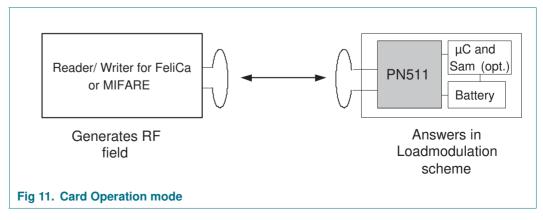

#### 8.3 Card Operation mode

The PN511 can be addressed like a FeliCa or ISO 14443A/Mifare card. This means that the PN511 can generate an answer in a load modulation scheme according to the ISO 14443A/Mifare or FeliCa interface description.

Note: The PN511 does not support a complete card protocol. This has to be handled by a dedicated card SAM or a host controller. The card-SAM is optional.

### 8.3.1 Mifare Card Operation mode

Table 12. Mifare Card Operation mode

| Communication direction   |                           | ISO 14443A/Mifare          | Mifare Higher transfer speeds |                            |

|---------------------------|---------------------------|----------------------------|-------------------------------|----------------------------|

|                           | Transfer speed            | 106 kbit/s                 | 212 kbit/s                    | 424 kbit/s                 |

| reader / writer → PN511   | Modulation on reader side | 100% ASK                   | 100% ASK                      | 100% ASK                   |

|                           | bit coding                | Modified Miller            | Modified Miller               | Modified Miller            |

|                           | Bitlength                 | (128/13.56) μs             | (64/13.56) μs                 | (32/13.56) μs              |

| PN511 → reader/<br>writer | Modulation on PN511 side  | subcarrier load modulation | subcarrier load modulation    | subcarrier load modulation |

|                           | subcarrier<br>frequency   | 13.56 MHz/16               | 13.56 MHz/16                  | 13.56 MHz/16               |

|                           | bit coding                | Manchester coding          | BPSK                          | BPSK                       |

**Transmission Module**

## 8.3.2 FeliCa Card Operation mode

FeliCa Card Operation mode

| Communication direction   |                               | FeliCa                   | FeliCa Higher transfer speeds |  |

|---------------------------|-------------------------------|--------------------------|-------------------------------|--|

|                           | Transfer speed                | 212 kbit/s               | 424 kbit/s                    |  |

| reader/writer →<br>PN511  | Modulation on reader side     | 8-30% ASK                | 8-30% ASK                     |  |

|                           | bit coding                    | Manchester Coding        | Manchester Coding             |  |

|                           | Bitlength                     | (64/13.56) μs            | (32/13.56) μs                 |  |

| PN511 → reader/<br>writer | Load modulation on PN511 side | >12% ASK load modulation | >12% ASK load modulation      |  |

|                           | bit coding                    | Manchester coding        | Manchester coding             |  |

**Transmission Module**

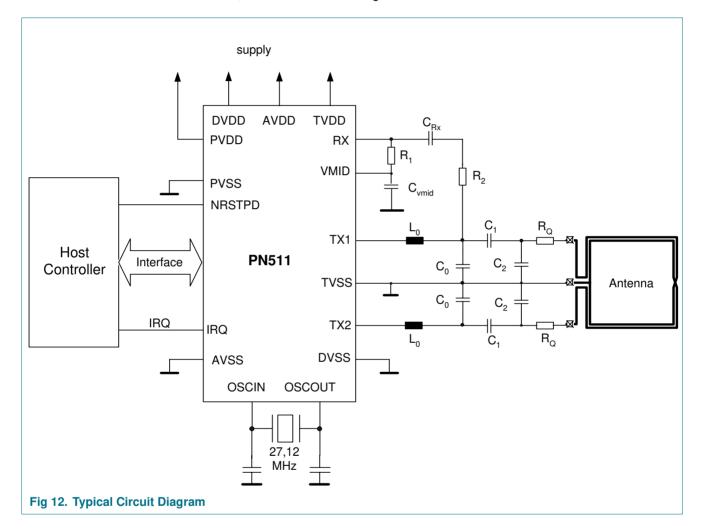

## 9. Application design-in information

The figure below shows a typical circuit diagram, using a complementary antenna connection to the PN511.

The antenna tuning and RF part matching is described in the application note PN511 transceiver IC; Antenna and RF Design Guide

## 10. Limiting values

#### Table 13. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                                                                                      | Conditions                               | Min  | Max  | Unit |

|------------------|------------------------------------------------------------------------------------------------|------------------------------------------|------|------|------|

| $PV_{DD}$        | Supply voltage                                                                                 |                                          | -0.5 | +4.0 | V    |

| P <sub>tot</sub> | Total power dissipation per package ( $V_{\text{BUS}}$ and $DV_{\text{DD}}$ in short cut mode) |                                          | -    | 200  | mW   |

| TJ               | Junction temperature range                                                                     |                                          |      | 100  | °C   |

| ESDH             | ESD Susceptibility (Human Body model)                                                          | 1500 $\Omega$ , 100 pF;<br>JESD22-A114-B |      | 2000 | V    |

| ESDM             | ESD Susceptibility (Machine model)                                                             | 0.75 μH, 200 pF;<br>JESD22-A114-A        |      | 200  | V    |

| ESDC             | ESD Susceptibility (Charge Device model)                                                       | Field induced model;<br>JESC22-C101-A    |      | 1000 | V    |

# 11. Package information

The PN511 can be delivered in 2 different packages.

### Table 14. Package Information

| Package | Remarks                                |

|---------|----------------------------------------|

| HVQFN32 | 8-bit parallel interface not supported |

| HVQFN40 | Supports the 8-bit parallel interface  |

## 12. Abbreviations

#### Table 15. Abbreviations

| Acronym              | Description                                                                                                                                                                              |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASK                  | Amplitude Shift keying                                                                                                                                                                   |

| Initiator            | Generates RF field at 13.56 MHz and starts the NFCIP-1 communication.                                                                                                                    |

| Loadmodulation Index | The load modulation index is defined as the card's voltage ratio (Vmax - Vmin)/ (Vmax + Vmin) measured at the card's coil.                                                               |

| Modulation Index     | The modulation index is defined as the voltage ratio (Vmax - Vmin)/ (Vmax + Vmin).                                                                                                       |

| PCD                  | Proximity Coupling Device. Definition for a Card reader/writer according to the ISO 14443 specification.                                                                                 |

| PICC                 | Proximity Cards. Definition for a contactless Smart Card according to the ISO 14443 specification.                                                                                       |

| $PCD \to PICC$       | Communication flow between a PCD and a PICC according to the ISO 14443A/Mifare.                                                                                                          |

| $PICC \to PCD$       | Communication flow between a PICC and a PCD according to the ISO 14443A/Mifare.                                                                                                          |

| SAM                  | Secure Access Module                                                                                                                                                                     |

| Target               | Responds to initiator command either using load modulation scheme (RF field generated by Initiator) or using modulation of self generated RF field (no RF field generated by initiator). |

**Transmission Module**

NXP Semiconductors PN511

Transmission Module

## 13. Revision history

### Table 16. Revision history

| Decument ID    | Dologoo dota                                                                                                                                | Data shoot status                                | Change notice               | Cuparaadaa          |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------|---------------------|--|

| Document ID    | Release date                                                                                                                                | Data sheet status                                | Change notice               | Supersedes          |  |

| 082733         | Juni 2007                                                                                                                                   | Product short data sheet                         |                             | Revision 3.2        |  |

| Modifications: | <ul> <li>Add <u>Section 1</u></li> </ul>                                                                                                    | 4.4 "Licenses"                                   |                             |                     |  |

| 082732         | Januar 2007                                                                                                                                 | Product short data sheet                         |                             | Revision 3.1        |  |

| Modifications: | <ul> <li>Usage of expi</li> </ul>                                                                                                           | ression "host controller" unified                |                             |                     |  |

|                | <ul> <li>Order informa<br/>PN5110A0HN</li> </ul>                                                                                            | tion "Type number" in <u>Table 2 o</u> l<br>1/C2 | n page 4 updated froi       | m PN5110A0HN1/C1 to |  |

| 082731         | 16 October 2006                                                                                                                             | Product short data sheet                         |                             | Revision 3.0        |  |

| Modifications: | <ul> <li>The format of this data sheet has been redesigned to comply with the new identity guidelines<br/>of NXP Semiconductors.</li> </ul> |                                                  |                             |                     |  |

|                | <ul> <li>Legal texts have been adapted to the new company name where appropriate.</li> </ul>                                                |                                                  |                             |                     |  |

|                | Section 7.2 "Pin description" on page 8:                                                                                                    |                                                  |                             |                     |  |

|                | - corrected in Table 3 "Pin description HVQFN32" Type of Pin 12: 0 -> PWR                                                                   |                                                  |                             |                     |  |

|                | - corrected in Table 4 "Pin description HVQFN40" on page 9 Type of Pin 15: 0 -> PWR                                                         |                                                  |                             |                     |  |

|                | • Section 8.1.2 "FeliCa reader/writer functionality" on page 12:                                                                            |                                                  |                             |                     |  |

|                | - <u>Table 6 "Cor</u>                                                                                                                       | nmunication overview for FeliCa                  | <u>reader/writer"</u> renam | ned Table Title     |  |

| 082730         | 7 July 2006                                                                                                                                 | Product short data sheet                         |                             | Revision 2.0        |  |

| 082720         | 1 February 2004                                                                                                                             | Preliminary short data sheet                     |                             | Revision 1.0        |  |

| 082710         | 1 March 2003                                                                                                                                | Objective short data sheet                       |                             | -                   |  |

|                |                                                                                                                                             |                                                  |                             |                     |  |

**Transmission Module**

## 14. Legal information

#### 14.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 14.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 14.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

**Limiting values** — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 14.4 Licenses

Purchase of an NXP Semiconductors IC that complies with one of the NFC Standards (ISO/IEC18.092; ISO/IEC21.481) does not convey an implied license under any patent right on that standards. A license for the portfolio of the NFC Standards patents of NXP B.V. needs to be obtained at Via Licensing, the pool agent of the NFC Patent Pool, e-mail: info@vialicensing.com

#### 14.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

Mifare — is a trademark of NXP B.V.

### 15. Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### **Transmission Module**

## 16. Tables

| Table 1. Table 2. Table 3. Table 4. Table 5. Table 6. Table 7. Table 8. | Ordering information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 11. Table 12. Table 13. Table 14. Table 15.                                                    | Communication Overview for Active Communication mode Communication Overview for Passive Communication mode Framing and Coding Overview Mifare Card Operation mode Limiting values Package Information Abbreviations Revision history                                                                                                 | . 15<br>. 16<br>. 17<br>. 19<br>. 19                                                               |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 17. F                                                                   | igures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| Fig 1.<br>Fig 2.<br>Fig 3.<br>Fig 4.<br>Fig 5.                          | PN511 Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Fig 7. Fig 8. N<br>Fig 9. A<br>Fig 10. F<br>Fig 11. C                                                | Data Coding and framing according to ISO 14443A.  FeliCa reader/writer Communication Diagram. NFCIP-1 mode  Active Communication mode  Passive Communication mode  Card Operation mode  Typical Circuit Diagram                                                                                                                      | . 12<br>. 13<br>. 14<br>. 15                                                                       |

| 18. C                                                                   | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                      |                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| 1 2 3 4 5 6 7 7.1 7.2 8 8.1.1.1 8.1.2 8.1.2.1 8.2.2 8.2.3               | Introduction         1           General description         1           Features         3           Quick reference data         4           Ordering information         4           Block diagram         5           Pinning information         7           Pinning         7           Pin description         8           Operating modes         10           Reader/Writer mode         10           ISO 14443A/Mifare reader/writer functionality         10           Data Coding and framing according to         15           ISO 14443A/Mifare         11           FeliCa reader/writer functionality         12           FeliCa framing and coding         12           NFCIP-1 mode         13           Active Communication mode         14           Passive Communication mode         15           NFCIP-1 framing and coding         16 | 10 L<br>11 F<br>12 A<br>13 F<br>14 L<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>15 C<br>16 T<br>17 F | NFCIP-1 Protocol Support Card Operation mode Mifare Card Operation mode FeliCa Card Operation mode Application design-in information Limiting values Package information Abbreviations Revision history Legal information Data sheet status Definitions Disclaimers Licenses Trademarks Contact information Tables Figures Contents. | 16<br>17<br>17<br>18<br>19<br>19<br>20<br>21<br>21<br>21<br>21<br>21<br>21<br>21<br>22<br>22<br>22 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2007.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 13 June 2007 Document identifier: 082733