# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

A Product Line of Diodes Incorporated

Real-time Clock Module (I<sup>2</sup>C Bus)

### Features

- Drop-In Replacement for PT7C4363

- Supports High-ESR Crystals Up To 100kΩ

- Using external 32.768kHz quartz crystal

- Supports I<sup>2</sup>C-Bus's high speed mode (400 kHz)

- Includes time (Hour/Minute/Second) and calendar (Year/Month/Date/Day) counter functions (BCD code)

- Programmable square wave output signal

- Oscillator stop flag

- Low backup current: typ. 400nA at  $V_{\rm DD}{=}3.0V$  and  $T_{\rm A}{=}25^{\circ}C$

- Operating range: 1.3V to 5.5V

## Description

The PT7C4363B serial real-time clock is a low-power clock/calendar with a programmable square-wave output.

Address and data are transferred serially via a 2-wire bidirectional bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in the 24-hour format indicator.

Table 1 shows the basic functions of PT7C4363B. More details are shown in section: overview of functions.

| Item |                    | Fund                        | ction            | PT7C4363B              |

|------|--------------------|-----------------------------|------------------|------------------------|

|      | Source: Crystal: 3 |                             | 32.768kHz        | $\checkmark$           |

| 1    | Oscillator         | Oscillator enable           | e/disable        | -                      |

|      |                    | Oscillator fail de          | etect            | ν                      |

|      |                    | Time disular                | 12-hour          | -                      |

| 2    |                    | Time display                | 24-hour          | ν                      |

| 2    | Time               | Century bit                 |                  | ν                      |

|      |                    | Time count chai             | n enable/disable | ν                      |

| 3    | Interment          | Alarm interrupt             |                  | √                      |

| 3    | Interrupt          | Timer interrupt             | output           | √                      |

| 4    | Programmable       | square wave outp            | ut (Hz)          | 1, 32, 1.024k, 32.768k |

|      | Communicati        | 2-wire I <sup>2</sup> C bus |                  | √                      |

| 5    | Communicati<br>on  | 3-wire bus                  |                  | -                      |

|      | on                 | Burst mode                  |                  | -                      |

|      |                    | Write protection            |                  | -                      |

| 6    | 6 Control Ext      |                             | est mode         | ν                      |

|      |                    | Power-on reset              | override         | $\checkmark$           |

#### **Table 1.** Basic functions of PT7C4363B

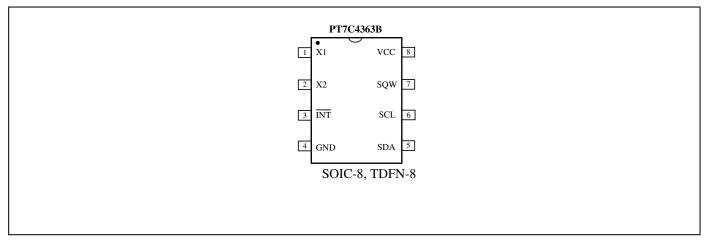

## **Pin Configuration**

## **Pin Description**

| Pin# | Pin | Туре | Description                                                                                                                                                               |

|------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | X1  | Ι    | Oscillator Circuit Input. Together with X2, 32.768kHz crystal is connected between them.                                                                                  |

| 2    | X2  | 0    | Oscillator Circuit Output. Together with X1, 32.768kHz crystal is connected between them.                                                                                 |

| 3    | INT | 0    | Interrupt Output. Open drain, active low.                                                                                                                                 |

| 4    | GND | Р    | Ground.                                                                                                                                                                   |

| 5    | SDA | I/O  | <b>Serial Data Input/Output.</b> SDA is the input/output pin for the 2-wire serial interface. The SDA pin is open-drain output and requires an external pull-up resistor. |

| 6    | SCL | Ι    | Serial Clock Input. SCL is used to synchronize data movement on the I <sup>2</sup> C serial interface.                                                                    |

| 7    | SQW | 0    | <b>Clock Output.</b> Open drain. Four frequencies selectable: 32.768k, 1.024k, 32, 1Hz when SQWE bit is set to 1.                                                         |

| 8    | VCC | Р    | Power.                                                                                                                                                                    |

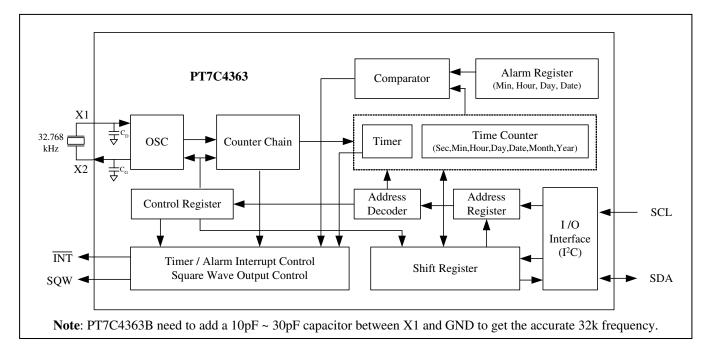

## **Function Block**

## **Maximum Ratings**

| Storage Temperature                             | 65°Cto +150°C                   |

|-------------------------------------------------|---------------------------------|

| Junction Temperature                            |                                 |

| Supply Voltage to Ground Potential (Vcc to GND) | -0.3V to +6.5V                  |

| DC Input (All Other Inputs except Vcc & GND)    | 0.3V to (V <sub>cc</sub> +0.3V) |

| DC Output Voltage (SDA, /INTA, /INTB pins)      | -0.3V to +6.5V                  |

| Power Dissipation                               |                                 |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended Operating Conditions**

| Symbol          | Description           | Min.                | Тур. | Max.                 | Unit |

|-----------------|-----------------------|---------------------|------|----------------------|------|

| V <sub>CC</sub> | Power voltage         | 1.3                 | -    | 5.5                  |      |

| V <sub>IH</sub> | Input high level      | 0.7 V <sub>CC</sub> | -    | V <sub>CC</sub> +0.3 | V    |

| V <sub>IL</sub> | Input low level       | -0.3                | -    | $0.3 V_{CC}$         |      |

| T <sub>A</sub>  | Operating temperature | -40                 | -    | 85                   | °C   |

## **DC Electrical Characteristics**

Unless otherwise specified, GND =0V,  $V_{CC}$  = 1.3 ~ 5.5 V,  $T_A$  = -40 °C to +85 °C,  $f_{OSC}$  = 32.768kHz.

| Sym.             | Description                                                                | Pin             | Conditions                                                                      | Min.                                 | Тур.        | Max. | Unit            |          |

|------------------|----------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------|--------------------------------------|-------------|------|-----------------|----------|

|                  | Supply voltage                                                             | V               | Interface inactive. $T_A = 25^{\circ}C^{(1)}$                                   |                                      | 1.1         | -    | 5.5             |          |

| V <sub>CC</sub>  | Supply voltage                                                             | V <sub>CC</sub> | Interface active. $f_{SCL} = 400 \text{kHz}$ ,                                  | $T_{\rm A} = 25^{\circ} {\rm C}^{1}$ | 1.3         | -    | 5.5             | v        |

| V CC             | Supply voltage for clock data integrity                                    | V <sub>CC</sub> | -                                                                               |                                      | 1.1         | -    | 5.5             | V        |

| I <sub>CCA</sub> | Active Supply current $V_{CC}$ Interface active $f_{SCL} = 400 \text{kHz}$ |                 | $f_{SCL} = 400 \text{kHz}$                                                      | -                                    | -           | 35   |                 |          |

| ICCA             | Active Supply cullent                                                      | • CC            | Interface active                                                                | $f_{SCL} = 100 kHz$                  | -           | -    | 15              | μA       |

|                  |                                                                            |                 | Interface inactive ( $f_{SCL} = 0Hz$ ),                                         | $V_{\rm CC} = 5.0 V$                 | -           | 450  | 700             | nA       |

|                  |                                                                            |                 | pin 7 disabled <sup>2)</sup> $T_A$ =-40~85°C                                    | $V_{\rm CC} = 3.0 V$                 | -           | 400  | 650             | шл       |

| I <sub>CCS</sub> | Standby current                                                            | V <sub>CC</sub> | Interface inactive ( $f_{SCL} = 0Hz$ ),                                         | -                                    | 650         | 900  |                 |          |

|                  |                                                                            |                 | pin 7 enabled at $32$ kHz <sup>2)</sup> T <sub>A</sub> =- $40$ ~ $85^{\circ}$ C | $V_{CC} = 3.0V$                      | -           | 600  | 850             | nA       |

| V <sub>IL1</sub> | Low-level input voltage                                                    | SCL             | -                                                                               |                                      | 0           | -    | $0.3V_{CC}$     | v        |

| V <sub>IH1</sub> | High-level input voltage                                                   | SCL             | -                                                                               |                                      | $0.7V_{CC}$ | -    | V <sub>CC</sub> | <b>v</b> |

| т                | Low-level output voltage                                                   | SDA             | $V_{OL} = 0.4V, V_{CC} = 5V$                                                    |                                      | -3          | -    | -               | mA       |

| I <sub>OL</sub>  | Low-level output voltage                                                   | /INT, SQW       | $V_{OL} = 0.4V, V_{CC} = 5V$                                                    |                                      | -1          | -    | -               | IIIA     |

| I <sub>IL</sub>  | Input leakage current                                                      | SCL             | -                                                                               | -1                                   | -           | 1    | μΑ              |          |

| I <sub>OZ</sub>  | Output current when OFF                                                    | -               | -                                                                               |                                      | -1          | -    | 1               | μΑ       |

Note:

1) For reliable oscillator start-up at power-up:  $V_{CC(min)power-up} = V_{CC(min)} + 0.3 V.$ 2) Timer source clock =  ${}^{1}/_{60}$  Hz, voltage of SCL and SDA is V<sub>CC</sub> or GND.

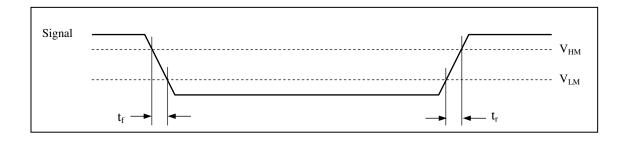

## **AC Electrical Characteristics**

| Sym             | Description                               | Value               | Unit |

|-----------------|-------------------------------------------|---------------------|------|

| V <sub>HM</sub> | Rising and falling threshold voltage high | 0.8 V <sub>CC</sub> | V    |

| V <sub>HL</sub> | Rising and falling threshold voltage low  | 0.2 V <sub>CC</sub> | V    |

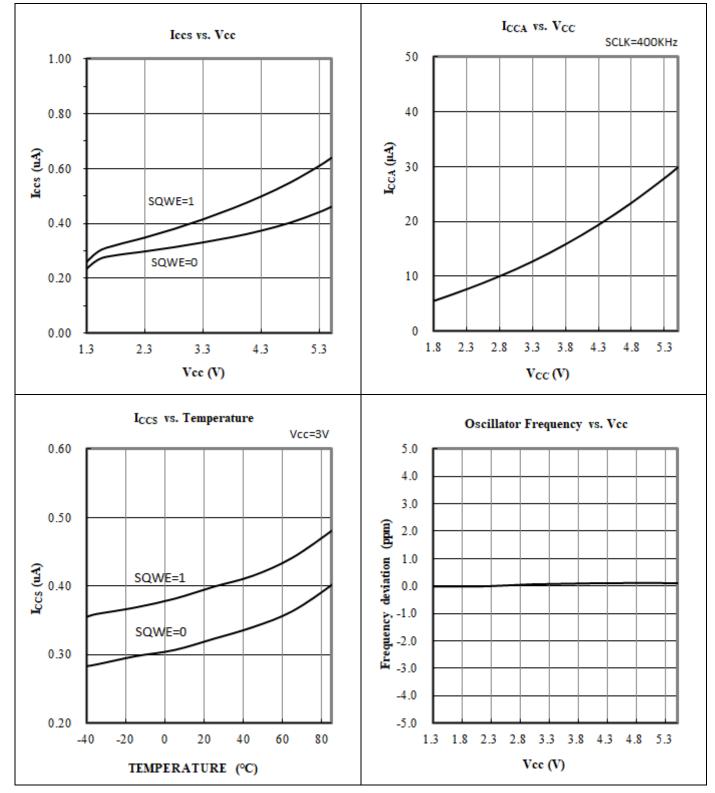

## **Typical Operation Characteristics**

Unless otherwise specified,  $V_{CC} = 3.3V$ ,  $T_A = 25$  °C

## Over the operating range

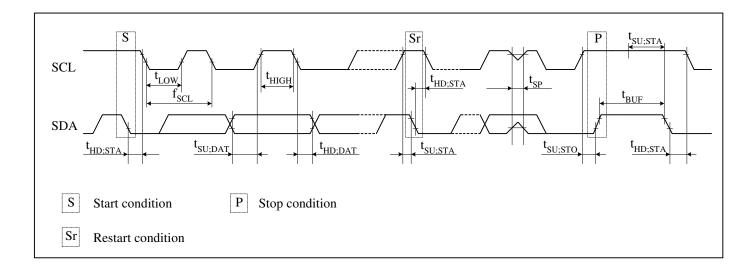

| Symbol               | Item                                             | Min. | Typ. | Max. | Unit |

|----------------------|--------------------------------------------------|------|------|------|------|

| f <sub>SCL</sub>     | SCL clock frequency                              | -    | -    | 400  | kHz  |

| t <sub>SU;STA</sub>  | START condition set-up time                      | 0.6  | -    | -    | μs   |

| t <sub>HD;STA</sub>  | START condition hold time                        | 0.6  | -    | -    | μs   |

| t <sub>SU;DAT</sub>  | Data set-up time (RTC read/write)                | 200  | -    | -    | ns   |

| t <sub>HD;DAT1</sub> | Data hold time (RTC write)                       | 35   | -    | -    | ns   |

| t <sub>HD;DAT2</sub> | Data hold time (RTC read)                        | 0    | -    | -    | μs   |

| t <sub>SU;STO</sub>  | STOP condition setup time                        | 0.6  | -    | -    | μs   |

| t <sub>BUF</sub>     | Bus idle time between a START and STOP condition | 1.3  | -    | -    | μs   |

| t <sub>LOW</sub>     | When SCL = "L"                                   | 1.3  | -    | -    | μs   |

| t <sub>HIGH</sub>    | When SCL = "H"                                   | 0.6  | -    | -    | μs   |

| t <sub>r</sub>       | Rise time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| t <sub>f</sub>       | Fall time for SCL and SDA                        | -    | -    | 0.3  | μs   |

| t <sub>SP</sub> *    | Allowable spike time on bus                      | -    | -    | 50   | ns   |

| C <sub>B</sub>       | Capacitance load for each bus line               | -    | -    | 400  | pF   |

\* Note: Only reference for design.

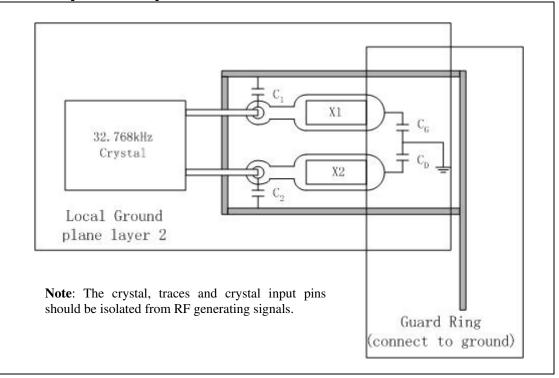

## **Recommended Layout for Crystal**

## Built-in Capacitors Specifications and Recommended External Capacitors

| Parameter            |           | Symbol         | Тур. | Unit |

|----------------------|-----------|----------------|------|------|

| Build-in capacitors  | X1 to GND | $C_{G}$        | 5    | pF   |

| Build-III capacitors | X2 to GND | C <sub>D</sub> | 20   | pF   |

| Recommended External | X1 to GND | $C_1$          | 20   | pF   |

| capacitors           | X2 to GND | $C_2$          | 0    | pF   |

Note: The frequency of crystal can be optimized by external capacitor C<sub>1</sub> and C<sub>2</sub>, for frequency=32.768Hz, C<sub>1</sub> and C<sub>2</sub> should meet the equation as below:

$Cpar + [(C_1+C_G)^*(C_2+C_D)]/[(C_1+C_G)+(C_2+C_D)] = C_L$

Cpar is all parasitical capacitor between X1 and X2.

C<sub>L</sub> is crystal's load capacitance.

#### **Crystal Specifications**

| Parameter         | Symbol         | Min. | Тур.   | Max. | Unit |

|-------------------|----------------|------|--------|------|------|

| Nominal Frequency | $f_0$          | -    | 32.768 | -    | kHz  |

| Series Resistance | ESR            | -    | -      | 100  | kΩ   |

| Load Capacitance  | C <sub>L</sub> | -    | 12.5   | -    | pF   |

## **Function Description**

## **Overview of Functions**

#### 1. Clock function

CPU can read or write data including the year (last two digits), month, date, day, hour, minute, and second. Any (two-digit) year that is a multiple of 4 is treated as a leap year and calculated automatically as such until the year 2100.

#### 2. Alarm function

These devices have one alarm system that outputs interrupt signals from INT for PT7C4363B to CPU when the date, day of the week, hour, minute or second correspond to the setting. Each of them may output interrupt signal separately at a specified time. The alarm may be selectable between on and off for matching alarm or repeating alarm.

#### 3. Programmable square wave output

A square wave output enable bit controls square wave output at pin 7. Four frequencies are selectable: 1, 32, 1.024k, and

32.768kHz.

#### 4. Interface with CPU

Data is read and written via the I<sup>2</sup>C bus interface using two signal lines: SCL (clock) and SDA (data).

Since the output of the I/O pin SDA is open drain, a pull-up resistor should be used on the circuit board if the CPU output I/O is

also open drain.

The SCL's maximum clock frequency is 400 kHz, which supports the I<sup>2</sup>C bus's high-speed mode.

#### 5. Oscillator fail detect

When oscillator fail, OSF bit will be set.

#### 6. Oscillator enable/disable

Only time count chain can be enable or disable by STOP bit.

#### 7. Timer function

The timer control register determines one of 4 source clock frequencies for the timer (4096 Hz, 64 Hz, 1 Hz, or 1/60 Hz) and enables or disables the timer. The timer counts down from software loaded 8-bit binary value. At the end of every countdown, the timer sets the Timer Flag (TF). The TF may only be cleared by software. The asserted TF can be used to generate an interrupt. The interrupt may be generated as a pulsed signal every countdown period or as a permanently active signal which follows the condition of TF. Bit TI/TP is used to control this mode selection. When reading the timer, the current countdown value is returned.

#### 8. Reset function

The PT7C4363B includes an internal reset circuit which is active whenever the oscillator is stopped. In the reset state the I<sup>2</sup>C-bus logic is initialized and all registers, including the address pointer, are cleared with the exception of bits FE, OSF, TD1, TD0, TESTC and AE which are set to logic 1.

A Product Line of Diodes Incorporated

## Registers

#### 1. Allocation of registers

| Addr.    | Function (time range     |                     |       |                        | Register            | definition          |                    |                    |                    |

|----------|--------------------------|---------------------|-------|------------------------|---------------------|---------------------|--------------------|--------------------|--------------------|

| (hex) *1 | BCD format)              | Bit 7               | Bit 6 | Bit 5                  | Bit 4               | Bit 3               | Bit 2              | Bit 1              | Bit 0              |

| 00       | Control/status 1         | TEST1 <sup>*2</sup> | -     | STOP <sup>*3</sup>     | -                   | TESTC <sup>*4</sup> | -                  | -                  | -                  |

| 01       | Control/status 2         | -                   | -     | -                      | TI/TP <sup>*5</sup> | $AF^{*6}$           | $\mathrm{TF}^{*6}$ | AIE <sup>*7</sup>  | TIE <sup>*7</sup>  |

| 02       | Seconds (00-59)          | OSF <sup>*8</sup>   | S40   | S20                    | S10                 | <b>S</b> 8          | <b>S</b> 4         | S2                 | S1                 |

| 03       | Minutes (00-59)          | ×                   | M40   | M20                    | M10                 | M8                  | M4                 | M2                 | M1                 |

| 04       | Hours (00-23)            | ×                   | ×     | H20                    | H10                 | H8                  | H4                 | H2                 | H1                 |

| 05       | Dates (01-31)            | х                   | ×     | D20                    | D10                 | D8                  | D4                 | D2                 | D1                 |

| 06       | Days of the week (00-06) | ×                   | ×     | ×                      | ×                   | ×                   | W4                 | W2                 | W1                 |

| 07       | Months (01-12)           | Century             | ×     | ×                      | MO10                | MO8                 | MO4                | MO2                | MO1                |

| 08       | Years (00-99)            | Y80                 | Y40   | Y20                    | Y10                 | Y8                  | Y4                 | Y2                 | Y1                 |

| 09       | Alarm: Minutes (00-59)   | AE <sup>*9</sup>    | M40   | M20                    | M10                 | M8                  | M4                 | M2                 | M1                 |

| 0A       | Alarm: Hours (01-12)     | AE <sup>*9</sup>    | ×     | H20                    | H10                 | H8                  | H4                 | H2                 | H1                 |

| 0B       | Alarm: Dates (01-31)     | AE <sup>*9</sup>    | ×     | D20                    | D10                 | D8                  | D4                 | D2                 | D1                 |

| 0C       | Alarm: Weekday (00-06)   | AE <sup>*9</sup>    | ×     | ×                      | ×                   | ×                   | W4                 | W2                 | W1                 |

| 0D       | SQW control              | SQWE                | ×     | ×                      | ×                   | ×                   | ×                  | RS1                | RS0                |

| 0E       | Timer control            | $TE^{*10}$          | ×     | ×                      | ×                   | ×                   | ×                  | TD1 <sup>*11</sup> | TD0 <sup>*11</sup> |

| 0F       | Timer                    |                     |       | Timer count down value |                     |                     |                    |                    |                    |

Caution points:

\*1. PT7C4363B uses 8 bits for address. For excess 0FH address, PT7C4363B will not respond.

\*2. EXT\_CLK test mode select bit.

\*3. When the bit is logic 1, time count chain stops but oscillator still runs.

\*4. Power-on reset override enable bit.

\*5. Timer interrupt output select bit.

\*6. Alarm and timer interrupt flag bits.

\*7. Alarm and timer interrupt enable bits.

\*8. Oscillator fail indicates. Indicate clock integrity.

\*9. Alarm enable bit. Alarm will be active when related time is matching if AE = 0.

\*10. Timer enable bit.

\*11. Timer source clock frequency select.

\*12. All bits marked with "×" are not implemented. All bits marked with "-" are not used bits and should always be written with logic 0. If read them, they could be logic 0 or 1.

#### 2. Control and status register

| Addr.<br>(hex) | Description      | D7        | D6        | D5        | D4          | D3         | D2        | D1        | D0        |

|----------------|------------------|-----------|-----------|-----------|-------------|------------|-----------|-----------|-----------|

| 00             | Control/status 1 | TEST1     | -         | STOP      | -           | TESTC      | -         | -         | -         |

| 00             | (default)        | 0         | Undefined | 0         | Undefined   | 1          | Undefined | Undefined | Undefined |

| 01             | Control/status 2 | -         | -         | -         | TI/TP       | AF         | TF        | AIE       | TIE       |

| 01             | (default)        | Undefined | Undefined | Undefined | 0           | Undefined  | Undefined | 0         | 0         |

| 0D             | SQW control      | SQWE      | ×         | ×         | ×           | ×          | ×         | RS1       | RS0       |

| 012            | (default)        | 1         | Undefined | Undefined | Undefined   | Undefined  | Undefined | 0         | 0         |

| 0E             | Timer control    | TE        | ×         | ×         | ×           | ×          | ×         | TD1       | TD0       |

| 0L             | (default)        | 0         | Undefined | Undefined | Undefined   | Undefined  | Undefined | 1         | 1         |

| 0F             | Timer            |           |           |           | Timer count | down value |           |           |           |

| UI.            | (default)        |           |           |           | Unde        | efined     |           |           |           |

#### a) Timer

#### • **TE:** Timer Enable bit.

| TE           | Data | Description    |         |

|--------------|------|----------------|---------|

| Read / Write | 0    | Timer disabled | Default |

| Keau / White | 1    | Timer enabled  |         |

#### • TD1, TD0: timer source clock frequency select. These bits determine the source clock for the countdown timer.

| TD1, TD0     | Data |        | Timer source clock freq. (Hz)                                  |  |  |  |  |

|--------------|------|--------|----------------------------------------------------------------|--|--|--|--|

|              | 00   | 4.096k |                                                                |  |  |  |  |

| Read / Write | 01   | 64     |                                                                |  |  |  |  |

| Keau / Wille | 10   | 1      |                                                                |  |  |  |  |

|              | 11   | 1/60   | When not in use, TD1 TD0 should be set to 11 for power saving. |  |  |  |  |

#### • Timer:

| ſ | Timer        | Data  | Description          |                                               |

|---|--------------|-------|----------------------|-----------------------------------------------|

|   | Read / Write | 00~FF | Count down value (n) | Countdown Period = n / Source Clock Frequency |

For example: If TE = 1, TD1 TD0 = 10, Timer = 03 are written into PT7C4363B, timer counts down every 1 second from 03 to 01 then 03 cycled.

#### b) Timer Interrupt

#### • **TIE:** Timer Interrupt Enable bit.

| TIE          | Data | Description              |         |

|--------------|------|--------------------------|---------|

| Read / Write | 0    | Timer interrupt disabled | Default |

|              | 1    | Timer interrupt enabled  |         |

#### • **TF:** Timer Flag

| TF    | Data | Description                                                         |  |  |

|-------|------|---------------------------------------------------------------------|--|--|

| Read  | 0    | Timer flag inactive                                                 |  |  |

|       | 1    | Timer flag active. At the end of a timer countdown, TF is set to 1. |  |  |

| Write | 0    | Timer flag is cleared                                               |  |  |

| wille | 1    | Timer flag remains unchanged                                        |  |  |

#### • **TI/TP:** Timer Interrupt output select

| TI/TP        | Data |                                               | Description                                                                                                     |                                |                                      |               |  |  |  |

|--------------|------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|---------------|--|--|--|

|              | 0    | $\overline{INT}$ is active when TF            | INT is active when TF is active (subject to the status of TIE)                                                  |                                |                                      |               |  |  |  |

|              |      | INT pulses active account the status of TIE). | INT pulses active according to source clock frequency and timer count down value (subject to the status of TIE) |                                |                                      |               |  |  |  |

|              |      | , ,                                           | Source clock                                                                                                    | INT negative pulse width (s)   |                                      |               |  |  |  |

|              |      |                                               | (Hz)                                                                                                            | n = 1                          | n > 1                                |               |  |  |  |

| Read / Write |      |                                               | 4096                                                                                                            | <sup>1</sup> / <sub>8192</sub> | <sup>1</sup> / <sub>4096</sub>       |               |  |  |  |

| Keau / Wille | 1    |                                               | 64                                                                                                              | <sup>1</sup> / <sub>128</sub>  | <sup>1</sup> / <sub>64</sub>         |               |  |  |  |

|              |      |                                               | 1                                                                                                               | <sup>1</sup> / <sub>64</sub>   | <sup>1</sup> / <sub>64</sub>         |               |  |  |  |

|              |      |                                               | 1/60                                                                                                            | <sup>1</sup> / <sub>64</sub>   | <sup>1</sup> / <sub>64</sub>         |               |  |  |  |

|              |      | И                                             | Note: TF and INT<br>n = loaded c                                                                                |                                | imultaneously.<br>. Timer stopped wl | hen $n = 0$ . |  |  |  |

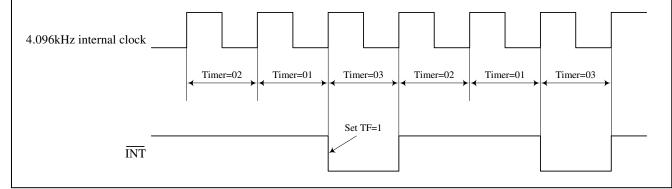

*Example 1*: If TE = 1, TD1 TD0 = 00, Timer = 03, TIE = 1, TF = 0, TI/TP = 1 are written into PT7C4363B, timer register counts down every  $\frac{1}{4.096 \text{ kHz}}$  seconds from 03 to 01 then 03 cycled and INT output negative pulse with  $\frac{1}{4096}$  seconds width. See Fig.1.

#### Fig.1 Example 1 of timer interrupts

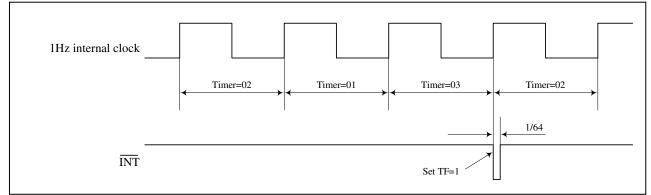

## *Example 2:* If TE = 1, TD1 TD0 = 10, Timer = 03, TIE = 1, TF = 0, TI/TP = 1 are written into PT7C4363B, timer counts down every $\frac{1}{4.096kHz}$ seconds from 03 to 01 then 03 cycled and INT output negative pulse with $\frac{1}{64}$ seconds width. See Fig.2.

#### Fig.2 Example 2 of timer interrupts

#### c) Alarm Interrupt

#### • AIE: Alarm Interrupt Enable bit.

| AIE          | Data | Description              |         |  |  |

|--------------|------|--------------------------|---------|--|--|

| Read / Write | 0    | Alarm interrupt disabled | Default |  |  |

| Read / Write | 1    | Alarm interrupt enabled  |         |  |  |

#### • **AF:** Alarm Flag

| AF      | Data | Description                  |

|---------|------|------------------------------|

| Read    | 0    | Alarm flag inactive          |

| Keau    | 1    | Alarm flag active            |

| Write – | 0    | Alarm flag is cleared        |

|         | 1    | Alarm flag remains unchanged |

#### d) SQW control

#### • **SQWE:** SQW output clock enable bit.

| SQWE         | Data | Description                                                         |         |  |

|--------------|------|---------------------------------------------------------------------|---------|--|

| Read / Write | 0    | the SQW output is inhibited and SQW output is set to high-impedance |         |  |

| Keau / Wille | 1    | the SQW output is activated                                         | Default |  |

#### • **RS1, RS0:** SQW output frequency select.

| RS1, RS0     | Data |         | SQW output freq. (Hz) |

|--------------|------|---------|-----------------------|

| Read / Write | 00   | 32.768k | Default               |

|              | 01   | 1.024k  |                       |

|              | 10   | 32      |                       |

|              | 11   | 1       |                       |

#### e) Time count

#### • STOP

| STOP                                                                                                                                      | Data | Description                                                                                                                      |         |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

|                                                                                                                                           | 0    | RTC source clock runs.                                                                                                           | Default |  |  |  |

| Read / Write     All RTC divider chain flip-flops are asynchronously set to logic 0; the RTC clock (SQW at 32.768 kHz is still available) |      | All RTC divider chain flip-flops are asynchronously set to logic 0; the RTC clock is stop (SQW at 32.768 kHz is still available) | oped    |  |  |  |

#### f) Test

#### • TEST1

| TEST1        | Data | Description        |         |

|--------------|------|--------------------|---------|

| Pand / Write | 0    | Normal mode.       | Default |

| Read / Write | 1    | EXT_CLK test mode. |         |

#### • TESTC

| TESTC        | Data | Description                                                                        |         |

|--------------|------|------------------------------------------------------------------------------------|---------|

| Read / Write | 0    | Power-on reset override facility is disabled; set to logic 0 for normal operation. |         |

| Keau / Wille | 1    | Power-on reset override may be enabled                                             | Default |

#### 3. Time Counter

Time digit display (in BCD code):

- Second digits: Range from 00 to 59 and carried to minute digits when incremented from 59 to 00.

- Minute digits: Range from 00 to 59 and carried to hour digits when incremented from 59 to 00.

- Hour digits: See description on the /12, 24 bit. Carried to day and day-of-the-week digits when incremented from 11 p.m. to 12 a.m. or 23 to 00.

| Addr.<br>(hex) | Description | D7                  | D6        | D5        | D4        | D3        | D2        | D1        | D0         |

|----------------|-------------|---------------------|-----------|-----------|-----------|-----------|-----------|-----------|------------|

| 02             | Seconds     | $\mathbf{OSF}^{*1}$ | S40       | S20       | S10       | S8        | S4        | S2        | <b>S</b> 1 |

| 02             | (default)   | 1                   | Undefined  |

| 03             | Minutes     | ×                   | M40       | M20       | M10       | M8        | M4        | M2        | M1         |

| 05             | (default)   | 0                   | Undefined  |

| 04             | Hours       | ×                   | ×         | H20       | H10       | H8        | H4        | H2        | H1         |

| 51             | (default)   | 0                   | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined  |

\*1 Note: Indicate clock integrity. When the bit is 1, the clock integrity is no longer guaranteed and the time need be adjusted.

#### 4. Days of the week Counter

The day counter is a divide-by-7 counter that counts from 00 to 06 and up 06 before starting again from 00. Values that correspond to the day of week are user defined but must be sequential (i.e., if 0 equals Sunday, then 1 equals Monday, and so on). Illogical time and date entries result in undefined operation.

| Addr.<br>(hex) | Description      | D7 | D6 | D5 | D4 | D3 | D2        | D1        | D0        |

|----------------|------------------|----|----|----|----|----|-----------|-----------|-----------|

| 06             | Days of the week | ×  | ×  | ×  | ×  | ×  | W4        | W2        | W1        |

| 00             | (default)        | 0  | 0  | 0  | 0  | 0  | Undefined | Undefined | Undefined |

#### 5. Calendar Counter

The data format is BCD format.

- Day digits: Range from 1 to 31 (for January, March, May, July, August, October and December).

- Range from 1 to 30 (for April, June, September and November).

- Range from 1 to 29 (for February in leap years).

- Range from 1 to 28 (for February in ordinary years).

- Carried to month digits when cycled to 1.

- Month digits: Range from 1 to 12 and carried to year digits when cycled to 1.

- Year digits: Range from 00 to 99 and 00, 04, 08, ..., 92 and 96 are counted as leap years.

| Addr.<br>(hex) | Description | D7                    | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|----------------|-------------|-----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 05             | Dates       | ×                     | ×         | D20       | D10       | D8        | D4        | D2        | D1        |

| 05             | (default)   | 0                     | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 07             | Months      | Century <sup>*1</sup> | ×         | ×         | M10       | M8        | M4        | M2        | M1        |

| 07             | (default)   | Undefined             | 0         | 0         | Undefined | Undefined | Undefined | Undefined | Undefined |

| 08             | Years       | Y80                   | Y40       | Y20       | Y10       | Y8        | Y4        | Y2        | Y1        |

|                | (default)   | Undefined             | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

\*1: The century bit is toggled when the years register overflows from 99 to 00.

#### 6. Alarm Register

#### PT7C4363B: Alarm Register

| Addr. | Description    | D7               | D6        | D5        | D4        | D3        | D2        | D1        | D0        |

|-------|----------------|------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 09    | Alarm: Minutes | $AE^{*1}$        | M40       | M20       | M10       | M8        | M4        | M2        | M1        |

| 07    | (default)      | Undefined        | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 0A    | Alarm: Hours   | $AE^{*2}$        | ×         | H20       | H10       | H8        | H4        | H2        | H1        |

| 011   | (default)      | Undefined        | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 0B    | Alarm: Dates   | AE <sup>*3</sup> | ×         | D20       | D10       | D8        | D4        | D2        | D1        |

| 0D    | (default)      | Undefined        | 0         | Undefined | Undefined | Undefined | Undefined | Undefined | Undefined |

| 0C    | Alarm: Weekday | $AE^{*4}$        | ×         | х         | ×         | ×         | W4        | W2        | W1        |

| 00    | (default)      | Undefined        | 0         | 0         | 0         | 0         | Undefined | Undefined | Undefined |

\*1 Note: Minute alarm enable bit.

\*2 Note: Hour alarm enable bit.

\*3 Note: Date alarm enable bit.

\*4 Note: Weekday alarm enable bit.

## **Alarm Function**

|    | Function         |       |       |       | Register | definition |            |       |            |

|----|------------------|-------|-------|-------|----------|------------|------------|-------|------------|

|    | Function         | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3      | Bit 2      | Bit 1 | Bit 0      |

| 01 | Control/status 2 | -     | -     | -     | TI/TP    | AF         | TF         | AIE   | TIE        |

| 02 | Seconds          | OSF   | S40   | S20   | S10      | <b>S</b> 8 | <b>S</b> 4 | S2    | <b>S</b> 1 |

| 03 | Minutes          | ×     | M40   | M20   | M10      | M8         | M4         | M2    | M1         |

| 04 | Hours            | ×     | ×     | H20   | H10      | H8         | H4         | H2    | H1         |

| 05 | Dates            | ×     | ×     | D20   | D10      | D8         | D4         | D2    | D1         |

| 06 | Days of the week | ×     | ×     | ×     | ×        | ×          | W4         | W2    | W1         |

| 09 | Alarm: Minutes   | AE    | M40   | M20   | M10      | M8         | M4         | M2    | M1         |

| 0A | Alarm: Hours     | AE    | ×     | H20   | H10      | H8         | H4         | H2    | H1         |

| 0B | Alarm: Dates     | AE    | ×     | D20   | D10      | D8         | D4         | D2    | D1         |

| 0C | Alarm: Weekday   | AE    | ×     | ×     | ×        | ×          | W4         | W2    | W1         |

Related register

When one or more of these registers are loaded with a valid minute, hour, day or weekday and its corresponding bit Alarm Enable (AE) is logic 0, then that information will be compared with the current minute, hour, day and weekday. When all enabled comparisons first match, the Alarm Flag (AF) is set. AF will remain set until cleared by software. Once AF has been cleared it will only be set again when the time increments to match the alarm condition once more. Alarm registers which have their bit AE at logic 1 will be ignored.

## EXT\_CLK Test Mode and POR override

## 1. EXT\_CLK Test Mode

A test mode is available which allows for on-board testing. In such a mode it is possible to set up test conditions and control the operation of the RTC. The test mode is entered by setting bit TEST1 in control/status1 register. Then pin SQW becomes an input. The test mode replaces the internal 64 Hz signal with the signal applied to pin SQW. Every 64 positive edges applied to pin SQW will then generate an increment of one second.

The signal applied to pin SQW should have a minimum pulse width of 300 ns and a minimum period of 1000 ns. The internal 64 Hz clock, now sourced from SQW, is divided down to 1 Hz by a 2<sup>6</sup> divide chain called a pre-scaler. The pre-scaler can be set into a known state by using bit STOP. When bit STOP is set, the pre-scaler is

reset to 0 (STOP must be cleared before the pre-scaler can operate again).

From a STOP condition, the first 1 second increment will take place after 32 positive edges on SQW. Thereafter, every 64 positive edges will cause a 1 second increment.

**Remark:** Entry into EXT\_CLK test mode is not synchronized to the internal 64 Hz clock. When entering the test mode, no assumption as to the state of the pre-scaler can be made.

#### Operation example:

- 1. Set EXT\_CLK test mode (control/status 1, bit TEST1 = 1)

- 2. Set STOP (control/status 1, bit STOP = 1)

- 3. Clear STOP (control/status 1, bit STOP = 0)

- 4. Set time registers to desired value

- 5. Apply 32 clock pulses to SQW

- 6. Read time registers to see the first change

- 7. Apply 64 clock pulses to SQW

- 8. Read time registers to see the second change.

Repeat 7 and 8 for additional increments.

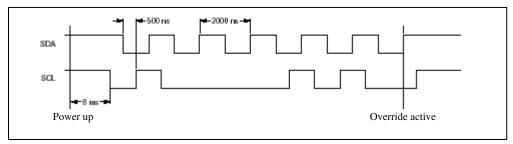

#### 2. Power-On Reset (POR) override

The POR duration is directly related to the crystal oscillator start-up time. Due to the long start-up times experienced by these types of circuits, a mechanism has been built in to disable the POR and hence speed up on-board test of the device. The setting of this mode requires that the I<sup>2</sup>C-bus pins, SDA and SCL, be toggled in a specific order as shown in Fig 6.4.2. All timings are required minimums.

Once the override mode has been entered, the device immediately stops being reset and normal operation may commence i.e. entry into the EXT\_CLK test mode via I<sup>2</sup>C-bus access.

The override mode may be cleared by writing a logic 0 to TESTC. TESTC must be set to logic 1 before re-entry into the override mode is possible. Setting TESTC to logic 0 during normal operation has no effect except to prevent from entering the POR override mode.

Fig.3 POR override sequence

## Communication

#### 1. I<sup>2</sup>C Bus Interface

#### a) Overview of I<sup>2</sup>C-BUS

The I<sup>2</sup>C bus supports bi-directional communications via two signal lines: the SDA (data) line and SCL (clock) line. A combination of these two signals is used to transmit and receive communication start/stop signals, data signals, acknowledge signals, and so on. Both the SCL and SDA signals are held at high level whenever communications are not being performed. The starting and stopping of communications is controlled at the rising edge or falling edge of SDA while SCL is at high level. During data transfers, data changes that occur on the SDA line are performed while the SCL line is at low level, and on the receiving side the data is captured while the SCL line is at high level. In either case, the data is transferred via the SCL line at a rate of one bit per clock pulse. The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device and the receiving device responds to communications only when its slave address matches the slave address in the received data.

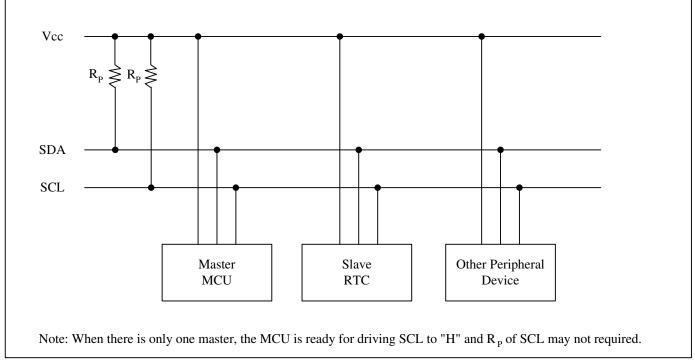

#### b) System Configuration

All ports connected to the I<sup>2</sup>C bus must be either open drain or open collector ports in order to enable AND connections to multiple devices.

SCL and SDA are both connected to the VDD line via a pull-up resistance. Consequently, SCL and SDA are both held at high level when the bus is released (when communication is not being performed).

Fig.4 System configuration

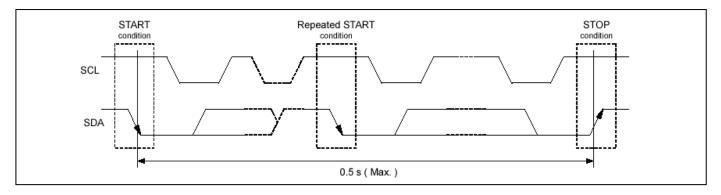

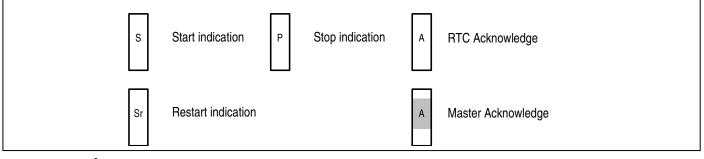

## c) Starting and Stopping I<sup>2</sup>C Bus Communications

Fig.5 Starting and stopping on I<sup>2</sup>C bus

START condition, repeated START condition, and STOP condition

- START condition SDA level changes from high to low while SCL is at high level

- STOP condition SDA level changes from low to high while SCL is at high level

- Repeated START condition (RESTART condition)

In some cases, the START condition occurs between a previous START condition and the next STOP condition, in which case the second START condition is distinguished as a RESTART condition. Since the required status is the same as for the START condition, the SDA level changes from high to low while SCL is at high level.

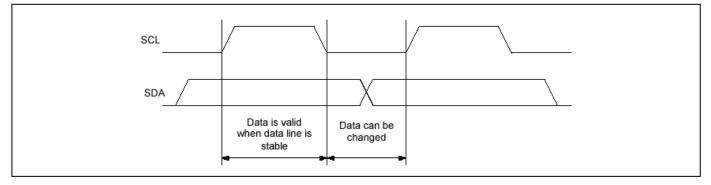

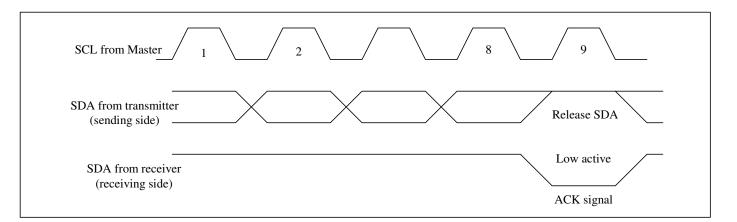

#### d) Data Transfers and Acknowledge Responses during I<sup>2</sup>C-BUS Communication

#### • Data transfers

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit on the amount (bytes) of data that are transferred between the START condition and STOP condition.

The address auto increment function operates during both write and read operations.

Updating of data on the transmitter (transmitting side)'s SDA line is performed while the SCL line is at low level. The receiver (receiving side) captures data while the SCL line is at high level.

\*Note with caution that if the SDA data is changed while the SCL line is at high level, it will be treated as a START, RESTART, or STOP condition.

#### • Data acknowledge response (ACK signal)

When transferring data, the receiver generates a confirmation response (ACK signal, low active) each time an 8-bit data segment is received. If there is no ACK signal from the receiver, it indicates that normal communication has not been established. (This does not include instances where the master device intentionally does not generate an ACK signal.)

Immediately after the falling edge of the clock pulse corresponding to the 8th bit of data on the SCL line, the transmitter releases the SDA line and the receiver sets the SDA line to low (= acknowledge) level.

After transmitting the ACK signal, if the Master remains the receiver for transfer of the next byte, the SDA is released at the falling edge of the clock corresponding to the 9th bit of data on the SCL line. Data transfer resumes when the Master becomes the transmitter.

When the Master is the receiver, if the Master does not send an ACK signal in response to the last byte sent from the slave, that indicates to the transmitter that data transfer has ended. At that point, the transmitter continues to release the SDA and awaits a STOP condition from the Master.

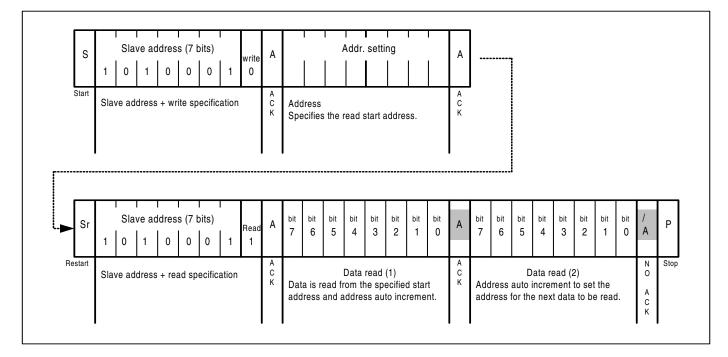

#### e) Slave Address

The I<sup>2</sup>C bus device does not include a chip select pin such as is found in ordinary logic devices. Instead of using a chip select pin, slave addresses are allocated to each device.

All communications begin with transmitting the [START condition] + [slave address (+ R/W specification)]. The receiving device responds to this communication only when the specified slave address it has received matches its own slave address. Slave addresses have a fixed length of 7 bits. See table for the details.

An R/W bit is added to each 7-bit slave address during 8-bit transfers.

| Operation | Transfer data |       |       | SS    |       | $R/\overline{W}$ bit |       |       |             |

|-----------|---------------|-------|-------|-------|-------|----------------------|-------|-------|-------------|

|           |               | bit 7 | bit 6 | bit 5 | bit 4 | bit 3                | bit 2 | bit 1 | bit 0       |

| Read      | A3 h          | 1     | 0     | 1     | 0     | 0                    | 0     | 1     | 1 (= Read)  |

| Write     | A2 h          | 1     | 0     | 1     | 0     | 0                    | 0     | 1     | 0 (= Write) |

## 2. I<sup>2</sup>C Bus's Basic Transfer Format

### a) Write via $I^2C$ bus

| s     |     | Sla   | ve ac  | ddres  | s (7 l | bits)   |       | write | A           | Addr. setting |                |          |       |      | А     | bit | bit         | bit | bit<br>4 | bit | bit | bit<br>1 | bit | А | Р |       |      |

|-------|-----|-------|--------|--------|--------|---------|-------|-------|-------------|---------------|----------------|----------|-------|------|-------|-----|-------------|-----|----------|-----|-----|----------|-----|---|---|-------|------|

|       | 1   | 0     | 1      | 0      | 0      | 0       | 1     | 0     |             |               |                |          | I     |      |       |     |             | ĺ ′ | 6        | 5   | 4   | 3        | 2   | ' | 0 |       |      |

| Start | Sla | ve ad | ldress | 8 + wr | ite sp | oecific | ation |       | A<br>C<br>K |               | ress<br>cifies | the writ | e sta | rt a | ddres | SS. | A<br>C<br>K | Wri | te dat   | a   |     |          |     |   |   | A C K | Stop |

#### b) Read via I<sup>2</sup>C bus

#### • Standard read

#### • Simplified read

| S     | 1  | Sla<br>0 | ve ac  | dres  | ss (7 | bits) | 1      | Read<br>1 | A           | bit<br>7 | bit<br>6 | bit<br>5                   | bit<br>4 | bit<br>3        | bit<br>2 | bit<br>1 | bit<br>0 | A           | bit<br>7 | <sup>bit</sup> | bit<br>5 | bit<br>4                 | bit<br>3 | bit<br>2 | bit<br>1 | bit<br>0 | /<br>A                | Ρ    |

|-------|----|----------|--------|-------|-------|-------|--------|-----------|-------------|----------|----------|----------------------------|----------|-----------------|----------|----------|----------|-------------|----------|----------------|----------|--------------------------|----------|----------|----------|----------|-----------------------|------|

| Start | SI | ave a    | ddress | s + r | ead s | pecif | icatio | on        | A<br>C<br>K | by t     | he int   | ead fr<br>ternal<br>auto i | addr     | e ado<br>ess re | iress    |          |          | A<br>C<br>K |          | addre          | regist   | ata re<br>er au<br>r the | to inc   | reme     |          | set      | N<br>O<br>A<br>C<br>K | Stop |

Note:

- 1. The above steps are an example of transfers of one or two bytes only. There is no limit to the number of bytes transferred during actual communications.

- 2. 49H, 4AH are used as test mode address. Customer should not use the addresses.

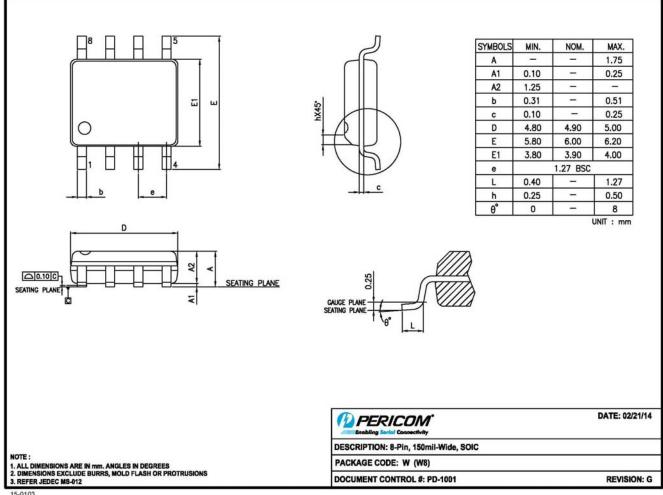

## **Mechanical Information**

W (SOIC-8)

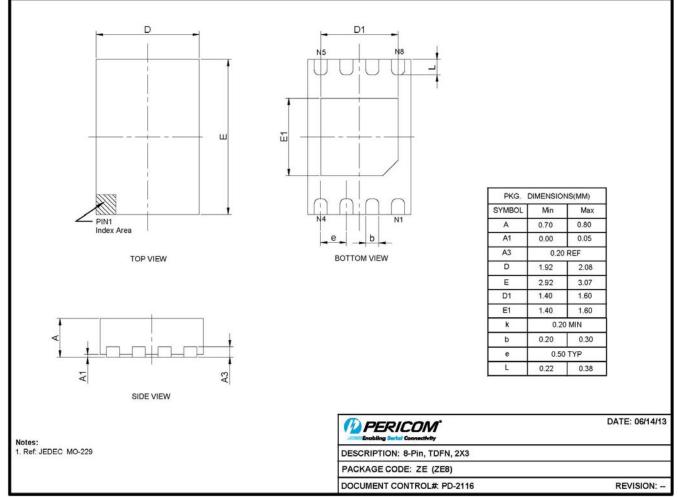

#### ZE (8-Pin TDFN)

13-0155

#### For latest package info.

please check: http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/

## **Ordering Information**

| Part Number   | Package Code | Package                   |

|---------------|--------------|---------------------------|

| PT7C4363BWEX  | W            | 8-Pin, 150mil Wide (SOIC) |

| PT7C4363BZEEX | ZE           | 8-Pin, 2x3 (TDFN)         |

Notes:

• Thermal characteristics can be found on the company web site at www.diodes.com/design/support/packaging/

• E = Pb-free and Green

• X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com