Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PTN3392

# 2-lane DisplayPort to VGA adapter IC Rev. 5 — 5 June 2014

**Product data sheet**

#### **General description** 1.

The PTN3392 is a DisplayPort to VGA adapter IC designed to connect a DisplayPort source to a VGA sink. The PTN3392 integrates a DisplayPort receiver and a high-speed triple video digital-to-analog converter that supports display resolutions from VGA to WUXGA (see Table 5). The PTN3392 supports either one or two DisplayPort v1.1a lanes operating at either 2.7 Gbit/s or 1.62 Gbit/s per lane. The PTN3392 has 'Flash-over-AUX' capability enabling simple firmware upgradability in the field.

The PTN3392 supports I<sup>2</sup>C-bus over AUX per *DisplayPort v1.1a specification* (Ref. 1), and bridges the VESA DDC channel to the DisplayPort Interface.

The PTN3392 is designed for single supply and minimizes application costs. It can be powered directly from the DisplayPort source side 3.3 V supply without a need for additional core voltage regulator. The VGA output is powered down when there is no valid DisplayPort source data being transmitted. The PTN3392 also aids in monitor detection by performing load sensing and reporting sink connection status to the source.

#### Features and benefits 2.

#### 2.1 VESA-compliant DisplayPort v1.1a converter

- Main Link: 1-lane and 2-lane modes supported

- HBR (High Bit Rate) at 2.7 Gbit/s per lane

- ◆ RBR (Reduced Bit Rate) at 1.62 Gbit/s per lane

- ◆ BER (Bit Error Rate) better than 10<sup>-9</sup>

- Down-spreading SSC (Spread Spectrum Clocking) supported

- 1 MHz AUX channel

- Supports native AUX CH syntax

- Supports I<sup>2</sup>C-bus over AUX CH syntax

- Hot Plug Detect (HPD) signal to the source

- Cost-effective design optimized for VGA application

#### 2.2 DDC channel output

- Supports 100 kbit/s I<sup>2</sup>C-bus speed, declared in DPCD register

- ◆ Support of I<sup>2</sup>C-bus speed control by DisplayPort source via DPCD registers, facilitating use of longer VGA cables

- I<sup>2</sup>C Over Aux feature facilitates full support of MCCS, DDC-CI, and DDC protocols (see Ref. 2)

#### 2-lane DisplayPort to VGA adapter IC

#### 2.3 Analog video output

- VSIS 1.2 compliance (Ref. 3) for all supported video output modes

- Analog RGB current-source outputs

- VSYNC and HSYNC outputs

- Pixel clock up to 240 MHz

- Triple 8-bit Digital-to-Analog Converter (DAC)

- Direct drive of double terminated 75  $\Omega$  load with standard 700 mV (peak-to-peak) signals

#### 2.4 General features

- Supports 'Flash-over-AUX' field upgradability

- Monitor presence detection. Connection/disconnection reported via HPD IRQ and DPCD update.

- All display resolutions from VGA to WUXGA are supported<sup>1</sup>, including e.g.:

- ◆ WUXGA: 6 bits, 1920 × 1200, 60 Hz, 193 MHz pixel clock rate

- ◆ WUXGA: 1920 × 1200, 60 Hz, reduced blanking, 154 MHz pixel clock rate

- ◆ UXGA: 1600 × 1200, 60 Hz, 162 MHz pixel clock rate

- ◆ SXGA: 1280 × 1024, 60 Hz, 108 MHz pixel clock rate

- ◆ XGA: 1024 × 768, 60 Hz, 65 MHz pixel clock rate

- ◆ SVGA: 800 × 600, 60 Hz, 40 MHz pixel clock rate

- ◆ VGA: 640 × 480, 60 Hz, 25 MHz pixel clock rate

- Any resolution and refresh rates are supported up to 8 bit color

- Bits per color (bpc) supported¹

- ♦ 6, 8 bits supported

- ◆ 10, 12, 16 bits supported by truncation to 8 MSBs

- All VGA colorimetry formats (RGB) supported

- Power modes

- Active-mode power consumption:

- ~600 mW at UXGA / 162 MHz pixel clock

- ~500 mW at SXGA / 108 MHz pixel clock

- ◆ ~40 mW at Low-power mode or before link training started

- On-board crystal oscillator for use with external 27 MHz crystal

- ESD protection

- ◆ 7 kV ESD HBM JEDEC

- ◆ 8 kV ESD HBM IEC 61000-4-2 (Ref. 4)

- 3.3 V ± 10 % power supply

- Commercial temperature range: 0 °C to 85 °C

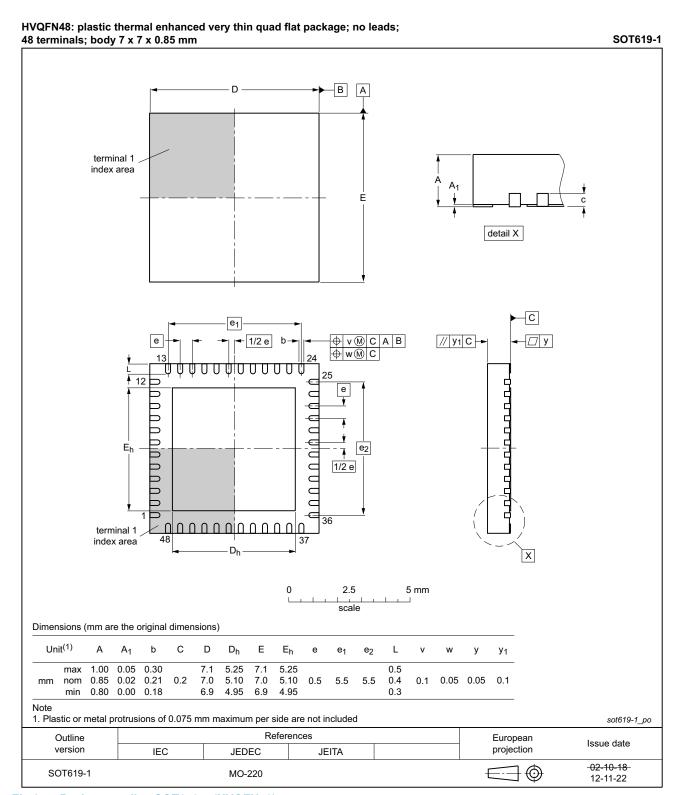

- 48-pin HVQFN, 7 mm × 7 mm × 0.85 mm (nominal); 0.5 mm pitch; lead-free package

PTN3392

Except for color depth beyond 8 bits, display resolutions and refresh rates are only limited to those which a standard 2-lane DisplayPort configuration is able to support.

#### 2-lane DisplayPort to VGA adapter IC

# 3. Applications

- Dongle PC accessory

- Dongle connected to PC DisplayPort output and connected to RGB monitor via VGA cable

- ◆ PTN3392 is powered by the DP\_PWR pin on the DisplayPort connector

- Desktop and notebook computers

- Notebook docking stations

# 4. Ordering information

Table 1. Ordering information

| Type number     | Topside mark | Package |                                                                                                           |          |  |  |  |

|-----------------|--------------|---------|-----------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                 |              | Name    | lame Description                                                                                          |          |  |  |  |

| PTN3392BS[1]    | PTN3392BS    | HVQFN48 | plastic thermal enhanced very thin quad flat package; no leads; 48 terminals; $7 \times 7 \times 0.85$ mm | SOT619-1 |  |  |  |

| PTN3392BS/FX[2] | PTN3392BS    | HVQFN48 | plastic thermal enhanced very thin quad flat package; no leads; 48 terminals; $7 \times 7 \times 0.85$ mm | SOT619-1 |  |  |  |

<sup>[1]</sup> PTN3392BS uses latest firmware version.

## 4.1 Ordering options

Table 2. Ordering options

| Type number     | Orderable part number           | Package | Packing method                             | Minimum order quantity | Temperature                                         |

|-----------------|---------------------------------|---------|--------------------------------------------|------------------------|-----------------------------------------------------|

| PTN3392BS[1]    | PTN3392BS,518                   | HVQFN48 | Reel 13" Q1/T1 *standard mark SMD dry pack | 4000                   | $T_{amb} = 0  ^{\circ}C \text{ to } +85  ^{\circ}C$ |

| PTN3392BS/FX[2] | PTN3392BS/FX,518 <sup>[3]</sup> | HVQFN48 | Reel 13" Q1/T1 *standard mark SMD dry pack | 4000                   | $T_{amb} = 0  ^{\circ}C \text{ to } +85  ^{\circ}C$ |

|                 | PTN3392BS/FXY[3]                | HVQFN48 | Reel 13" Q1/T1 *standard mark SMD dry pack | 4000                   | T <sub>amb</sub> = 0 °C to +85 °C                   |

<sup>[1]</sup> PTN3392BS uses latest firmware version.

<sup>[2]</sup> PTN3392BS/FX uses specific firmware version ('X' = 1, 2, 3, etc., and changes according to firmware version).

<sup>[2]</sup> PTN3392BS/FX uses specific firmware version ('X' = 1, 2, 3, etc., and changes according to firmware version).

<sup>[3]</sup> PTN3392BS/FX,518 is orderable part number for firmware versions 1, 2, or 3. PTN3392BS/FXY is orderable part number for firmware versions 4 or higher.

#### 2-lane DisplayPort to VGA adapter IC

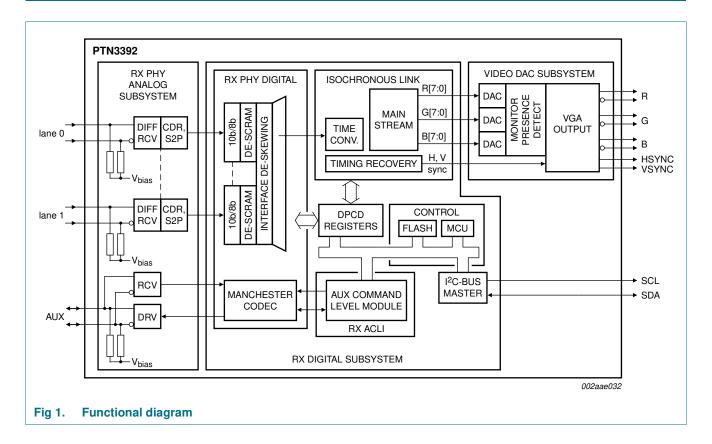

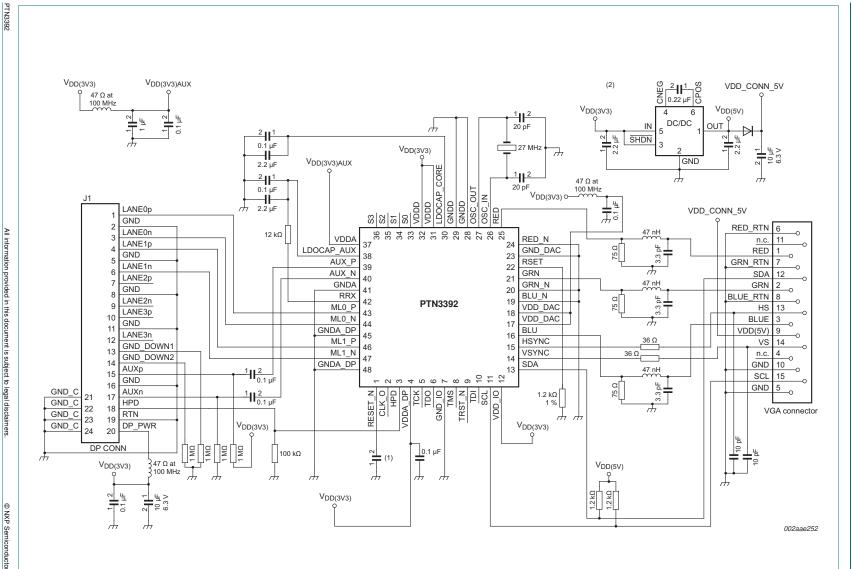

# 5. Functional diagram

#### 2-lane DisplayPort to VGA adapter IC

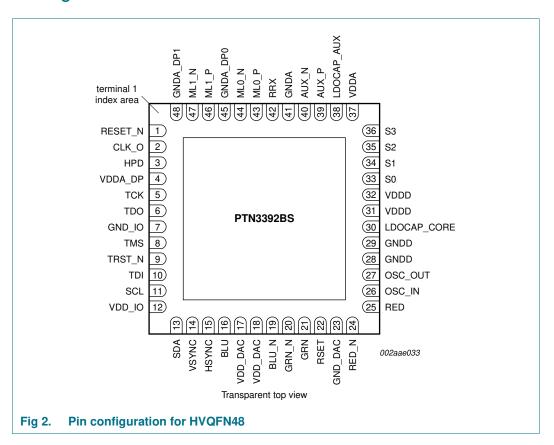

# 6. Pinning information

#### 6.1 Pinning

# 6.2 Pin description

Table 3. Pin description

| Symbol      | Pin    | Туре  | Description                                         |

|-------------|--------|-------|-----------------------------------------------------|

| VDDD        | 32, 31 | power | digital core 3.3 V supply                           |

| VDDA        | 37     | power | analog AUX, bias and PLL 3.3 V supply voltage       |

| VDDA_DP     | 4      | power | analog 3.3 V supply for DisplayPort receiver module |

| VDD_IO      | 12     | power | I/O 3.3 V supply voltage                            |

| VDD_DAC     | 17, 18 | power | analog 3.3 V supply for DAC                         |

| GND_IO[1]   | 7      | power | I/O supply ground                                   |

| GND_DAC[1]  | 23     | power | analog ground for DAC                               |

| GNDA_DP0[1] | 45     | power | analog ground for DisplayPort Lane0                 |

| GNDA_DP1[1] | 48     | power | analog ground for DisplayPort Lane1                 |

| GNDA[1]     | 41     | power | analog AUX, bias and PLL supply ground              |

| GNDD[1]     | 28, 29 | power | digital core supply ground                          |

# 2-lane DisplayPort to VGA adapter IC

Table 3.

Pin description ...continued

| Symbol           | Pin | Type                                         | Description                                                                                                 |

|------------------|-----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| DisplayPort      |     |                                              |                                                                                                             |

| ML0_P            | 43  | self-biasing<br>differential input           | DisplayPort main lane signal lane 0, positive                                                               |

| ML0_N            | 44  | self-biasing<br>differential input           | DisplayPort main lane signal lane 0, negative                                                               |

| ML1_P            | 46  | self-biasing<br>differential input           | DisplayPort main lane signal lane 1, positive                                                               |

| ML1_N            | 47  | self-biasing<br>differential input           | DisplayPort main lane signal lane 1, negative                                                               |

| AUX_P            | 39  | self-biasing<br>differential<br>input/output | DisplayPort auxiliary channel signal, positive                                                              |

| AUX_N            | 40  | self-biasing<br>differential<br>input/output | DisplayPort auxiliary channel signal, negative                                                              |

| HPD              | 3   | 3.3 V TTL single-ended output                | Hot-plug detect                                                                                             |

| RGB DAC outpu    | its |                                              |                                                                                                             |

| BLU              | 16  | analog output                                | 'blue' current analog output                                                                                |

| BLU_N            | 19  | analog output                                | 'blue' current complementary analog output                                                                  |

| GRN              | 21  | analog output                                | 'green' current analog output                                                                               |

| GRN_N            | 20  | analog output                                | 'green' current complementary analog output                                                                 |

| RED              | 25  | analog output                                | 'red' current analog output                                                                                 |

| RED_N            | 24  | analog output                                | 'red' current complementary analog output                                                                   |

| RSET             | 22  | analog input/output                          | DAC full-scale current control resistor. Pull down to ground by an external 1.2 $k\Omega \pm 1$ % resistor. |

| DDC              |     |                                              |                                                                                                             |

| SCL              | 11  | single-ended 5 V<br>open-drain DDC I/O       | 5 V sink-side DDC clock I/O. Pulled up by 1.2 k $\Omega$ external resistor to 5 V.                          |

| SDA              | 13  | single-ended 5 V<br>open-drain DDC I/O       | 5 V sink-side DDC data I/O. Pulled up by 1.2 k $\Omega$ external resistor to 5 V.                           |

| Monitor-side syr | nc  |                                              |                                                                                                             |

| HSYNC            | 15  | single-ended 3.3 V<br>TTL output             | horizontal sync signal to monitor; serial resistance of 36 $\Omega$ is recommended.                         |

| VSYNC            | 14  | single-ended 3.3 V<br>TTL output             | vertical sync signal to monitor; serial resistance of 36 $\Omega$ is recommended.                           |

| JTAG             |     |                                              |                                                                                                             |

| TCK              | 5   | input                                        | JTAG clock input                                                                                            |

| TDO              | 6   | output                                       | JTAG data output                                                                                            |

| TMS              | 8   | input                                        | JTAG mode select input                                                                                      |

| TRST_N           | 9   | input                                        | JTAG reset (active LOW) input                                                                               |

| TDI              | 10  | input                                        | JTAG data input                                                                                             |

#### 2-lane DisplayPort to VGA adapter IC

Table 3.

Pin description ...continued

| Symbol            | Pin | Туре   | Description                                                                                                                                                                                              |

|-------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Strap pins, S[3:0 | ]   |        |                                                                                                                                                                                                          |

| S0                | 33  | input  | Open (internal pull-down) = logic 0:                                                                                                                                                                     |

|                   |     |        | Implement VGA-side monitor detect according to VESA DisplayPort Standard v1.1a sections 7 and 8 (Ref. 1). Refer to Section 7.4.1 for S0 = 0 behavior.                                                    |

|                   |     |        | HIGH (external pull-up) = logic 1:                                                                                                                                                                       |

|                   |     |        | Set HPD HIGH upon VGA monitor detection; set HPD LOW upon VGA monitor detachment. Refer to Section 7.4.2 for S0 = 1 behavior.                                                                            |

|                   |     |        | Default S0 = 0 for standard compliance.                                                                                                                                                                  |

| S1                | 34  | input  | reserved; leave open-circuit (default internal pull-down)                                                                                                                                                |

| S2                | 35  | input  | Open (internal pull-down) = logic 0 to set default I <sup>2</sup> C speed to 50 kbit/s for PTN3392BS/F3, 100 kbit/s for PTN3392BS/F1, PTN3392BS/F2.                                                      |

|                   |     |        | HIGH (external pull-up) = logic 1, to set default I <sup>2</sup> C speed to 10 kbit/s.                                                                                                                   |

|                   |     |        | This pin may be left open-circuit (internal pull-down) or tied to $V_{DD}$ according to the desired default $I^2C$ speed. See more explanation in Table 4 about S2 pin setting and DPCD register 00109h. |

| S3                | 36  | input  | reserved; leave open-circuit (default internal pull-down)                                                                                                                                                |

| Miscellaneous     | I   |        |                                                                                                                                                                                                          |

| RESET_N           | 1   | input  | Hardware reset input (active LOW); internal pull-up. A capacitor must be connected between this pin and ground. A 1 $\mu$ F capacitor is recommended.                                                    |

| CLK_O             | 2   | output | DisplayPort receiver test clock output                                                                                                                                                                   |

| LDOCAP_CORE       | 30  | power  | 1.8 V digital core supply decoupling                                                                                                                                                                     |

| OSC_IN            | 26  | input  | crystal oscillator input                                                                                                                                                                                 |

| OSC_OUT           | 27  | output | crystal oscillator output                                                                                                                                                                                |

| LDOCAP_AUX        | 38  | power  | 1.8 V AUX supply decoupling                                                                                                                                                                              |

| RRX               | 42  | input  | Receiver termination resistance control. A 12 k $\Omega$ resistor must be connected between this pin and LDOCAP_AUX (pin 38).                                                                            |

<sup>[1]</sup> HVQFN48 package die supply ground is connected to both GND pins and exposed center pad. GND pins 7, 23, 28, 29, 41, 45, 48, and exposed center pad must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad must be soldered to the board using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias must be incorporated in the PCB in the thermal pad region.

#### 2-lane DisplayPort to VGA adapter IC

# 7. Functional description

Referring to Figure 1 "Functional diagram", the PTN3392 converts the DisplayPort AC-coupled high-speed differential signaling protocol into a VESA VSIS 1.2 compliant analog VGA signaling. The PTN3392 integrates a DisplayPort receiver (according to VESA DisplayPort v1.1a specification, Ref. 1) and a high-speed triple 8-bit video digital-to-analog converter that supports display resolution from VGA to WUXGA (see Table 5 "Display resolution and pixel clock rate[1]"), up to a pixel clock rate of 240 MHz. The PTN3392 supports one or two DisplayPort v1.1a Main Link lanes operating at either in 2.7 Gbit/s or 1.62 Gbit/s per lane. The PTN3392 can drive up to 100 feet of analog video cable.

The DisplayPort receiver comprises the following functional blocks:

- Main Link

- AUX CH (Auxiliary Channel)

- DPCD (DisplayPort Configuration Data)

- · Monitor detection

- · EDID handling

- Video DAC

The RGB video data with corresponding synchronization references is extracted from the main stream video data. Main stream video attribute information is also extracted. This information is inserted once per video frame during the vertical blanking period by the DisplayPort source. The attributes describe the main video stream format in terms of geometry, timing, and color format. The original clock and video stream are derived from these main link data.

The PTN3392 internal DPCD registers can be accessed by the source via the auxiliary channel. The monitor's DDC control bus may also be controlled via the auxiliary channel. A bridging conversion block translates the input DisplayPort auxiliary channel signals from the source side to the DDC signals on the sink side. The PTN3392 passes through sink-side status change (e.g., hot-plug events) to the source side, through HPD interrupts and DPCD registers.

#### 7.1 DisplayPort Main Link

The DisplayPort main link consists of doubly terminated, AC-coupled differential pair. The 50  $\Omega$  internally calibrated termination resistors are integrated inside PTN3392.

The PTN3392 supports HBR at 2.7 Gbit/s and RBR at 1.62 Gbit/s per lane.

#### 7.2 DisplayPort auxiliary channel

The AUX CH is a half-duplex, bidirectional channel between DisplayPort transmitter and receiver. It consists of one differential pair transporting self-clocked data at 1 Mbit/s. The PTN3392 integrates the AUX CH replier (or slave), and responds to transactions initiated by the DisplayPort source AUX CH requester (or master).

The AUX CH uses the Manchester-II code for the self-clocked transmission of signals; every 'zero' is represented by LOW-to-HIGH transition, and 'one' represented by HIGH-to-LOW transition, in the middle of the bit time.

PTN3392

Product data sheet

#### 2-lane DisplayPort to VGA adapter IC

#### 7.3 DPCD registers

DPCD registers that are part of the VESA DisplayPort v1.1a are described in detail in Ref. 1. The following paragraphs only describe the specific implementation by PTN3392.

The PTN3392 DisplayPort receiver capability and status information about the link are reported by DisplayPort Configuration Data (DPCD) registers, when a DisplayPort source issues a read command on the AUX CH. The DisplayPort source device can also write to the link configuration field of DPCD to configure and initialize the link. The DPCD is DisplayPort v1.1a compliant.

It is the responsibility of the host to only issue commands within the capability of the PTN3392 as defined in the 'Receiver Capability Field' in order to prevent undefined behavior. PTN3392 specific DPCD registers are listed in Table 4.

#### 7.3.1 PTN3392 specific DPCD register settings

Table 4. PTN3392 specific DPCD registers

| DPCD register [1] | Description                                                                                                                                      | Power-on<br>Reset value | Read/write over AUX CH |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|

| Receiver Ca       | pability Field                                                                                                                                   |                         |                        |

| 0000Bh            | RECEIVE_PORT1_CAP_1. ReceiverPort1 Capability_1.                                                                                                 | 00h                     | read only              |

| 0000Ch            | I <sup>2</sup> C-bus speed control capabilities bit map. The bit values in this register are assigned to I <sup>2</sup> C-bus speeds as follows: | 8Fh                     | read only              |

|                   | Bits 7:0                                                                                                                                         |                         |                        |

|                   | 0000 0001b = 1 kbit/s; supported by PTN3392                                                                                                      |                         |                        |

|                   | 0000 0010b = 3 kbit/s; supported by PTN3392                                                                                                      |                         |                        |

|                   | 0000 0100b = 10 kbit/s; supported by PTN3392                                                                                                     |                         |                        |

|                   | 0000 1000b = 100 kbit/s; supported by PTN3392                                                                                                    |                         |                        |

|                   | 0001 0000b = 400 kbit/s; not supported by PTN3392                                                                                                |                         |                        |

|                   | 0010 0000b = 1 Mbit/s; not supported by PTN3392                                                                                                  |                         |                        |

|                   | 0100 0000b = reserved                                                                                                                            |                         |                        |

|                   | 1000 0000b = 50 kbit/s; supported by PTN3392BS/F3                                                                                                |                         |                        |

|                   | 1000 0000b = reserved in PTN3392BS/F1, PTN3392BS/F2                                                                                              |                         |                        |

#### 2-lane DisplayPort to VGA adapter IC

Table 4. PTN3392 specific DPCD registers ...continued

| DPCD                | Description                                                                                                                            | Power-on    | Read/write  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| register [1]        |                                                                                                                                        | Reset value | over AUX CH |

|                     | uration Field                                                                                                                          |             |             |

| 00109h              | I <sup>2</sup> C-bus speed control/status bit map. Bit values in this register are assigned to I <sup>2</sup> C-bus speeds as follows: | S2 setting  | read/write  |

|                     | Bits 7:0                                                                                                                               |             |             |

|                     | 0000 0001b = 1 kbit/s; supported by PTN3392                                                                                            |             |             |

|                     | 0000 0010b = 3 kbit/s; supported by PTN3392                                                                                            |             |             |

|                     | 0000 0100b = 10 kbit/s; supported by PTN3392                                                                                           |             |             |

|                     | 0000 1000b = 100 kbit/s; supported by PTN3392                                                                                          |             |             |

|                     | 0001 0000b = 400 kbit/s; not supported by PTN3392                                                                                      |             |             |

|                     | 0010 0000b = 1 Mbit/s; not supported by PTN3392                                                                                        |             |             |

|                     | 0100 0000b = reserved                                                                                                                  |             |             |

|                     | 1000 0000b = 50 kbit/s; supported by PTN3392BS/F3                                                                                      |             |             |

|                     | 1000 0000b = reserved in PTN3392BS/F1, PTN3392BS/F2                                                                                    |             |             |

|                     | Default value: 1000 0000b (50 kbit/s) for PTN3392BS/F3                                                                                 |             |             |

|                     | Default value: 0000 1000b (100 kbit/s) for PTN3392BS/F1, PTN3392BS/F2                                                                  |             |             |

|                     | See also behavior of pin S2 in Table 3.                                                                                                |             |             |

| Automated           | testing sub-field (optional)                                                                                                           |             |             |

| 00218h to<br>0027Fh | Not supported.                                                                                                                         |             |             |

| Branch devi         | ice-specific field                                                                                                                     |             |             |

| 00500h              | BRANCH_IEEE_OUI 7:0                                                                                                                    | 00h         | read only   |

|                     | Branch vendor 24-bit IEEE OUI.                                                                                                         |             |             |

|                     | NXP OUI = 00                                                                                                                           |             |             |

| 00501h              | BRANCH_IEEE_OUI 15:8                                                                                                                   | 60h         | read only   |

|                     | NXP OUI = 60                                                                                                                           |             |             |

| 00502h              | BRANCH_IEEE_OUI 23:16                                                                                                                  | 37h         | read only   |

|                     | NXP OUI = 37                                                                                                                           |             |             |

| 00503h              | ID string = 3392N2                                                                                                                     | 33h         | read only   |

| 00504h              |                                                                                                                                        | 33h         | read only   |

| 00505h              |                                                                                                                                        | 39h         | read only   |

| 00506h              |                                                                                                                                        | 32h         | read only   |

| 00507h              |                                                                                                                                        | 4Eh         | read only   |

| 00508h              | -                                                                                                                                      | 32h         | read only   |

| 00509h              | Hardware revision level v1.2                                                                                                           | 12h         | read only   |

| 0050Ah,             | Major revision level (example: v1.38),                                                                                                 | 01h,        | read only   |

| 0050Rh              | Minor revision level (example: v1.38)                                                                                                  | 26h         | 344 5.11    |

| 0050Ch to<br>005FFh | RESERVED                                                                                                                               | -           | read only   |

<sup>[1]</sup> Byte fields that are not explicitly listed are by definition reserved ('RES') and their default value is 0h.

#### 2-lane DisplayPort to VGA adapter IC

#### 7.3.2 I<sup>2</sup>C over AUX CH registers

#### 7.3.2.1 I<sup>2</sup>C-bus speed control register (read only, 0000Ch)

Bit or bits are set to indicate I<sup>2</sup>C-bus speed control capabilities.

DisplayPort source reads register 0000Ch and sets the I<sup>2</sup>C-bus speed according to the DPCD register 00109h setting. The PTN3392 then adapts its I<sup>2</sup>C-bus bit rate to the speed set by the DisplayPort source.

#### 7.3.2.2 I<sup>2</sup>C-bus speed control/status register (read/write, 00109h)

Bit values in this register are assigned to I<sup>2</sup>C-bus speeds.

Prior to software writing to this register, PTN3392 defaults to the I<sup>2</sup>C-bus speed (either 50 kbit/s or 10 kbit/s) selected by the S2 pin (Table 3).

On read, the PTN3392 returns a value set to indicate the speed currently in use.

On write, software provides a mask to limit the speeds to be enabled:

- The PTN3392 uses the slowest speed enabled by the mask and the PTN3392 speed capabilities.

- If the result of the mask with the speed capabilities is 0000 0000b, then the PTN3392 keeps the S2 setting I<sup>2</sup>C-bus speed that it is using before the software write (i.e., no change).

Some specific examples are listed below for clarification purposes:

- If the source writes 1111 1111b, the PTN3392 uses the lowest speed of 1 kbit/s.

- If the source writes 0000 1100b, the PTN3392 uses the lower of 10 kbit/s and 100 kbit/s, i.e., 10 kbit/s.

- If the source writes 0011 0000b, the PTN3392 would stay using the same I<sup>2</sup>C-bus speed that it is using before the software write (i.e., no change).

For DDC communication, the PTN3392 generates defer responses to the source while the I<sup>2</sup>C-bus transfer is taking place as specified in the *DisplayPort standard v1.1a*. Note that when the I<sup>2</sup>C-bus bit rate is set to 1 kbit/s, each bit takes 1 ms. One byte including I2C\_ACK takes 9 ms. Given this, the DisplayPort source should expect over 20 I2C\_DEFER's when requesting to read a byte over I<sup>2</sup>C-bus at the slowest rate.

#### 2-lane DisplayPort to VGA adapter IC

#### 7.4 Monitor detection

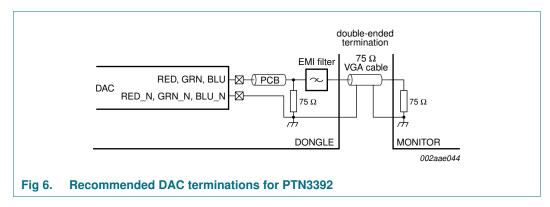

The PTN3392 assumes 75  $\Omega$  double termination, as shown in Figure 6. The load sensing circuit of the PTN3392 senses a 37.5  $\Omega$  or 75  $\Omega$  termination respectively, when the monitor is connected or disconnected. The load-sensing circuit is active during the vertical blanking period (never during the horizontal retrace period), so that there is no disturbance to the screen image caused by the load-sensing circuit.

Upon detection of an RGB monitor being connected, the PTN3392 dynamically updates DPCD register 00200h and 00204h, to indicate the presence of a sink device being connected (see Section 7.3). After updating the DPCD register 00200h, the PTN3392 generates an IRQ request on HPD.

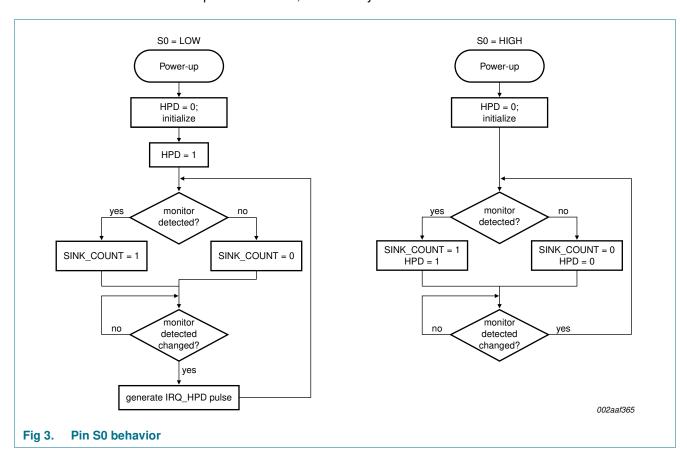

The PTN3392 implements two different ways to handle the HPD signal. The HPD behavior is governed by the S0 pin value after the reset and initialization sequence is completed (see <u>Figure 3</u>).

- If S0 is tied LOW, HPD is driven HIGH irrespective of whether a VGA monitor is detected.

- If S0 pin is tied HIGH, HPD is only driven HIGH when a monitor is detected.

#### 2-lane DisplayPort to VGA adapter IC

#### 7.4.1 S0 = $\log c 0$

If S0 is left open-circuit (internal pull-down) (DisplayPort v1.1a compliant behavior), PTN3392 behaves as stated in *VESA DisplayPort v1.1a*, sections 7 and 8. PTN3392 will keep HPD LOW during its internal initialization sequence after power-up. It will then update DPCD register SINK\_COUNT to the expected value, depending if a VGA monitor is detected or not, and will then assert HPD HIGH whatever is the value of SINK\_COUNT register. Each time PTN3392 detects a change in the VGA monitor connection status, it updates the SINK\_COUNT register accordingly, set

DOWNSTREAM\_PORT\_STATUS\_CHANGED register bit to 1 and generate IRQ\_HPD pulse to signal the source about the status change. Refer to Figure 3, S0 = LOW flowchart.

#### 7.4.2 S0 = logic 1

If S1 is tied to HIGH with external pull-up (best interoperability behavior), the PTN3392 will keep HPD LOW during its internal initialization sequence after power-up. It then waits for a VGA monitor to be connected downstream before asserting HPD HIGH to force source waiting for a VGA monitor before starting protocol negotiations. If a VGA monitor is disconnected during normal operations, PTN3392 asserts HPD LOW so that the source considers that no sink device is connected anymore. Refer to Figure 3, S0 = HIGH flowchart.

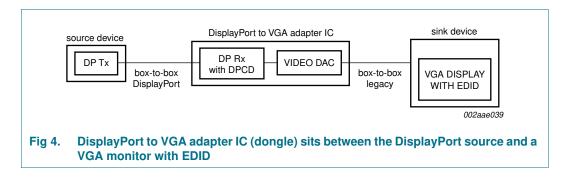

#### 7.5 EDID handling

<u>Figure 4</u> shows a DisplayPort-to-analog video converter (or dongle) situated between the DisplayPort source and a VGA monitor. The PTN3392 converts a DP I<sup>2</sup>C Over AUX request to I<sup>2</sup>C on the monitor's DDC bus. The monitor's EDID read data is then returned to the DP source via an I<sup>2</sup>C Over AUX response issued by the PTN3392.

It is the responsibility of the source to choose only video modes which are declared in the EDID and to adjust the DisplayPort link capabilities (link rate and lane count) to provide the necessary video bandwidth. The PTN3392 does not cache or modify the EDID to match the capabilities of the DisplayPort link data.

If the DisplayPort source drives display modes that are not specified in the EDID mode list, the PTN3392 does not detect such conditions, and displays at its output what it is presented by the DisplayPort source.

#### 2-lane DisplayPort to VGA adapter IC

#### 7.6 Triple 8-bit video DACs and VGA outputs

The triple 8-bit video DACs output a 700 mV (peak-to-peak) analog video output signal into 37.5  $\Omega$  load, as is the case of a doubly terminated 75  $\Omega$  cable. The DAC is capable of supporting the maximum pixel rate supported by a two-lane DP link (240 MHz).

The PTN3392 generates the RGB video timing and synchronization signals, RGB signals are then sent to the DACs for conversion to analog signals.

#### 7.6.1 DAC reference resistor

An external reference resistor must be connected between pin RSET and analog ground. This resistor sets the reference current which determines the analog output level, and is specified as 1.2 k $\Omega$  with a 1 % tolerance. This value allows a 0.7 V (peak-to-peak) output into a 37.5  $\Omega$  load, such as a double-terminated 75  $\Omega$  coaxial cable.

# 8. Power-up and reset

PTN3392 has built-in power-on reset circuitry which automatically sequences the part through reset and initialization.

For proper behavior, a capacitor should be connected from the RESET\_N pin to ground to slow down the internal reset pulse; 1  $\mu$ F capacitance is recommended.

Before link is established, the PTN3392 holds VSYNC and HSYNC signals LOW and blanks the RGB signals.

While the PTN3392 performs initialization,

- The HPD signal is driven LOW, to indicate to the DisplayPort source that the PTN3392 is not ready for link communication

- The RED, GRN, BLU and complementary outputs (RED\_N, GRN\_N, BLU\_N) are disabled

- · The VSYNC and HSYNC outputs are driven LOW

# Application design-in information

9

- (1) 1 μF is recommended.

- Example of external DC-to-DC regulator.

**Application diagram**

Product data sheet

Rev.

G

5 June 2014

#### 2-lane DisplayPort to VGA adapter IC

# 9.1 Display resolution

<u>Table 5</u> lists some example display resolutions and clock rates that PTN3392 supports. (Refer to Footnote 1 on page 2.)

Table 5. Display resolution and pixel clock rate[1]

| Display | Active vide | 0        | Total frame              |                          | Bits         | Vertical          | Pixel          | Data             | Standard type     |

|---------|-------------|----------|--------------------------|--------------------------|--------------|-------------------|----------------|------------------|-------------------|

| type    | Horizontal  | Vertical | Horizontal total (pixel) | Vertical<br>total (line) | per<br>pixel | frequency<br>(Hz) | clock<br>(MHz) | rate<br>(Gbit/s) |                   |

| VGA     | 640         | 480      | 800                      | 525                      | 24           | 59.94             | 25.175         | 0.76             | Industry standard |

| SVGA    | 800         | 600      | 1056                     | 628                      | 24           | 60.317            | 40.000         | 1.20             | VESA guidelines   |

| XGA     | 1024        | 768      | 1344                     | 806                      | 24           | 60.004            | 65.000         | 1.95             | VESA guidelines   |

| XGA+    | 1152        | 864      | 1600                     | 900                      | 24           | 75                | 108.000        | 3.24             | VESA standard     |

| HD      | 1360        | 768      | 1792                     | 795                      | 24           | 60.015            | 85.500         | 2.56             | VESA standard     |

| HD/WXGA | 1366        | 768      | 1792                     | 798                      | 24           | 59.79             | 85.501         | 2.57             | VESA standard     |

| HD/WXGA | 1280        | 720      | 1650                     | 750                      | 24           | 60                | 74.250         | 2.23             | CEA standard      |

| WXGA    | 1280        | 800      | 1680                     | 831                      | 24           | 59.81             | 83.500         | 2.50             | CVT               |

| WXGA    | 1280        | 800      | 1696                     | 838                      | 24           | 74.934            | 106.500        | 3.19             | CVT               |

| WXGA    | 1280        | 800      | 1712                     | 843                      | 24           | 84.88             | 122.500        | 3.68             | CVT               |

| SXGA-   | 1280        | 960      | 1800                     | 1000                     | 24           | 60                | 108.000        | 3.24             | VESA standard     |

| SXGA    | 1280        | 1024     | 1688                     | 1066                     | 24           | 60.02             | 108.000        | 3.24             | VESA standard     |

| SXGA    | 1280        | 1024     | 1688                     | 1066                     | 24           | 75.025            | 135.001        | 4.05             | VESA standard     |

| SXGA    | 1280        | 1024     | 1728                     | 1072                     | 24           | 85.024            | 157.500        | 4.72             | VESA standard     |

| SXGA+   | 1400        | 1050     | 1864                     | 1089                     | 24           | 59.978            | 121.749        | 3.65             | CVT               |

| WXGA+   | 1440        | 900      | 1904                     | 934                      | 24           | 59.887            | 106.499        | 3.19             | CVT               |

| HD+     | 1600        | 900      | 1800                     | 1000                     | 24           | 60                | 108.000        | 3.24             | VESA standard     |

| UXGA    | 1600        | 1200     | 2160                     | 1250                     | 24           | 60                | 162.000        | 4.86             | VESA standard     |

| UXGA    | 1600        | 1200     | 2160                     | 1250                     | 24           | 65                | 175.500        | 5.27             | VESA standard     |

| WSXGA+  | 1680        | 1050     | 2240                     | 1089                     | 24           | 59.954            | 146.249        | 4.39             | CVT               |

| FHD     | 1920        | 1080     | 2200                     | 1125                     | 24           | 60                | 148.500        | 4.46             | CEA standard      |

| WUXGA   | 1920        | 1200     | 2592                     | 1245                     | 18           | 59.885            | 193.251        | 4.35             | CVT               |

| WUXGA   | 1920        | 1200     | 2080                     | 1235                     | 24           | 59.95             | 154.000        | 4.62             | CVT RB            |

|         | 1920        | 1440     | 2600                     | 1500                     | 18           | 60                | 234.000        | 5.27             | CVT RB            |

| QWXGA   | 2048        | 1152     | 2250                     | 1200                     | 24           | 60                | 162.000        | 4.86             | VESA standard     |

| QXGA    | 2048        | 1536     | 2144                     | 1555                     | 24           | 49.266            | 164.249        | 4.93             | CVT               |

<sup>[1]</sup> Contact NXP team for other monitor timings not listed in this table.

The available bandwidth over a 2-lane HBR DisplayPort v1.1a link limits pixel clock rate support to:

- 240 MHz at 6 bpc

- 180 MHz at 8 bpc

#### 2-lane DisplayPort to VGA adapter IC

#### 9.2 Power supply filter

All supply pins can be tied to a single 3.3 V power source. Sufficient decoupling capacitance to ground should be connected from each  $V_{DD}$  pin directly to ground to filter supply noise. (Refer to Figure 5 "Application diagram".)

#### 9.3 DAC terminations

We recommend the DAC outputs to use 75  $\Omega$  double termination. <u>Figure 6</u> shows an example of VGA dongle application. A 75  $\Omega$  termination is used to terminate inside the dongle, and another 75  $\Omega$  termination is typically used inside the RGB monitor. The load sensing mechanism assumes this double termination.

# 10. Limiting values

Table 6. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions                                    |     | Min  | Max            | Unit |

|------------------|---------------------------------|-----------------------------------------------|-----|------|----------------|------|

| $V_{DDA}$        | analog supply voltage           |                                               |     | -0.3 | +3.8           | V    |

| $V_{DDD}$        | digital supply voltage          |                                               |     | -0.3 | +4.6           | V    |

| VI               | input voltage                   | 3.3 V CMOS inputs                             |     | -0.3 | $V_{DD} + 0.5$ | V    |

| T <sub>stg</sub> | storage temperature             |                                               |     | -65  | +150           | °C   |

| $V_{ESD}$        | electrostatic discharge voltage | НВМ                                           | [1] | -    | 7000           | V    |

|                  |                                 | CDM                                           | [2] | -    | 1000           | V    |

|                  |                                 | IEC contact discharge to signal pins (to GND) | [3] | -    | 8000           | V    |

<sup>[1]</sup> Human Body Model: ANSI/ESDA/JEDEC JDS-001-2012 (Revision of ANSI/ESDA/JEDEC JS-001-2011), ESDA/JEDEC Joint standard for ESD sensitivity testing, Human Body Model - Component level; Electrostatic Discharge Association, Rome, NY, USA; JEDEC Solid State Technology Association, Arlington, VA, USA.

[3] IEC 61000-4-2, Level 4 (Ref. 4).

<sup>[2]</sup> Charged Device Model: JESD22-C101E December 2009 (Revision of JESD22-C101D, October 2008), standard for ESD sensitivity testing, Charged Device Model - Component level; JEDEC Solid State Technology Association, Arlington, VA, USA.

#### 2-lane DisplayPort to VGA adapter IC

# 11. Recommended operating conditions

Table 7. Operating conditions

| Symbol                 | Parameter                       | Conditions                                                                          | Min | Тур       | Max | Unit |

|------------------------|---------------------------------|-------------------------------------------------------------------------------------|-----|-----------|-----|------|

| $V_{DDA}$              | analog supply voltage           |                                                                                     | 3.0 | 3.3       | 3.6 | V    |

| $V_{DDD}$              | digital supply voltage          |                                                                                     | 3.0 | 3.3       | 3.6 | V    |

| V <sub>I</sub>         | input voltage                   | 3.3 V CMOS inputs                                                                   | 0   | 3.3       | 3.6 | V    |

|                        |                                 | SDA and SCL inputs with respect to ground                                           | 0   | 5         | 5.5 | V    |

| V <sub>I(AV)</sub>     | average input voltage           | DC value at [1] ML_LANE0+, ML_LANE0-, ML_LANE1+, ML_LANE1-, AUX_CH+, AUX_CH- inputs | -   | 0         | -   | V    |

| R <sub>ext(RSET)</sub> | external resistance on pin RSET | between RSET (pin 22) and GND                                                       | -   | 1.2 ± 1 % | -   | kΩ   |

| T <sub>amb</sub>       | ambient temperature             | commercial grade                                                                    | 0   | -         | 85  | °C   |

<sup>[1]</sup> Input signals to these pins must be AC-coupled.

# 12. Characteristics

# 12.1 Current consumption, power dissipation and thermal characteristics

Table 8. Current consumption, power dissipation and thermal characteristics

| Symbol               | Parameter                                   | Conditions                                                      | Min | Тур | Max | Unit |

|----------------------|---------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub>      | supply current                              | normal operation,<br>UXGA / 162 MHz pixel clock                 | -   | 180 | -   | mA   |

| I <sub>DD(stb)</sub> | standby supply current                      | Standby mode                                                    | -   | 12  | -   | mA   |

| Р                    | power dissipation                           | normal operation,<br>UXGA / 162 MHz pixel clock                 | -   | 600 | -   | mW   |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air for SOT619-1                                        | -   | 35  | -   | K/W  |

| R <sub>PU</sub>      | pull-up resistance                          | RESET_N pin; $0 \text{ V} \leq V_I \leq V_{DD}$                 | 44  | 66  | 95  | kΩ   |

| R <sub>pd</sub>      | pull-down resistance                        | S0 to S3 pins; 0 V $\leq$ V <sub>I</sub> $\leq$ V <sub>DD</sub> | 44  | 66  | 95  | kΩ   |

#### 2-lane DisplayPort to VGA adapter IC

# 12.2 DisplayPort receiver main link

Table 9. DisplayPort receiver main link characteristics

| Symbol                         | Parameter                                                                    | Conditions                                       |        | Min  | Тур | Max   | Unit |

|--------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|--------|------|-----|-------|------|

| UI                             | unit interval                                                                | for high bit rate<br>(2.7 Gbit/s per lane)       | [1]    | -    | 370 | -     | ps   |

|                                |                                                                              | for low bit rate<br>(1.62 Gbit/s per lane)       | [1]    | -    | 617 | -     | ps   |

| Δf <sub>DOWN_SPREAD</sub>      | link clock down spreading                                                    |                                                  | [2]    | 0.0  | -   | 0.5   | %    |

| V <sub>RX_DIFFp-p</sub>        | differential input peak-to-peak                                              | at RX package pins                               |        |      | '   |       |      |

|                                | voltage                                                                      | for high bit rate                                | [3]    | 120  | -   | -     | mV   |

|                                |                                                                              | for reduced bit rate                             | [3]    | 40   | -   | -     | mV   |

| trx_eye_conn                   | receiver eye time at RX-side                                                 | for high bit rate                                | [4]    | 0.51 | -   | -     | UI   |

|                                | connector pins                                                               | for reduced bit rate                             | [4][5] | 0.25 | -   | -     | UI   |

| t <sub>RX_EYE_CHIP</sub>       | receiver eye time at RX package pins                                         | for high bit rate                                | [4]    | 0.47 | -   | -     | UI   |

|                                |                                                                              | for reduced bit rate                             | [4][5] | 0.22 | -   | -     | UI   |

| t <sub>RX_EYE_m-m</sub> JT_CHP | time between jitter median and<br>maximum median deviation<br>(package pins) | for high bit rate                                | [4]    | -    | -   | 0.265 | UI   |

|                                |                                                                              | for reduced bit rate                             | [4][5] | -    | -   | 0.39  | UI   |

| V <sub>RX_DC_CM</sub>          | RX DC common mode voltage                                                    |                                                  | [6]    | 0    | -   | 2.0   | V    |

| I <sub>RX_SHORT</sub>          | RX short-circuit current limit                                               |                                                  | [7]    | -    | -   | 50    | mA   |

| L <sub>RX_SKEW</sub>           | total skew                                                                   | inter-pair; lane-to-lane skew at RX package pins | [8]    | -    | -   | 5200  | ps   |

|                                |                                                                              | lane intra-pair skew at RX package pins;         |        |      |     | ,     |      |

|                                |                                                                              | for high bit rate                                | [9]    | -    | -   | 100   | ps   |

|                                |                                                                              | for reduced bit rate                             | [9]    | -    | -   | 300   | ps   |

| f <sub>RX</sub> TRACKING BW    | jitter tracking bandwidth                                                    |                                                  | [10]   | 20   | -   | -     | MHz  |

- [1] Range is nominal ±350 ppm. DisplayPort link RX does not require local crystal for link clock generation.

- [2] Up to 0.5 % down spread is supported. Modulation frequency range of 30 kHz to 33 kHz must be supported.

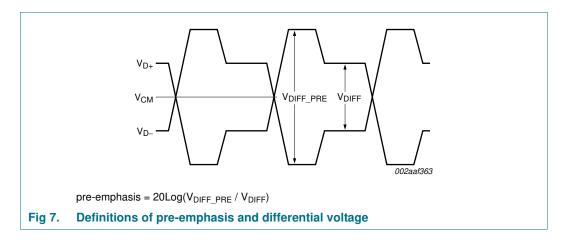

- [3] Informative; refer to Figure 7 for definition of differential voltage.

- $\label{eq:thm:mass} \text{[4]} \quad t_{\text{RX\_EYE\_m-mJT\_CHP}} \text{ specifies the total allowable Deterministic Jitter (DJ)}.$

- $\label{eq:convergence} [5] \quad 1 t_{RX\_EYE\_CONN} \mbox{ specifies the allowable Total Jitter (TJ)}.$

- [6] Common mode voltage is equal to  $V_{bias\_RX}$  voltage.

- [7] Total drive current of the input bias circuit when it is shorted to its ground.

- [8] Maximum skew limit between different RX lanes of a DisplayPort link.

- [9] Maximum skew limit between D+ and D- of the same lane.

- [10] Minimum CDR tracking bandwidth at the receiver when the input is repetition of D10.2 symbols without scrambling.

#### 2-lane DisplayPort to VGA adapter IC

#### 12.3 DisplayPort receiver AUX CH

Table 10. DisplayPort receiver AUX CH characteristics

| Symbol                        | Parameter                          | Conditions              | Min  | Тур | Max  | Unit |

|-------------------------------|------------------------------------|-------------------------|------|-----|------|------|

| UI                            | unit interval                      | AUX [1]                 | 0.4  | 0.5 | 0.6  | μS   |

| N <sub>PRECHARGE_PULSES</sub> | number of precharge pulses         | [2]                     | 10   | -   | 16   |      |

| t <sub>AUX_BUS_PARK</sub>     | AUX CH bus park time               | [3]                     | 10   | -   | -    | ns   |

| t <sub>jit(cc)</sub>          | cycle-to-cycle jitter time         | transmitting device [4] | -    | -   | 0.04 | UI   |

|                               |                                    | receiving device [5]    | -    | -   | 0.05 | UI   |

| V <sub>AUX_DIFFp-p</sub>      | AUX differential peak-to-peak      | transmitting device [6] | 0.39 | -   | 1.38 | V    |

|                               | voltage                            | receiving device [6]    | 0.32 | -   | 1.36 | V    |

| R <sub>AUX_TERM(DC)</sub>     | AUX CH termination DC resistance   | informative             | -    | 100 | -    | Ω    |

| V <sub>AUX_DC_CM</sub>        | AUX DC common-mode voltage         | [7]                     | 0    | -   | 2.0  | V    |

| V <sub>AUX_TURN_CM</sub>      | AUX turnaround common-mode voltage | [8]                     | -    | -   | 0.4  | V    |

| I <sub>AUX_SHORT</sub>        | AUX short-circuit current limit    | [9]                     | -    | -   | 90   | mA   |

| C <sub>AUX</sub>              | AUX AC coupling capacitor          | [10]                    | 75   | -   | 200  | nF   |

- [1] Results in the bit rate of 1 Mbit/s including the overhead of Manchester II coding.

- [2] Each pulse is a '0' in Manchester II code.

- [3] Period after the AUX CH STOP condition for which the bus is parked.

- [4] Maximum allowable UI variation within a single transaction at connector pins of a transmitting device. Equal to 24 ns maximum. The transmitting device is a source device for a request transaction and a sink device for a reply transaction.

- [5] Maximum allowable UI variation within a single transaction at connector pins of a receiving device. Equal to 30 ns maximum. The transmitting device is a source device for a request transaction and a sink device for a reply transaction.

- $[6] \quad V_{AUX\_DIFFp\text{-}p} = 2 \times |V_{AUX+} V_{AUX-}|.$

- [7] Common-mode voltage is equal to  $V_{bias\_TX}$  (or  $V_{bias\_RX}$ ) voltage.

- [8] Steady-state common-mode voltage shift between transmit and receive modes of operation.

- [9] Total drive current of the transmitter when it is shorted to its ground.

- [10] The AUX CH AC coupling capacitor placed both on the DisplayPort source and sink devices.

#### 2-lane DisplayPort to VGA adapter IC

#### 12.4 HPD characteristics

Table 11. HPD characteristics

| Symbol           | Parameter                               | Conditions                                   | Min | Тур | Max | Unit |

|------------------|-----------------------------------------|----------------------------------------------|-----|-----|-----|------|

| Output ch        | naracteristics                          |                                              |     |     | '   |      |

| V <sub>OH</sub>  | HIGH-level output voltage               | $I_{OH} = 2 \text{ mA}$                      | 2   | -   | -   | ٧    |

| V <sub>OL</sub>  | LOW-level output voltage                | $I_{OL} = -2 \text{ mA}$                     | -   | -   | 0.8 | ٧    |

| I <sub>OSH</sub> | HIGH-level short-circuit output current | drive HIGH; cell connected to ground         | -   | -   | 129 | mA   |

| I <sub>OSL</sub> | LOW-level short-circuit output current  | drive LOW; cell connected to V <sub>DD</sub> | -   | -   | 126 | mA   |

#### 12.5 DDC characteristics

Table 12. DDC characteristics

$V_{CC} = 4.5 \text{ V to } 5.5 \text{ V.}$

| Symbol              | Parameter                    | Conditions                                                    | Min                 | Тур | Max  | Unit |

|---------------------|------------------------------|---------------------------------------------------------------|---------------------|-----|------|------|

| Input cha           | racteristics                 |                                                               | '                   |     |      |      |

| $V_{IH}$            | HIGH-level input voltage     |                                                               | 2                   | -   | 5.5  | V    |

| $V_{IL}$            | LOW-level input voltage      |                                                               | -0.5                | -   | +0.8 | V    |

| V <sub>I(hys)</sub> | hysteresis of input voltage  |                                                               | $0.1 \times V_{DD}$ | -   | -    | V    |

| ILI                 | input leakage current        | $V_1 = 5.5 \text{ V}$                                         | -                   | -   | ±1   | μА   |

| Output ch           | naracteristics               |                                                               |                     |     |      |      |

| I <sub>OL</sub>     | LOW-level output current     | V <sub>OL</sub> = 0.4 V                                       | 3.0                 | -   | -    | mA   |

| I <sub>O(sc)</sub>  | short-circuit output current | drive LOW; cell connected to V <sub>DD</sub>                  | -                   | -   | 40.0 | mA   |

| C <sub>io</sub>     | input/output capacitance     | $V_{I} = 3 \text{ V or } 0 \text{ V}; V_{DD} = 3.3 \text{ V}$ | -                   | 6   | 7    | pF   |

|                     |                              | $V_{I} = 3 \text{ V or } 0 \text{ V}; V_{DD} = 0 \text{ V}$   | -                   | 6   | 7    | pF   |

<sup>[1]</sup>  $V_{CC}$  is the pull-up voltage for DDC.

#### 12.6 DAC

Table 13. DAC characteristics

| Symbol                           | Parameter                    | Conditions          | Min | Тур  | Max  | Unit |

|----------------------------------|------------------------------|---------------------|-----|------|------|------|

| N <sub>res(DAC)</sub>            | DAC resolution               |                     | -   | -    | 8    | bit  |

| f <sub>clk</sub>                 | clock frequency              |                     | -   | -    | 240  | MHz  |

| $\Delta I_{O(DAC)}$              | DAC output current variation | DAC-to-DAC          | -   | -    | 4    | %    |

| INL                              | integral non-linearity       |                     | -1  | ±0.5 | +1   | LSB  |

| DNL                              | differential non-linearity   |                     | -1  | -    | +1   | LSB  |

| $V_{o(DAC)}$                     | DAC output voltage           |                     | 0   | -    | 1.25 | ٧    |

| C <sub>o(DAC)</sub>              | DAC output capacitance       |                     | -   | 3.5  | -    | pF   |

| $\alpha_{\text{ct}(\text{DAC})}$ | DAC crosstalk                | between DAC outputs | -   | -54  | -    | dB   |

#### 2-lane DisplayPort to VGA adapter IC

# 12.7 HSYNC, VSYNC characteristics

Table 14. HSYNC and VSYNC characteristics

| Symbol                 | Parameter                               | Conditions                                   |     | Min | Тур | Max   | Unit |

|------------------------|-----------------------------------------|----------------------------------------------|-----|-----|-----|-------|------|

| Output characteristics |                                         |                                              |     |     |     |       |      |

| V <sub>OH</sub>        | HIGH-level output voltage               | $I_{OH} = 8 \text{ mA}$                      |     | 2   | -   | -     | V    |

| $V_{OL}$               | LOW-level output voltage                | $I_{OL} = -8 \text{ mA}$                     |     | -   | -   | 8.0   | V    |

| I <sub>OSH</sub>       | HIGH-level short-circuit output current | drive HIGH; cell connected to ground         | [1] | -   | -   | 129.0 | mA   |

| I <sub>OSL</sub>       | LOW-level short-circuit output current  | drive LOW; cell connected to V <sub>DD</sub> | [1] | -   | -   | 126.0 | mA   |

<sup>[1]</sup> The parameter values specified are simulated and absolute values.

#### 12.8 Strap pins S[3:0]

Table 15. Strap pins S[3:0] characteristics

| Symbol          | Parameter                      | Conditions     | Min                 | Тур  | Max                 | Unit |  |  |

|-----------------|--------------------------------|----------------|---------------------|------|---------------------|------|--|--|

| Input chara     | Input characteristics          |                |                     |      |                     |      |  |  |

| $V_{IH}$        | HIGH-level input voltage       |                | $0.7 \times V_{DD}$ | -    | -                   | V    |  |  |

| $V_{IL}$        | LOW-level input voltage        |                |                     |      | $0.3 \times V_{DD}$ | V    |  |  |

| Weak pull-      | Weak pull-down characteristics |                |                     |      |                     |      |  |  |

| I <sub>pd</sub> | pull-down current              | $V_I = V_{DD}$ | 25.0                | 50.0 | 95.0                | μΑ   |  |  |

## 12.9 JTAG and RESET\_N

Table 16. JTAG and RESET\_N characteristics

| Symbol          | Parameter                 | Conditions                       | Min                 | Тур | Max                 | Unit |

|-----------------|---------------------------|----------------------------------|---------------------|-----|---------------------|------|

| Input cha       | racteristics              |                                  |                     |     |                     | ·    |

| V <sub>IH</sub> | HIGH-level input voltage  |                                  | $0.7 \times V_{DD}$ | -   | -                   | V    |

| V <sub>IL</sub> | LOW-level input voltage   |                                  |                     |     | $0.3 \times V_{DD}$ | V    |

| Output ch       | naracteristics            | ,                                | '                   |     |                     |      |

| V <sub>OH</sub> | HIGH-level output voltage | RESET_N; I <sub>OH</sub> = 4 mA  | 2                   | -   | -                   | V    |

|                 |                           | JTAG; I <sub>OH</sub> = 2 mA     | 2                   | -   | -                   | V    |

| $V_{OL}$        | LOW-level output voltage  | RESET_N; I <sub>OL</sub> = -4 mA | -                   | -   | 0.8                 | V    |

|                 |                           | JTAG; I <sub>OL</sub> = −2 mA    | -                   | -   | 0.8                 | V    |

#### 2-lane DisplayPort to VGA adapter IC

# 13. Package outline

Fig 8. Package outline SOT619-1 (HVQFN48)

PTN3392

#### 2-lane DisplayPort to VGA adapter IC

# 14. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365 "Surface mount reflow soldering description"*.

#### 14.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

#### 14.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- · Through-hole components

- · Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- · Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- · The moisture sensitivity level of the packages

- · Package placement

- · Inspection and repair

- Lead-free soldering versus SnPb soldering

#### 14.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- · Solder bath specifications, including temperature and impurities

#### 2-lane DisplayPort to VGA adapter IC

#### 14.4 Reflow soldering

Key characteristics in reflow soldering are:

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 9</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 17 and 18

Table 17. SnPb eutectic process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |     |  |  |  |  |

|------------------------|---------------------------------|-----|--|--|--|--|

|                        | Volume (mm <sup>3</sup> )       |     |  |  |  |  |

|                        | < 350 ≥ 350                     |     |  |  |  |  |

| < 2.5                  | 235                             | 220 |  |  |  |  |

| ≥ 2.5                  | 220                             | 220 |  |  |  |  |

Table 18. Lead-free process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C)  Volume (mm³)  < 350 |     |     |  |  |  |

|------------------------|------------------------------------------------------|-----|-----|--|--|--|

|                        |                                                      |     |     |  |  |  |

|                        |                                                      |     |     |  |  |  |

| < 1.6                  | 260                                                  | 260 | 260 |  |  |  |

| 1.6 to 2.5             | 260                                                  | 250 | 245 |  |  |  |

| > 2.5                  | 250                                                  | 245 | 245 |  |  |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 9.