# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## USB Type-C power delivery PHY and protocol IC

Rev. 1.1 — 25 July 2017

**Product data sheet**

## 1. General description

PTN5100 is a single port USB Type-C Power Delivery (PD) PHY and Protocol IC that provides Type-C Configuration channel interface and USB PD Physical and Protocol layer functions to a System PD Port Policy Controller (Policy Engine and Device Policy Manager, Alternate mode controller). It complies with USB PD[1] and Type-C[2] specifications and delta updates of PD spec. This IC is targeted for a wide range of platforms (Standard Notebook PCs, Desktop PCs, Chromebooks, Tablets, Convertibles, Smart phones) and PC Accessories (e.g. Docks, Monitors, Cable adapters etc.) applications. PTN5100 is architected to deliver robust performance, compliant behavior, configurability and system implementation flexibility that are essential to tide over interoperability and compliance hurdles in the platform applications.

PTN5100 can support system realization of the following PD roles: (i) Provider (P) only, (ii) Provider/Consumer (P/C) (iii) Consumer only (C) (iv) Consumer/Provider (C/P). Further, it can be register programmed to operate in Type-C specific Upstream Facing Port (UFP), Downstream Facing Port (DFP) or Dual Role Port (DRP) role.

PTN5100 implements VCONN low RON switch with register programmable Forward Current protection feature. The VCON switch also provides Reverse current protection feature to detect reverse current flow into the system whenever (inductive or) charged cable is unplugged from the connector.

PTN5100 operates from platform power supply VDD, or it can also be powered from USB power VBUS directly, which is especially required for operation under Dead Battery (DB) condition and certain platform use cases. The host interface operates on VIO supply to facilitate interfacing to systems that use IO supply rail different from VDD supply rail.

It provides SPI/I2C interface for system host control/status update. The interface choice is pre- configured in NXP factory.

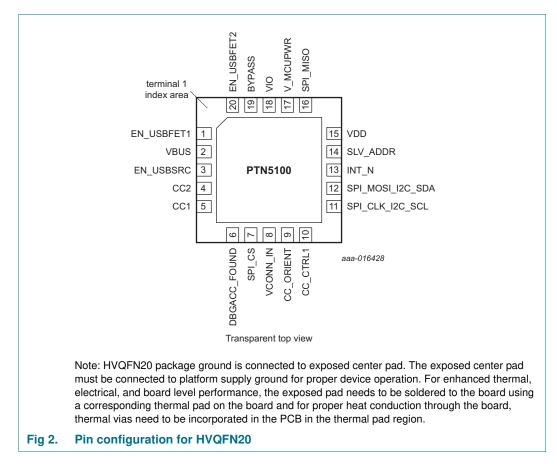

PTN5100 is available in a small footprint package option: HVQFN20 4 mm x 4 mm, 0.5 mm pitch.

#### **Remark:**

- 1. The term 'EC' is used interchangeably with 'Embedded Controller', 'AP', 'Application Processor' or 'System Management Controller, SMC' or System Host Controller throughout this document.

- 2. The terms 'PMIC', 'Power Management Interface Controller', 'Charger IC' are used interchangeably throughout this document.

## 2. Features and benefits

### 2.1 USB PD and Type-C Features

Complies with USB PD[1] and USB Type-C[2] specifications.

- Supports implementation of various system PD roles: P, P/C, C, C/P

- Supports Type-C role configurability

- Type-C role (DFP, UFP, DRP) is Non-Volatile Memory (NVM) and register programmable based on OEM platform requirements

- Implements UFP role pull down behavior to handle dead battery condition on battery powered platforms

- Supports register programmable and variable 'Rp' indication (for DRP/DFP usage and accessory detection)

- Implements 'Rd' indication on CC pin (for Device side implementation)

- CC detection/indication scheme based on Type-C role

- Indication of orientation detection via CC\_ORIENT pin and status register(s)

- Debug and Audio Accessory detection and indication in status register(s)

- Cooperatively works under the control of Policy controller MCU for power delivery negotiation and contract(s), Alternate mode and VDM exchanges

- Implements BMC (de)coding, 4B5B symbol (de)coding, CRC generation/checking, PD packet assembling/disassembling including Preamble, SOP, EOP, Good CRC response, Retries, Hard and Cable resets

- PD PHY and Protocol layer interface control and status update handled via SPI/I2C interface

- SOP\* Configurability

- Register programmable to generate and receive SOP, SOP', SOP'-debug, SOP", SOP"-debug" in DFP/DRP (host use case)

- Register programmable to receive and respond on SOP, SOP'-debug and SOP"-debug commands

- Supports low RON VCONN switch with enable/disable (Hi-Z) support

- Capable of maximum current delivery of 1 A over 2.7 V to 5.5 V

- Supports register programmable Forward current protection control

- Supports register programmable Reverse current protection

### 2.2 System protection features

- Back current protection on all pins when PTN5100 is unpowered

- CC1 and CC2 pins are 5.5 V tolerant

- VBUS pin and VBUS power path MOSFET enable pins are 28 V tolerant

## 2.3 General

- Delivers (active LOW enable) gate control signals for PMOS Power MOSFETs on VBUS source and sink power paths

- Provides dedicated IO pin (CC\_ORIENT) for indicating Cable/plug orientation and IO pin (DBGACC\_FOUND) for indicating Debug accessory detection

- Delivers up to 30 mA (max) for powering Policy controller MCU

- Supports SPI slave interface (SPI modes 1 and 2 supported) up to 30 MHz

- Supports I2C slave interface standard mode (100 kHz), Fast mode (400 kHz) and Fast mode plus (1 MHz)

- I2C Device slave address programmable up to 3 values

- Supports 3.3 V or 1.8 V capable I<sup>2</sup>C-bus or SPI interface

- Supports register access device configuration, control and status/interrupt interfacing through Slave I<sup>2</sup>C-bus interface

- Power supplies VDD (3.3 V ±10 %) or VBUS

- ◆ Tolerant up to 28 V on VBUS and operational up to maximum of 25 V on VBUS

- Operating temperature –20 °C to 85 °C

- ESD 8 kV HBM, 1 kV CDM

- Package: HVQFN20 4 mm × 4 mm, 0.5 mm pitch

## 3. Applications

- PC platforms: Notebook PCs, Desktop PCs, Ultrabooks, Chromebooks

- Tablets, 2:1 Convertibles, Smartphones and Portable devices

- PC accessories/peripherals: Docking, Mobile Monitors, Multi-Function Monitors, Portable/External hard drives, Cable adaptors, Dongles and accessories, etc.

## 4. Ordering information

| Type number | Topside<br>marking | Package |                                                                                                                                 |          |  |

|-------------|--------------------|---------|---------------------------------------------------------------------------------------------------------------------------------|----------|--|

|             |                    | Name    | Description                                                                                                                     | Version  |  |

| PTN5100BS   | 5100               | HVQFN20 | plastic thermal enhanced very thin quad flat package;<br>no leads; 20 terminals; body $4 \times 4 \times 0.85 \text{ mm}^{[2]}$ | SOT917-4 |  |

| PTN5100ABS  | 510A               | HVQFN20 | plastic thermal enhanced very thin quad flat package;<br>no leads; 20 terminals; body $4 \times 4 \times 0.85 \text{ mm}^{[3]}$ | SOT917-4 |  |

[1] Total height after printed-circuit board mounting <=1 mm (maximum)

[2] Supported system interface - SPI

[3] Supported system interface - I<sup>2</sup>C

Product data sheet

## 4.1 Ordering options

| Table 2. Ordering options |                          |         |                                                  |                           |                                                    |

|---------------------------|--------------------------|---------|--------------------------------------------------|---------------------------|----------------------------------------------------|

| Type number               | Orderable<br>part number | Package | Packing method                                   | Minimum<br>order quantity | Temperature                                        |

| PTN5100BS                 | PTN5100BSMP              | HVQFN20 | Reel 13" Q2/T3<br>*standard mark SMD<br>dry pack | 6000                      | $T_{amb} = -20 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

| PTN5100ABS                | PTN5100ABSMP             | HVQFN20 | Reel 13" Q2/T3<br>*standard mark SMD<br>dry pack | 6000                      | $T_{amb} = -20 \text{ °C to } +85 \text{ °C}$      |

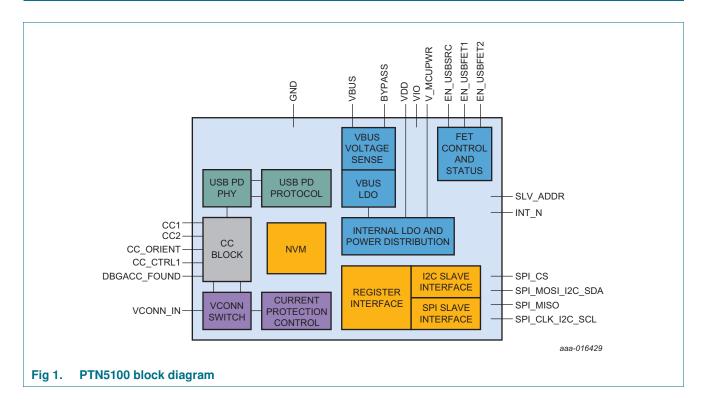

## 5. Block diagram

## 6. Pinning information

## 6.1 Pinning

**Product data sheet**

## 6.2 Pin description

| Symbol       | Pin | Pin<br>direction | Pin Type                  | Description                                                                                                                                                                                                                                                                            |

|--------------|-----|------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN_USBSRC    | 3   | Output           | Open drain                | USB PD VBUS Source Power path PMOS FET gate<br>Active Low enable.                                                                                                                                                                                                                      |

|              |     |                  |                           | At default/POR, this pin is Hi-Z; PTN5100 drives this<br>pin LOW based on Type-C connection state and/or<br>policy controller MCU command.                                                                                                                                             |

|              |     |                  |                           | The pin status can be read in the internal register(s)                                                                                                                                                                                                                                 |

| EN_USBFET1   | 1   | Output           | Open drain                | USB PD VBUS Source or Sink Power path PMOS FET gate Active Low enable.                                                                                                                                                                                                                 |

|              |     |                  |                           | At default/POR, this pin is Hi-Z; PTN5100 drives this pin LOW based on Type-C connection state and/or policy controller MCU command.                                                                                                                                                   |

|              |     |                  |                           | The pin status can be read in the internal register(s).                                                                                                                                                                                                                                |

| EN_USBFET2   | 20  | Output           | Open drain                | USB PD VBUS Source or Sink Power path PMOS FET gate Active Low enable.                                                                                                                                                                                                                 |

|              |     |                  |                           | At default/POR, this pin is Hi-Z; PTN5100 drives this pin LOW based on policy controller MCU command.                                                                                                                                                                                  |

|              |     |                  |                           | The pin status can be read in the internal register(s)                                                                                                                                                                                                                                 |

| CC1          | 5   | IO               | Custom IO                 | Type-C Configuration channel #1                                                                                                                                                                                                                                                        |

|              |     |                  |                           | TVS or similar protection diode (e.g.<br>PESD5V0S1USF, PESD5V0S1UL, etc.) shall be<br>used to protect the CC1/2 pins from<br>overshoot/undershoot during cable plug/unplug and<br>cable discharge events.                                                                              |

| CC2          | 4   | IO               | Custom IO                 | Type-C Configuration channel #2                                                                                                                                                                                                                                                        |

|              |     |                  |                           | TVS protection diode (e.g. PESD5V0S1USF,<br>PESD5V0S1UL, etc) shall be used to protect the<br>CC1/2 pins from overshoot/undershoot during cable<br>plug/unplug and cable discharge events.                                                                                             |

| CC_ORIENT    | 9   | Output           | CMOS IO on VIO power      | This pin indicates Type-C cable plug orientation.                                                                                                                                                                                                                                      |

|              |     |                  | rail                      | The pin's polarity is inverted at power-on reset and<br>the PD policy controller MCU has to initialize<br>PTN5100D before the pin level is valid. After the<br>initialization, the pin indicates orientation as follows:<br>LOW = Normal plug orientation (CC<br>communication on CC1) |

|              |     |                  |                           | HIGH = Reverse plug orientation (CC communication on CC2)                                                                                                                                                                                                                              |

|              |     |                  |                           | Default pin value is LOW even if there is no<br>connection or normal plug connection                                                                                                                                                                                                   |

| CC_CTRL1     | 10  | Input            | Analog Input              | Input to indicate whether to present 'Rd' or Open on CC pin under Unpowered condition                                                                                                                                                                                                  |

| DBGACC_FOUND | 6   | Output           | CMOS IO on VIO power rail | Indicates the presence of Type-C Debug accessory<br>Default/POR value is LOW                                                                                                                                                                                                           |

|              |     |                  |                           | 1                                                                                                                                                                                                                                                                                      |

| Symbol               | Pin           | Pin<br>direction | Pin Type                                                                                      | Description                                                                                                                                                                               |  |

|----------------------|---------------|------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SPI_MOSI_<br>I2C_SDA | 12            | IO               | Open drain IO (I2C<br>mode) referenced to VIO<br>voltage<br>V_MCUPWR power rail<br>(SPI mode) | Dual purpose pin. In I2C slave mode, this serves as<br>I2C data input/output (open drain)<br>In SPI slave mode, this pin serves Master Output<br>Slave Input function (push pull CMOS IO) |  |

| SPI_MISO             | 16            | Output           | V_MCUPWR rail                                                                                 | This serves Master Input Slave Output function of SPI interface                                                                                                                           |  |

| SPI_CLK_I2C_SCL      | 11            | Input            | Open drain IO (I2C<br>mode) referenced to VIO<br>voltage<br>V_MCUPWR power rail<br>(SPI mode) | Dual purpose pin. In I2C slave mode, this serves a<br>I2C clock input (open drain).<br>In SPI slave mode, it serves as SPI clock input pin                                                |  |

| SPI_CS               | 7             | Input            | V_MCUPWR rail                                                                                 | This pin provides SPI chip select Input                                                                                                                                                   |  |

| INT_N                | 13            | Output           | Open drain                                                                                    | Level triggered interrupt. Open drain output; This pin needs to be externally pulled up VIO.                                                                                              |  |

| SLV_ADDR             | 14            | Ternary<br>input | V_MCUPWR rail                                                                                 | This pin is usable only when VDD is valid<br>Ternary slave address (I2C) pin                                                                                                              |  |

| V_MCUPWR             | 17            | Output           | Power                                                                                         | This pin delivers current up to 30 mA (max) to policy controller MCU. External supply de-coupling capacitor(s) (2.2 $\mu$ F ±10 % ceramic capacitor) are required                         |  |

| VIO                  | 18            | Input            | Power                                                                                         | IO domain power supply. External supply de-coupling capacitor(s) are required                                                                                                             |  |

| VBUS                 | 2             | Input            | Power                                                                                         | VBUS power supply. External supply de-coupling capacitor(s) are required                                                                                                                  |  |

| VDD                  | 15            | Input            | Power                                                                                         | Core domain power supply. External supply de-coupling capacitor(s) are required                                                                                                           |  |

| BYPASS               | 19            | Internal         | Internal power rail                                                                           | Internal power rail. A ceramic capacitor (2.2 $\mu F$ $\pm 10$ %) is to be connected to this pin                                                                                          |  |

| GND                  | Center<br>pad |                  | GND                                                                                           | Ground Center pad                                                                                                                                                                         |  |

#### Table 3. Pin description ...continued

## 7. Functional description

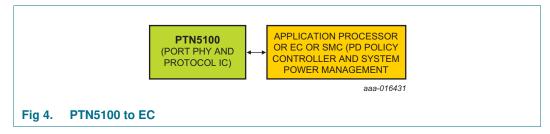

PTN5100 is a 1-port USB Type-C PD Physical and Protocol Layer IC that can be used to realize single or multi-port USB Type-C PD and/or Alternate mode implementations. It complies with USB PD [1] and Type-C specifications [2]. PTN5100 supports the following use configurations:

- 1. On a System Host (single or multi-port configuration)

- a. Controlled by a PD Policy controller and/or Alternate mode control MCU

- b. Controlled by Embedded controller or Application processor

- 2. On a Device platform

a. Controlled by a PD policy controller or Alternate mode control MCU or existing processor

On the host and device use cases, different PD roles are possible: (P), (P/C), (C), (C/P).

PTN5100 supports two levels of configurability and programmability:

- NVM configuration options configurability in the factory through NVM configuration utility

- I2C/SPI register programmable read/write accesses at application/Firmware (FW) level

PTN5100 can be partitioned into the following major functional blocks along with their respective interfaces:

- Type-C Configuration Channel functional block

- USB Power Delivery function

- VCONN Low RON Switch

- Power FET Enable Control

- MCU interface and Control

The following subsections describe the PTN5100 with its major functional blocks.

#### 7.1 Type-C Configuration Channel functional block

Type-C Configuration Channel (CC) function operates as a front end to cable/plug interface.

PTN5100 can operate autonomously or under MCU control. To support use cases especially with autonomous mode, PTN5100 implements HW circuitry to perform the following operations:

- Applying 'Rp' or 'Rd' depending on the (NVM) configured role

- · Detecting cable/plug connect and disconnect events

- Indicating Type-C current limit level in a system under DFP role

- Detecting the current level supported by remote end under UFP role

- Identifying plug orientation and indicating through CC\_ORIENT pin

- Identifying Type-C Debug accessory detection and indicating through DBGACC\_FOUND pin

- Updating event, interrupt and status registers and raising interrupt signal using INT\_N pin

In order to provide reliable connect/disconnect event triggers, debouncing is also implemented as per [2].

PTN5100 allows for NVM configurability and/or register programmability to enable usage under different platform configurations.

PTN5100

## 7.2 USB Power Delivery Function

In general, the Embedded Controller (EC) or System Management Controller (SMC) handles the overall Application/Platform power management given the system states, battery status, etc. It reviews capabilities and status of various power providers (USB PD, AC-DC adapter, battery, docking, etc.) dynamically and determines a specific source for powering/charging the platform - the power source selection is an important and platform dependent aspect of Application power delivery scheme.

- For example, in some computing applications, EC plays a central role in controlling the various power sources including USB PD. To support this, PTN5100 and Policy controller MCU can be configured to negotiate and agree on power contract based on command/response exchanges with EC

- In several applications, EC may not even exist or EC wants to play a hands-off role. To support these applications, PTN5100 and Policy controller MCU can be configured to operate autonomously

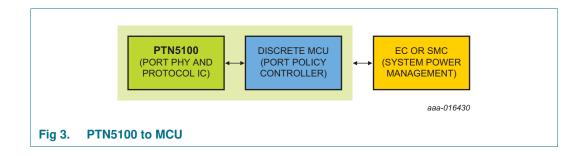

In a Type-C PD implementation, the system partitioning involves the following parts:

- Port PHY and Protocol layer functions  $\rightarrow$  PTN5100

- Port policy engine and device policy management, Alternate mode support → Discrete policy controller MCU

- System management  $\rightarrow$  EC or SMC

PTN5100 implements USB PD PHY layer and HW intensive Protocol functions and it works along with a discrete MCU to implement Full PD functionality. The combined 2-chip system solution (PTN5100 and MCU) can be configured to support one or more of the following PD roles:

- 1. PD Consumer (C)

- 2. PD Consumer/Provider (C/P)

- 3. PD Provider (P)

- 4. PD Provider/Consumer (P/C)

The interface between PTN5100 and Policy controller MCU can be either SPI or I2C. PTN5100 provides a transparent set of commands and register interface for the MCU to control the operation and ensure safe/suitable system behavior/response. PTN5100 Application Programming guide [3] describes the register set supported for the PD control, status updates and operational control/sequences.

The policy controller MCU implements PD port policy layer as per [1]. The default PD power profiles are configured in the MCU and the EC could request for specific profile and PD contract based on platform application. The 2-chip solution can operate autonomously or under EC control.

PTN5100

PTN5100 implements USB PD PHY layer function as follows:

- Slew rate controlled IO

- · Bit transmission and data recovery

- Bi-phase Mark Coding

- 4B5B Line coding

- CRC computation and checking

It handles the following Protocol layer functions:

- Data Packetization and Extraction

- Good CRC Response

- Automated Retries

- Hard reset, Cable reset

- Tx and Rx buffer management

It handles both Transmit and Receive operation and it maintains dedicated TX and RX data buffers. To minimize chances of collision, PTN5100 checks the CC line before start of transmission. Once the data is transmitted or received, the I2C interface status is updated and MCU is interrupted.

BIST mode (Tx, Rx) is also supported.

Note: NXP is open to engage on Firmware licensing to give a head start to customers on USB PD Policy and Alternate mode Firmware front. Please contact NXP for further details.

## 7.3 VCONN Switch

Type-C specification defines a dedicated power pin VCONN\_IN to deliver power to full featured cables, dongles and cable adapters.

PTN5100 implements very low RON switch that can deliver up to 1 A current. Depending on the pin over which CC communication is established, VCONN power is delivered into the other CC pin. With patented architecture, the switch implements Soft Start behavior to avoid heavy inrush current flow.

The VCONN switch is to be used only when VCONN\_IN lies within the valid range (2.7 V to 5.5 V).

The VCONN switch can be enabled or disabled by Firmware. When in disabled condition, it presents Hi-Z condition. The switch implements two important features related to robustness:

- Forward Current Protection (FCP) that monitors over current condition (over current limit is register programmable) and trips the connection by disabling the switch

- Reverse Current Protection (RCP) that avoids reverse current flow back into the system due to inductive effects of cable unplug events

Further, both FCP and RCP circuitry shall be activated only when VCONN\_IN is within valid range.

#### 7.3.1 Forward Current Protection (FCP)

PTN5100 implements Forward current protection in VCONN switch that keeps monitoring for a current flow above the preconfigured level from the system side and whenever the threshold is exceeded, the switch is opened and an interrupt event is raised. The switch remains open until the port controller MCU reads the status and re-enables the switch.

#### 7.3.2 Reverse Current Protection (RCP)

PTN5100 implements Reverse Current Protection in VCONN switch that watches for any instantaneous reverse current flow back into the system via VCONN and whenever the preconfigured threshold is exceeded, the switch is opened and an interrupt event is raised. The switch remains open until the port controller MCU reads the status and re-enables the switch.

#### 7.4 Power FET control

PTN5100 implements three dedicated open drain IOs that can be used to control the external power MOSFETs and enable/ disable VBUS source and sink power paths of the system. These are enabled or disabled based on PD power role (provider or consumer) of the Type-C interface. Based on PD negotiation and contract, the policy controller MCU enables/disables the specific power path (source FET or sink FETs).

- EN\_USBSRC: This pin is used to enable/disable the power MOSFETs that corresponds to VBUS source (e.g. 5V regulated output). The FET enable can be configured and controlled through the register interface by the MCU. The pin status is monitored and updated in a status register.

- EN\_USBFET1: This pin is used to enable/disable the power MOSFETs that corresponds to USB PD power from external power sources or delivering VBUS power to external peripherals. Its specific use as a VBUS source or sink path control is programmable. The FET enable can be configured and controlled through the register interface by the MCU. The pin status is monitored and updated in a status register.

PTN5100

• EN\_USBFET2: This pin is used to enable/disable the power MOSFETs that corresponds to USB PD power from external power sources or delivering VBUS power to external peripherals. It specific use as a VBUS source or sink path control is programmable. The FET enable can be configured and controlled through the register interface by the MCU. The pin status is monitored and updated in a status register.

## 7.5 MCU interface and control

PTN5100 works along with policy controller MCU to realize USB PD functionality and/or Alternate mode support. The MCU can control and interface with PTN5100 through a dedicated I2C/SPI interface. In a given system implementation, only one of the two interfaces (I2C, SPI) can be used. This selection can be static configured via NVM.

PTN5100 provides up to three I2C slave address combinations based on ternary pin (SLV\_ADDR) setting as per the table below.

| SLV_ADDR pin | Device address (Write/read) |  |

|--------------|-----------------------------|--|

| GND          | 0xE0/0xE1                   |  |

| VDDIO        | 0xE4/0xE5                   |  |

| Unconnected  | 0xE8/0xE9                   |  |

#### Table 4.I2C slave address combinations

#### 7.5.1 l<sup>2</sup>C-bus interface

PTN5100 has a slave I2C interface through which it provides a mechanism for control and status interaction/communication with the MCU. It supports Standard mode, Fast mode and Fast mode plus.

#### 7.5.1.1 I2C writes

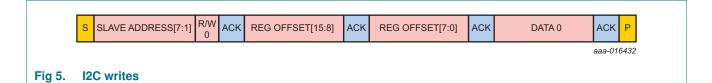

The following figure shows the basic protocol for I2C writes. A 16-bit offset is used to address each register.

#### 7.5.1.2 I2C reads

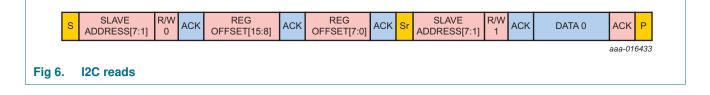

The following figure shows the basic protocol for I2C reads. They start off like I2C writes by specifying a 16-bit register offset. This is followed by a repeat start condition, the Slave Address (Read), and the read data.

#### 7.5.1.3 I2C address auto-incrementing

Bursts are allowed during writes and reads. Bit 15 of the register offset is the auto-increment indication. If '0' then the internally generated MMIO address will not increment with each data byte. If '1', then the address will increment with each data byte.

A detailed description of the I<sup>2</sup>C-bus specification, with applications, is given in user manual UM10204, "I<sup>2</sup>C-bus specification and user manual" [4]. Referring to I2C protocol, PTN5100 positively acknowledges all 256 register offset addresses, though there are certain undefined address offsets.

#### 7.5.2 SPI interface

PTN5100 provides an SPI slave interface as well. It supports SPI modes 1 and 2. This interface exposes same register interface as that of I2C. Its main advantage is faster command and data transport and relaxes MCU response time/latency requirements.

#### 7.5.3 Register interface

PTN5100 Application programming guide [3] describes the various registers with their bit definitions, POR values and the various functions. Also, sample 'C' programs corresponding to various functions and operations are given. This guide can be used by the platform system architects to implement the EC firmware to control the operations with PTN5100. Refer to programming guide for more information. The register definitions are also described in the guide.

#### 7.5.4 Relevant Interface pins - SLV\_ADDR, SPI\_CLK\_I2C\_SCL, SPI\_MOSI\_I2C\_SDA, SPI\_CS, SPI\_MISO, INT\_N

- SLV\_ADDR is a ternary input pin that is used to support up to 3 slave PTN5100 devices on a given platform. This pin can be pulled to V\_MCUPWR rail, left open or pulled to GND.

- While in SPI mode, SPI\_CLK\_I2C\_SCL, SPI\_MISO, SPI\_MOSI\_I2C\_SDA and SPI\_CS provide the necessary interface for connecting to SPI master controller on the MCU.

- While in I2C mode, SPI\_CLK\_I2C\_SCL and SPI\_MOSI\_I2C\_SDA are used for I2C clock and data interfacing to MCU

- INT\_N pin is used to raise Active LOW level triggered interrupt signal to EC. PTN5100

processes various events and raises interrupt that require SMC intervention. Once all

relevant events are processed by the MCU, the INT\_N pin goes HIGH. At POR, this

pin remains HIGH (when VIO is valid). The specific events that can generate the

interrupt can be selected.

#### 7.6 **Power supplies**

PTN5100 is designed to operate under various power supplies. It can operate under both normal battery and dead battery environments (while drawing power from VBUS). PTN5100 handles power supply transitions (VBUS, VDD) transparently and there is no specific power supply ramp requirement imposed on the system (between VDD and VIO rails) also.

The following table highlights the power supplies and operating conditions for PTN5100.

| Valid power supply<br>input combination | Operational condition                                                                                                                            | Remarks                                                        |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| VDD, VIO                                | Normal powered condition (both battery based or non-battery based platforms)                                                                     | All interfaces operational                                     |  |

| VDD, VIO, VBUS                          | Normal powered condition; Host Platform<br>may be powered/charged through VBUS<br>simultaneously                                                 | All interfaces operational                                     |  |

| VBUS,<br>VIO(=V_MCUPWR)                 | Dead battery in battery based platforms or<br>Normal powered condition under other<br>platforms; Host Platform powered/charged<br>through USB PD | All interfaces operational                                     |  |

| VBUS                                    | Dead battery operation; PTN5100 draws<br>power from VBUS for its operation; Host<br>Platform may be powered/charged through<br>USB PD later      | PTN5100 pins<br>(dependent on VIO rail)<br>are not operational |  |

#### Table 5. Power supplies vs. operating conditions

**Remark:** The Policy controller MCU is powered by PTN5100.

The relevant pins associated with this functional block are:

- VDD

- VIO

- VBUS

- V\_MCUPWR

- BYPASS

## 8. PTN5100 - Use case view

Given that USB Power Delivery could address the requirements of a wide set of markets and product segments, PTN5100 is designed to work over a range of product categories, platform applications, use cases and usage roles. With its configurability, it can be serve the needs of both general and custom applications. Not limited to these but the following subsections illustrate a set the use cases of PTN5100.

## 8.1 System use cases

#### 8.1.1 USB PD Provider/Consumer - Notebook/Ultrabook/Chromebook/Tablet PC

condition) 1 of 2

## 8.1.1.1 Brief description

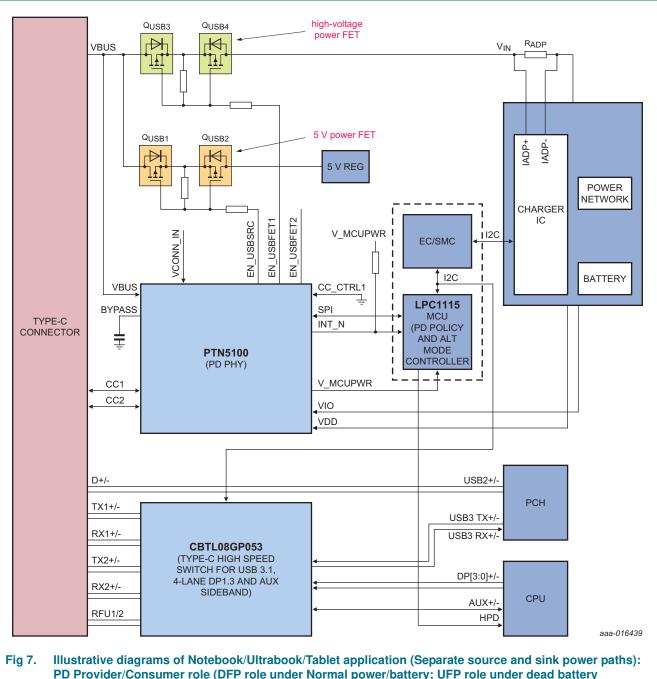

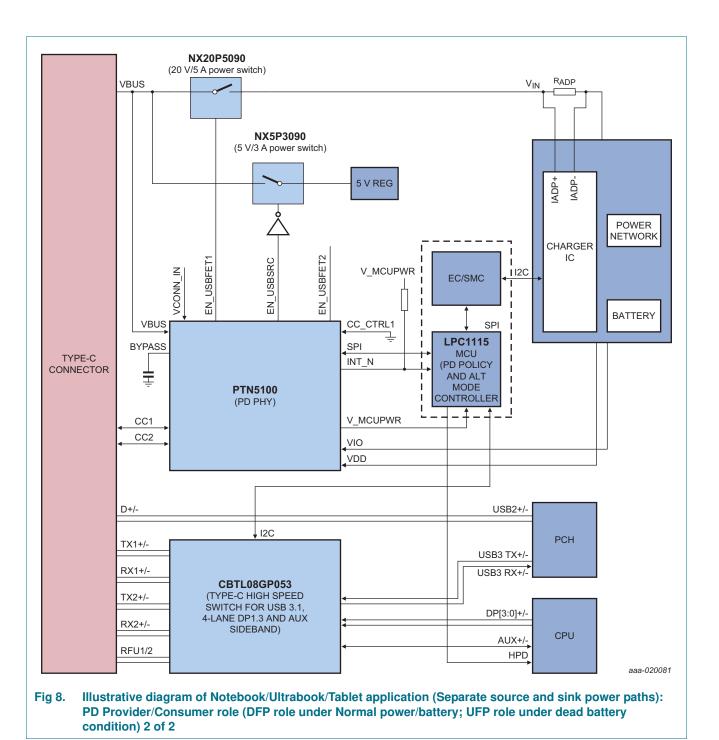

In this illustration, the 2-chip solution (PTN5100 + Policy controller & Alternate mode MCU) is behind the Type-C receptacle and it is configured as a PD Provider/ Consumer. The EC interfaces with the Charger IC to configure at specific voltage/ current levels to perform battery charging and/or powering of the platform.

This application is expected to:

- Source VBUS 5 V (if not under dead battery)

- · Charge from VBUS PD and AC barrel power, if applicable

- Source VCONN power

The EC communicates with controller MCU via an I2C bus and control the operations. The PTN5100 and MCU can operate autonomously or under the control of EC.

Figure 7 and Figure 8 illustrate the configurations with discrete MOSFETs and Power switches respectively. PTN5100 controls the power FETs/switch to determine charging (Green colored FETs/switch on VBUS power inputs) and 5 V VBUS power delivery (Orange colored FETs/switch on VBUS). If NXP5P3090 is used, then the Active HIGH switch enable control is required to be generated based on the EN\_USBSRC control output.

An important aspect to consider here is that PTN5100 would indicate a 'Rd' pulldown (UFP) under dead battery condition and this enables the port partner to provide VBUS at 5 V (provided the port partner is capable of acting as DFP). However, after system starts up, role swap has to be performed to become DFP. This is handled by PTN5100 and MCU together.

CC\_ORIENT and DBGACC\_FOUND outputs can be used by the platform, if necessary.

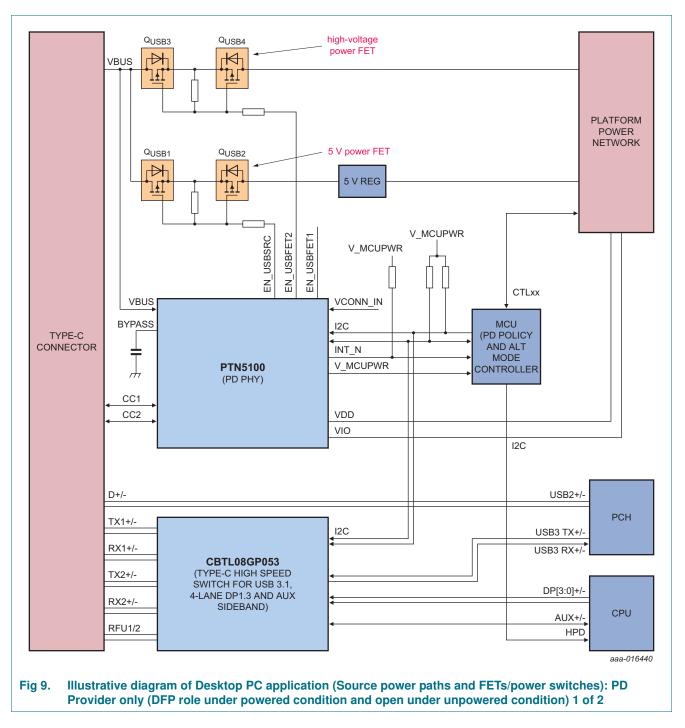

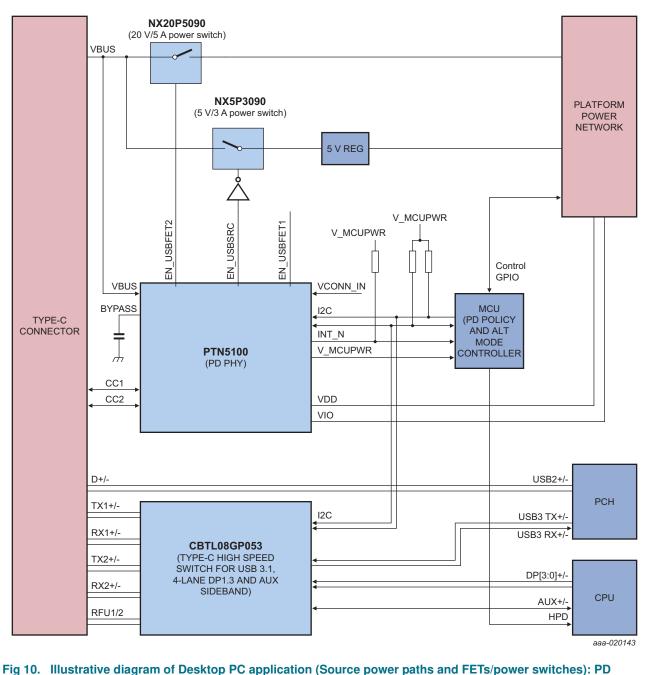

## 8.1.2 USB PD Provider with Type-C receptacle - Desktop PC

PTN5100

J 10. Illustrative diagram of Desktop PC application (Source power paths and FE Is/power switches): PL Provider only (DFP role under powered condition and open under unpowered condition) 2 of 2

#### 8.1.2.1 Brief description

In this illustration also, the 2-chip solution (PTN5100+ Policy controller & Alternate mode control MCU) is behind Type-C receptacle and it is configured to act as a PD Provider (Autonomous mode) based on pre-configured Power profiles. The PC system uses the ATX or similar power supply and it can deliver power to all USB ports. In this diagram, there is no EC to interface with and so, the 2-chip solution (MCU and PTN5100) is configured for autonomous operation.

For USB ports, this application:

- Sources VBUS 5 V

- Sources USB PD power (specific wattage depends on the system application)

- Sources VCONN power

<u>Figure 9</u> and <u>Figure 10</u> illustrate the configurations with discrete MOSFETs and Power switches respectively. PTN5100 controls the power FETs/switches to VBUS 5V and PD power (Orange colored FETs/Switch). The handshake with power supply unit is dependent on OEM/ODM design.

An important aspect to consider here is that a Desktop PC does not have dead battery condition though it can be unpowered. If not powered, it presents 'Open' on CC pins. After power up initialization, PTN5100 would indicate 'Rp'. After PD negotiation, the Desktop platform could deliver higher voltage/current.

CC\_ORIENT and DBGACC\_FOUND connections can be used based on platform need.

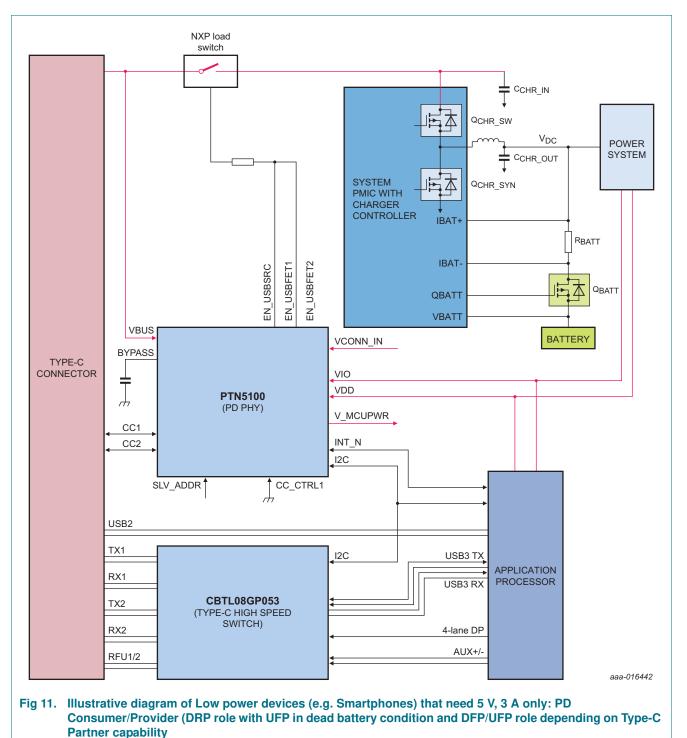

#### 8.1.3 USB PD Consumer/Provider (Smartphone use case) - Standalone PTN5100

#### 8.1.3.1 Application description

In this illustration, PTN5100 is behind Type-C receptacle and it is configured to act as a PD consumer/ Provider. It is important to note that there is no dedicated policy controller MCU associated with the PD functionality as this application can operate with 5V, 3A only. Under normal battery/powered condition, PTN5100 is configured as DFP, DRP or UFP based on register configuration setting and it performs cable/plug connect and disconnect detection, orientation detection. However, on dead battery condition, it defaults to UFP role. The power path FET control may or may not be used in the application depending on the capabilities of System PMIC.

This application is expected to

- Receive VBUS 5 V @ 3 A

- Provides VBUS 5 V @ 3 A

- Sourcing VCONN power is dependent on the Type-C role taken

PTN5100 operates autonomously but it is possible for the system processor to control it via I2C interface. Though there may not be a need to negotiate higher voltage/current, the platform may still need to support Alternate modes and VDMs. The Application Processor is used to handle those capabilities.

**Product data sheet**

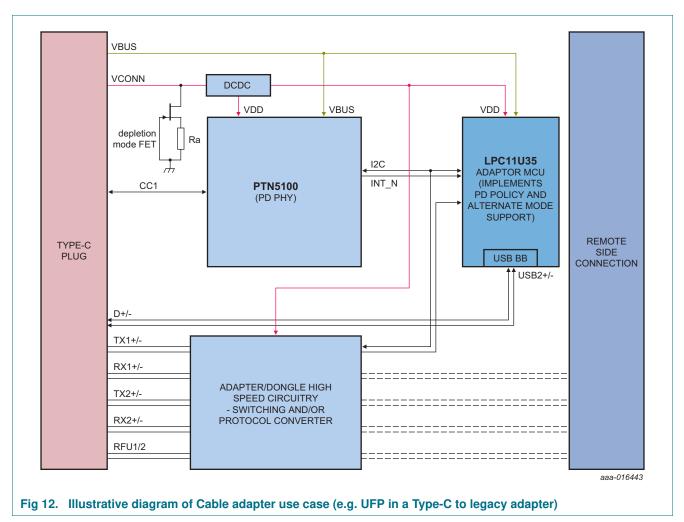

## 8.1.4 Type-C cable adapters with PTN5100

#### 8.1.4.1 Application description

In this illustration, PTN5100 is inside Type-C cable adapter operating in UFP role. Some example use cases are Type-C to DP adapter, Type-C to VGA adapter, Type-C to Thunderbolt adapter etc. PTN5100 serves as PD PHY layer device for a Cable adapter management MCU or dedicated PD MCU wherein PD policy management, Alternate mode and VDM support are handled. The USB Billboard device is assumed to be implemented as part of adapter management MCU.

The cable adapter implementation operates on VCONN supply. Discrete depletion mode FET has to be used in the application for 'Ra' indication on CC pin.

**PTN5100**

## 8.1.5 USB PD Consumer/Provider with Type-C receptacle

**PTN5100**

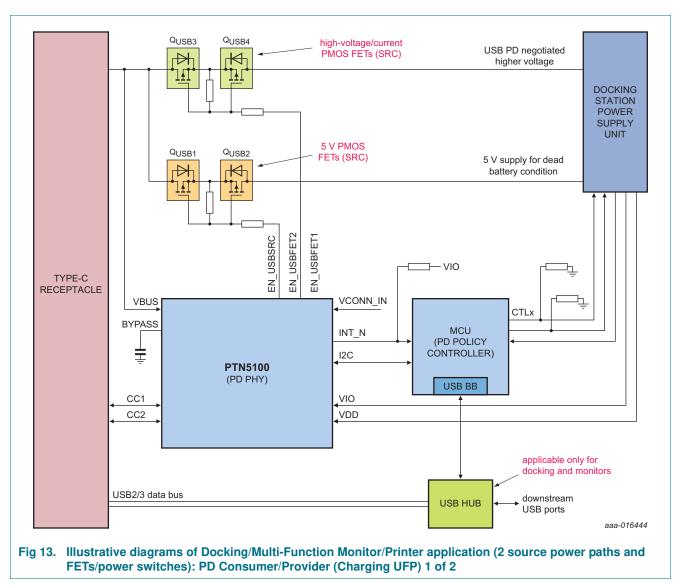

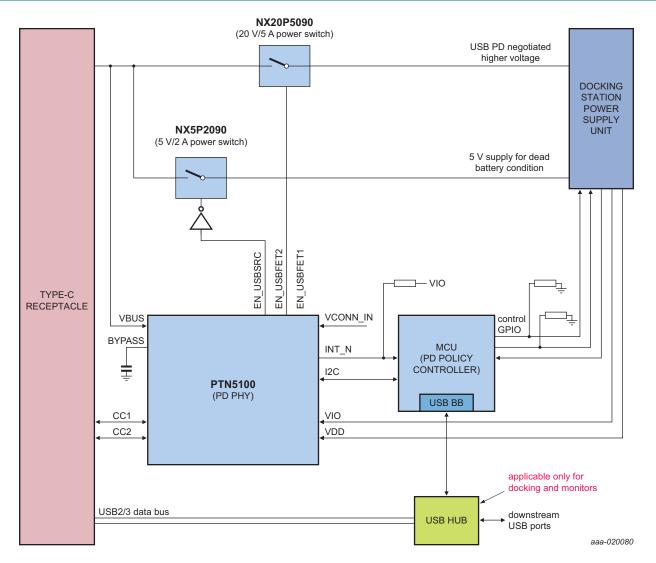

Fig 14. Illustrative diagrams of Docking/Multi-Function Monitor/Printer application (2 source power paths and FETs/power switches): PD Consumer/Provider (Charging UFP) 2 of 2

#### 8.1.5.1 Application description

The example applications are Multi-function monitor, Dock or Printer. PTN5100 is configured for Charging UFP role. The policy controller MCU would probe PTN5100 to make sure there is no dead battery device connected at the other end. If a pulldown 'Rd' is detected at the remote cable end, this platform supplies VBUS 5V. Once the remote end system is capable of performing power role swap, the roles would be reversed.

This application is expected to:

- Receive VBUS 5 V (or provide power during Dead battery operation VBUS 5 V)

- · Provides VBUS PD power

The PD software running on the MCU controls the power FETs/switches to determine VBUS 5 V and USB PD power delivery (Orange colored power FETs/switch on VBUS).