Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Preconfigured DSP System** for Hearing Aids

#### Description

RHYTHM™ R3920 is a preconfigured hearing health processor based on a DSP platform. Featuring 16 channels of Wide Dynamic Range Compression and Impulse Noise Reduction, R3920 encompasses a rich set of advanced sound processing algorithms and is ideal for high end, full-featured hearing aids. The R3920 hybrid is available in one of the industry's smallest form-factors and is well-suited for all hearing aid types, including those placed deep in the ear canal.

#### **Features and Benefits**

Wide Dynamic Range Compression (WDRC) – R3920 contains 16 Channels of Wide Dynamic Range Compression, each with individual settings for Squelch Attentuation and Threshold, Low Level Gain, High Level Gain, Upper and Lower Thresholds, and Compression Ratio. Independent level detectors for both Squelch and WDRC are available with customizable attack and release times set in each channel.

**Impulse Noise Reduction (INR)** – Loud, impulsive sounds in the environment such as slamming doors, dropped items, or clattering dishes can become uncomfortably or dangerously loud in a traditional hearing aid. The INR algorithm actively monitors and processes the incoming acoustic signal for such sounds. It ensures that the output sound preserves the integrity of the speech signal and is descriptive of the environment, while maintaining an optimal comfort level for the hearing aid user.

Acoustic Environment Classification – iSceneDetect™ analyzes incoming acoustic signals in order to determine the appropriate classification for a given acoustic environment. Six separate environments are supported by iSceneDetect: quiet, speech in quiet, noise, speech in noise, music, and wind. The feature uses this classification to automatically adjust settings of other features for optimum audio performance.

iLog™ 4.0 Datalogging – Enables the recording of various hearing aid parameters such as program selection, volume setting and ambient sound levels. The sampling interval can be configured to record from every 4 seconds up to once every 60 minutes. The manufacturer can program the fitting system to retrieve the data for further analysis after an extensive period of wearing the hearing aid. This allows the audiologist to fine tune the hearing aid and further counsel the end-user.

**Automatic Adaptive Directionality** – The Automatic Adaptive Directional Microphone (ADM) algorithm automatically reduces the level of sound sources that originate from behind or to the side of the hearing aid wearer without affecting sounds from the front. The algorithm can also gather input from the acoustic iSceneDetect environmental classifier algorithm and automatically select whether directionality is needed or not, translating into additional current savings.

#### ON Semiconductor®

www.onsemi.com

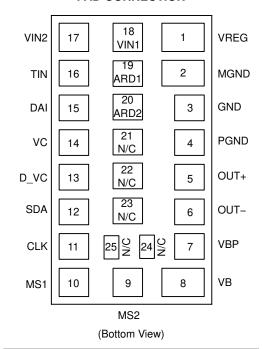

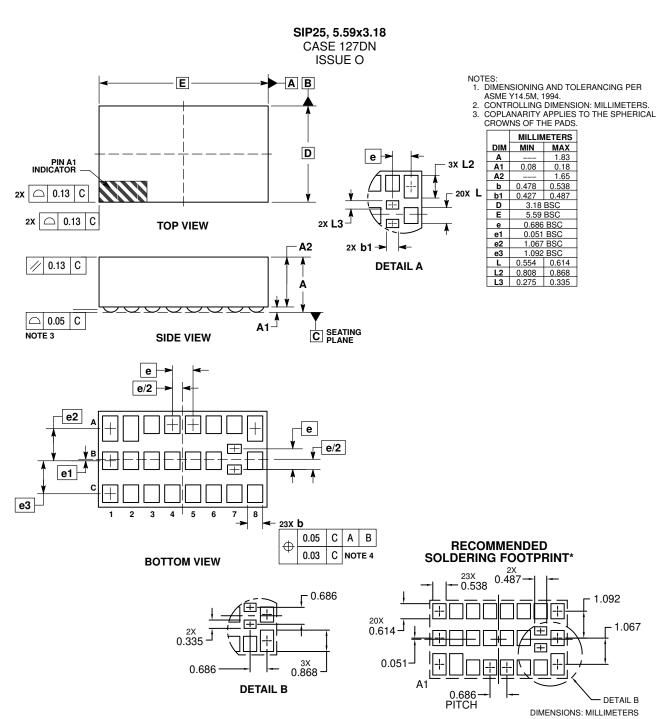

25 PAD HYBRID CASE 127DN

#### PAD CONNECTION

#### MARKING DIAGRAM

R3920–CFAB XXXXXX

R3920-CFAB = Specific Device Code XXXXXX = Work Order Number

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 9 of this data sheet

Adaptive Feedback Canceller – Automatically reduces acoustic feedback. It allows for an increase in the stable gain while minimizing artifacts for music and tonal input signals. Additional tuning parameters make for more precise tuning of the algorithm to the hearing aid. The development tools for the R3920 offer a special calibration module to help assess the maximum stable gain in the hearing aid the manufacturer has built to further optimize the Adaptive Feedback Canceller algorithm.

**Adaptive Noise Reduction** – The Adaptive Noise Reduction algorithm monitors noise levels independently in 128 individual bands and employs advanced psychoacoustic models to reduce noise and provide user comfort. The algorithm can be set for varying levels of aggressiveness from 3 dB up to 12 dB.

**Automatic Receiver Detection** – For Receiver–in–Canal (RIC) devices with field replaceable receivers, R3920 allows manufacturers to code different receiver types so they are automatically recognizable in software, eliminating potential selection errors.

**Tinnitus Masking** – R3920 is equipped with a noise source that can be used to mask tinnitus. The noise can be shaped and attenuated and then summed into the audio path either before or after the volume control. A white noise signal is generated and inserted into the audio path either before or after the volume control. Filtering can be performed on the white noise signal in order to shape the noise signal to a desired frequency and bandwidth. The tinnitus masker can be used as a stand alone tinnitus making device or as part of a hearing aid.

**EVOKE**<sup>™</sup> **Advanced Acoustic Indicators** – Allows hearing aid manufacturers to provide more pleasing, multi–frequency tones simulating musical notes or chords to indicate events such as program or volume changes.

**In-situ Tone Generator** – The narrow-band noise stimulus feature can be used for in-situ validation of the hearing aid fitting. The frequency, level and duration of the stimuli are individually adjustable.

Other Key Features – R3920 also supports the following features: FrontWave<sup>®</sup> directional processing, built–in feedback path measurement, cross fading between audio paths for click–free program changes, 16–band graphic equalizer, 8 generic biquad filters (configurable as parametric or other filter types), programming speed enhancements, optional peak clipping, flexible compression adjustments, direct interfaces to analog or digital volume control, rocker switch, direct audio input and telecoil. Rhythm R3920 also encompasses industry–leading security features to avoid cloning and software piracy.

#### **Support Tools**

- Hybrid Jig

- DSP3 Programming Box

- ARK Software Support

#### **Features**

- 16 Channel WDRC

- Advanced Research Algorithms:

- ◆ Impulse Noise Reduction (INR)

- iSceneDetect Environmental Classification

- Automatic Adaptive Directional Microphones (ADM)

- FrontWave Directionality

- 128-band Adaptive Noise Reduction

- Next-Generation Adaptive Feedback Cancellation (AFC)

- iLog 4.0 Datalogging

- Tinnitus Masking Noise Generator

- Evoke Acoustic Indicators

- Auto Telecoil with Programmable Delay

- Feedback Path Measurement Tool

- AGC-O with Variable Threshold, Time Constants, and Optional Adaptive Release

- 16-band Graphic Equalizer

- Narrow-Band Noise Stimulus

- SDA or I<sup>2</sup>C Programming

- 8 Biquadratic Filters

- 4 Analog Inputs

- 16 kHz or 8 kHz Bandwidth

- 6 Fully Configurable Memories with Audible Memory Change Indicator

- 96 dB Input Dynamic Range with HRX<sup>™</sup> Headroom Extension

- 128-bit Fingerprint Security System and Other Security Features to Protect Against Device Cloning and Software Piracy

- High Fidelity Audio CODEC

- Soft Acoustic Fade between Memory Changes

- Drives Zero-Bias 2-Terminal Receivers

- Internal or External Digital Volume Control with Programmable Range

- Digital Volume Control Level Retention After Power Cycle

- Rocker Switch Support

- Support for Active Hi or Active Lo Switching

- 20-bit Audio Processing

- thinSTAX® Packaging

- E1 RoHS Compliant Hybrid

- These Devices are Pb-Free and are RoHS Compliant

#### **Packaging Information**

• Hybrid Typical Dimensions: 0.220 x 0.125 x 0.060 in. (5.59 x 3.18 x 1.52 mm)

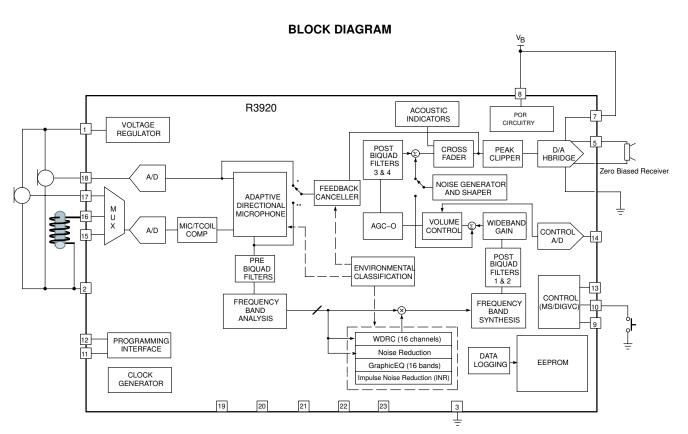

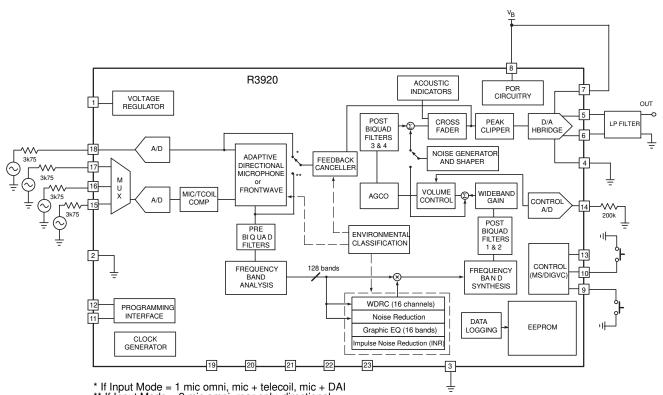

Figure 1. Hybrid Block Diagram

#### **SPECIFICATIONS**

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Value      | Units |

|------------------------------------|------------|-------|

| Operating Temperature Range        | 0 to +40   | °C    |

| Storage Temperature Range          | –20 to +70 | °C    |

| Absolute Maximum Power Dissipation | 50         | mW    |

| Maximum Operating Supply Voltage   | 1.65       | VDC   |

| Absolute Maximum Supply Voltage    | 1.8        | VDC   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

WARNING: Electrostatic Sensitive Device – Do not open packages or handle except at a static–free workstation.

WARNING: Moisture Sensitive Device – RoHS Compliant; Level 4 MSL. Do not open packages except under controlled conditions.

$\textbf{Table 2. ELECTRICAL CHARACTERISTICS} \ (Supply \ Voltage \ V_B = 1.25 \ V; \ Temperature = 25 ^{\circ}C)$

| Parameter                        | Symbol              | Conditions                                             | Min   | Тур   | Max   | Units  |  |

|----------------------------------|---------------------|--------------------------------------------------------|-------|-------|-------|--------|--|

| Minimum Operating Supply Voltage | $V_{BOFF}$          | Ramp down, audio path                                  | 0.93  | 0.95  | 0.97  | V      |  |

|                                  |                     | Ramp down, control logic                               | 0.77  | 0.80  | 0.83  |        |  |

| Supply Voltage Turn On Threshold | $V_{BON}$           | Ramp up, zinc-air                                      | 1.06  | 1.10  | 1.16  | V      |  |

|                                  |                     | Ramp up, NiMH                                          | 1.16  | 1.20  | 1.24  |        |  |

| Hybrid Current                   |                     | All functions, 32 kHz sampling rate                    | -     | 730   | -     | μΑ     |  |

|                                  |                     | All functions, 16 kHz sampling rate                    | -     | 620   | _     | -      |  |

| EEPROM Burn Cycles               | -                   | -                                                      | 100 k | -     | -     | cycles |  |

| Low Frequency System Limit       | -                   | -                                                      | -     | 125   | _     | Hz     |  |

| High Frequency System Limit      | -                   | -                                                      | -     | 16    | _     | kHz    |  |

| Total Harmonic Distortion        | THD                 | $V_{IN} = -40 \text{ dBV}$                             | -     | _     | 1     | %      |  |

| THD at Maximum Input             | THD <sub>M</sub>    | $V_{IN} = -15 \text{ dBV}, HRX - ON$                   | -     | _     | 3     | %      |  |

| Clock Frequency                  | <i>f</i> clk        | -                                                      | 3.973 | 4.096 | 4.218 | MHz    |  |

| REGULATOR                        |                     |                                                        |       |       |       |        |  |

| Regulator Voltage                | $V_{REG}$           | -                                                      | 0.87  | 0.90  | 0.93  | V      |  |

| System PSRR                      | PSRR <sub>SYS</sub> | 1 kHz, Input referred, HRX enabled                     | -     | 70    | _     | dB     |  |

| INPUT                            |                     |                                                        |       |       |       |        |  |

| Input Referred Noise             | IRN                 | Bandwidth 100 Hz – 8 kHz                               | -     | -108  | -106  | dBV    |  |

| Input Impedance                  | Z <sub>IN</sub>     | 1 kHz                                                  | -     | 3     | -     | МΩ     |  |

| Anti-aliasing Filter Rejection   | -                   | $f = [DC - 112 \text{ kHz}], V_{IN} = -40 \text{ dBV}$ | -     | 80    | -     | dB     |  |

| Crosstalk                        | -                   | Between both A/D and Mux                               | -     | 60    | -     | dB     |  |

| Maximum Input Level              | -                   | -                                                      | -     | -15   | -13   | dBV    |  |

| Analogue Input Voltage Range     | V <sub>AN_IN</sub>  | V <sub>IN1</sub> , V <sub>IN2</sub> , AI               | 0     | _     | 800   | mV     |  |

|                                  | V <sub>AN_TIN</sub> | T <sub>IN</sub>                                        | -100  | _     | 800   |        |  |

| Input Dynamic Range              | -                   | HRX – ON Bandwidth<br>100 Hz – 8 kHz                   | -     | 95    | 96    | dB     |  |

| Audio Sampling Rate              | -                   | -                                                      | 8     | -     | 48    | kHz    |  |

| OUTPUT                           | •                   |                                                        |       | •     | •     | •      |  |

| D/A Dynamic Range                | -                   | 100 Hz – 8 kHz                                         | -     | 88    | _     | dB     |  |

| Output Impedance                 | Z <sub>OUT</sub>    | -                                                      | -     | 10    | 13    | Ω      |  |

Table 2. ELECTRICAL CHARACTERISTICS (Supply Voltage  $V_B = 1.25 \text{ V}$ ; Temperature =  $25^{\circ}\text{C}$ )

| Parameter                     | Symbol            | Conditions                | Min   | Тур              | Max   | Units |

|-------------------------------|-------------------|---------------------------|-------|------------------|-------|-------|

| CONTROL A/D                   | ·                 |                           |       |                  | •     |       |

| Resolution (monotonic)        |                   | -                         | 7     | _                | _     | bits  |

| Zero Scale Level              | -                 | -                         | -     | 0                | -     | V     |

| Full Scale Level              | -                 | -                         | -     | V <sub>REG</sub> | -     | V     |

| VOLUME CONTROL                | <u> </u>          |                           | •     |                  |       |       |

| Volume Control Resistance     | R <sub>VC</sub>   | Three-terminal connection | 200   | -                | 1000  | kΩ    |

| Volume Control Range          | -                 | -                         | -     | -                | 42    | dB    |

| PC_SDA INPUT                  |                   |                           | •     | •                | •     |       |

| Logic 0 Voltage               |                   | -                         | 0     | _                | 0.3   | V     |

| Logic 1 Voltage               |                   | -                         | 1     | -                | 1.25  | V     |

| PC_SDA OUTPUT                 | -                 |                           | 1     |                  | •     |       |

| Stand-by Pull Up Current      | -                 | Creftrim = 6              | 3     | 5                | 6.5   | μΑ    |

| Sync Pull Up Current          | -                 | Creftrim = 6              | 748   | 880              | 1020  | μΑ    |

| Max Sync Pull Up Current      |                   | Creftrim = 15             | -     | 1380             | -     | μΑ    |

| Min Sync Pull Up Current      | -                 | Creftrim = 0              | -     | 550              | -     | μΑ    |

| Logic 0 Current (Pull Down)   |                   | Creftrim = 6              | 374   | 440              | 506   | μΑ    |

| Logic 1 Current (Pull Up)     | -                 | Creftrim = 6              | 374   | 440              | 506   | μΑ    |

| Synchronization Time          | T <sub>SYNC</sub> | Baud = 0                  | 237   | 250              | 263   | μs    |

| (Synchronization Pulse Width) |                   | Baud = 1                  | 118   | 125              | 132   | 1     |

|                               |                   | Baud = 2                  | 59    | 62.5             | 66    | 1     |

|                               |                   | Baud = 3                  | 29.76 | 31.25            | 32.81 | 1     |

|                               |                   | Baud = 4                  | 14.88 | 15.63            | 16.41 | 1     |

|                               |                   | Baud = 5                  | 7.44  | 7.81             | 8.20  | 1     |

|                               |                   | Baud = 6                  | 3.72  | 3.91             | 4.10  | 1     |

|                               |                   | Baud = 7                  | 1.86  | 1.95             | 2.05  | 1     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

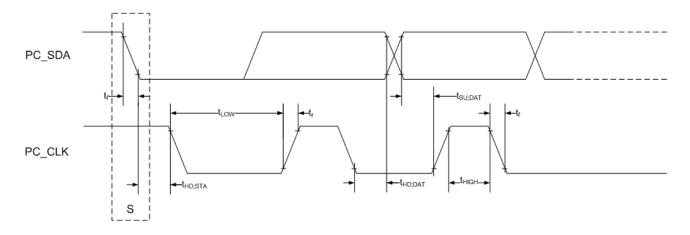

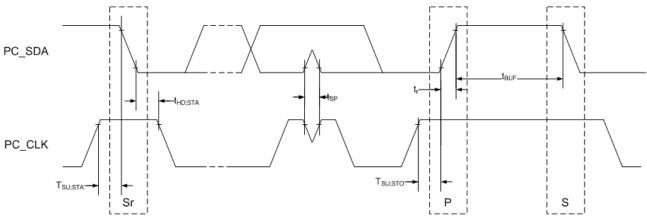

Table 3, I<sup>2</sup>C TIMING

|                                                                                                            | Standard Mode       |                   | ard Mode           | Fast Mode                           |              |       |

|------------------------------------------------------------------------------------------------------------|---------------------|-------------------|--------------------|-------------------------------------|--------------|-------|

| Parameter                                                                                                  | Symbol              | Min               | Max                | Min                                 | Max          | Units |

| Clock Frequency                                                                                            | f <sub>PC_CLK</sub> | 0                 | 100                | 0                                   | 400          | kHz   |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated.               | t <sub>HD;STA</sub> | 4.0               | -                  | 0.6                                 | -            | μsec  |

| LOW Period of the PC_CLK Clock                                                                             | t <sub>LOW</sub>    | 4.7               | -                  | -                                   | -            | μsec  |

| HIGH Period of the PC_CLK Clock                                                                            | t <sub>HIGH</sub>   | 4.0               | -                  | -                                   | -            | μsec  |

| Set-up time for a repeated START condition                                                                 | t <sub>SU;STA</sub> | 4.7               | -                  | -                                   | -            | μsec  |

| Data Hold Time:<br>for CBUS Compatible Masters<br>for I <sup>2</sup> C-bus Devices                         | t <sub>HD;DAT</sub> | 5.0<br>0 (Note 1) | -<br>3.45 (Note 2) | 0 (Note 1)                          | 0.9 (Note 2) | μsec  |

| Data set-up time                                                                                           | t <sub>SU;DAT</sub> | 250               | -                  | 100                                 | -            | nsec  |

| Rise time of both PC_SDA and PC_CLK signals                                                                | t <sub>r</sub>      | -                 | 1000               | 20 + 0.1 C <sub>b</sub><br>(Note 4) | 300          | nsec  |

| Fall time of both PC_SDA and PC_CLK signals                                                                | t <sub>f</sub>      | -                 | 300                | 20 + 0.1 C <sub>b</sub><br>(Note 4) | 300          | nsec  |

| Set-up time for STOP condition                                                                             | t <sub>SU;STO</sub> | 4.0               | -                  | 0.6                                 | -            | nsec  |

| Bus free time between a STOP and START condition                                                           | t <sub>BUF</sub>    | 4.7               | -                  | 1.3                                 | -            | μsec  |

| Output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub> with a bus capacitance from 10 pF to 400 pF | t <sub>of</sub>     | _                 | 250                | 20 + 0.1 C <sub>b</sub>             | 250          | nsec  |

| Pulse width of spikes which must be suppressed by the input filter                                         | t <sub>SP</sub>     | n/a               | n/a                | 0                                   | 50           | nsec  |

| Capacitive load for each bus line                                                                          | C <sub>b</sub>      | _                 | 400                | -                                   | 400          | pF    |

A device must internally provide a hold time of at least 300 ns for the PC\_SDA signal to bridge the undefined region of the falling edge of PC\_CLK.

The maximum t<sub>HD;DAT</sub> has only to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the PC\_CLK signal.

A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU;DAT</sub> P250ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the PC\_CLK signal. If such a device does stretch the LOW period of the PC\_CLK signal, it must output the next data bit to the PC\_SDA line t<sub>r</sub> max + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the PC\_CLK line is released.

C<sub>b</sub> = total capacitance of one bus line in pF.

Figure 2. I<sup>2</sup>C Mode Timing

#### TYPICAL APPLICATIONS

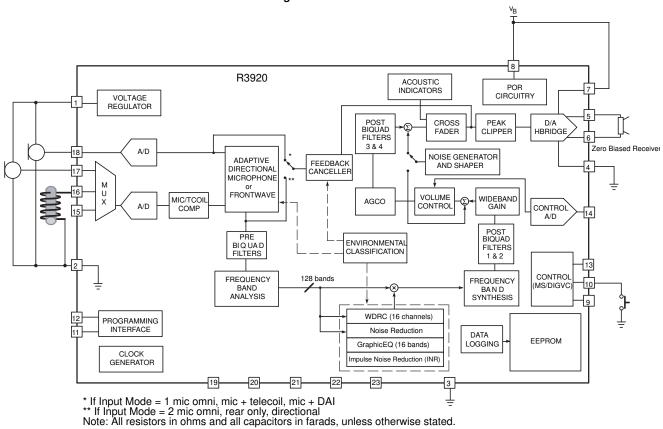

\* If Input Mode = 1 mic omni, mic + telecoil, mic + DAI

\*\* If Input Mode = 2 mic omni, rear only, directional

Note: All resistors in ohms and all capacitors in farads, unless otherwise stated.

Figure 3. Test Circuit

Figure 4. Typical Application Circuit

#### **ORDERING INFORMATION**

| Device         | Package                     | Shipping <sup>†</sup>   |

|----------------|-----------------------------|-------------------------|

| R3920-CFAB-E1T | 25 Pad Hybrid<br>Case 127DN | 250 Units / Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# **Tools Ordering Information**

To order a Hybrid Jig Evaluation Board for Rhythm R3920 contact your Sales Account Manager or FAE and use part number SA3400GEVB.

To order the DSP3 Programming box use part number SU6701-E1.

# **PAD LOCATIONS**

**Table 4. PAD POSITION AND DIMENSIONS**

| Pad No. | Pad Po | osition    | Pad Dim    | ensions    |

|---------|--------|------------|------------|------------|

|         | Х      | Υ          | Xdim (mil) | Ydim (mil) |

| 1       | 0      | 0          | 20         | 33         |

| 2       | -27    | 0          | 20         | 33         |

| 3       | -54    | <b>-</b> 5 | 20         | 23         |

| 4       | -81    | <b>-</b> 5 | 20         | 23         |

| 5       | -108   | <b>-</b> 5 | 20         | 23         |

| 6       | -135   | -5         | 20         | 23         |

| 7       | -162   | -5         | 20         | 23         |

| 8       | -189   | 0          | 20         | 33         |

| 9       | -189   | 42         | 20         | 23         |

| 10      | -189   | 85         | 20         | 23         |

| 11      | -162   | 85         | 20         | 23         |

| 12      | -135   | 85         | 20         | 23         |

| 13      | -108   | 85         | 20         | 23         |

| 14      | -81    | 85         | 20         | 23         |

| 15      | -54    | 85         | 20         | 23         |

| 16      | -27    | 85         | 20         | 23         |

| 17      | 0      | 85         | 20         | 23         |

| 18      | 0      | 42         | 20         | 23         |

| 19      | -27    | 42         | 20         | 23         |

| 20      | -54    | 42         | 20         | 23         |

| 21      | -81    | 42         | 20         | 23         |

| 22      | -108   | 42         | 20         | 23         |

| 23      | -135   | 42         | 20         | 23         |

| 24      | -162   | 26.5       | 18         | 12         |

| 25      | -162   | 53.5       | 18         | 12         |

**Table 4. PAD POSITION AND DIMENSIONS**

| Pad No. | X      | Υ      | Xdim (mm) | Ydim (mm) |

|---------|--------|--------|-----------|-----------|

| 1       | 0      | 0      | 0.508     | 0.838     |

| 2       | -0.686 | 0      | 0.508     | 0.838     |

| 3       | -1.372 | -0.127 | 0.508     | 0.584     |

| 4       | -2.057 | -0.127 | 0.508     | 0.584     |

| 5       | -2.743 | -0.127 | 0.508     | 0.584     |

| 6       | -3.429 | -0.127 | 0.508     | 0.584     |

| 7       | -4.115 | -0.127 | 0.508     | 0.584     |

| 8       | -4.801 | 0      | 0.508     | 0.838     |

| 9       | -4.801 | 1.067  | 0.508     | 0.584     |

| 10      | -4.801 | 2.159  | 0.508     | 0.584     |

| 11      | -4.115 | 2.159  | 0.508     | 0.584     |

| 12      | -3.429 | 2.159  | 0.508     | 0.584     |

| 13      | -2.743 | 2.159  | 0.508     | 0.584     |

| 14      | -2.057 | 2.159  | 0.508     | 0.584     |

| 15      | -1.372 | 2.159  | 0.508     | 0.584     |

| 16      | -0.686 | 2.159  | 0.508     | 0.584     |

| 17      | 0      | 2.159  | 0.508     | 0.584     |

| 18      | 0      | 1.067  | 0.508     | 0.584     |

| 19      | -0.686 | 1.067  | 0.508     | 0.584     |

| 20      | -1.372 | 1.067  | 0.508     | 0.584     |

| 21      | -2.057 | 1.067  | 0.508     | 0.584     |

| 22      | -2.743 | 1.067  | 0.508     | 0.584     |

| 23      | -3.429 | 1.067  | 0.508     | 0.584     |

| 24      | -4.115 | 0.673  | 0.457     | 0.305     |

| 25      | -4.115 | 1.359  | 0.457     | 0.305     |

#### **PACKAGE DIMENSIONS**

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

iSceneDetect, iLog, RHYTHM, HRX and EVOKE are trademarks of Semiconductor Components Industries, LLC. thinSTAX, FRONTWAVE, and ARKonline are registered trademarks of Semiconductor Components Industries, LLC.

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent\_Marking.pdf">www.onsemi.com/site/pdt/Patent\_Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor akes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative