Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

"Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **User's Manual**

# **V850ES/IE2**

32-bit Single-Chip Microcontrollers

**Hardware**

$\mu$ PD70F3713  $\mu$ PD70F3714

Document No. U17716EJ2V0UD00 (2nd edition)

Date Published February 2008 N

© NEC Electronics Corporation 2005

Printed in Japan

# [MEMO]

#### NOTES FOR CMOS DEVICES —

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

# (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

# **6** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

- The information in this document is current as of January, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

# (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

#### **PREFACE**

Readers

This manual is intended for users who wish to understand the functions of the V850ES/IE2 to design application systems using the V850ES/IE2.

**Purpose**

This manual is intended to give users an understanding of the hardware functions.

Organization

The V850ES/IE2 User's Manual is divided into two parts: Hardware (this manual) and Architecture (V850ES Architecture User's Manual). The organization of each manual is as follows:

# Hardware

- Pin functions

- CPU function

- On-chip peripheral functions

- Flash memory programming

- Electrical specifications

# Architecture

- Data type

- Register set

- Instruction format and instruction set

- Interrupts and exceptions

- Pipeline operation

#### **How to Read This Manual**

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

- To understand the overall functions of the V850ES/IE2

- →Read this manual according to the **CONTENTS**.

- To find the details of a register where the name is known

- →See APPENDIX B REGISTER INDEX.

- How to interpret the register format

- →For a bit whose bit number is enclosed in angle brackets < >, its bit name is defined as a reserved word in the device file.

- To understand the details of an instruction function

- →Refer to the V850ES Architecture User's Manual.

- To know the electrical specifications of the V850ES/IE2

- →See CHAPTER 19 ELECTRICAL SPECIFICATIONS.

The "yyy bit of the xxx register" is described as the "xxx.yyy bit" in this manual. Note with caution that if "xxx.yyy" is described as is in a program, however, the compiler/assembler cannot recognize it correctly.

The mark <R> shows major revised points. The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

Conventions

Data significance: Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on

the bottom

**Note**: Footnote for item marked with **Note** in the text

**Caution**: Information requiring particular attention

**Remark**: Supplementary information Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory

capacity):  $K \text{ (kilo): } 2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$

G (giga):  $2^{30} = 1,024^3$

Data type: Word ... 32 bits

Halfword ... 16 bits

Byte ... 8 bits

# **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# Documents related to V850ES/IE2

| Document Name                     | Document No. |

|-----------------------------------|--------------|

| V850ES Architecture User's Manual | U15943E      |

| V850ES/IE2 Hardware User's Manual | This manual  |

# Documents related to development tools (user's manuals)

| Docum                                                | ent Name          | Document No. |

|------------------------------------------------------|-------------------|--------------|

| QB-V850ESIX2 (in-circuit emulator)                   |                   | U17909E      |

| QB-MINI2 (On-Chip Debug Emulator with Program        | ming Function)    | U18371E      |

| CA850 (Ver. 3.00) (C compiler package)               | Operation         | U17293E      |

|                                                      | C Language        | U17291E      |

|                                                      | Assembly Language | U17292E      |

|                                                      | Link Directive    | U17294E      |

| PM+ (Ver. 6.30) (Project manager)                    |                   | U18416E      |

| ID850QB (Ver. 3.40) (Integrated debugger)            | Operation         | U18604E      |

| TW850 (Ver. 2.00) (Performance analysis tuning tool) |                   | U17241E      |

| RX850 (Ver. 3.20) (Real-time OS)                     | Basics            | U13430E      |

|                                                      | Installation      | U17419E      |

|                                                      | Technical         | U13431E      |

|                                                      | Task Debugger     | U17420E      |

| RX850 Pro (Ver. 3.21) (Real-time OS)                 | Basics            | U18165E      |

|                                                      | Installation      | U17421E      |

|                                                      | Technical         | U13772E      |

|                                                      | Task Debugger     | U17422E      |

| AZ850 (Ver. 3.30) (System performance analyzer)      |                   | U17423E      |

| PG-FP4 Flash Memory Programmer                       |                   | U15260E      |

| PG-FP5 Flash Memory Programmer                       |                   | U18865E      |

# **CONTENTS**

| CHAPTE | R 1 II | NTRODUCTION                                          | 14  |

|--------|--------|------------------------------------------------------|-----|

| 1.1    | Gene   | ral                                                  | 14  |

| 1.2    |        | ıres                                                 |     |

| 1.3    | Appli  | cations                                              | 16  |

| 1.4    | Orde   | ring Information                                     | 16  |

| 1.5    | Pin C  | onfiguration                                         | 17  |

| 1.6    |        | tion Blocks                                          |     |

| CHAPTE | R 2 P  | PIN FUNCTIONS                                        | 22  |

| 2.1    | List o | of Pin Functions                                     | 22  |

| 2.2    | Pin I/ | O Circuits and Recommended Connection of Unused Pins | 26  |

| 2.3    | Pin I/ | O Circuits                                           | 28  |

| CHAPTE | R 3 C  | PU FUNCTION                                          | 29  |

| 3.1    | Featu  | ıres                                                 | 29  |

| 3.2    | CPU    | Register Set                                         | 30  |

|        | 3.2.1  | Program register set                                 | 31  |

|        | 3.2.2  | System register set                                  | 32  |

| 3.3    | Opera  | ating Modes                                          | 38  |

| 3.4    | Addre  | ess Space                                            | 39  |

|        | 3.4.1  | CPU address space                                    | 39  |

|        | 3.4.2  | Wraparound of CPU address space                      | 40  |

|        | 3.4.3  | Memory map                                           | 41  |

|        | 3.4.4  | Areas                                                | 43  |

|        | 3.4.5  | Recommended use of address space                     | 47  |

|        | 3.4.6  | On-chip peripheral I/O registers                     | 50  |

|        | 3.4.7  | Special registers                                    |     |

|        | 3.4.8  | System wait control register (VSWC)                  | 61  |

| CHAPTE | R 4 P  | PORT FUNCTIONS                                       | 62  |

| 4.1    | Featu  | ires                                                 | 62  |

| 4.2    | Basic  | Port Configuration                                   | 62  |

| 4.3    | Port ( | Configuration                                        | 63  |

|        | 4.3.1  | Port 0                                               | 67  |

|        | 4.3.2  | Port 1                                               | 73  |

|        | 4.3.3  | Port 2                                               | 85  |

|        | 4.3.4  | Port 3                                               | 91  |

|        | 4.3.5  | Port 4                                               | 98  |

|        | 4.3.6  | Port DL                                              | 105 |

| 4.4    |        | ut Data and Read Value of Port for Each Setting      |     |

| 4.5    | Port I | Register Settings When Alternate Function Is Used    | 113 |

| 4.6    | Noise  | e Eliminator                                         | 117 |

| 4.7    | Cauti  | ons                                                  | 119 |

|        | 4.7.1  | Cautions on setting port pins                        | 119 |

|        | 4.7.2   | Cautions on bit manipulation instruction for port n register (Pn) | 120 |

|--------|---------|-------------------------------------------------------------------|-----|

| CHAPTE | ER 5 C  | LOCK GENERATOR                                                    | 121 |

| 5.1    | Overv   | iew                                                               | 121 |

| 5.2    |         | guration                                                          |     |

| 5.3    | -       | ol Registers                                                      |     |

| 5.4    |         | unction                                                           |     |

| 0      | 5.4.1   | Overview                                                          |     |

|        | 5.4.2   | PLL mode                                                          |     |

|        | 5.4.3   | Clock-through mode                                                |     |

| 5.5    |         | tion                                                              |     |

| 0.0    | 5.5.1   | Operation of each clock                                           |     |

|        | 5.5.2   | Operation timing                                                  |     |

| 5.6    |         | Monitor                                                           |     |

|        |         | 6-BIT TIMER/EVENT COUNTER P (TMP)                                 |     |

| 6.1    |         | iew                                                               |     |

| 6.2    |         | ions                                                              |     |

| 6.3    |         | guration                                                          |     |

| 6.4    | -       | ters                                                              |     |

| 6.5    | _       | Output Operations                                                 |     |

| 6.6    |         | ition                                                             |     |

|        | 6.6.1   | Interval timer mode (TPnMD2 to TPnMD0 bits = 000)                 |     |

|        | 6.6.2   | External event count mode (TPkMD2 to TPkMD0 bits = 001)           |     |

|        | 6.6.3   | External trigger pulse output mode (TPmMD2 to TPmMD0 bits = 010)  |     |

|        | 6.6.4   | One-shot pulse output mode (TPmMD2 to TPmMD0 bits = 011)          |     |

|        | 6.6.5   | PWM output mode (TPmMD2 to TPmMD0 bits = 100)                     |     |

|        | 6.6.6   | Free-running timer mode (TPnMD2 to TPnMD0 bits = 101)             |     |

|        | 6.6.7   | Pulse width measurement mode (TPkMD2 to TPkMD0 bits = 110)        |     |

| CHAPTE | ER 7 16 | 6-BIT TIMER/EVENT COUNTER Q (TMQ)                                 | 238 |

| 7.1    | Overv   | iew                                                               | 238 |

| 7.2    | Funct   | ions                                                              |     |

| 7.3    |         | guration                                                          |     |

| 7.4    | -       | ters                                                              |     |

| 7.5    | Timer   | Output Operations                                                 | 260 |

| 7.6    | Opera   | tion                                                              | 261 |

|        | 7.6.1   | Interval timer mode (TQnMD2 to TQnMD0 bits = 000)                 | 269 |

|        | 7.6.2   | External event count mode (TQ0MD2 to TQ0MD0 bits = 001)           | 281 |

|        | 7.6.3   | External trigger pulse output mode (TQ0MD2 to TQ0MD0 bits = 010)  | 291 |

|        | 7.6.4   | One-shot pulse output mode (TQ0MD2 to TQ0MD0 bits = 011)          | 305 |

|        | 7.6.5   | PWM output mode (TQ0MD2 to TQ0MD0 bits = 100)                     | 314 |

|        | 7.6.6   | Free-running timer mode (TQnMD2 to TQnMD0 bits = 101)             |     |

|        | 7.6.7   | Pulse width measurement mode (TQ0MD2 to TQ0MD0 bits = 110)        | 345 |

| CHAPTE | ER 8 16 | 6-BIT INTERVAL TIMER M (TMM)                                      | 351 |

| 8.1    |         | iew                                                               |     |

| 8.2    | Configuration                                                              | 352 |

|--------|----------------------------------------------------------------------------|-----|

| 8.3    | Control Register                                                           | 353 |

| 8.4    | Operation                                                                  | 354 |

|        | 8.4.1 Interval timer mode                                                  | 354 |

| 8.5    | Cautions                                                                   | 358 |

| CHAPTE | ER 9 MOTOR CONTROL FUNCTION                                                | 359 |

| 9.1    | Functional Overview                                                        | 359 |

| 9.2    | Configuration                                                              |     |

| 9.3    | Control Registers                                                          |     |

| 9.4    | Operation                                                                  |     |

|        | 9.4.1 System outline                                                       | 377 |

|        | 9.4.2 Dead-time control (generation of negative-phase wave signal)         | 382 |

|        | 9.4.3 Interrupt culling function                                           |     |

|        | 9.4.4 Operation to rewrite register with transfer function                 |     |

|        | 9.4.5 TMP1 tuning operation for A/D conversion start trigger signal output | 414 |

|        | 9.4.6 A/D conversion start trigger output function                         | 417 |

| CHAPTE | ER 10 WATCHDOG TIMER FUNCTIONS                                             | 422 |

| 10.1   | Functions                                                                  | 422 |

| 10.2   |                                                                            |     |

| 10.3   | •                                                                          |     |

| 10.4   | •                                                                          |     |

| 10.5   | •                                                                          |     |

|        |                                                                            |     |

| CHAPTE | ER 11 A/D CONVERTERS 0 AND 1                                               |     |

| 11.1   | Features                                                                   |     |

| 11.2   | •                                                                          |     |

| 11.3   | •                                                                          |     |

| 11.4   | •                                                                          |     |

|        | 11.4.1 Basic operation                                                     |     |

|        | 11.4.2 Operation mode and trigger mode                                     |     |

| 11.5   | Operation in Software Trigger Mode                                         |     |

|        | 11.5.1 Continuous select mode operations                                   |     |

|        | 11.5.2 Continuous scan mode operations                                     |     |

|        | 11.5.3 One-shot select mode operations                                     |     |

|        | 11.5.4 One-shot scan mode operations                                       |     |

| 11.6   |                                                                            |     |

|        | 11.6.1 Continuous select mode/one-shot select mode operations              |     |

|        | 11.6.2 Continuous scan mode/one-shot scan mode operations                  |     |

| 11.7   |                                                                            |     |

|        | 11.7.1 Continuous select mode/one-shot select mode operations              |     |

|        | 11.7.2 Continuous scan mode/one-shot scan mode operations                  |     |

| 11.8   | Internal Equivalent Circuit                                                |     |

| 11.9   | Notes on Operation                                                         |     |

|        | 11.9.1 Stopping conversion operation                                       |     |

|        | 11.9.2 Timer/external trigger interval                                     |     |

|        | 11.9.3 Operation in standby mode                                           | 467 |

|              | 11.9.4 Timer interrupt request signal in timer trigger mode                | 468 |

|--------------|----------------------------------------------------------------------------|-----|

|              | 11.9.5 Re-conversion start trigger input during stabilization time         | 468 |

|              | 11.9.6 Variation of A/D conversion results                                 | 468 |

|              | 11.9.7 A/D conversion result hysteresis characteristics                    | 468 |

|              | 11.9.8 Restrictions on setting one-shot mode and software trigger mode     | 469 |

| 11.10        | How to Read A/D Converter Characteristics Table                            | 470 |

| CHAPTE       | R 12 ASYNCHRONOUS SERIAL INTERFACE A (UARTA)                               | 474 |

| 12.1         | Features                                                                   |     |

| 12.2         | Configuration                                                              | 475 |

| 12.3         | Control Registers                                                          | 477 |

| 12.4         | Interrupt Request Signals                                                  | 482 |

| 12.5         | Operation                                                                  | 483 |

|              | 12.5.1 Data format                                                         | 483 |

|              | 12.5.2 UART transmission                                                   | 485 |

|              | 12.5.3 Continuous transmission procedure                                   | 486 |

|              | 12.5.4 UART reception                                                      | 488 |

|              | 12.5.5 Reception errors                                                    | 489 |

|              | 12.5.6 Parity types and operations                                         | 490 |

|              | 12.5.7 Receive data noise filter                                           | 491 |

| 12.6         | Dedicated Baud Rate Generator                                              | 492 |

| 12.7         | Cautions                                                                   | 499 |

| CHAPTE       | R 13 3-WIRE VARIABLE-LENGTH SERIAL I/O (CSIB)                              | 500 |

| 13.1         | Features                                                                   |     |

| 13.2         | Configuration                                                              | 501 |

| 13.3         | Control Registers                                                          | 503 |

| 13.4         | Operation                                                                  | 510 |

|              | 13.4.1 Single transfer mode (master mode, transmission mode)               | 510 |

|              | 13.4.2 Single transfer mode (master mode, reception mode)                  | 512 |

|              | 13.4.3 Single transfer mode (master mode, transmission/reception mode)     | 514 |

|              | 13.4.4 Single transfer mode (slave mode, transmission mode)                | 516 |

|              | 13.4.5 Single transfer mode (slave mode, reception mode)                   | 518 |

|              | 13.4.6 Single transfer mode (slave mode, transmission/reception mode)      | 520 |

|              | 13.4.7 Continuous transfer mode (master mode, transmission mode)           | 522 |

|              | 13.4.8 Continuous transfer mode (master mode, reception mode)              | 524 |

|              | 13.4.9 Continuous transfer mode (master mode, transmission/reception mode) | 527 |

|              | 13.4.10 Continuous transfer mode (slave mode, transmission mode)           | 531 |

|              | 13.4.11 Continuous transfer mode (slave mode, reception mode)              | 533 |

|              | 13.4.12 Continuous transfer mode (slave mode, transmission/reception mode) | 536 |

|              | 13.4.13 Reception error                                                    | 540 |

|              | 13.4.14 Clock timing                                                       |     |

| 13.5         | Output Pins                                                                | 543 |

| CHAPTE       | R 14 INTERRUPT/EXCEPTION PROCESSING FUNCTION                               | 544 |

| 14.1         | Features                                                                   |     |

| 14.2         | Non-Maskable Interrupts                                                    |     |

| <del>-</del> | 14.2.1 Operation                                                           |     |

|              | •                                                                          | _   |

|                | 14.2.2 Restore                                                                                                                                                                                                                                          | 550          |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                | 14.2.3 Non-maskable interrupt status flag (NP)                                                                                                                                                                                                          | 551          |

| 14.3           | Maskable Interrupts                                                                                                                                                                                                                                     | 552          |

|                | 14.3.1 Operation                                                                                                                                                                                                                                        | 552          |

|                | 14.3.2 Restore                                                                                                                                                                                                                                          | 554          |

|                | 14.3.3 Priorities of maskable interrupts                                                                                                                                                                                                                | 555          |

|                | 14.3.4 Interrupt control registers (xxICn)                                                                                                                                                                                                              | 559          |

|                | 14.3.5 Interrupt mask registers 0 to 3 (IMR0 to IMR3)                                                                                                                                                                                                   | 562          |

|                | 14.3.6 In-service priority register (ISPR)                                                                                                                                                                                                              | 564          |

|                | 14.3.7 Maskable interrupt status flag (ID)                                                                                                                                                                                                              |              |

| 14.4           | External Interrupt Request Input Pins (INTP0 to INTP6)                                                                                                                                                                                                  | 566          |

|                | 14.4.1 Noise elimination                                                                                                                                                                                                                                | 566          |

|                | 14.4.2 Edge detection                                                                                                                                                                                                                                   | 567          |

| 14.5           | Software Exception                                                                                                                                                                                                                                      | 568          |

|                | 14.5.1 Operation                                                                                                                                                                                                                                        | 568          |

|                | 14.5.2 Restore                                                                                                                                                                                                                                          | 569          |

|                | 14.5.3 Exception status flag (EP)                                                                                                                                                                                                                       | 570          |

| 14.6           | Exception Trap                                                                                                                                                                                                                                          | 571          |

|                | 14.6.1 Illegal opcode definition                                                                                                                                                                                                                        | 571          |

|                | 14.6.2 Debug trap                                                                                                                                                                                                                                       |              |

| 14.7           | Multiple Interrupt Servicing Control                                                                                                                                                                                                                    | 575          |

| 14.8           | Interrupt Response Time of CPU                                                                                                                                                                                                                          |              |

| 14.9           | Periods in Which CPU Does Not Acknowledge Interrupts                                                                                                                                                                                                    | 578          |

| 14.10          | Caution                                                                                                                                                                                                                                                 | 578          |

|                |                                                                                                                                                                                                                                                         |              |

| CHAPTE         | R 15 STANDBY FUNCTION                                                                                                                                                                                                                                   | 579          |

| 15.1           | Overview                                                                                                                                                                                                                                                |              |

| 15.2           | Control Registers                                                                                                                                                                                                                                       |              |

| 15.3           | HALT Mode                                                                                                                                                                                                                                               |              |

|                | 15.3.1 Setting and operation status                                                                                                                                                                                                                     |              |

|                | 15.3.2 Releasing HALT mode                                                                                                                                                                                                                              |              |

| 15.4           | IDLE Mode                                                                                                                                                                                                                                               | 585          |

|                | 15.4.1 Setting and operation status                                                                                                                                                                                                                     | 585          |

|                | 15.4.2 Releasing IDLE mode                                                                                                                                                                                                                              | 585          |

| 15.5           | STOP Mode                                                                                                                                                                                                                                               | 587          |

|                |                                                                                                                                                                                                                                                         |              |

|                | 15.5.1 Setting and operation status                                                                                                                                                                                                                     | 587          |

| 15.6           | 15.5.2 Releasing STOP mode                                                                                                                                                                                                                              | 587          |

|                |                                                                                                                                                                                                                                                         | 587          |

|                | 15.5.2 Releasing STOP mode                                                                                                                                                                                                                              | 587          |

| СНАРТЕ         | 15.5.2 Releasing STOP mode                                                                                                                                                                                                                              | 587          |

| CHAPTE<br>16.1 | 15.5.2 Releasing STOP mode                                                                                                                                                                                                                              | 587<br>589   |

|                | 15.5.2 Releasing STOP mode  Securing Oscillation Stabilization Time  R 16 RESET FUNCTIONS                                                                                                                                                               | 587589590    |

| 16.1           | 15.5.2 Releasing STOP mode  Securing Oscillation Stabilization Time  R 16 RESET FUNCTIONS  Overview                                                                                                                                                     | 587589590590 |

| 16.1<br>16.2   | 15.5.2 Releasing STOP mode  Securing Oscillation Stabilization Time  R 16 RESET FUNCTIONS  Overview  Registers to Check Reset Source                                                                                                                    |              |

| 16.1<br>16.2   | 15.5.2 Releasing STOP mode  Securing Oscillation Stabilization Time  R 16 RESET FUNCTIONS  Overview  Registers to Check Reset Source  Operation                                                                                                         |              |

| 16.1<br>16.2   | 15.5.2 Releasing STOP mode  Securing Oscillation Stabilization Time  R 16 RESET FUNCTIONS  Overview  Registers to Check Reset Source  Operation  16.3.1 Reset operation via RESET pin                                                                   |              |

| 16.1<br>16.2   | 15.5.2 Releasing STOP mode  Securing Oscillation Stabilization Time  R 16 RESET FUNCTIONS  Overview  Registers to Check Reset Source  Operation  16.3.1 Reset operation via RESET pin  16.3.2 Reset operation by watchdog timer (WDT) overflow (WDTRES) |              |

| CHAP  | TER 17 REGULATOR                                                        | 605 |

|-------|-------------------------------------------------------------------------|-----|

| 17    | .1 Overview                                                             | 605 |

| 17    | .2 Operation                                                            | 606 |

| CHAP  | TER 18 FLASH MEMORY                                                     | 607 |

| 18    | .1 Features                                                             | 607 |

| 18    | .2 Memory Configuration                                                 | 608 |

| 18    | .3 Functional Overview                                                  | 609 |

| 18    | .4 Rewriting by Dedicated Flash Memory Programmer                       | 613 |

|       | 18.4.1 Programming environment                                          | 613 |

|       | 18.4.2 Communication mode                                               | 614 |

|       | 18.4.3 Flash memory control                                             | 619 |

|       | 18.4.4 Selection of communication mode                                  |     |

|       | 18.4.5 Communication commands                                           | 621 |

|       | 18.4.6 Pin connection                                                   | 622 |

| 18    | .5 Rewriting by Self Programming (μPD70F3714 only)                      | 627 |

|       | 18.5.1 Overview                                                         | 627 |

|       | 18.5.2 Features                                                         | 628 |

|       | 18.5.3 Standard self programming flow                                   | 629 |

|       | 18.5.4 Flash functions                                                  | 630 |

|       | 18.5.5 Pin processing                                                   | 630 |

|       | 18.5.6 Internal resources used                                          | 631 |

|       | TER 19 ELECTRICAL SPECIFICATIONS                                        |     |

| СНАР  | TER 21 RECOMMENDED SOLDERING CONDITIONS                                 | 652 |

| APPEI | NDIX A CAUTIONS                                                         | 653 |

| Α.    | 1 Restriction on Conflict Between sld Instruction and Interrupt Request | 653 |

|       | A.1.1 Description                                                       | 653 |

|       | A.1.2 Countermeasure                                                    | 653 |

| APPEI | NDIX B REGISTER INDEX                                                   | 654 |

| APPEI | NDIX C INSTRUCTION SET LIST                                             | 659 |

| C.    | 1 Conventions                                                           | 659 |

| C.:   |                                                                         |     |

| APPEI | NDIX D REVISION HISTORY                                                 | 669 |

| D.    | 1 Major Revisions in This Edition                                       | 669 |

# **CHAPTER 1 INTRODUCTION**

The V850ES/IE2 is one of the low-power operation products in the NEC Electronics V850 Series of single-chip microcontrollers designed for real-time control applications.

# 1.1 General

The V850ES/IE2 is a 32-bit single-chip microcontroller that includes the V850ES CPU core and peripheral functions such as ROM/RAM, a timer/counter, serial interfaces, a watchdog timer, and an A/D converter.

In addition to high real-time response characteristics and 1-clock-pitch basic instructions, the V850ES/IE2 features instructions such as multiply instructions, saturated operation instructions, and bit manipulation instructions realized by a hardware multiplier, as optimum instructions for digital servo control applications. Moreover, as a real-time control system, the V850ES/IE2 enables an extremely high cost-performance for applications such as motor inverter control.

#### 1.2 Features

O Minimum instruction execution time:

50 ns (at internal 20 MHz operation)

O General-purpose registers: 32 bits × 32

O CPU features: Signed multiplication ( $16 \times 16 \rightarrow 32$ ): 1 to 2 clocks

Signed multiplication (32  $\times$  32  $\rightarrow$  64): 1 to 5 clocks

Saturated operation instructions (with overflow/underflow detection function)

32-bit shift instructions: 1 clock Bit manipulation instructions

Load/store instructions with long/short format

Signed load instructions

O Internal memory:

| Part Number | Internal ROM          | Internal RAM |

|-------------|-----------------------|--------------|

| μPD70F3713  | 64 KB (flash memory)  | 6 KB         |

| μPD70F3714  | 128 KB (flash memory) | 6 KB         |

O Interrupts/exceptions: Non-maskable interrupts: 1 source (external: none, internal: 1)

Maskable interrupts: 42 sources (external: 7, internal: 35)

Software exceptions: 32 sources Exception traps: 2 sources

O I/O lines: I/O ports: 39

O Timer/counter function: 16-bit interval timer M (TMM): 1 channel

16-bit timer/event counter Q (TMQ): 2 channels 16-bit timer/event counter P (TMP): 4 channels

Motor control function (uses timer TMQ: 1 channel (TMQ1), TMP: 1 channel (TMP1))

16-bit accuracy 6-phase PWM function with dead time: 1 channel

High-impedance output control function

Timer tuning operation function

Arbitrary cycle setting function

Arbitrary dead-time setting function

Watchdog timer: 1 channel

O Serial interfaces: Asynchronous serial interface A (UARTA)

3-wire variable length serial I/O (CSIB)

CSIB: 1 channel UARTA: 2 channels

O A/D converter: 10-bit resolution A/D converters (A/D converters 0 and 1): 4 channels × 2 units

#### **CHAPTER 1 INTRODUCTION**

O Clock generator: 2.5 MHz resonator connectable (external clock input prohibited)

Multiplication function by PLL clock synthesizer (fixed to multiplication by eight, fxx =

20 MHz)

CPU clock division function (fxx, fxx/2, fxx/4, fxx/8)

O Power-save function: HALT/IDLE/ STOP mode

O Power-on-clear function

O Low-voltage detection function

O Self programming Supported only in the  $\mu$ PD70F3714 (not supported in the  $\mu$ PD70F3713)

O Package: 64-pin plastic LQFP (14 × 14)

O Operation supply voltage: VDD = EVDD = 3.5 to 5.5 V

$AV_{DD0}$ ,  $AV_{DD1} = 4.5$  to 5.5 V

O Operation ambient temperature:

$T_A = -40 \text{ to } +85^{\circ}\text{C}$

# 1.3 Applications

• Consumer appliances (such as inverter air conditioners, refrigerators, washing machines, etc.)

• Industrial equipment (such as motor control and general-purpose inverters, etc.)

# 1.4 Ordering Information

| Part Number        | Package                              | Internal ROM          |

|--------------------|--------------------------------------|-----------------------|

| μPD70F3713GC-8BS-A | 64-pin plastic LQFP (14 × 14)        | Flash memory (64 KB)  |

| μPD70F3714GC-8BS-A | 64-pin plastic LQFP (14 $\times$ 14) | Flash memory (128 KB) |

**Remark** Products with -A at the end of the part number are lead-free products.

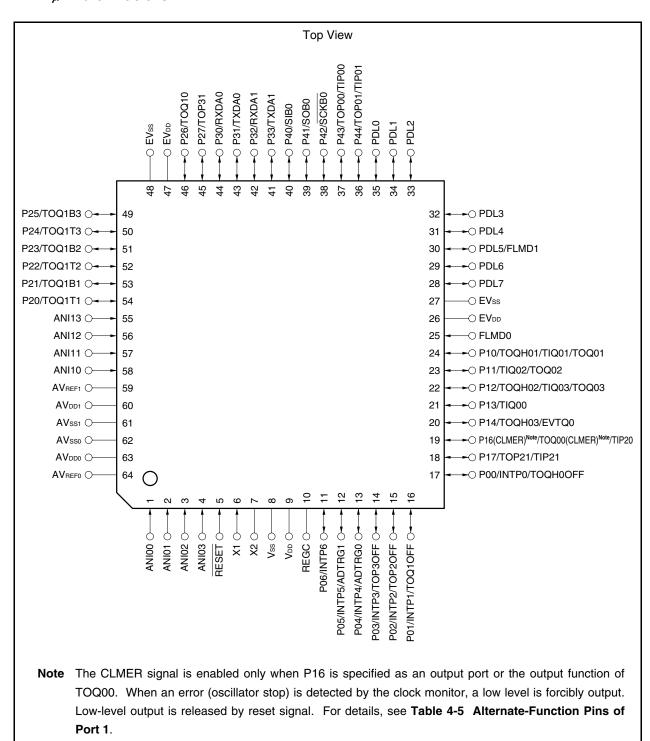

# 1.5 Pin Configuration

64-pin plastic LQFP (14 × 14)

μPD70F3713GC-8BS-A

μPD70F3714GC-8BS-A

# Pin Identification

ADTRG0, ADTRG1: A/D trigger input SCKB0: Serial clock ANI00 to ANI03, SIB0: Serial input

ANI10 to ANI13: Analog input SOB0: Serial output

AVDD0, AVDD1: Analog power supply TIP00, TIP01, AVREF0, AVREF1: Analog reference voltage TIP20, TIP21,

AVsso, AVss1: Analog ground TIQ00 to TIQ03: Timer trigger input

EVDD: Power supply for port TOP00, TOP01,

EVss: Ground for port TOP21, TOP31,

EVTQ0: Timer event count input TOQ1B1 to TOQ1B3,

FLMD0, FLMD1: Flash programming mode TOQ1T1 to TOQ1T3,

INTP0 to INTP6: External interrupt input TOQ00 to TOQ03,

P00 to P06: Port 0 TOQ10,

P10 to P14, P16, P17: Port 1 TOQH01 to TOQH03: Timer output

P20 to P27: Port 2 TOP2OFF, TOP3OFF,

P30 to P33: Port 3 TOQ1OFF, TOQH0OFF: Timer output off P40 to P44: Port 4 TXDA0, TXDA1: Transmit data PDL0 to PDL7: Port DL VDD: Power supply

REGC: Regulator control Vss: Ground

RESET: Reset X1, X2: Clock oscillator pin

RXDA0, RXDA1: Receive data

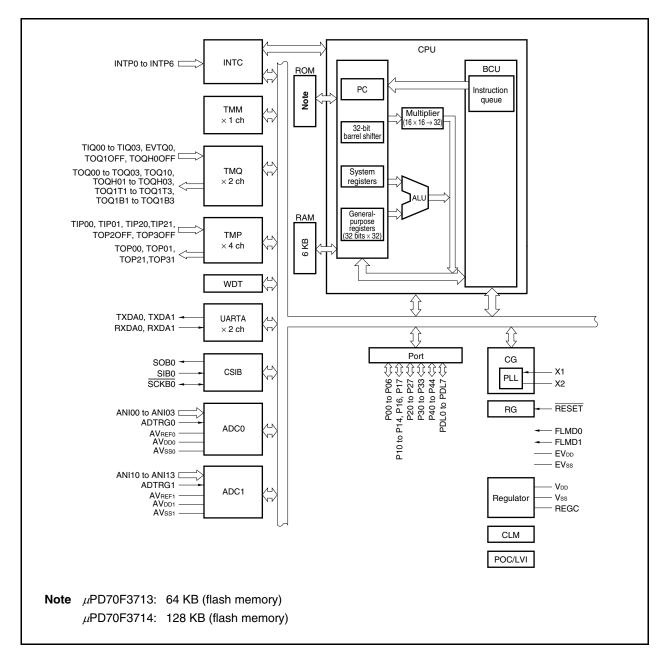

# 1.6 Function Blocks

# (1) Internal block diagram

#### (2) Internal units

# (a) CPU

The CPU uses five-stage pipeline control to enable single-clock execution of address calculations, arithmetic logic operations, data transfers, and almost all other instruction processing.

Other dedicated on-chip hardware, such as a multiplier (16 bits  $\times$  16 bits  $\rightarrow$  32 bits) and a barrel shifter (32 bits), help accelerate complex processing.

#### (b) Bus control unit (BCU)

The BCU controls the internal bus.

# (c) ROM

This is flash memory that is mapped from address 00000000H.

During instruction fetch, ROM/flash memory can be accessed from the CPU in 1-clock cycles. The internal ROM capacity and area differ as follows depending on the product.

| Part Number | Internal ROM Capacity | Internal ROM Area      |

|-------------|-----------------------|------------------------|

| μPD70F3713  | 64 KB (flash memory)  | xn000000H to xn00FFFFH |

| μPD70F3714  | 128 KB (flash memory) | xn000000H to xn01FFFFH |

**Remark** n = xx11B

#### (d) RAM

This is a 6 KB internal RAM that is mapped to the addresses xnFFD800H to xnFFEFFFH.

During instruction fetch or data access, data can be accessed from the CPU in 1-clock cycles.

**Remark** n = xx11B

#### (e) Interrupt controller (INTC)

This controller handles hardware interrupt requests (INTP0 to INTP6) from on-chip peripheral hardware and external hardware. Eight levels of interrupt priorities can be specified for these interrupt requests, and multiple-interrupt servicing control can be performed.

# (f) Clock generator (CG)

The clock generator includes two basic operation modes: PLL mode (fixed to multiplication by eight) and clock-through mode. It generates four types of clocks (fxx, fxx/2, fxx/4, fxx/8), and supplies one of them as the operating clock for the CPU (fcpu).

#### (q) Timer/counter

This unit incorporates one 16-bit interval timer M (TMM) channel, two 16-bit timer/event counter Q (TMQ) channels, and four 16-bit timer/event counter P (TMP) channels, and can measure pulse interval widths or frequency, enable an inverter function for motor control, and output a programmable pulse.

# (h) Watchdog timer (WDT)

A watchdog timer is equipped to detect program loops, system abnormalities, etc.

It generates a non-maskable interrupt request signal (INTWDT) or internal reset signal (WDTRES) after an overflow occurs.

# (i) Serial interface

The V850ES/IE2 includes two asynchronous serial interface A (UARTA) channels and one 3-wire variable length serial I/O (CSIB) channel as the serial interface.

For UARTA, data is transferred via the TXDAn and RXDAn pins (n = 0, 1).

For CSIB, data is transferred via the SOB0, SIB0, and SCKB0 pins.

# (j) A/D converter (ADC)

The V850ES/IE2 includes two-channel 10-bit A/D converters (ADC0 and ADC1) with four analog input pins.

# (k) Ports

As shown below, the following ports have general-purpose port functions and control pin functions.

| Port    | I/O       | Alternate Function                                                                     |

|---------|-----------|----------------------------------------------------------------------------------------|

| Port 0  | 7-bit I/O | Timer/counter input, external interrupt input, external trigger input of A/D converter |

| Port 1  | 7-bit I/O | Timer/counter I/O                                                                      |

| Port 2  | 8-bit I/O | Timer/counter output                                                                   |

| Port 3  | 4-bit I/O | Serial interface I/O                                                                   |

| Port 4  | 5-bit I/O | Serial interface I/O, timer/counter I/O                                                |

| Port DL | 8-bit I/O | -                                                                                      |

# **CHAPTER 2 PIN FUNCTIONS**

# 2.1 List of Pin Functions

The names and functions of the pins in the V850ES/IE2 are listed below. These pins can be divided into port pins and non-port pins according to their function.

There are two power supplies for the I/O buffer of a pin: power supply for A/D converter (AVDD0 and AVDD1) and power supply for external pin (EVDD). The relationship between each power supply and the pins is shown below.

Table 2-1. I/O Buffer Power Supplies for Each Pin

| Power Supply     | Corresponding Pins             |  |

|------------------|--------------------------------|--|

| AVDD0, AVDD1     | ANI00 to ANI03, ANI10 to ANI13 |  |

| EV <sub>DD</sub> | Ports 0 to 4, port DL, RESET   |  |

# (1) Port pins

(1/2)

| Pin Name                       | Pin No. | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate Function      |

|--------------------------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| P00                            | 17      | I/O | Port 0 7-bit I/O port Input data read/output data write is enabled in 1-bit units. Use of an on-chip pull-up resistor can be specified in 1-bit units (the on-chip pull-up resistor can be connected only in the input mode of the port mode and when the alternate function of the pin is used).                                                                                                                                                           | INTP0/TOQH0OFF          |

| P01                            | 16      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INTP1/TOQ1OFF           |

| P02                            | 15      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INTP2/TOP2OFF           |

| P03                            | 14      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INTP3/TOP3OFF           |

| P04                            | 13      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INTP4/ADTRG0            |

| P05                            | 12      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INTP5/ADTRG1            |

| P06                            | 11      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | INTP6                   |

| P10                            | 24      | I/O | Port 1 7-bit I/O port Input data read/output data write is enabled in 1-bit units. Use of an on-chip pull-up resistor can be specified in 1-bit units (the on-chip pull-up resistor can be connected only in the input mode of the port mode, when the input mode of alternate function of the pin is used, and when TOP21 and TOQH01 to TOQH03 pins, which function as output pins when their alternate function is used, go into a high-impedance state). | TOQH01/TIQ01/TOQ01      |

| P11                            | 23      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TIQ02/TOQ02             |

| P12                            | 22      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TOQH02/TIQ03/TOQ03      |

| P13                            | 21      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TIQ00                   |

| P14                            | 20      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TOQH03/EVTQ0            |

| P16<br>(CLMER) <sup>Note</sup> | 19      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TOQ00 (CLMER)Note/TIP20 |

| P17                            | 18      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TOP21/TIP21             |

Note The CLMER signal is enabled only when P16 is specified as an output port or the output function of TOQ00. When an error (oscillator stop) is detected by the clock monitor, a low level is forcibly output. Low-level output is released by reset signal. For details, see Table 4-5 Alternate-Function Pins of Port 1.

(2/2)

| Pin Name | Pin No. | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                          | Alternate Function |

|----------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| P20      | 54      | I/O | Port 2 8-bit I/O port Input data read/output data write is enabled in 1-bit units. Use of an on-chip pull-up resistor can be specified in 1-bit units (the on-chip pull-up resistor can be connected only in the input mode of the port mode, or when TOQ1T1 to TOQ1T3 and TOQ1B1 to TOQ1B3 and TOP31 pins, which function as output pins when their alternate function is used, go into a high-impedance state). | TOQ1T1             |

| P21      | 53      |     |                                                                                                                                                                                                                                                                                                                                                                                                                   | TOQ1B1             |

| P22      | 52      |     |                                                                                                                                                                                                                                                                                                                                                                                                                   | TOQ1T2             |

| P23      | 51      |     |                                                                                                                                                                                                                                                                                                                                                                                                                   | TOQ1B2             |