# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## RENESAS

## RAA23021x

R18DS0013EJ0102 Rev.1.02 Jul 23, 2014

Datasheet

## Description

The RAA23021x is a high efficiency monolithic step-down DC/DC synchronous converter plus a LDO (low dropout) regulator which has an ultra-low power mode.

## Features

- DC/DC converter (ch1)

- Synchronous rectification type step-down circuit

- Integrated power MOSFETs

- Preset output voltage (There are also products that have adjustable output voltage using external resistors.)

- Internal phase compensator

- Switching frequency: 1 MHz (fixed)

- Internal timer-latch-type short-circuit protector (fixed delay time)

- 100% duty cycle operation

- LDO (ch2)

- 500mA

- Internal over current protector (foldback-current limiting)

- Ultra low-power save mode (25uA typical)

- Common Features

- Internal rise up sequencer

- Internal digital soft-start function (2 ms fixed soft-start time)

- Internal discharge circuit

- Power good function

- Internal timer-latch-type thermal shutdown circuit (shutdown temperature: 150°C or higher)

- Internal recovery-type under voltage lockout circuit

## Application

- Communication

- Industrial

- Building

- Smart meter

And, usable around MCU, ASIC, FPGA, etc.

#### **Ordering Information**

| Ordering Part No. | Package       | Tape and Reel                  |

|-------------------|---------------|--------------------------------|

| RAA230214GSB#HA0  | 20-pin HTSSOP | Embossed taping. 2,500pcs/reel |

| RAA230215GSB#HA0  |               |                                |

Note: A quality grade of these ICs is "Standard". Recommended applications are indicated below.

Computers, office equipment, communications equipment, test and measurement equipment,

audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment, and industrial robots, etc.

## Part No Summary

|              |                                         | Input       | Output V                                                   | /oltage            | Maximum        | Switching |         |

|--------------|-----------------------------------------|-------------|------------------------------------------------------------|--------------------|----------------|-----------|---------|

| Part No.     | Output                                  | Voltage     | ch1                                                        | ch2                | Output Current | Frequency | Package |

| RAA230214GSB | ch1:DC/DC                               | 3.0 V       | 3.3                                                        | 3.3                | ch1:3 A        | 1 MHz     | 20-pin  |

| RAA230215GSB | (step-down,<br>current mode)<br>ch2:LDO | to<br>5.5 V | 0.9 V to VII<br>(Adjustable<br>output indiv<br>by external | e each<br>/idually | ch2:0.5 A      | (fixed)   | HTSSOP  |

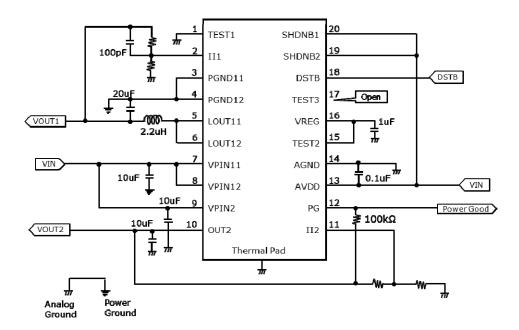

## Circuit example (RAA230215GSB)

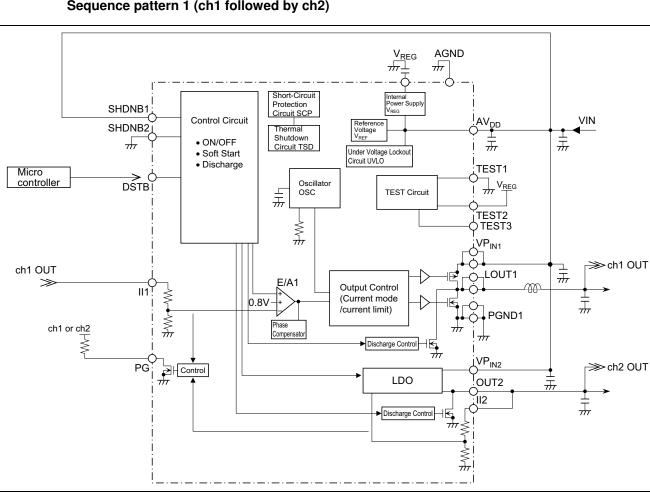

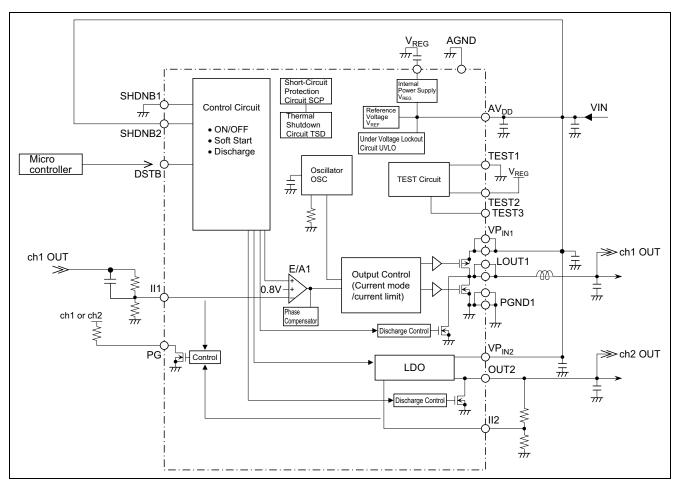

### **Block Diagram**

ch1/ch2: Preset output voltage by internal resistor. Sequence pattern 1 (ch1 followed by ch2)

ch1/ch2: Adjustable output voltage by external resistor. Sequence pattern 2 (ch2 followed by ch1)

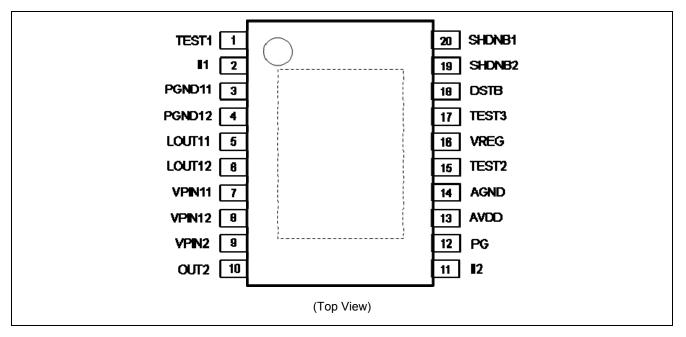

## **Pin Configuration**

#### **Pin Function**

| Pin No. | Symbol             | I/O          | Function                                   |

|---------|--------------------|--------------|--------------------------------------------|

| 1       | TEST1              | —            | Test pin 1 (connect to AGND)               |

| 2       | ll1                | Input        | Inverted input for error amplifier of ch1  |

| 3       | PGND11             | Ground       | Power ground                               |

| 4       | PGND12             | Ground       | Power ground                               |

| 5       | LOUT11             | Output       | Inductor connection 1 for ch1              |

| 6       | LOUT12             | Output       | Inductor connection 2 for ch1              |

| 7       | VP <sub>IN11</sub> | Power supply | Output stage power input 1 of ch1          |

| 8       | VP <sub>IN12</sub> | Power supply | Output stage power input 2 of ch1          |

| 9       | VP <sub>IN2</sub>  | Power supply | Output stage power input of ch2            |

| 10      | OUT2               | Output       | Output of ch2                              |

| 11      | 112                | Input        | Inverted input for error amplifier of ch2  |

| 12      | PG                 | Output       | Power-good output (open-drain)             |

| 13      | AV <sub>DD</sub>   | Power supply | Analog block power supply                  |

| 14      | AGND               | Ground       | Analog ground                              |

| 15      | TEST2              | —            | Test pin 2 (connect to V <sub>REG</sub> )  |

| 16      | V <sub>REG</sub>   | Output       | Internal power supply output (connect 1uF) |

| 17      | TEST3              | —            | Test pin 3 (open)                          |

| 18      | DSTB               | Input        | Light-load operation mode setting pin      |

| 19      | SHDNB2             | Input        | Output ON/OFF of ch2                       |

| 20      | SHDNB1             | Input        | Output ON/OFF of ch1                       |

## **Absolute Maximum Ratings**

|                                                                |                          |                    | (Unless | otherwise specified, $T_A = 25^{\circ}C$                    |

|----------------------------------------------------------------|--------------------------|--------------------|---------|-------------------------------------------------------------|

| Parameter                                                      | Symbol                   | Ratings            | Unit    | Condition                                                   |

| Analog power supply (AV <sub>DD</sub> pin)                     | AV <sub>DD</sub>         | -0.5 to +6.5       | V       | AV <sub>DD</sub>                                            |

| VP <sub>IN</sub> pin applied voltage                           | VPIN                     | -0.5 to +6.5       | V       | VP <sub>IN11</sub> , VP <sub>IN12</sub> , VP <sub>IN2</sub> |

| SHDNB pin applied voltage                                      | V <sub>SHDNB</sub>       | -0.5 to +6.5       | V       | SHDNB1, SHDNB2                                              |

| DSTB pin applied voltage                                       | V <sub>DSTB</sub>        | -0.5 to +6.5       | V       | DSTB                                                        |

| PG pin applied voltage                                         | V <sub>PG</sub>          | -0.5 to +6.5       | V       | PG                                                          |

| II pin applied voltage                                         | VII                      | -0.5 to +6.5       | V       | 1,   2                                                      |

| VP <sub>IN11</sub> +VP <sub>IN12</sub> pin sink current (peak) | IP <sub>IN1(peak)-</sub> | 3500               | mA      | VPIN11+VPIN12                                               |

| LOUT11+LOUT12 pin output source                                | I <sub>LO1(peak)+</sub>  | 3500               | mA      | LOUT11, LOUT12                                              |

| current (peak)                                                 |                          |                    |         |                                                             |

| VP <sub>IN2</sub> pin sink current (DC)                        | IP <sub>IN2(DC)</sub> -  | 500                | mA      | VP <sub>IN2</sub>                                           |

| OUT2 pin output source current (DC)                            | I <sub>O2(DC)+</sub>     | 500                | mA      | OUT2                                                        |

| LOUT11+LOUT12, OUT2 pin output                                 | ILO1,O2(DC)-             | 100                | mA      | when discharge circuit is                                   |

| source current (DC)                                            |                          |                    |         | operation.                                                  |

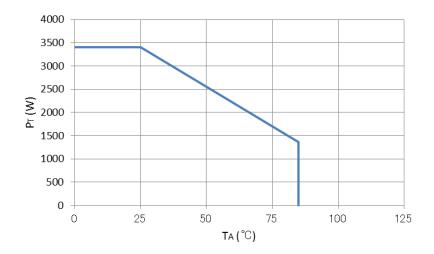

| Total power dissipation                                        | PT                       | 3400 <sup>*1</sup> | mW      | $T_A \le +25^{\circ}C$                                      |

| Operating ambient temperature                                  | T <sub>A</sub>           | -40 to +85         | °C      |                                                             |

| Junction temperature                                           | TJ                       | -40 to +150        | °C      |                                                             |

| Storage temperature                                            | T <sub>stg</sub>         | -55 to +150        | °C      |                                                             |

Note:

\*1 This is the value at  $T_A \le +25^{\circ}$ C. At  $T_A > +25^{\circ}$ C, the total power dissipation is derated by 34mW/°C.

Board specification : 4-layers glass epoxy board, 76.2mm x 114.3mm x 1.664mm.

Copper coverage area: 50%, 0.070mm thickness (top and bottom layers)

95%, 0.035mm thickness (layers 2 and 3).

Connecting exposed pad

Caution: Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

## **Recommended Operating Condition**

(Unless otherwise specified,  $T_A = 25^{\circ}C$ )

|                                      |                    |     |                  | ( -       |      |                                                             |

|--------------------------------------|--------------------|-----|------------------|-----------|------|-------------------------------------------------------------|

| Parameter                            | Symbol             | Min | Тур              | Max       | Unit | Condition                                                   |

| Analog power supply voltage          | AV <sub>DD</sub>   | 3.0 | 5.0              | 5.5       | V    | AV <sub>DD</sub>                                            |

| (AV <sub>DD</sub> pin)               |                    |     |                  |           |      |                                                             |

| VP <sub>IN</sub> pin applied voltage | VPIN               | —   | AV <sub>DD</sub> | —         | V    | VP <sub>IN11</sub> , VP <sub>IN12</sub> , VP <sub>IN2</sub> |

| SHDNB pin applied voltage            | V <sub>SHDNB</sub> | 0   | —                | $AV_{DD}$ | V    | SHDNB1, SHDNB2                                              |

| DSTB pin applied voltage             | V <sub>DSTB</sub>  | 0   | —                | $AV_{DD}$ | V    | DSTB                                                        |

| PG pin applied voltage               | V <sub>PG</sub>    | 0   | —                | $AV_{DD}$ | V    | PG                                                          |

| II pin applied voltage               | VII                | 0   | —                | $AV_{DD}$ | V    | 1,   2                                                      |

| V <sub>REG</sub> pin capacitance     | C <sub>REG</sub>   | —   | 1.0              | —         | μF   | V <sub>REG</sub>                                            |

| Operating junction temperature       | T <sub>JO</sub>    | -40 | _                | +125      | °C   |                                                             |

## **Electrical Characteristics**

(Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $AV_{DD} = VP_{IN1} = VP_{IN2} = 5.0 V$ , VOUT2 = 3.3 V,  $f_{OSC} = 1 MHz$ , DSTB = L)

|                                                          | Parameter                                   | Symbol                 | Min   | Тур   | Max   | Unit | Condition                                                                             |

|----------------------------------------------------------|---------------------------------------------|------------------------|-------|-------|-------|------|---------------------------------------------------------------------------------------|

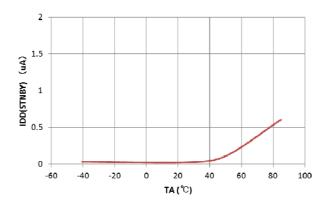

| Total                                                    | Standby current                             | I <sub>DD(STNBY)</sub> | _     | 1     | 2     | μΑ   | AI <sub>DD</sub> +IP <sub>IN1</sub> +IP <sub>IN2</sub><br>SHDNB1 = SHDNB2 = AGND      |

|                                                          | Circuit operation current 1                 | I <sub>DD1</sub>       |       | 1.2   | 2     | mA   | AI <sub>DD</sub> , SHDNB1 = SHDNB2 = AV <sub>DD</sub><br>DSTB = GND (normal mode)     |

|                                                          | Circuit operation current 2                 | I <sub>DD2</sub>       |       | 25    | 45    | μA   | $AI_{DD}$ , SHDNB1 = SHDNB2 = $AV_{DD}$<br>DSTB = $AV_{DD}$ (ultra low-power<br>mode) |

| Internal<br>power<br>supply block<br>(V <sub>REG</sub> ) | Internal power supply voltage               | V <sub>REG</sub>       | 2.25  | 2.4   | 2.55  | V    | I <sub>REG</sub> = 0mA                                                                |

| Under<br>voltage lock                                    | Operation start voltage<br>during rise time | $AV_{DD(L-H)}$         | 2.7   | 2.9   | 3.0   | V    | $AV_{DD}$ pin voltage is detected                                                     |

| out circuit<br>(UVLO)                                    | Operation stop voltage                      | $AV_{DD(H-L)}$         | 2.6   | 2.8   | 3.0   | V    | $AV_{\mbox{\scriptsize DD}}$ pin voltage is detected                                  |

| Short-circuit protection                                 | II1 input detection voltage (ch1)           | V <sub>TH(II)1</sub>   | 65    | 75    | 85    | %    | II1 pin, Ratio to the output voltage<br>or E/A1 threshold voltage                     |

| circuit (SCP)                                            | Delay time                                  | t <sub>(DLY)</sub>     |       | 10    | 20    | ms   |                                                                                       |

| Oscillation<br>block                                     | Oscillation frequency                       | f <sub>osc</sub>       |       | 1000  | —     | kHz  |                                                                                       |

| Soft start<br>block                                      | Soft start time                             | t <sub>ss</sub>        | 0.9   | 2.0   | 4.0   | ms   | ch1, ch2                                                                              |

| PWM block                                                | Maximum duty                                | D <sub>MAX.(PWM)</sub> | _     | 100   | _     | %    | ch1                                                                                   |

| Output                                                   | ch1 output voltage accuracy                 | V <sub>OUT1</sub>      | -2.5  |       | +2.5  | %    | I <sub>01</sub> = 200mA, (with internal resistor)                                     |

| voltage<br>accuracy<br>(with resistor<br>inside)         | ch2 output voltage accuracy                 | V <sub>OUT2</sub>      | -1    |       | +1    | %    | $I_{O2}$ = 10mA, (with internal resistor)                                             |

| E/A block<br>(with resistor                              | E/A 1 input threshold voltage               | V <sub>ITH1</sub>      | 0.780 | 0.800 | 0.820 | V    | Including input offset, (with external resistor)                                      |

| outside)                                                 | E/A 2 input threshold voltage               | V <sub>ITH2</sub>      | 0.792 | 0.800 | 0.808 | V    | Including input offset, (with external resistor)                                      |

| Output block                                             | P-ch ON resistance                          | R <sub>on-p1</sub>     | _     | 0.15  | 0.3   | Ω    | I <sub>0</sub> = 100mA                                                                |

|                                                          | N-ch ON resistance                          | R <sub>on-n1</sub>     | —     | 0.15  | 0.3   | Ω    | I <sub>o</sub> = -100mA                                                               |

| Discharging                                              | ch1 ON resistance                           | R <sub>ondc1</sub>     |       | 100   | 200   | Ω    | ch1, I <sub>DC</sub> = 20mA                                                           |

| circuit block                                            | ch2 ON resistance                           | R <sub>ondc2</sub>     | —     | 200   | 400   | Ω    | ch2, I <sub>DC</sub> = 20mA                                                           |

| Series<br>regulator                                      | The voltage between the<br>input and output | V <sub>DIF2</sub>      | 0.5   | _     | —     | V    | I <sub>02</sub> = 20mA                                                                |

| block (ch2,                                              | Input regulation                            | REG <sub>IN2</sub>     | _     | _     | 50    | mV   | $I_{02}$ = 20mA, VP <sub>IN</sub> = 3.0V to 5.5V                                      |

| DSTB =                                                   | Load regulation                             | REG <sub>L2</sub>      |       |       | 50    | mV   | I <sub>02</sub> = 1mA to 500mA                                                        |

| AGND:<br>normal                                          | Output short-circuit current                | I <sub>O2short</sub>   |       | 100   | —     | mA   | OUT2=AGND                                                                             |

| mode)                                                    | Peak output current                         | I <sub>O2peak</sub>    | 550   | _     |       | mA   |                                                                                       |

| Series<br>regulator                                      | The voltage between the<br>input and output | V <sub>DIF2</sub>      | 0.5   | —     |       | V    | I <sub>O2</sub> = 10μA                                                                |

| block (ch2,                                              | Input regulation                            | REG <sub>IN2</sub>     | _     | _     | 100   | mV   | $I_{O2}$ = 10µA, VP <sub>IN</sub> = 3.0V to 5.5V                                      |

| DSTB =<br>AV <sub>DD</sub> : ultra<br>low-power<br>mode) | Load regulation                             | REG <sub>L2</sub>      | _     | _     | 100   | mV   | I <sub>02</sub> = 10μA to 50mA                                                        |

## **Electrical Characteristics (cont.)**

| (Unless otherwise specified, $T_A = 25^{\circ}C$ , $AV_{DD} = VP_{IN1} = VP_{IN2} = 5.0 V$ , $VOUT2 = 3.3 V$ , $f_{OSC}$ |

|--------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------|

|                               | Parameter              | Symbol               | Min | Тур | Max | Unit | Condition                                                                        |

|-------------------------------|------------------------|----------------------|-----|-----|-----|------|----------------------------------------------------------------------------------|

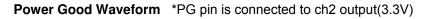

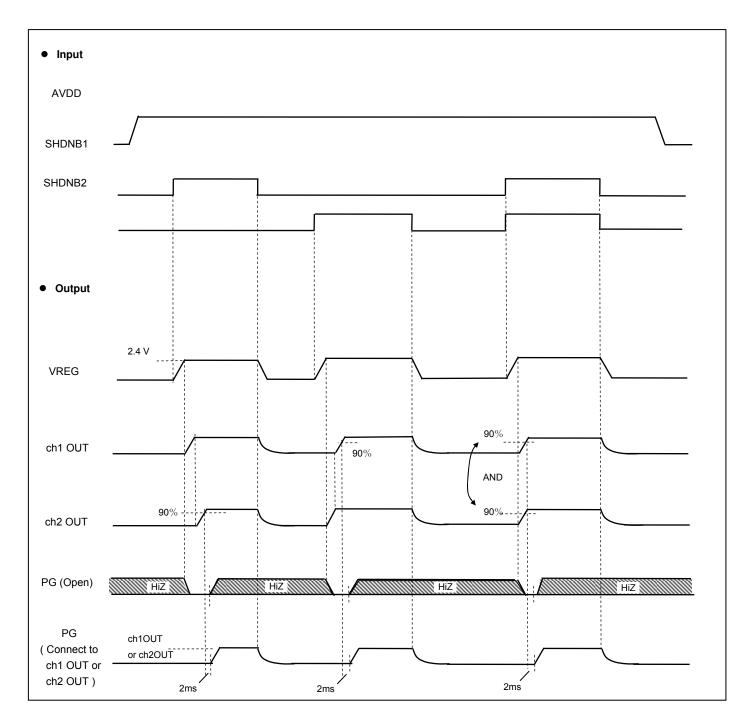

| Power-good                    | Threshold voltage      | V <sub>TH(PG)</sub>  | 86  | 90  | 94  | %    | PG = "HiZ"→"L", "L"→"HiZ"                                                        |

| circuit block                 |                        |                      |     |     |     |      | Ratio to the output voltage                                                      |

|                               | PG pin output voltage  | $V_{PG}$             |     | _   | 0.1 | V    | I <sub>PG-</sub> = 0.1mA                                                         |

|                               | PG pin leakage current | I <sub>LEAK-PG</sub> |     | _   | 1   | μA   | SHDNB1, SHDNB2 = AGND                                                            |

|                               | Delay time             | t <sub>DLY-PG</sub>  |     | _   | 2   | ms   | Time from detecting of output<br>startup until change form L to HiZ<br>on PG pin |

| ON/OFF<br>controller<br>block | Threshold voltage      | V <sub>TH</sub>      | 0.6 | —   | 1.4 | V    | SHDNB1, SHDNB2, DSTB                                                             |

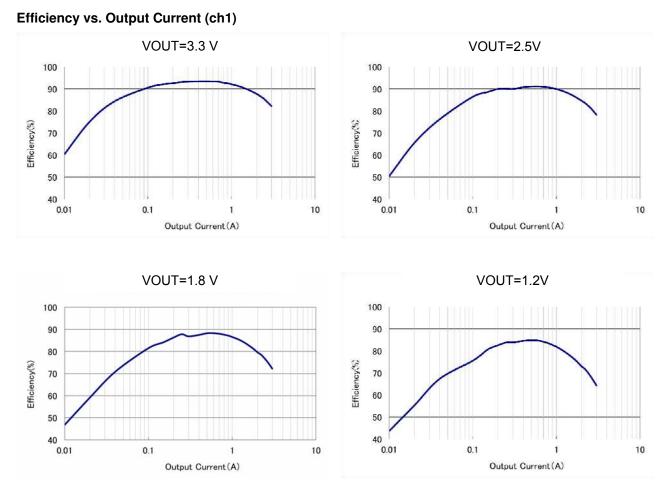

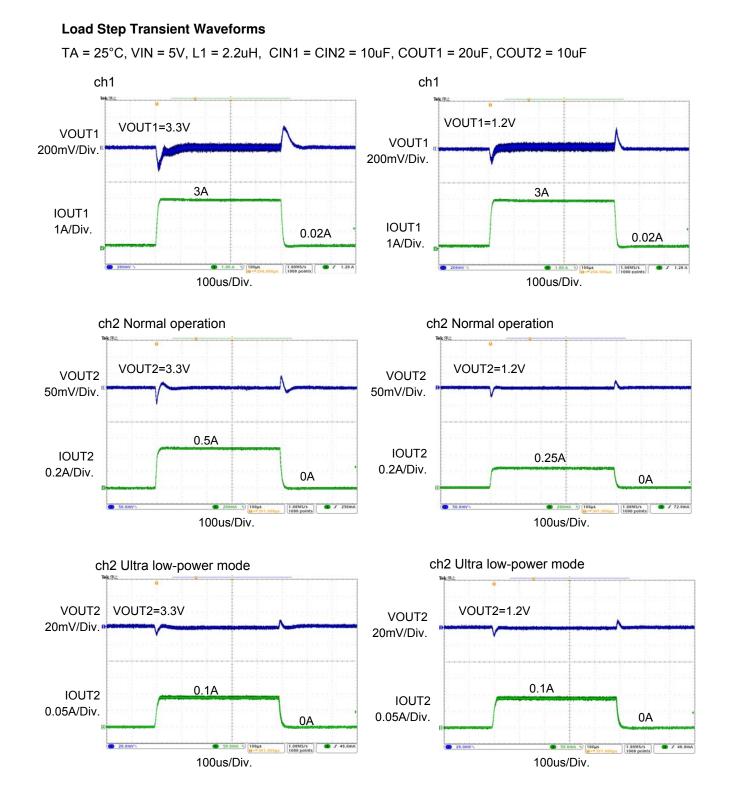

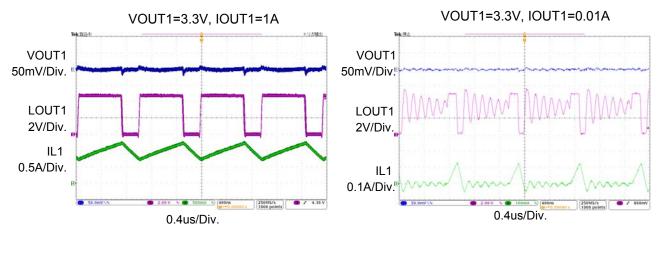

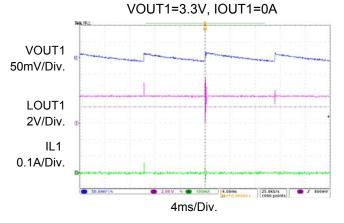

## **Typical Performance Characteristics**

(Unless otherwise specified,  $T_A = 25^{\circ}C$ ,  $AV_{DD} = VP_{IN1} = VP_{IN2} = 5.0 V$ )

#### R18DS0013EJ0102 Rev.1.02 Jul 23. 2014

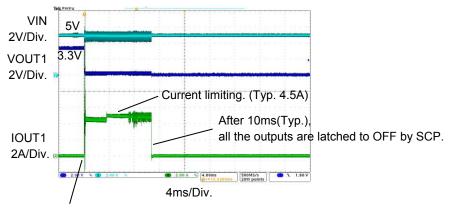

#### **Ch1 Operation Waveforms**

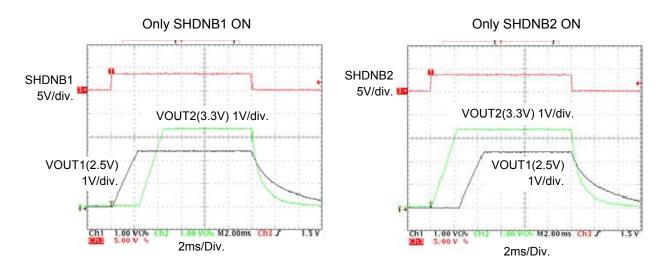

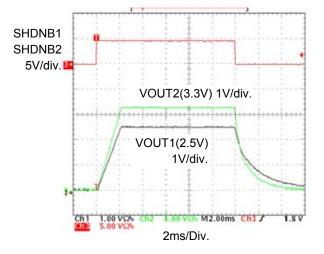

#### Start-up and Shutdown Waveforms

Both SHDNB1 and SHDNB2 ON at the same time

#### Short-circuit protection waveform

Ch1 output short-circuits.

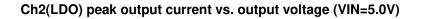

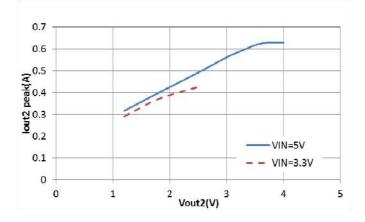

Ch2(LDO) output voltage vs. output current (VIN=5.0V)

Standby current vs. Operating ambient temperature

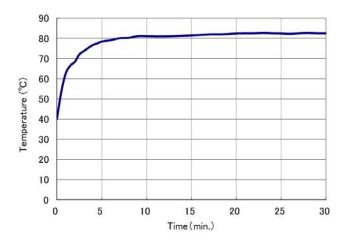

#### IC Surface Temperature vs. Time

Ch1 and ch2 operation (normal mode) VIN=5V ch1:3.3V, 2A ch2 : 1.8V, 0.3A  $T_A = 25^{\circ}C$ Measured on Renesas Evaluation Board

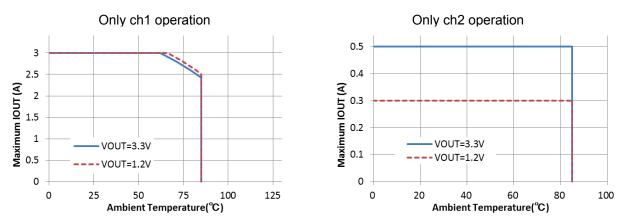

#### **Temperature Derating Curve**

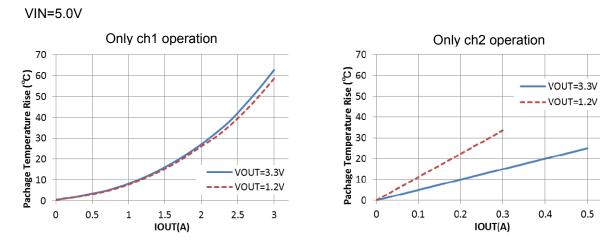

#### Pakage Tempereture Rise vs. IOUT

#### Maximum IOUT vs. Ambient Tempereture

Note : When calculate the package temperature with both ch1 and ch2 operation, reference these data.

0.5

### **Control Block**

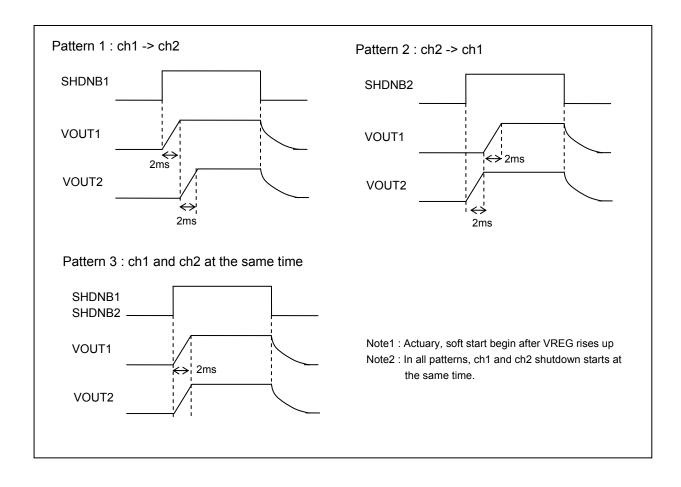

#### SHDNB1, SHDNB2: ON/OFF Setting

| SHDNB1 | SHDNB2 | ch1                                                                        | ch2 |

|--------|--------|----------------------------------------------------------------------------|-----|

| L      | L      | OFF                                                                        | OFF |

| Н      | L      | Start-up in order of ch1 and ch2<br>Stop ch1 and ch2 at the same time      |     |

| L      | Н      | Start-up in order of ch2 and ch1<br>Stop ch1 and ch2 at the same time      |     |

| Н      | Н      | Start-up ch1 and ch2 at the same time<br>Stop ch1 and ch2 at the same time |     |

Note: L: Low level, H: High level

OFF: circuit stand-by, ON: circuit operation status

When both SHDNB1 and SHDNB2 are H, RAA23021x continues operation even if one of them is turned to L. RAA23021x stops when both of them are turned L.

#### DSTB: IC Ultra Low-Power Mode Setting

| DSTB | IC Operation                                               |  |  |  |

|------|------------------------------------------------------------|--|--|--|

| L    | Normal operation                                           |  |  |  |

| Н    | Ultra low-power mode operation (ch1: stop, ch2: operation) |  |  |  |

Note: L: Low level, H: High level

## **Output Status**

#### V<sub>REG</sub> Pin Status

| SHDNB1 | SHDNB2 | DSTB   | V <sub>REG</sub> |

|--------|--------|--------|------------------|

| L      | L      | L or H | AGND             |

| Н      | L      | L      | 2.4 V            |

| L      | Н      |        |                  |

| Н      | Н      |        |                  |

| Н      | L      | Н      | AGND             |

| L      | Н      |        |                  |

| Н      | Н      |        |                  |

Note: L: Low level, H: High level

#### ch1, ch2 Output Pin Status

| ch1 · ch2 | ch1                                  | ch2                     |

|-----------|--------------------------------------|-------------------------|

| Status    | LOUT1                                | OUT2                    |

| Stop      | PGND                                 | AGND                    |

|           | (Discharge circuit: On)*             | (Discharge circuit: On) |

| Operation | Pulse<br>(VP <sub>IN1</sub> or PGND) | Set voltage             |

Note: Ch1 discharge circuit is "On" during ultra low-power mode.

#### PG Pin Status (ch1, ch2 output detect)

| IC Operation Status      |             |                                                                                   |                  |  |  |

|--------------------------|-------------|-----------------------------------------------------------------------------------|------------------|--|--|

| SHDNB Pin                | DSTB<br>Pin | ch1, ch2 Output Status                                                            | Output<br>Status |  |  |

| SHDNB1 = L<br>SHDNB2 = L | L or H      | Stop                                                                              | HiZ              |  |  |

| SHDNB1 = H               | L           | ch1 or ch2 output voltage is under 90% of the set voltage                         | L                |  |  |

| or                       |             | ch1 and ch2 output voltage are over 90% of the set voltage                        | HiZ              |  |  |

| SHDNB2 = H               | Н           | ch1: Stop                                                                         | HiZ              |  |  |

|                          |             | ch2: Operation (Both output voltage is over 90% of setting voltage and under 90%) |                  |  |  |

Note: L: Low level, H: High level, HiZ: High impedance

Caution: When both ch1 and ch2 output voltage start up over 90%, there is delay time (under 2ms) before PG pin becomes HiZ.

When using power good (PG pin), connect it to ch1 or ch2 output. Recommended value of pull-up resistor is  $100k\Omega$ .

## **Timing Chart**

## **Operation of Each Block (Overview)**

#### Rise up sequencer

The IC "rise up" sequence feature has 3 patterns described below. The internal "rise up" sequence capability does not need any additional external circuitry or components.

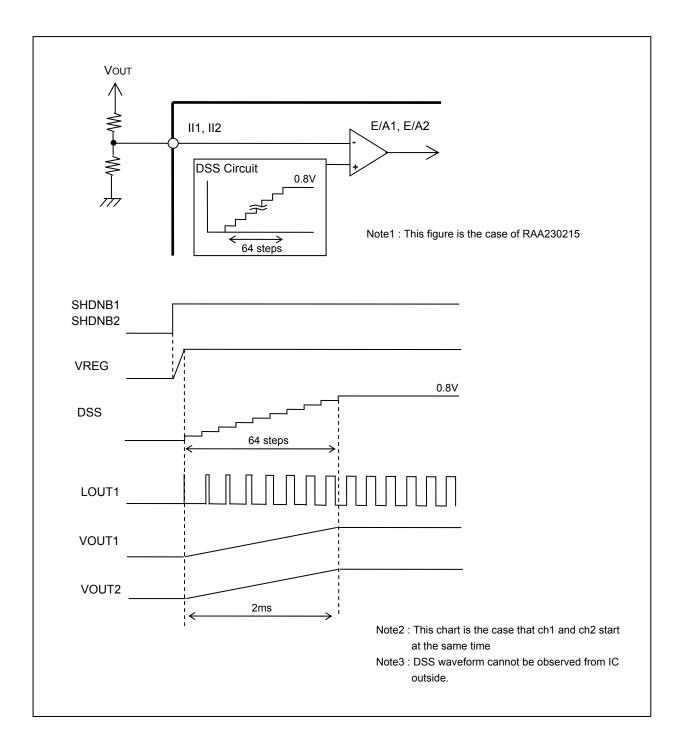

#### Soft start

To limit the startup inrush current and output voltage overshoot, a soft start circuit is used to ramp up the reference voltage from 0 V to its final value linearly. The soft start time are fixed for both ch1 and ch2 are 2ms(Typ.) and no additional components are needed. Soft start feature gradually increases the error amplifier (E/A) input threshold voltage by using the voltage that is generated by the digital soft start (DSS) circuit in 64 steps.

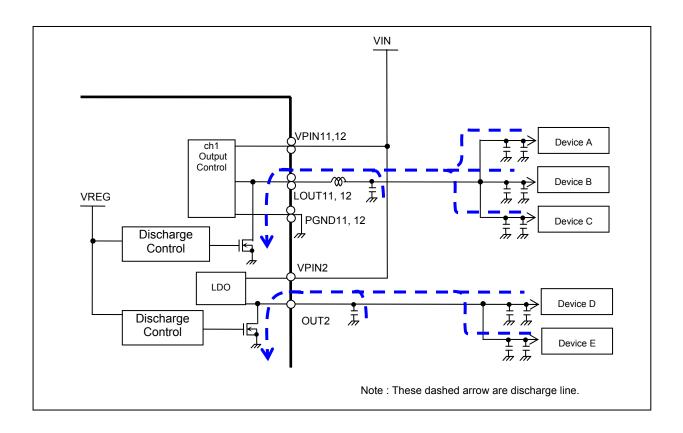

#### **Discharge circuit**

This IC has the discharge circuit for both ch1 and ch2. This enables a rapid discharge without an external MOSFET. When SHDNB pin is changed from high level to low, discharge switches of ch1 and ch2 turn on at the same time, and they discharge all capacitors which are connected to each output through LOUT1 and OUT2 pin.

When AVDD pin voltage becomes low level, discharge switches become off because there are no voltage to keep them on. The control voltage of discharge switches is VREG, and the discharge time of VREG capacitor is over 100ms when AVDD voltage fall down, so even if SHDNB pin is connected to AVDD pin, the output voltage of ch1 and ch2 can be discharged because VREG voltage level can keep the discharge switches on.

About calculation of discharge time, see page 30.

#### **Power Good**

Power Good (PG) is an open-drain output that requires a pull – up resistor (Recommended value =  $100k\Omega$ ). PG releases when the both ch1 and ch2 FB voltage and thus the output voltage rises above 90% of nominal regulation point. The PG goes low when the FB voltage falls below 90% of the regulation point. When both SHDNB pins become low level, PG pin become high impedance (HiZ) because VREG is used for PG control and it fall down at this time. So, if PG is connected to AVDD, its status keep high level. PG pin must be connected to ch1 or ch2 output.

This function can be used for sequence signal for other devices.

#### RAA23021x

#### **Protection Circuit View**

|                 |                                                   | Operat                         | ion Status          |                                         |  |  |

|-----------------|---------------------------------------------------|--------------------------------|---------------------|-----------------------------------------|--|--|

| Protection      |                                                   | Common Circuit                 | • • •               |                                         |  |  |

| Circuit         | Function                                          | (V <sub>REG</sub> , OSC, etc.) | Output              | Reset                                   |  |  |

| Short-circuit   | Detect ch1 output voltage                         | Operation                      | All the output are  | Change SHDNB1 pin and                   |  |  |

| protection      | dropping because of                               |                                | latched to OFF      | SHDNB2 pin from high to low             |  |  |

| (SCP)           | short-circuit, etc.                               |                                |                     | or                                      |  |  |

| *Only ch1       | (Timer latch type)                                |                                |                     | Drop AV <sub>DD</sub> pin input voltage |  |  |

| Thermal         | Detect increase of IC                             | Operation                      | All the output are  | under the operation stop                |  |  |

| shutdown        | internal temperature                              |                                | latched to OFF      | voltage (2.8 V)                         |  |  |

| circuit         | (Over 150°C)                                      |                                |                     |                                         |  |  |

| (TSD)           | (Timer latch type)                                |                                |                     |                                         |  |  |

| Over current    | Detect ch2 over current                           | Operation                      | ch2 output is down  | Release over current status             |  |  |

| protection      |                                                   |                                | (ch1 continues      | (Under the output short-circuit         |  |  |

| (OCP)           |                                                   |                                | operation)          | current: 100 mA)                        |  |  |

| *Only ch2       |                                                   |                                |                     |                                         |  |  |

| Under voltage   | Under voltage Detect dropping of AV <sub>DD</sub> |                                | All the outputs are | Up AV <sub>DD</sub> pin input voltage   |  |  |

| lockout circuit | (IC power supply)                                 |                                | stop                | over the operation start                |  |  |

| (UVLO)          |                                                   |                                |                     | voltage (2.9 V)                         |  |  |

Note: The common circuit stops if AVDD is lower than VREG.

When ultra low-power mode, these protection circuits DO NOT operate.

#### Short-Circuit Protection Circuit (ch1)

When the voltage of ch1 drops, the voltage of the II1 pin also drops. If it falls below the input detection voltage of the short-circuit protection circuit (under 75% of output voltage), the timer circuit starts operating. And after 10 ms, all the outputs are latched to OFF. At this time, common circuits (such as the internal power supply block, and oscillator, etc.) continue operating.

When the short-circuit protection circuit is operating, to reset the latch circuit, either change the level of the SHDNB1 pin and SHDNB2 pin from high to low or drop the level of the power supply voltage ( $AV_{DD}$ ) to the level below the operation stop voltage of the under voltage lockout circuit (2.8 V).

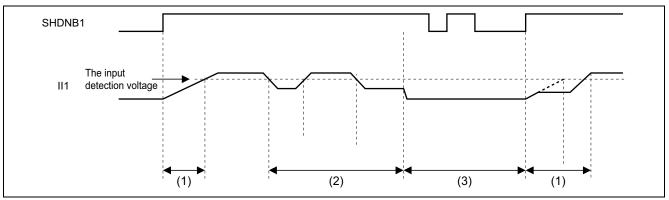

• Timing Chart (when ch1 is short circuited)

- (1) At starting

- A short-circuit will not be detected while the ch1 is undergoing a soft start (that is, short-circuit protection is not triggered). If a short circuit occurs while ch1 is starting, short-circuit protection will start after the soft start time elapses following startup.

- If a short-circuit occurs in a channel that is operating while another channel is being soft-started, short-circuit

protection will start immediately.

- (2) Short-circuit protection operation

- If a short circuit is detected in ch1 (ch1 II pin voltage is lower than the input detection voltage except soft-stare period), the timer circuit starts operating. And after 10 ms, all the outputs are latched to OFF.

— Common circuits (such as the internal power supply block, and oscillator, etc.) continue operating.

- (3) Cancelling short-circuit protection

- To reset the latch circuit, either change the level of the SHDNB1 pin and SHDNB2 pin from high to low, or drop the level of the power supply voltage (AV<sub>DD</sub>) to the operation stop voltage of the under voltage lockout circuit (2.8 V).

#### Thermal Shutdown Circuit (Timer Latch Type)

After overheating has been detected (shutdown temperature: 150°C or higher), the timer circuit starts operating (as same as SCP). And after 10 ms, all the outputs are latched to OFF. Common circuits (such as the internal power supply block, and oscillator, etc.) continue operating.

When the thermal shutdown circuit is operating, either change the level of the SHDNB1 pin and SHDNB2 pin from high to low, or drop the level of the power supply voltage ( $AV_{DD}$ ) to the operation stop voltage of the under voltage lockout circuit (2.8 V).

When ultra low-power mode, this circuits DOES NOT operate.

#### Under Voltage Lockout Circuit (Auto Recovery Type)

(1) Under voltage lockout operation

When the power supply voltage  $(AV_{DD})$  falls to the operation stop voltage (2.8 V), output from all channels stops. Common circuits (such as the internal power supply block, and oscillator, etc.) continue operating.

(2) Restoring output

Once  $AV_{DD}$  voltage is restored to the operation start voltage (2.9 V), the under voltage lockout operation is canceled and output automatically resumes. The output voltage cannot be restored while the under voltage lockout circuit is operating, not even by manipulating the SHDNB pin.

When ultra low-power mode, this circuits DOES NOT operate.

#### **Current Limiting**

Current limit

Ch1 operates under the current control mode. If an overcurrent occurs, the current is limited on a pulse-by-pulse basis. If the current sensor detects an overcurrent, the current is limited and the switching operation of the Power MOSFET in the output stage stops until the next cycle.

4.5

А

ch1OUT 3.3V

ch10UT 1.2V

When the ch1 current is limited, the output voltage drops. If the ch1 II pin voltage falls below the input detection voltage, the short-circuit protection circuit starts operating.

| Reference data (Unless otherwise specified, $T_A = 25^{\circ}C$ , $AV_{DD} = VP_{IN1} = 5.0 V$ ) |        |     |     |     |      |                       |  |  |

|--------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|-----------------------|--|--|

| Item                                                                                             | Symbol | Min | Тур | Max | unit | Measurement condition |  |  |

II IM1 1

| value         | ch1 Current limet 2         | I <sub>LIM1_2</sub> | — | 4.5        |     | Α |

|---------------|-----------------------------|---------------------|---|------------|-----|---|

| Noto: Thoop d | ata ara far rafaranaa and n | of guarant          |   | agaitigati | 222 |   |

Note: These data are for reference and not guaranteed as specifications.

#### **Reverse Current Protection (ch1)**

ch1 Current limet 1

Ch1 have a reverse current protection circuit. When the bottom of inductor current is under ground, low-side N-ch MOSFET of output block is stopped, and ch1 operate as diode rectification. So, consumption current at light load can be reduced.

#### Over Current Protection (ch2)

Ch2 have a fold back type current protection circuit. If over current occur, protection operation is started and load current is limited (output short-circuit current: 100 mA).

Peak output current depend on output voltage. When VPIN2=5V and VOUT2=3.3V, it is over 550mA.

When ultra low-power mode, this circuits DOES NOT operate.