Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **3V W-CDMA BAND 8 LINEAR PA MODULE**

Package Style: Module, 10-Pin, 3mmx3mmx1.0mm

### **Features**

- HSDPA and HSPA+ Compliant

- Low Voltage Positive Bias Supply (3.0V to 4.35V)

- +28.5 dBm Linear Output Power (+27.0 dBm HSDPA)

- High Efficiency Operation 41% at P<sub>OUT</sub>=+28.5dBm 22% at P<sub>OUT</sub>=+18.0dBm 11% at P<sub>OUT</sub>=+10.0dBm

- Low Quiescent Current in Low Power Mode: 6 mA

- Internal Voltage Regulator

Eliminates the Need for External Reference Voltage (V<sub>RFF</sub>)

- 3-Mode Power States with Digital Control Interface

- Integrated Power Coupler

- Integrated Blocking and Collector Decoupling Capacitors

### **Applications**

- WCDMA/HSDPA/HSUPA Wireless Handsets and Data Cards

- Dual-Mode UMTS Wireless Handsets

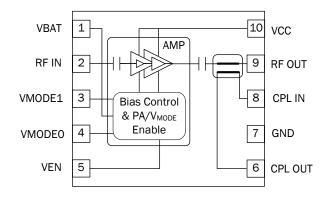

Functional Block Diagram

### **Product Description**

The RF7228 is a high-power, high-efficiency, linear power amplifier designed for use as the final RF amplifier in 3V,  $50\Omega$  W-CDMA mobile cellular equipment and spread-spectrum systems. This PA is developed for UMTS Band 8 which operates in the 880MHz to 915MHz frequency band. The RF7228 has two digital control pins to select one of three power modes to optimize performance and current drain at lower power levels. The part also has an integrated directional coupler which eliminates the need for an external discrete coupler at the output. The RF7228 is fully HSDPA and HSPA+ compliant and is assembled in a 10-pin, 3mmx3mm module.

### **Ordering Information**

RF7228 3V W-CDMA Band 8 Linear PA Module RF7228PCBA-410 Fully Assembled Evaluation Board

| Optimum recimology Matching® Applied |               |              |            |  |  |

|--------------------------------------|---------------|--------------|------------|--|--|

| GaAs HBT                             | ☐ SiGe BiCMOS | ☐ GaAs pHEMT | ☐ GaN HEMT |  |  |

| GaAs MESFET                          | ☐ Si BiCMOS   | ☐ Si CMOS    | ☐ RF MEMS  |  |  |

| InGaP HBT                            | ☐ SiGe HBT    | ☐ Si BJT     | ☐ LDMOS    |  |  |

### **Absolute Maximum Ratings**

| Parameter                                         | Rating      | Unit |

|---------------------------------------------------|-------------|------|

| Supply Voltage in Standby Mode                    | 6.0         | V    |

| Supply Voltage in Idle Mode                       | 6.0         | V    |

| Supply Voltage in Operating Mode, $50\Omega$ Load | 6.0         | V    |

| Supply Voltage, V <sub>BAT</sub>                  | 6.0         | V    |

| Control Voltage, VMODE0,<br>VMODE1                | 3.5         | V    |

| Control Voltage, V <sub>EN</sub>                  | 3.5         | V    |

| RF - Input Power                                  | +10         | dBm  |

| RF - Output Power                                 | +30         | dBm  |

| Output Load VSWR (Ruggedness)                     | 10:1        |      |

| Operating Ambient Temperature                     | -30 to +110 | °C   |

| Storage Temperature                               | -55 to +150 | °C   |

### Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EUDirective 2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

| Dawastan                                | Specification       |      |        | 11.21 | 0                       |  |

|-----------------------------------------|---------------------|------|--------|-------|-------------------------|--|

| Parameter                               | Min.                | Тур. | . Max. | Unit  | Condition               |  |

| Recommended Operating Conditions        |                     |      |        |       |                         |  |

| Operating Frequency Range               | 880                 |      | 915    | MHz   |                         |  |

| V <sub>BAT</sub>                        | +3.0                | +3.4 | +4.35  | V     |                         |  |

| V <sub>CC</sub>                         | +3.0 <sup>1</sup>   | +3.4 | +4.35  | V     |                         |  |

| V <sub>EN</sub>                         | 0                   |      | 0.5    | V     | PA disabled.            |  |

|                                         | 1.4                 | 1.8  | 3.0    | V     | PA enabled.             |  |

| V <sub>MODEO</sub> , V <sub>MODE1</sub> | 0                   |      | 0.5    | V     | Logic "low".            |  |

|                                         | 1.5                 | 1.8  | 3.0    | V     | Logic "high".           |  |

| P <sub>OUT</sub>                        |                     |      |        |       |                         |  |

| Maximum Linear Output<br>(HPM)          | 28.5 <sup>2,3</sup> |      |        | dBm   | High Power Mode (HPM)   |  |

| Maximum Linear Output<br>(MPM)          | 18.0 <sup>2,3</sup> |      |        | dBm   | Medium Power Mode (MPM) |  |

| Maximum Linear Output<br>(LPM)          | 10.0 <sup>2,3</sup> |      |        | dBm   | Low Power Mode (LPM)    |  |

| Ambient Temperature                     | -30                 | +25  | +85    | °C    |                         |  |

#### Notes:

HSDPA Configuration:  $\beta c=12$ ,  $\beta d=15$ ,  $\beta hs=24$

HSPA+ Configuration: Rel7 Subtest 1

$<sup>^{1}\</sup>mathrm{Minimum}\,\mathrm{V}_{\mathrm{CC}}$  for max  $\mathrm{P}_{\mathrm{OUT}}$  is indicated.

$<sup>^2</sup>$ For operation at V<sub>CC</sub>=+3.2V, derate P<sub>OUT</sub> by 0.6dB. For operation at V<sub>CC</sub>=3.0V, derate P<sub>OUT</sub> by 1.3dB.

$<sup>^{3}</sup>$ P $_{OUT}$  is specified for 3GPP (Rel99) modulation. For HSDPA and HSPA+ operation, derate P $_{OUT}$  by 1.5 dB:

| Parameter                                               | Specification |       |      | Heit   | Condition                                                                                                                                                                                                                              |

|---------------------------------------------------------|---------------|-------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                               | Min.          | Тур.  | Max. | Unit   | Condition                                                                                                                                                                                                                              |

| Electrical Specifications                               |               |       |      |        | $ \begin{array}{l} \text{T=+25^{\circ}\text{C},V_{\text{CC}}=V_{\text{BAT}}=+3.4\text{V},V_{\text{EN}}=+1.8\text{V},50\Omega} \\ \text{system,W-CDMARel99Modulationunless} \\ \text{otherwise specified.} \end{array} $                |

| Gain                                                    | 27            | 30    |      | dB     | HPM, P <sub>OUT</sub> =28.5 dBm                                                                                                                                                                                                        |

|                                                         | 16            | 18    |      | dB     | MPM, P <sub>OUT</sub> ≤18.0dBm                                                                                                                                                                                                         |

|                                                         | 10            | 13    |      | dB     | LPM, P <sub>OUT</sub> ≤10.0dBm                                                                                                                                                                                                         |

| Gain Linearity                                          |               | ±0.7  |      | dB     | HPM, 18.0dBm≤P <sub>OUT</sub> ≤28.5dBm                                                                                                                                                                                                 |

| ACLR - 5 MHz Offset                                     |               | -40   |      | dBc    | HPM, P <sub>OUT</sub> =28.5dBm                                                                                                                                                                                                         |

|                                                         |               | -40   |      | dBc    | MPM, P <sub>OUT</sub> =18.0dBm                                                                                                                                                                                                         |

|                                                         |               | -40   |      | dBc    | LPM, P <sub>OUT</sub> =10.0dBm                                                                                                                                                                                                         |

| ACLR - 10 MHz Offset                                    |               | -52   |      | dBc    | HPM, P <sub>OUT</sub> =28.5 dBm                                                                                                                                                                                                        |

|                                                         |               | -60   |      | dBc    | MPM, P <sub>OUT</sub> =18.0dBm                                                                                                                                                                                                         |

|                                                         |               | -60   |      | dBc    | LPM, P <sub>OUT</sub> =10.0dBm                                                                                                                                                                                                         |

| PAE                                                     |               | 41    |      | %      | HPM, P <sub>OUT</sub> =28.5 dBm                                                                                                                                                                                                        |

|                                                         |               | 22    |      | %      | MPM, P <sub>OUT</sub> =18.0dBm                                                                                                                                                                                                         |

|                                                         |               | 11    |      | %      | P <sub>OUT</sub> =11.0dBm                                                                                                                                                                                                              |

| Current Drain                                           |               | 500   |      | mA     | HPM, P <sub>OUT</sub> =28.5dBm                                                                                                                                                                                                         |

|                                                         |               | 85    |      | mA     | MPM, P <sub>OUT</sub> =18dBm                                                                                                                                                                                                           |

|                                                         |               | 30    |      | mA     | LPM, P <sub>OUT</sub> = 10 dBm                                                                                                                                                                                                         |

| Quiescent Current                                       |               | 85    |      | mA     | HPM, DC only                                                                                                                                                                                                                           |

| Quiescent durent                                        |               | 20    |      | mA     | MPM, DC only                                                                                                                                                                                                                           |

|                                                         |               | 6     |      | mA     | LPM, DC only                                                                                                                                                                                                                           |

| Enable Current                                          |               | 0.1   |      | mA     | Source or sink current. V <sub>EN</sub> =1.8V.                                                                                                                                                                                         |

| Mode Current (I <sub>MODE0</sub> , I <sub>MODE1</sub> ) |               | 0.1   |      | mA     | Source or sink current. V <sub>MODEO</sub> , V <sub>MODE1</sub> =1.8V.                                                                                                                                                                 |

| Leakage Current                                         |               | 5.0   | 15.0 | μА     | DC only. V <sub>CC</sub> =V <sub>BAT</sub> =4.35V,                                                                                                                                                                                     |

|                                                         |               |       |      | -      | V <sub>EN</sub> =V <sub>MODEO</sub> =V <sub>MODE1</sub> =0.5V.                                                                                                                                                                         |

| Noise Power in Receive Band                             |               | -135  |      | dBm/Hz | All power modes, measured at duplex offset frequency (FTX+45MHz). Rx: 925MHz to 960MHz, P <sub>OUT</sub> ≤28.5dBm                                                                                                                      |

| Input Impedance                                         |               | 1.5:1 |      | VSWR   | No ext. matching, P <sub>OUT</sub> ≤28.5dBm, all modes.                                                                                                                                                                                |

| Harmonic, 2FO                                           |               | -15   |      | dBm    | P <sub>OUT</sub> ≤28.5 dBm, all power modes.                                                                                                                                                                                           |

| Harmonic, 3FO                                           |               | -25   |      | dBm    | P <sub>OUT</sub> ≤28.5dBm, all power modes.                                                                                                                                                                                            |

| Spurious Output Level                                   |               |       | -70  | dBc    | All spurious, $P_{OUT} \le 28.5  dBm$ , all conditions, load VSWR $\le 6:1$ , all phase angles.                                                                                                                                        |

| Insertion Phase Shift                                   |               | ±25   |      | ٥      | Phase shift at 18dBm when switching from HPM to MPM and MPM to LPM at 10dBm.                                                                                                                                                           |

| DC Enable Time                                          |               |       | 10   | μS     | DC only. Time from $V_{\rm EN}$ =high to stable idle current (90% of steady state value).                                                                                                                                              |

| RF Rise/Fall Time                                       |               |       | 6    | μS     | P <sub>OUT</sub> ≤28.5 dBm, all modes. 90% of target, DC settled prior to RF.                                                                                                                                                          |

| Coupling Factor                                         |               | -20   |      | dB     | P <sub>OUT</sub> ≤28.5 dBm, all modes.                                                                                                                                                                                                 |

| Coupling Accuracy - Temp/Voltage                        |               | ±0.5  |      | dB     | $\begin{array}{l} P_{OUT}{\le}28.5\text{dBm, all modes.} \ \ -30^{\circ}\text{C}{\le}\text{T}{\le}85^{\circ}\text{C},\\ 3.0\text{V}{\le}\text{V}_{CC}^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

| Coupling Accuracy - VSWR                                |               | ±0.25 |      | dB     | P <sub>OUT</sub> ≤28.5dBm, all modes, load VSWR=2:1,<br>±0.25dB accuracy corresponds to 20dB directivity.                                                                                                                              |

| Pin         | Function | Description                                                                                                                                                                                                                                     |  |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | VBAT     | Supply voltage for bias circuitry.                                                                                                                                                                                                              |  |  |  |

| 2           | RF IN    | RF input internally matched to $50\Omega$ and DC blocked. Input matching includes a shunt inductor to ground which would short DC voltage placed on this pin.                                                                                   |  |  |  |

| 3           | VMODE1   | Digital control input for power mode selection (see Operating Modes truth table).                                                                                                                                                               |  |  |  |

| 4           | VMODE0   | Digital control input for power mode selection (see Operating Modes truth table).                                                                                                                                                               |  |  |  |

| 5           | VEN      | Digital control input for PA enable and disable (see Operating Modes truth table).                                                                                                                                                              |  |  |  |

| 6           | CPL_OUT  | Coupler output.                                                                                                                                                                                                                                 |  |  |  |

| 7           | GND      | This pin must be grounded.                                                                                                                                                                                                                      |  |  |  |

| 8           | CPL_IN   | Coupler input used for cascading couplers in series. Terminate this pin with a $50\Omega$ resistor if not connected to another coupler.                                                                                                         |  |  |  |

| 9           | RF OUT   | RF output internally matched to $50\Omega$ and DC blocked.                                                                                                                                                                                      |  |  |  |

| 10          | VCC      | Supply voltage for the first and second stage amplifier.                                                                                                                                                                                        |  |  |  |

| Pkg<br>Base | GND      | Ground connection. The package backside should be soldered to a topside ground pad connecting to the PCB ground plane with multiple ground vias. The pad should have a low thermal resistance and low electrical impedance to the ground plane. |  |  |  |

| $V_{EN}$ | V <sub>MODEO</sub> | V <sub>MODE1</sub> | V <sub>BAT</sub> | V <sub>CC</sub> | Conditions/Comments |

|----------|--------------------|--------------------|------------------|-----------------|---------------------|

| Low      | Low                | Low                | 3.0V to 4.35V    | 3.0V to 4.35V   | Power down mode     |

| Low      | Х                  | X                  | 3.0V to 4.35V    | 3.0V to 4.35V   | Standby Mode        |

| High     | Low                | Low                | 3.0V to 4.35V    | 3.0V to 4.35V   | High power mode     |

| High     | High               | Low                | 3.0V to 4.35V    | 3.0V to 4.35V   | Medium power mode   |

| High     | High               | High               | 3.0V to 4.35V    | 3.0V to 4.35V   | Low power mode      |

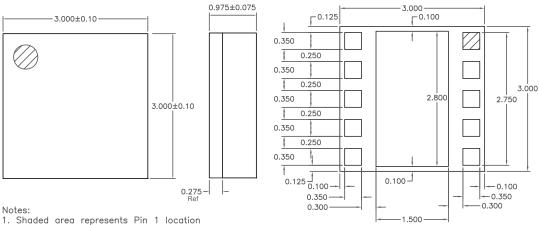

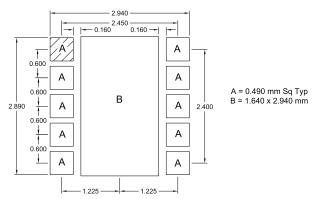

## **Package Drawing**

1. Snaded area represents Pin 1 location

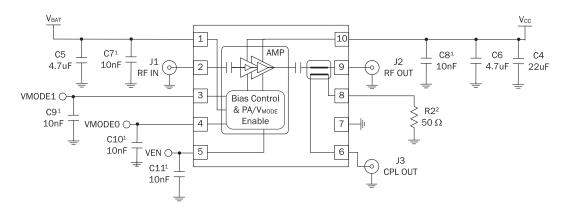

### **Preliminary Application Schematic**

#### NOTES

- 1 Place these capacitors as close to PA as possible.

- $250 \Omega$  resistor will be removed if pin 8 is connected to another coupler.

### **PCB Design Requirements**

#### **PCB Surface Finish**

The PCB surface finish used for RFMD's qualification process is electroless nickel, immersion gold. Typical thickness is  $3\mu$ inch to  $8\mu$ inch gold over  $180\mu$ inch nickel.

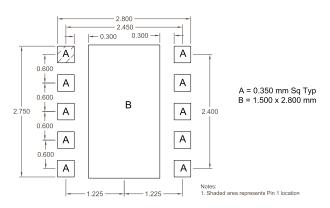

#### **PCB Land Pattern Recommendation**

PCB land patterns for RFMD components are based on IPC-7351 standards and RFMD empirical data. The pad pattern shown has been developed and tested for optimized assembly at RFMD. The PCB land pattern has been developed to accommodate lead and package tolerances. Since surface mount processes vary from company to company, careful process development is recommended.

### **PCB Metal Land Pattern**

PCB Metal Land Pattern (Top View)

# **RF7228**

#### **PCB Solder Mask Pattern**

Liquid Photo-Imageable (LPI) solder mask is recommended. The solder mask footprint will match what is shown for the PCB metal land pattern with a 2mil to 3mil expansion to accommodate solder mask registration clearance around all pads. The center-grounding pad shall also have a solder mask clearance. Expansion of the pads to create solder mask clearance can be provided in the master data or requested from the PCB fabrication supplier.

PCB Solder Mask Pattern (Top View)

#### Thermal Pad and Via Design

The PCB land pattern has been designed with a thermal pad that matches the die paddle size on the bottom of the device.

Thermal vias are required in the PCB layout to effectively conduct heat away from the package. The via pattern has been designed to address thermal, power dissipation and electrical requirements of the device as well as accommodating routing strategies.

The via pattern used for the RFMD qualification is based on thru-hole vias with 0.203mm to 0.330mm finished hole size on a 0.5mm to 1.2mm grid pattern with 0.025mm plating on via walls. If micro vias are used in a design, it is suggested that the quantity of vias be increased by a 4:1 ratio to achieve similar results.