# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **FLASH-Based Microcontroller with ASK/FSK Transmitter**

#### High Performance RISC CPU:

- · Only 35 instructions to learn

- All single cycle instructions except branches

- Operating speed:

- Precision Internal 4 MHz oscillator, factory calibrated to  $\pm 1\%$

- DC 20 MHz Resonator/Crystal/Clock modes

- DC 20 MHz crystal oscillator/clock input

- DC 4 MHz external RC oscillator

- DC 4 MHz XT crystal oscillator

- External Oscillator modes

- · Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

#### **Peripheral Features:**

- · Memory

- 1024 x 14 words of FLASH program memory

- 128 x 8 bytes of EEPROM data memory

- 64 x 8 bytes of SRAM data memory

- 100,000 write FLASH endurance

- 1,000,000 write EEPROM endurance

- FLASH/data EEPROM retention: > 40 years

- · Programmable code protection

- 6 I/O pins with individual direction control, weak pull-ups, and interrupt-on-pin change

- · High current sink/source for direct LED drive

- Analog comparator: 16 internal reference levels

- · Analog-to-Digital Converter: 10 bits, 4 channels

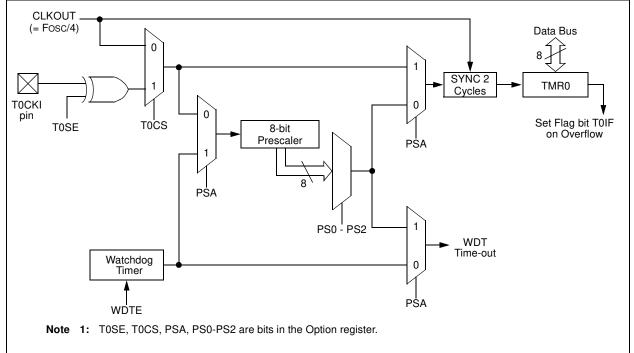

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with 3-bit prescaler

- Timer1 can use LP oscillator in INTOSC mode

- 5 μs wake-up from SLEEP typical with VDD = 3V

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

#### Low Power Features:

- Low power consumption: (typical with VDD = 3V)

- 14 mA transmitting +6 dBm at 434 MHz

- 4 mA transmitting -15 dBm at 434 MHz

- 500  $\mu\text{A},\,4.0~\text{MHz}$  INTOSC

- 0.6 µA SLEEP with watchdog enabled

- 0.1 µA standby current

- Wide operating voltage range from 2.0 5.5V

- Industrial and Extended temperature range

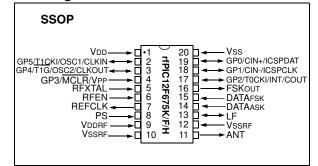

#### Pin Diagram:

#### **UHF ASK/FSK Transmitter:**

- Integrated crystal oscillator, VCO, loop filter and power amp for minimum external components

- ASK data rate: 0 40 Kbps

- FSK data rate: 0 40 Kbps by crystal pulling

- Output power: +10 dBm to -12 dBm in 4 steps

- · Adjustable transmitter power consumption

- Transmit frequency set by crystal multiplied by 32

- VCO phase locked to quartz crystal reference; allows narrow band receivers to be used to maximize range and interference immunity

- Crystal frequency divide by 4 available (REFCLK)

- Used in applications conforming to US FCC Part 15.231 and European EN 300 220 regulations

#### **Applications:**

- · Automotive Remote Keyless Entry (RKE) systems

- · Automotive alarm systems

- · Community gate and garage door openers

- · Burglar alarm systems

- · Building access

- · Low power telemetry

- · Meter reading

- Tire pressure sensors

- · Wireless sensors

| Device       | Frequency   | Modulation |  |  |

|--------------|-------------|------------|--|--|

| rfPIC12F675K | 290-350 MHz | ASK/FSK    |  |  |

| rfPIC12F675F | 380-450 MHz | ASK/FSK    |  |  |

| rfPIC12F675H | 850-930 MHz | ASK/FSK    |  |  |

#### **Table of Contents**

| 1.0   | Device Overview                             | 3   |

|-------|---------------------------------------------|-----|

| 2.0   | Memory Organization                         | 5   |

| 3.0   | GPIO Port                                   | 17  |

| 4.0   | Timer0 Module                               | 25  |

| 5.0   | Timer1 Module with Gate Control             | 28  |

| 6.0   | Comparator Module                           |     |

| 7.0   | Analog-to-Digital Converter (A/D) Module    | 39  |

| 8.0   | Data EEPROM Memory                          | 45  |

|       | UHF ASK/FSK Transmitter                     |     |

| 10.0  | Special Features of the CPU                 | 55  |

| 11.0  | Instruction Set Summary                     | 73  |

| 12.0  | Development Support                         | 81  |

| 13.0  | Electrical Specifications                   | 87  |

| 14.0  | DC and AC Characteristics Graphs and Tables | 13  |

| 15.0  | Packaging Information 1                     | 123 |

| Appe  | andix A: Data Sheet Revision History        | 125 |

| Index | ٢ 1                                         | 27  |

| On-L  | ine Support 1                               | 31  |

| Syste | ems Information and Upgrade Hot Line 1      | 31  |

| Read  | ler Response 1                              | 32  |

| Prod  | uct Identification System 1                 | 133 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

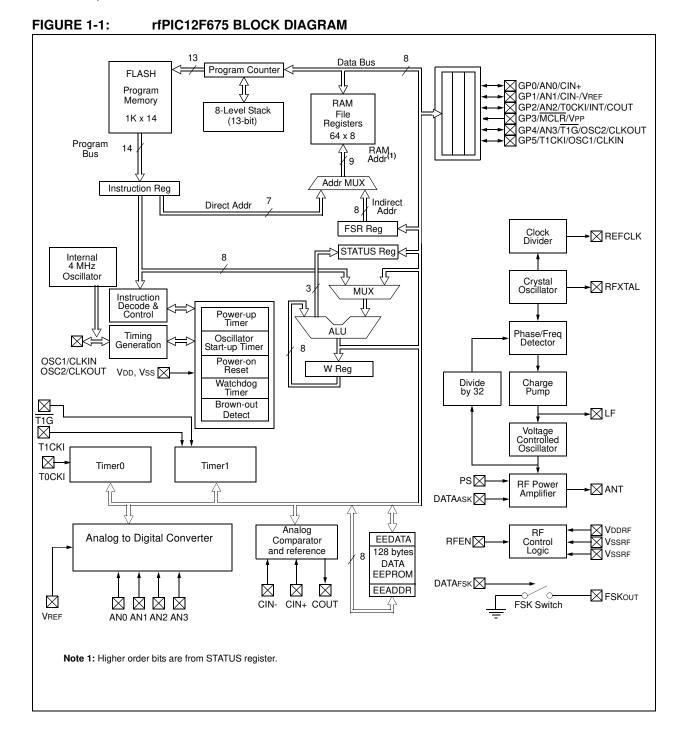

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the rfPIC12F675. Additional information may be found in the *PICmicro<sup>TM</sup> Mid-Range Reference Manual* (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this Data Sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The rfPIC12F675 comes in a 20-pin SSOP package. Figure 1-1 shows a block diagram of the rfPIC12F675 device. Table 1-1 shows the pinout description.

#### **TABLE 1-1:** rfPIC12F675 PINOUT BUFFER WEAK PIN DESCRIPTION PULL-UP IN OUT Vdd Direct Power Supply 1 General purpose I/O. Individually controlled interrupt-on-change. GP5 TTL CMOS Prog Individually enabled pull-up. T1CKI ST Timer1 clock 2 OSC1 Xtal Bias **XTAL** connection CLKIN ST External RC network or clock input General purpose I/O. Individually controlled interrupt-on-change. GP4 TTL CMOS Prog Individually enabled pull-up. T1G ST Timer1 gate 3 AN3 A/D Channel 3 input Analog \_ \_ OSC2 Xtal **XTAL** connection Bias CLKOUT CMOS Tosc/4 reference clock \_\_\_\_ \_\_\_\_ General purpose input. Individually controlled interrupt-on-GP3 TTL change. 4 MCLR ST No Master Clear Reset \_\_\_\_ VPP ΗV \_\_\_\_ Programming voltage 5 RFXTAL Xtal Xtal Bias **RF** Crystal RFEN 6 TTI **RF** Enable Reference Clock/4 Output (on rfPIC12F675K/F) 7 REFCLK CMOS Reference Clock/8 Output (on rfPIC12F675H) PS 8 Power Select Analog Bias \_\_\_\_ RF Power Supply 9 VDDRF Direct 10 Direct **RF Ground Reference** VSSRF 11 ANT OD RF power amp output to antenna 12 VSSRF Direct **RF Ground Reference** \_\_\_\_ LF Loop Filter 13 Analog Analog 14 TTL ASK modulation data DATAASK 15 DATAFSK TTL FSK modulation data \_ 16 **FSKOUT** OD FSK output to modulate reference crystal \_\_\_\_ General purpose I/O. Individually controlled interrupt-on-change. GP2 ST CMOS Prog Individually enabled pull up. AN2 Analog A/D Channel 2 input 17 COUT CMOS Comparator output \_ \_\_\_\_ **T0CKI** ST External clock for Timer0 INT ST External interrupt \_\_\_\_ \_ General purpose I/O. Individually controlled interrupt-on-change. GP1 TTL CMOS Prog Individually enabled pull-up. AN1 Analog A/D Channel 1 input \_ \_ 18 CIN-Analog Comparator input - negative \_ \_\_\_\_ VREF External voltage reference Analog \_\_\_ \_ **ICSPCLK** ST Serial programming clock General purpose I/O. Individually controlled interrupt-on-change. GP0 TTL CMOS Prog Individually enabled pull-up. AN0 A/D Channel 0 input Analog 19 CIN+ Comparator input - positive Analog \_ ICSPDAT TTL CMOS Serial Programming Data I/O 20 Vss Direct Ground reference TTL = TTL input buffer, ST = Schmitt Trigger input buffer, OD = Open Drain output Legend:

### 2.0 MEMORY ORGANIZATION

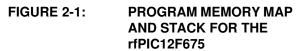

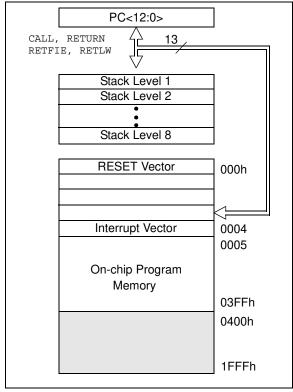

#### 2.1 Program Memory Organization

The rfPIC12F675 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h - 03FFh) for the rfPIC12F675 devices is physically implemented. Accessing a location above these boundaries will cause a wrap around within the first 1K x 14 space. The RESET vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

#### 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose registers and the Special Function registers. The Special Function registers are located in the first 32 locations of each bank. Register locations 20h-5Fh are General Purpose registers, implemented as static RAM and are mapped across both banks. All other RAM is unimplemented and returns '0' when read. RP0 (STATUS<5>) is the bank select bit.

- RP0 = 0 Bank 0 is selected

- RP0 = 1 Bank 1 is selected

- Note: The IRP and RP1 bits STATUS<7:6> are reserved and should always be maintained as '0's.

- 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $64 \times 8$  in the rfPIC12F675 devices. Each register is accessed, either directly or indirectly, through the File Select Register FSR (see Section 2.4).

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE rfPIC12F675

| Indirect addr. <sup>(1)</sup> | 00h | Indirect addr.(1)     | 801 |

|-------------------------------|-----|-----------------------|-----|

| TMR0                          | 01h | OPTION_REG            | 811 |

| PCL                           | 02h | PCL                   | 821 |

| STATUS                        | 03h | STATUS                | 831 |

| FSR                           | 04h | FSR                   | 84  |

| GPIO                          | 05h | TRISIO                | 85ł |

| ano                           | 06h | 111010                | 86  |

|                               | 07h |                       | 87ł |

|                               | 08h |                       | 88  |

|                               | 09h |                       | 89ł |

| PCLATH                        | 0Ah | PCLATH                | 8A  |

| INTCON                        | 0Bh | INTCON                | 8B  |

| PIR1                          | 0Ch | PIE1                  | 8C  |

| FINI                          | 0Dh | FIEI                  | 8D  |

|                               |     | DOON                  | -   |

| TMR1L                         | 0Eh | PCON                  | 8E  |

| TMR1H                         | 0Fh | 000041                | 8Fł |

| T1CON                         | 10h | OSCCAL                | 90ł |

|                               | 11h |                       | 91ł |

|                               | 12h |                       | 92ł |

|                               | 13h |                       | 93ł |

|                               | 14h |                       | 94ł |

|                               | 15h | WPU                   | 95ł |

|                               | 16h | IOC                   | 96ł |

|                               | 17h |                       | 97ł |

|                               | 18h |                       | 98ł |

| CMCON                         | 19h | VRCON                 | 99ł |

|                               | 1Ah | EEDATA                | 9AI |

|                               | 1Bh | EEADR                 | 9Bl |

|                               | 1Ch | EECON1                | 9C  |

|                               | 1Dh | EECON2 <sup>(1)</sup> | 9D  |

| ADRESH                        | 1Eh | ADRESL                | 9EI |

| ADCON0                        | 1Fh | ANSEL                 | 9Fł |

| General                       | 20h |                       | AOI |

| Purpose                       |     | accesses              |     |

| Registers                     |     | 20h-5Fh               |     |

| 64 Bytes                      |     |                       |     |

|                               | 5Fh |                       | DF  |

|                               | 60h |                       | EOI |

| Deal                          | 7Fh | Declar                | FFI |

| Bank 0                        |     | Bank 1                |     |

| Address | Name                | Bit 7              | Bit 6                                                             | Bit 5         | Bit 4          | Bit 3            | Bit 2          | Bit 1         | Bit 0  | Value on<br>POR, BOD | Page  |

|---------|---------------------|--------------------|-------------------------------------------------------------------|---------------|----------------|------------------|----------------|---------------|--------|----------------------|-------|

| Bank 0  |                     |                    |                                                                   |               |                |                  |                |               |        |                      |       |

| 00h     | INDF <sup>(1)</sup> | Addressing         | ressing this Location uses Contents of FSR to Address Data Memory |               |                |                  |                |               |        |                      | 16,63 |

| 01h     | TMR0                | Timer0 Mod         | lule's Registe                                                    | er            |                |                  |                |               |        | XXXX XXXX            | 25    |

| 02h     | PCL                 | Program Co         | ounter's (PC)                                                     | Least Signifi | cant Byte      |                  |                |               |        | 0000 0000            | 15    |

| 03h     | STATUS              | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup>                                                | RP0           | то             | PD               | Z              | DC            | С      | 0001 1xxx            | 9     |

| 04h     | FSR                 | Indirect Dat       | a Memory Ac                                                       | dress Pointe  | er             |                  |                | •             |        | xxxx xxxx            | 16    |

| 05h     | GPIO                | —                  | —                                                                 | GPIO5         | GPIO4          | GPIO3            | GPIO2          | GPIO1         | GPIO0  | xx xxxx              | 17    |

| 06h     | _                   | Unimpleme          | nted                                                              | •             | •              | •                |                | •             |        | —                    | _     |

| 07h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | _                    | —     |

| 08h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 09h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 0Ah     | PCLATH              | _                  | —                                                                 | _             | Write Buffer   | for Upper 5      | bits of Progra | am Counter    |        | 0 0000               | 15    |

| 0Bh     | INTCON              | GIE                | PEIE                                                              | T0IE          | INTE           | GPIE             | T0IF           | INTF          | GPIF   | 0000 0000            | 11    |

| 0Ch     | PIR1                | EEIF               | ADIF                                                              | _             | _              | CMIF             | _              | -             | TMR1IF | 0000                 | 13    |

| 0Dh     | —                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | _                    | —     |

| 0Eh     | TMR1L               | Holding Reg        | gister for the                                                    | Least Signifi | cant Byte of t | he 16-bit Tim    | ier1           |               |        | xxxx xxxx            | 28    |

| 0Fh     | TMR1H               | Holding Reg        | gister for the                                                    | Most Signific | ant Byte of th | ne 16-bit Time   | er1            |               |        | xxxx xxxx            | 28    |

| 10h     | T1CON               | _                  | TMR1GE                                                            | T1CKPS1       | T1CKPS0        | T1OSCEN          | T1SYNC         | TMR1CS        | TMR10N | -000 0000            | 30    |

| 11h     | _                   | Unimpleme          | nted                                                              | •             | •              | •                |                | •             |        | _                    | _     |

| 12h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | _                    | _     |

| 13h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | _                    | _     |

| 14h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | _                    | _     |

| 15h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 16h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 17h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 18h     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 19h     | CMCON               | —                  | COUT                                                              | _             | CINV           | CIS              | CM2            | CM1           | CM0    | -0-0 0000            | 33    |

| 1Ah     | _                   | Unimpleme          | nted                                                              |               |                |                  |                | •             |        | —                    | _     |

| 1Bh     | -                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | _     |

| 1Ch     | -                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | —     |

| 1Dh     | _                   | Unimpleme          | nted                                                              |               |                |                  |                |               |        | —                    | —     |

| 1Eh     | ADRESH              | Most Signifi       | cant 8 bits of                                                    | the Left Shif | ted A/D Resi   | ult or 2 bits of | the Right SI   | nifted Result |        | xxxx xxxx            | 40    |

| 1Fh     | ADCON0              | ADFM               | VCFG                                                              | _             | _              | CHS1             | CHS0           | GO/DONE       | ADON   | 00 0000              | 41,63 |

| TABLE 2-1: | SPECIAL | FUNCTION REGISTE | ERS SUMMARY |

|------------|---------|------------------|-------------|

**Note 1:** This is not a physical register.

2: These bits are reserved and should always be maintained as '0'.

| Address | Name                  | Bit 7              | Bit 6                                                              | Bit 5         | Bit 4        | Bit 3           | Bit 2          | Bit 1         | Bit 0   | Value on<br>POR, BOD | Page  |

|---------|-----------------------|--------------------|--------------------------------------------------------------------|---------------|--------------|-----------------|----------------|---------------|---------|----------------------|-------|

| Bank 1  |                       |                    |                                                                    |               |              |                 |                |               |         |                      |       |

| 80h     | INDF <sup>(1)</sup>   | Addressing         | dressing this Location uses Contents of FSR to Address Data Memory |               |              |                 |                |               |         |                      |       |

| 81h     | OPTION_REG            | GPPU               | INTEDG                                                             | TOCS          | TOSE         | PSA             | PS2            | PS1           | PS0     | 1111 1111            | 10,26 |

| 82h     | PCL                   | Program Co         | ounter's (PC)                                                      | Least Signifi | cant Byte    |                 |                |               |         | 0000 0000            | 15    |

| 83h     | STATUS                | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup>                                                 | RP0           | TO           | PD              | Z              | DC            | С       | 0001 1xxx            | 9     |

| 84h     | FSR                   | Indirect Dat       | a Memory Ac                                                        | dress Pointe  | er           |                 |                |               | •       | xxxx xxxx            | 16    |

| 85h     | TRISIO                | —                  | —                                                                  | TRISIO5       | TRISIO4      | TRISIO3         | TRISIO2        | TRISIO1       | TRISIO0 | 11 1111              | 17    |

| 86h     | —                     | Unimpleme          | nted                                                               | •             | •            | •               |                | •             |         | —                    | —     |

| 87h     | _                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | _     |

| 88h     | _                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | _     |

| 89h     | -                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | _                    | —     |

| 8Ah     | PCLATH                | _                  | _                                                                  | _             | Write Buffer | for Upper 5     | bits of Progra | am Counter    |         | 0 0000               | 15    |

| 8Bh     | INTCON                | GIE                | PEIE                                                               | T0IE          | INTE         | GPIE            | T0IF           | INTF          | GPIF    | 0000 0000            | 11    |

| 8Ch     | PIE1                  | EEIE               | ADIE                                                               | _             | _            | CMIE            | _              | _             | TMR1IE  | 0000                 | 12    |

| 8Dh     | -                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | _                    | —     |

| 8Eh     | PCON                  | _                  | —                                                                  | —             | —            | —               |                | POR           | BOD     | 0x                   | 14    |

| 8Fh     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 90h     | OSCCAL                | CAL5               | CAL4                                                               | CAL3          | CAL2         | CAL1            | CAL0           | —             | _       | 1000 00              | 14    |

| 91h     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 92h     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 93h     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 94h     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 95h     | WPU                   | —                  |                                                                    | WPU5          | WPU4         | -               | WPU2           | WPU1          | WPU0    | 11 -111              | 18    |

| 96h     | IOC                   | —                  | —                                                                  | IOC5          | IOC4         | IOC3            | IOC2           | IOC1          | IOC0    | 00 0000              | 19    |

| 97h     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 98h     | —                     | Unimpleme          | nted                                                               |               |              |                 |                |               |         | —                    | —     |

| 99h     | VRCON                 | VREN               | —                                                                  | VRR           | -            | VR3             | VR2            | VR1           | VR0     | 0-0- 0000            | 38    |

| 9Ah     | EEDATA                | Data EEPR          | OM Data Reg                                                        | gister        |              |                 |                |               |         | 0000 0000            | 45    |

| 9Bh     | EEADR                 | _                  | Data EEPR                                                          | OM Address    | Register     |                 |                |               |         | -000 0000            | 45    |

| 9Ch     | EECON1                | _                  | _                                                                  | _             | _            | WRERR           | WREN           | WR            | RD      | x000                 | 46    |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM C           | ontrol Regist                                                      | er 2          |              |                 |                |               |         |                      | 46    |

| 9Eh     | ADRESL                | Least Signif       | icant 2 bits o                                                     | f the Left Sh | fted A/D Res | ult of 8 bits o | r the Right S  | hifted Result |         | XXXX XXXX            | 40    |

| 9Fh     | ANSEL                 | _                  | ADCS2                                                              | ADCS1         | ADCS0        | ANS3            | ANS2           | ANS1          | ANS0    | -000 1111            | 42,63 |

#### TABLE 2-1: SPECIAL FUNCTION REGISTERS SUMMARY (CONTINUED)

**Note 1:** This is not a physical register.

2: These bits are reserved and should always be maintained as '0'.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- · the arithmetic status of the ALU

- · the RESET status

- the bank select bits for data memory (SRAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any STATUS bits. For other instructions not affecting any STATUS bits, see the "Instruction Set Summary".

- Note 1: Bits IRP and RP1 (STATUS<7:6>) are not used by the rfPIC12F675 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and <u>Digit</u> Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

|       | Reserved                  | Reserved                                                                                                               | R/W-0                         | R-1                  | R-1           | R/W-x                                        | R/W-x        | R/W-x |  |  |  |

|-------|---------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|---------------|----------------------------------------------|--------------|-------|--|--|--|

|       | IRP                       | RP1                                                                                                                    | RP0                           | TO                   | PD            | Z                                            | DC           | С     |  |  |  |

|       | bit 7                     |                                                                                                                        |                               |                      |               |                                              |              | bit 0 |  |  |  |

|       |                           |                                                                                                                        |                               |                      |               |                                              |              |       |  |  |  |

| bit 7 | IRP: This b               | oit is reserve                                                                                                         | d and shoul                   | d be mainta          | ined as '0'   |                                              |              |       |  |  |  |

| bit 6 | RP1: This                 | <b>RP1:</b> This bit is reserved and should be maintained as '0'                                                       |                               |                      |               |                                              |              |       |  |  |  |

| bit 5 | 1 = Bank 1                | <b>RP0:</b> Register Bank Select bit (used for direct addressing)<br>1 = Bank 1 (80h - FFh)<br>0 = Bank 0 (00h - 7Fh)  |                               |                      |               |                                              |              |       |  |  |  |

| bit 4 | 1 = After p               | <b>TO:</b> Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred |                               |                      |               |                                              |              |       |  |  |  |

| bit 3 |                           | -down bit<br>ower-up or b<br>cution of the                                                                             |                               |                      | n             |                                              |              |       |  |  |  |

| bit 2 |                           | sult of an ari<br>sult of an ari                                                                                       |                               |                      |               | D                                            |              |       |  |  |  |

| bit 1 | For borrow<br>1 = A carry | arry/borrow<br>, the polarity<br>-out from th<br>ry-out from t                                                         | v is reversed<br>e 4th low or | l.<br>der bit of the | e result occu | instructions)<br>rred                        |              |       |  |  |  |

| bit 0 | 1 = A carry               | prrow bit (AD<br>-out from th<br>ry-out from t                                                                         | e Most Sign                   | ificant bit of       | the result or | curred                                       |              |       |  |  |  |

|       | Note:                     | complemen                                                                                                              | t of the sec                  | ond operan           | d. For rotate | on is execut<br>e (RRF, RLF)<br>e source reg | instructions | •     |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

© 2003-2013 Microchip Technology Inc.

#### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- n = Value at POR

- TMR0/WDT prescaler

- External GP2/INT interrupt

- TMR0

- Weak pull-ups on GPIO

### REGISTER 2-2: OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|         | R/W-1       | R/W-1                                                                                                                            | R/W-1                                                       | R/W-1                                                                     | R/W-1         | R/W-1      | R/W-1          | R/W-1 |  |  |  |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------|---------------|------------|----------------|-------|--|--|--|

|         | GPPU        | INTEDG                                                                                                                           | TOCS                                                        | TOSE                                                                      | PSA           | PS2        | PS1            | PS0   |  |  |  |

|         | bit 7       |                                                                                                                                  |                                                             |                                                                           |               |            |                | bit 0 |  |  |  |

| bit 7   | 1 = GPIO    | PIO Pull-up E<br>pull-ups are<br>pull-ups are                                                                                    | disabled                                                    | individual po                                                             | rt latch valu | es         |                |       |  |  |  |

| bit 6   | 1 = Interru | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of GP2/INT pin<br>0 = Interrupt on falling edge of GP2/INT pin |                                                             |                                                                           |               |            |                |       |  |  |  |

| bit 5   | 1 = Transit | R0 Clock So<br>tion on GP2/<br>al instruction                                                                                    | T0CKI pin                                                   |                                                                           |               |            |                |       |  |  |  |

| bit 4   | 1 = Increm  | -                                                                                                                                | -to-low trans                                               | bit<br>sition on GP2<br>sition on GP2                                     | •             |            |                |       |  |  |  |

| bit 3   | 1 = Presca  | caler Assigr<br>aler is assigr<br>aler is assigr                                                                                 | ned to the W                                                | /DT<br>MER0 modu                                                          | lle           |            |                |       |  |  |  |

| bit 2-0 | PS2:PS0:    | Prescaler R                                                                                                                      | ate Select b                                                | oits                                                                      |               |            |                |       |  |  |  |

|         | l           | Bit Value T                                                                                                                      | MR0 Rate                                                    | WDT Rate                                                                  |               |            |                |       |  |  |  |

|         | -           | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                             | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |               |            |                |       |  |  |  |

|         | Legend:     |                                                                                                                                  |                                                             |                                                                           |               |            |                |       |  |  |  |

|         | R = Reada   | able bit                                                                                                                         | W = V                                                       | Vritable bit                                                              | U = Unin      | nplemented | bit, read as ' | 0'    |  |  |  |

| Note: | To achieve a 1:1 prescaler assignment for |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|

|       | TMR0, assign the prescaler to the WDT by  |  |  |  |  |  |  |

|       | setting PSA bit to '1' (OPTION<3>). See   |  |  |  |  |  |  |

|       | Section 4.4                               |  |  |  |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO port change and external GP2/INT pin interrupts.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### **REGISTER 2-3:** INTCON — INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh OR 8Bh)

|       | R/W-0                                                                                                                                    | R/W-0                                                             | R/W-0                       | R/W-0         | R/W-0         | R/W-0         | R/W-0         | R/W-0     |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------|---------------|---------------|---------------|---------------|-----------|--|--|--|

|       | GIE                                                                                                                                      | PEIE                                                              | T0IE                        | INTE          | GPIE          | T0IF          | INTF          | GPIF      |  |  |  |

|       | bit 7                                                                                                                                    |                                                                   |                             |               |               |               |               | bit 0     |  |  |  |

| bit 7 | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                            |                                                                   |                             |               |               |               |               |           |  |  |  |

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts |                                                                   |                             |               |               |               |               |           |  |  |  |

| bit 5 | <b>TOIE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                     |                                                                   |                             |               |               |               |               |           |  |  |  |

| bit 4 | 1 = Enable                                                                                                                               | /INT Externations the GP2/II<br>as the GP2/II                     | NT external                 | interrupt     |               |               |               |           |  |  |  |

| bit 3 | 1 = Enable                                                                                                                               | Change Int<br>s the GPIO<br>es the GPIO                           | port change                 | interrupt     |               |               |               |           |  |  |  |

| bit 2 | 1 = TMR0                                                                                                                                 | 0 Overflow l<br>register has<br>register did                      | overflowed                  | (must be cle  | eared in soft | ware)         |               |           |  |  |  |

| bit 1 | 1 = The GI                                                                                                                               | /INT Externa<br>P2/INT exter<br>P2/INT exter                      | nal interrupi               | t occurred (r |               | red in softwa | are)          |           |  |  |  |

| bit 0 | 1 = When a                                                                                                                               | Change Intention Change Intention<br>at least one<br>of the GP5:C | of the GP5:                 | GP0 pins ch   |               | (must be cl   | eared in soft | ware)     |  |  |  |

|       | Note 1:                                                                                                                                  | IOC registe                                                       | er must also                | be enabled    | to enable ar  | n interrupt-o | n-change.     |           |  |  |  |

|       | 2:                                                                                                                                       |                                                                   | set when 1<br>nitialized be |               |               | ER0 is unch   | anged on F    | RESET and |  |  |  |

|       | Legend:                                                                                                                                  |                                                                   |                             |               |               |               |               |           |  |  |  |

|       | R = Reada                                                                                                                                | ble bit                                                           | W = W                       | /ritable bit  | U = Unin      | nplemented    | bit, read as  | 0'        |  |  |  |

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

|         | R/W-0 F                                                                                                                       | R/W-0    | U-0          | U-0          | R/W-0        | U-0       | U-0          | R/W-0   |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------|----------|--------------|--------------|--------------|-----------|--------------|---------|--|--|

|         | EEIE                                                                                                                          | ADIE     | _            | —            | CMIE         | _         | _            | TMR1IE  |  |  |

|         | bit 7                                                                                                                         |          |              |              |              |           |              | bit 0   |  |  |

| bit 7   | <b>EEIE:</b> EE Write<br>1 = Enables th<br>0 = Disables th                                                                    | e EE wri | te complete  | interrupt    |              |           |              |         |  |  |

| bit 6   |                                                                                                                               |          |              |              |              |           |              |         |  |  |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                    |          |              |              |              |           |              |         |  |  |

| bit 3   | <b>CMIE:</b> Comparator Interrupt Enable bit<br>1 = Enables the comparator interrupt<br>0 = Disables the comparator interrupt |          |              |              |              |           |              |         |  |  |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                    |          |              |              |              |           |              |         |  |  |

| bit 0   | <b>TMR1IE:</b> TMR<br>1 = Enables th<br>0 = Disables th                                                                       | e TMR1   | overflow int | errupt       |              |           |              |         |  |  |

|         | Legend:                                                                                                                       |          |              |              |              |           |              |         |  |  |

|         | R = Readable                                                                                                                  | bit      | W = W        | /ritable bit | U = Unim     | plemented | bit, read as | ; '0'   |  |  |

|         | - n = Value at F                                                                                                              | POR      | '1' = B      | it is set    | '0' = Bit is | s cleared | x = Bit is   | unknown |  |  |

#### REGISTER 2-4: PIE1 — PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-5.

- n = Value at POR

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1 — PERIPHERAL INTERRUPT REGISTER 1 (ADDRESS: 0Ch)

| EN 2-5. |                                                                                                                                                      |                                                   |             |                                               | SIER I (A     | DDRESS.   |                |        |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------|-----------------------------------------------|---------------|-----------|----------------|--------|--|--|

|         | R/W-0                                                                                                                                                | R/W-0                                             | U-0         | U-0                                           | R/W-0         | U-0       | U-0            | R/W-0  |  |  |

|         | EEIF                                                                                                                                                 | ADIF                                              | _           | —                                             | CMIF          | _         |                | TMR1IF |  |  |

|         | bit 7                                                                                                                                                |                                                   |             |                                               |               |           |                | bit 0  |  |  |

| bit 7   | 1 = The wr                                                                                                                                           | ite operatior                                     | completed   | nterrupt Flag<br>(must be cle<br>mpleted or h | eared in soft | ,         |                |        |  |  |

| bit 6   | ADIF: A/D Converter Interrupt Flag bit<br>1 = The A/D conversion is complete (must be cleared in software)<br>0 = The A/D conversion is not complete |                                                   |             |                                               |               |           |                |        |  |  |

| bit 5-4 | Unimplem                                                                                                                                             | ented: Read                                       | d as '0'    |                                               |               |           |                |        |  |  |

| bit 3   | 1 = Compa                                                                                                                                            | nparator Inte<br>Irator input h<br>Irator input h | as changed  | l (must be cl                                 | eared in sof  | tware)    |                |        |  |  |

| bit 2-1 | Unimplem                                                                                                                                             | ented: Read                                       | d as '0'    |                                               |               |           |                |        |  |  |

| bit 0   | 1 = TMR1 I                                                                                                                                           | MR1 Overflo<br>register over<br>register did      | flowed (mus | st be cleared                                 | l in software | )         |                |        |  |  |

|         | Legend:                                                                                                                                              |                                                   |             |                                               |               |           |                |        |  |  |

|         | R = Reada                                                                                                                                            | ble bit                                           | W = W       | /ritable bit                                  | U = Unim      | plemented | bit, read as ' | 0'     |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON — POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

|       | —   | _   | —   | —   | _   | POR   | BOD   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR:** Power-on Reset STATUS bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

#### bit 0 **BOD**: Brown-out Detect STATUS bit

- 1 = No Brown-out Detect occurred

- 0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.7 OSCCAL Register

bit 7-2

bit 1-0

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

#### REGISTER 2-7: OSCCAL — OSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

| R/W-1                      | R/W-0                                                                                 | R/W-0  | R/W-0       | R/W-0    | R/W-0     | U-0            | U-0 |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------|--------|-------------|----------|-----------|----------------|-----|--|--|--|

| CAL5                       | CAL4                                                                                  | CAL3   | CAL2        | CAL1     | CAL0      | _              | _   |  |  |  |

| bit 7                      |                                                                                       |        |             |          |           |                | bit |  |  |  |

| 100000 = 0                 | 111111 = Maximum frequency<br>100000 = Center frequency<br>000000 = Minimum frequency |        |             |          |           |                |     |  |  |  |

| Unimplemented: Read as '0' |                                                                                       |        |             |          |           |                |     |  |  |  |

| Unimplem                   | chicu. nea                                                                            | 1 45 0 |             |          |           |                |     |  |  |  |

| Legend:                    |                                                                                       |        |             |          |           |                |     |  |  |  |

| •                          |                                                                                       |        | ritable bit | U = Unin | plemented | bit, read as ' | 0'  |  |  |  |

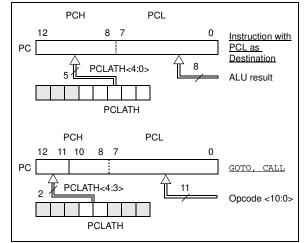

#### 2.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any RESET, the PC is cleared. Figure 2-3 shows the two situations for the loading of the PC. The upper example in Figure 2-3 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-3 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note *"Implementing a Table Read"* (AN556).

#### 2.3.2 STACK

The rfPIC12F675 Family has an 8-level deep x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

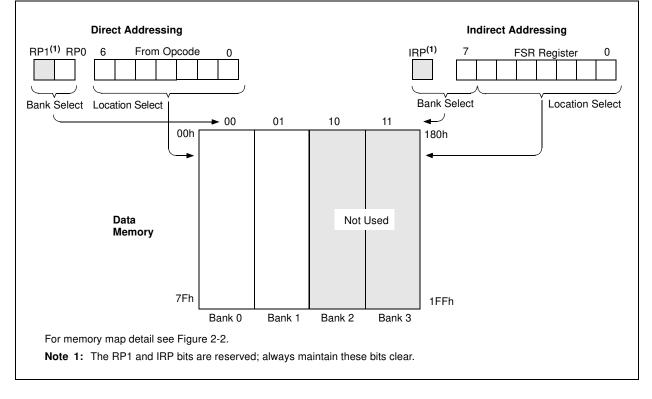

#### 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

|          | movlw | 0x20  | ; initialize pointer |

|----------|-------|-------|----------------------|

|          | movwf | FSR   | ;to RAM              |

| NEXT     | clrf  | INDF  | ;clear INDF register |

|          | incf  | FSR   | ; inc pointer        |

|          | btfss | FSR,4 | ;all done?           |

|          | goto  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

#### FIGURE 2-4: DIRECT/INDIRECT ADDRESSING rfPIC12F675

### 3.0 GPIO PORT

There are as many as six general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

| Note: | Additional information on I/O ports may be |

|-------|--------------------------------------------|

|       | found in the PIC Mid-Range Reference       |

|       | Manual (DS33023)                           |

#### 3.1 GPIO and the TRISIO Registers

GPIO is an 6-bit wide, bi-directional port. The corresponding data direction register is TRISIO. Setting a TRISIO bit (= 1) will make the corresponding GPIO pin an input (i.e., put the corresponding output driver in a Hi-impedance mode). Clearing a TRISIO bit (= 0) will make the corresponding GPIO pin an output (i.e., put the contents of the output latch on the selected pin). The exception is GP3, which is input only and its TRISIO bit will always read as '1'. Example 3-1 shows how to initialize GPIO.

Reading the GPIO register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch. GP3 reads '0' when MCLREN = 1.

The TRISIO register controls the direction of the GP pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISIO

register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

| Note: | The ANSEL (9Fh) and CMCON (19h)              |

|-------|----------------------------------------------|

|       | registers (9Fh) must be initialized to       |

|       | configure an analog channel as a digital     |

|       | input. Pins configured as analog inputs will |

|       | read '0'.                                    |

#### EXAMPLE 3-1: INITIALIZING GPIO

|       | -           |                        |

|-------|-------------|------------------------|

| bcf   | STATUS, RPO | ;Bank 0                |

| clrf  | GPIO        | ;Init GPIO             |

| movlw | 07h         | ;Set GP<2:0> to        |

| movwf | CMCON       | ;digital IO            |

| bsf   | STATUS, RPO | ;Bank 1                |

| clrf  | ANSEL       | ;Digital I/O           |

| movlw | 0Ch         | ;Set GP<3:2> as inputs |

| movwf | TRISIO      | ;and set GP<5:4,1:0>   |

|       |             | ;as outputs            |

|       |             |                        |

#### 3.2 Additional Pin Functions

Every GPIO pin on the rfPIC12F675 has an interrupton-change option and every GPIO pin, except GP3, has a weak pull-up option. The next two sections describe these functions.

#### 3.2.1 WEAK PULL-UP

Each of the GPIO pins, except GP3, has an individually configurable weak internal pull-up. Control bits WPUx enable or disable each pull-up. Refer to Register 3-3. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the GPPU bit (OPTION<7>).

#### REGISTER 3-1: GPIO — GPIO REGISTER (ADDRESS: 05h)

| U-0   | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | GPIO5 | GPIO4 | GPIO3 | GPIO2 | GPIO1 | GPIO0 |

| bit 7 | •   | •     | •     |       |       |       | bit 0 |

bit 7-6: Unimplemented: Read as '0'

bit 5-0: **GPIO<5:0>**: General Purpose I/O pin.

1 = Port pin is >VIH 0 = Port pin is <VIL

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

© 2003-2013 Microchip Technology Inc.

bit 7-6 bit 5-4

#### REGISTER 3-2: TRISIO — GPIO TRISTATE REGISTER (ADDRESS: 85h)

| U-0   | U-0 | R/W-x   | R/W-x   | R-1     | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     |     | TRISI05 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

bit 7-6: **Unimplemented**: Read as '0'

bit 5-0: **TRISIO<5:0>**: General Purpose I/O Tri-State Control bit

1 = GPIO pin configured as an input (tri-stated)

0 =GPIO pin configured as an output.

Note: TRISIO<3> always reads 1.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 3-3: WPU — WEAK PULL-UP REGISTER (ADDRESS: 95h)

| U-0                                  | U-0         | R/W-1        | R/W-1            | U-0 | R/W-1 | R/W-1 | R/W-1 |  |

|--------------------------------------|-------------|--------------|------------------|-----|-------|-------|-------|--|

|                                      | _           | WPU5         | WPU4             |     | WPU2  | WPU1  | WPU0  |  |

| bit 7                                |             |              |                  |     |       |       | bit 0 |  |

| Unimplemented: Read as '0'           |             |              |                  |     |       |       |       |  |

| WPU<5:4>: Weak Pull-up Register bit  |             |              |                  |     |       |       |       |  |

| WPU<5:4>                             | : Weak Pull | -up Reaister | <sup>r</sup> bit |     |       |       |       |  |

| <b>WPU&lt;5:4&gt;</b><br>1 = Pull-up |             | -up Register | <sup>r</sup> bit |     |       |       |       |  |

#### bit 3 Unimplemented: Read as '0'

- bit 2-0 WPU<2:0>: Weak Pull-up Register bit

- 1 = Pull-up enabled

- 0 = Pull-up disabled

- **Note 1:** Global GPPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISIO = 0).

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 3.2.2 INTERRUPT-ON-CHANGE

Each of the GPIO pins is individually configurable as an interrupt-on-change pin. Control bits IOC enable or disable the interrupt function for each pin. Refer to Register 3-4. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of GPIO. The 'mismatch' outputs of the last read are OR'd together to set, the GP Port Change Interrupt flag bit (GPIF) in the INTCON register. This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of GPIO. This will end the mismatch condition.

- b) Clear the flag bit GPIF.

A mismatch condition will continue to set flag bit GPIF. Reading GPIO will end the mismatch condition and allow flag bit GPIF to be cleared.

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the GPIF interrupt flag may not get set.

#### REGISTER 3-4: IOC — INTERRUPT-ON-CHANGE GPIO REGISTER (ADDRESS: 96h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

|       | —   | IOC5  | IOC4  | IOC3  | IOC2  | IOC1  | IOC0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOC<5:0>: Interrupt-on-Change GPIO Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

**Note 1:** Global interrupt enable (GIE) must be enabled for individual interrupts to be recognized.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 3.3 Pin Descriptions and Diagrams

Each GPIO pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the comparator or the A/D, refer to the appropriate section in this Data Sheet.

#### 3.3.1 GP0/AN0/CIN+

Figure 3-1 shows the diagram for this pin. The GP0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D

- · an analog input to the comparator

#### 3.3.2 GP1/AN1/CIN-/VREF

Figure 3-1 shows the diagram for this pin. The GP1 pin is configurable to function as one of the following:

- as a general purpose I/O

- an analog input for the A/D

- an analog input to the comparator

- a voltage reference input for the A/D

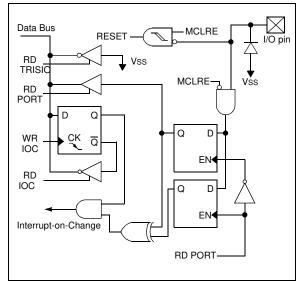

#### FIGURE 3-1: BLOCK DIAGRAM OF GP0 AND GP1 PINS

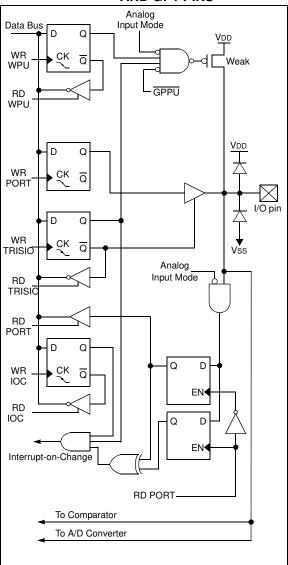

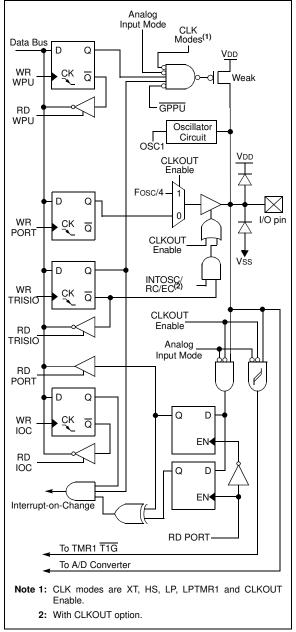

#### 3.3.3 GP2/AN2/T0CKI/INT/COUT

Figure 3-2 shows the diagram for this pin. The GP2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D

- · the clock input for TMR0

- · an external edge triggered interrupt

- · a digital output from the comparator

#### FIGURE 3-2: **BLOCK DIAGRAM OF GP2** Analog Input Mode Data Bus Q D Vdd WR CK Q Weak WPU GPPU RD WPU Analog COUT Input Mode Enable Vdd D Q Ţ WR СК Q PORT COUT $\mathbb{X}$ 0 I/O pin D Q WR CK Q TRISI Analog Input Mode RD TRISI ð RD POR Q D Q D WR CK Q IOC EN• RD IOC D Q ΕN Interrupt-on-Change **RD PORT** To TMR0 To INT

#### 3.3.4 GP3/MCLR/VPP

Figure 3-3 shows the diagram for this pin. The GP3 pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset

#### FIGURE 3-3: BLOCK DIAGRAM OF GP3

© 2003-2013 Microchip Technology Inc.

To A/D Converter

#### 3.3.5 GP4/AN3/T1G/OSC2/CLKOUT

Figure 3-4 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- · an analog input for the A/D

- a TMR1 gate input

- · a crystal/resonator connection

- · a clock output

#### FIGURE 3-4: **BLOCK DIAGRAM OF GP4**

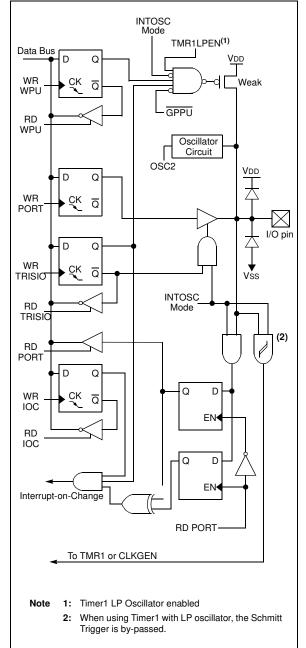

#### 3.3.6 GP5/T1CKI/OSC1/CLKIN

Figure 3-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- · a TMR1 clock input

- a crystal/resonator connection

- · a clock input

#### **BLOCK DIAGRAM OF GP5**