# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Wireless Power Receiver Compliant with WPC**

### **General Description**

The RT1650 is a wireless power receiver compliant with WPC V1.1 standard. The RT1650 integrates a synchronous full-bridge rectifier, a low dropout regulator, and a Micro Controller Unit (MCU) for control and communication. The device receives AC power from a WPC compatible wireless transmitter and provides output power up to 7.5W, which could be used as a power supply for a charger of mobile or consumer devices.

The MCU-based controller can support bi-direction channel communication including Frequency Shift Keying (FSK) demodulation for power signal from the transmitter and Amplitude Shift Keying (ASK) modulation for power signal to the transmitter. The RT1650 provides Foreign Object Detection (FOD) function to meet the requirement after WPC V1.1. It communicates with the transmitter for the received power to determine if a foreign object is present within the magnetic interface. This provides a higher level of safety.

The RT1650 provides a programmable dynamic rectifier voltage control function to improve power efficiency, a programmable power management control for maximum power delivery, a programmable current limit for suitable load setting, a programmable temperature setting with external NTC for thermoregulation, and proper protection functions such as UVLO, OVP, and OTP.

### **Features**

- Single-Chip WPC V1.1 Compliant Receiver

- Integrated Synchronous Rectifier Switch

- ► Support Output Power up to 7.5W

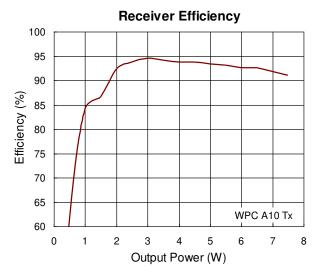

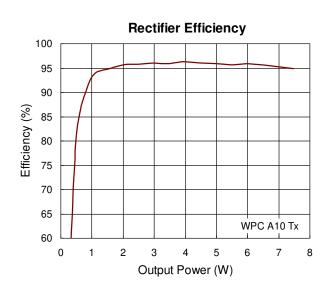

- ▶ High Rectifier Efficiency up to 96%

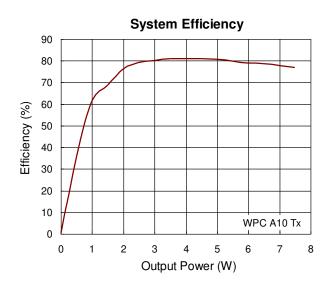

- ▶ High System Efficiency up to 80%

- Programmable Loading for Synchronous Rectifier Operation

- Programmable Dynamic Rectifier Voltage Control for Optimized Transient Response and Power Efficiency

- High Accurate Received Power Calculation for FOD Function

- ▶ 10-bit ADC for Voltage/Current Measurement

- ► Coil Power Loss Modeling for Optimized Compensation

- Adaptive Power Offset Compensation

- Low Quiescent Embedded 32-bit ARM Cortex-M0

MCU

- ▶ 32KB ROM/OTP, 1KB SRAM and 272B MTP

- Easy Tuning for Communication and Control Parameters

- Support Bi-direction Channel Communication

- ► FSK Demodulation for Power Signal from Wireless Power Transmitter

- ► ASK Modulation for Power Signal to Wireless Power Transmitter

- Programmable Temperature Control

- Programmable Charge Status Packet

- Support Alignment with Transmitter

- Support Enable, Charge Complete and Fault Control Inputs

- Receiver Controlled EPT Packet

- Over Current Limit

- Over Voltage Protection

- Thermal Shutdown

- CSP 3.0mm x 3.4mm 48B (Pitch = 0.4mm)

- Low Profile (0.5mm Max.)

### Applications

- WPC Compliant Receivers

- Cell Phones & Smart Phones

- Digital Cameras

- Power Banks

- Wireless Power Embedded Batteries

- Headsets

- Portable Media Players

- Hand-held Devices

### RICHTEK

### **Ordering Information**

RT1650 D Package Type WSC : WL-CSP-48B 3x3.4 (BSC)

#### Note :

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ► Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

RT1650 WSC YMDNN RT1650WSC : Product Number YMDNN : Date Code

### **Pin Configurations**

(TOP VIEW)

| (A1)         | A2          | (A3)          | A4           | A5           | A6            |

|--------------|-------------|---------------|--------------|--------------|---------------|

| BOOT2        |             | PGND          |              | PGND         | BOOT1         |

| (B1)<br>AC2  | (B2)<br>AC2 | (B3)<br>AC2   | (B4)<br>AC1  | (B5)<br>AC1  | (B6)<br>AC1   |

| AC2          | AC2         | AC2           | AC1          | AC1          | AC1           |

| (C1)<br>RECT | (C2)        | (C3)<br>RECT  | (C4)         | (C5)         | (C6)          |

| RECT         | RECT        | RECT          | RECT         | RECT         | COM1          |

| (D1)         | D2          | (D3)<br>OUT   | D4           | D5           | (D6)          |

| OUT          | OUT         | OUT           | OUT          | OUT          | CLMP1         |

| (E1)         | (E2)        | (E3)<br>NC    | (E4)         | (E5)         | (E6)          |

| GND          | NC          | NC            | VDD1         | VDD2         | COM2          |

| (F1)         | (F2)        | (F3)          | (F4)<br>VDD1 | (F5)<br>VDD2 | (F6)<br>CLMP2 |

| SCL          | SDA         | (F3)<br>GPIO  | VDD1         |              |               |

| (G1)<br>TS   | (G2)        | (G3)<br>MODE1 | G4<br>NC     | (G5)         | (G6)          |

| TS           | MODE0       |               | NC           | NC           | PGND          |

| (H1)<br>CHG  | (H2)        | (H3)<br>ADD   | (H4)         | (H5)         | (H6)          |

| CHG          | ADEN        | ADD           | GND          | GND          | PGND          |

WL-CSP-48B 3x3.4 (BSC)

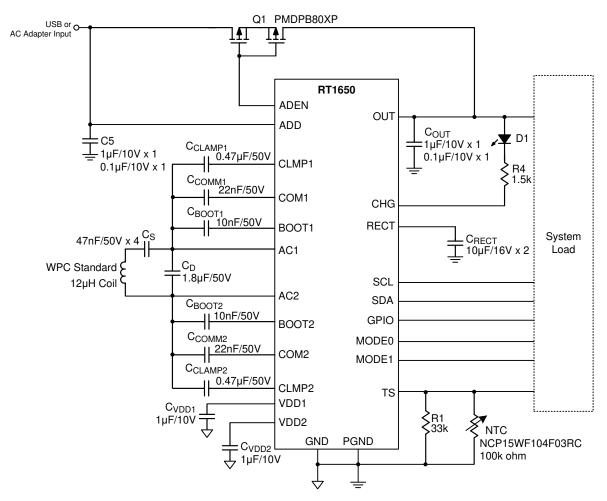

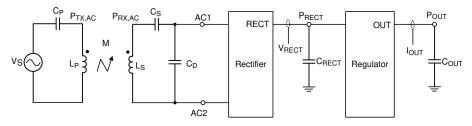

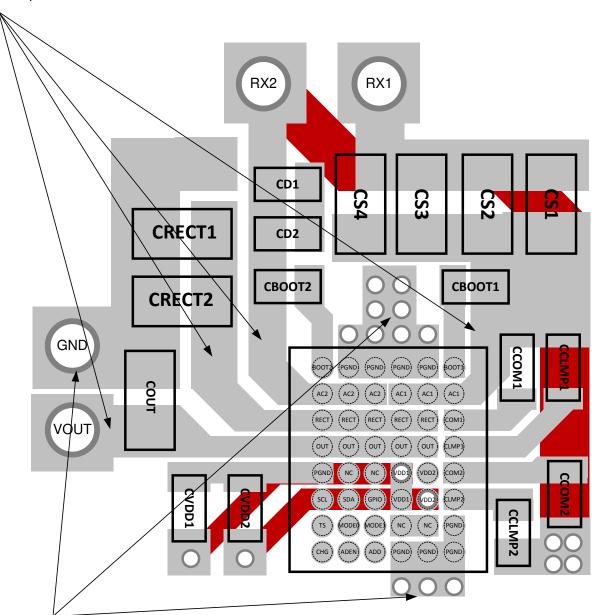

### **Typical Application Circuit**

Note : The component value and the maximum voltage rating is based on the WPC standard transmitter and 5V adapter application. The customer should modify it depend on the different design and application.

| Pin No.            | Pin Name | I/O | Pin Function                                                                                                      |  |  |  |

|--------------------|----------|-----|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| A1                 | BOOT2    | 0   | Bootstrap Supply for Driving the High-side FETs of Synchronous Rectifier.                                         |  |  |  |

| A6                 | BOOT1    | 0   | Connect a 10nF ceramic capacitor from BOOT1 to AC1 and from BOOT2 to AC2.                                         |  |  |  |

| A2 to A5<br>G6, H6 | PGND     |     | Power Ground.                                                                                                     |  |  |  |

| B1 to B3           | AC2      | I   | AC Bower Input from Bosoiver Coil                                                                                 |  |  |  |

| B4 to B6           | AC1      | I   | AC Power Input from Receiver Coil.                                                                                |  |  |  |

| C1 to C5           | RECT     | 0   | Output of Synchronous Rectifier. Connect a ceramic capacitor (10 $\mu$ F to 22 $\mu$ F) between this pin to PGND. |  |  |  |

| C6                 | COM1     | 0   | Open-Drain Output for Communication with Transmitter. Connect through                                             |  |  |  |

| E6                 | COM2     | 0   | a capacitor to AC1/AC2 for capacitive load modulation.                                                            |  |  |  |

| D1 to D5           | OUT      | 0   | Power Output of Regulator.                                                                                        |  |  |  |

### **Functional Pin Description**

| Pin No.          | Pin Name | I/O | Pin Function                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| D6               | CLMP1    | 0   | Open Drain Output for Over-voltage Clamp Protection. Connect a $0.47 \mu$ F ceramic capacitor between this pin to AC1/AC2. When the RECT voltage                                                                                                                                                                             |  |  |

| F6               | CLMP2    | 0   | exceeds 11.5V, both switches will be turned on and the capacitors will act as a low impedance to protect the IC from damage.                                                                                                                                                                                                 |  |  |

| E1, H4,<br>H5    | GND      |     | Analog Ground.                                                                                                                                                                                                                                                                                                               |  |  |

| E2, E3<br>G4, G5 | NC       |     | No Connection. Keep this pin as floating. Do not connect this pir power input or ground.                                                                                                                                                                                                                                     |  |  |

| E4, F4           | VDD1     | 0   | Voltage Supply for Internal Circuit. Connect a $1\mu F$ ceramic capacitor between this pin and GND.                                                                                                                                                                                                                          |  |  |

| E5, F5           | VDD2     | 0   | Voltage Supply for Internal Circuit. Connect a $1\mu F$ ceramic capacitor between this pin and GND.                                                                                                                                                                                                                          |  |  |

| F1               | SCL      | I   | I <sup>2</sup> C Compatible Series-Clock Input for internal register/MTP access.                                                                                                                                                                                                                                             |  |  |

| F2               | SDA      | I/O | I <sup>2</sup> C Compatible Series-Data Input/Output for internal register/MTP access.                                                                                                                                                                                                                                       |  |  |

| F3               | GPIO     | I/O | General Purpose Input/Output.                                                                                                                                                                                                                                                                                                |  |  |

| H1               | CHG      | 0   | Open-Drain Indicator Output. When the output regulator is enabled, this pin is pulled to low.                                                                                                                                                                                                                                |  |  |

| H2               | ADEN     | 0   | Enable Control Output for External P-FET connecting ADD and OUT. This pin is pulled to the higher of OUT and ADD when turning off the external FET. This voltage tracks approximately 4V below ADD when voltage is present at ADD.                                                                                           |  |  |

| НЗ               | ADD      | I   | Adapter Power Detection Input. Connect this pin to the adapter input.<br>When a voltage is applied to this pin, wireless power is disabled and<br>ADEN is pulled low. If not used, this pin should be connected to ground.                                                                                                   |  |  |

| G1               | TS       | I   | Temperature Sense Input. Connect a NTC between this pin and GND for temperature sensing. If the temperature sensing function is not desired, connect a $24k\Omega$ resistor to GND. Host side can control this pin to send end power transfer (EPT) to the transmitter: pull-low for EPT fault; pull-up for EPT termination. |  |  |

| G2               | MODE0    | I   | Operation Mode Control Input. These two pins are used to set power source operation mode.<br>[MODE0, MODE1] = [0, 0]. Auto mode. Adapter power prior.                                                                                                                                                                        |  |  |

| G3               | MODE1    | I   | [MODE0, MODE1] = [0, 1]. Wireless power mode.<br>[MODE0, MODE1] = [1, 0]. Adapter power mode and OTG mode<br>[MODE0, MODE1] = [1, 1]. Disable both adapter and wireless powers.                                                                                                                                              |  |  |

4

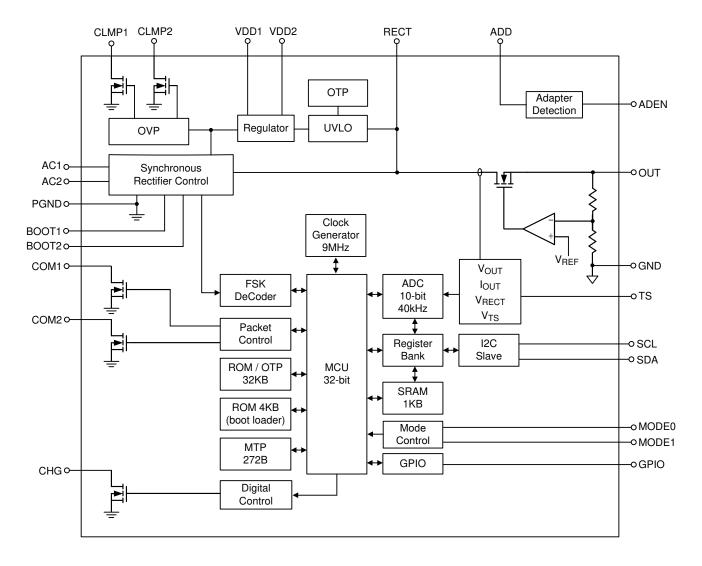

### **Function Block Diagram**

### Operation

### **MCU Based Digital Circuit**

RT1650 is a SoC (System on Chip) produce, which contains system level feature to control the communication with power transmitter, power calculation and GPIO. The firmware can be programmed into OTP (One Time Programmable) memory, so that user can discuss the features with RICHTEK, and custom some functions and GPIO behavior. To flexibly control whole functions, this chip embedded a MTP (Multiple Time Programmable) memory to save various setting and parameters. The external host can real-time read some power information via I<sup>2</sup>C interface.

### **OVP (Over Voltage Protection)**

The OVP function using to protect the abnormal power signal to let the RT1650 damaged. Once the VRECT exceeds 11.5V, this block will drive the CLAMP MOS to avoid the over voltage damage.

### **OTP (Over Temperature Protection)**

The OTP function shuts down the linear regulator operation when the junction temperature exceeds 150°C. Once the junction temperature cools down by around 20°C, the receiver will automatically resume operating.

### **Synchronous Rectifier Control**

This block detect the zero-cross of the AC1 and AC2 voltage then control the high-side and low-side MOS of the rectifier. RT1650 provide the Asynchronous, Half-synchronous and Full-synchronous control to optimize the rectifier efficiency.

### Mode Control

Mode control is using for the default mode, wireless mode, adapter mode and disable mode selection.

### Adapter Detection

In the default mode and adapter mode, adapter detection block control the ADEN pin to follow the VADD-5V to avoid the PMOS damaged.

#### **FSK Decoder**

This block analysis the frequency from the AC1 and AC2. This information can use for the FSK (Frequency Shift Key) decode to the WPC medium power standard. This information also can use for the power loss calculation of the resonant tank.

### Packet Control

This block build up the WPC standard 2kHz bi-phase encoding scheme with the asynchronous serial format and the packet structure. This block control the open-drain MOS to achieve the ASK (Amplitude Shift Key) communication.

6

# **RT1650**

| Absolute Maximum Ratings (Note 1)                                          |                |

|----------------------------------------------------------------------------|----------------|

| • Supply Input Voltage, AC1, AC2, RECT, COM1, COM2, OUT, CHG, CLMP1, CLMP2 | –0.3V to 20V   |

| Supply Input Voltage, ADD, ADEN                                            | –0.3V to 30V   |

| Supply Input Voltage, BOOT1, BOOT2                                         | –0.3V to 26V   |

| Supply Input Voltage, VDD1, VDD2, SDA, SCL, GPIO, TS                       | –0.3V to 6V    |

| Input Current, AC1, AC2                                                    | 2A(rms)        |

| Output Current, OUT                                                        | 2A             |

| Output Sink Current, CHG                                                   | 15mA           |

| Output Sink Current, COM1, COM2                                            | 1A             |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$                             |                |

| • WL-CSP-48B 3x3.4                                                         | 3.67W          |

| Package Thermal Resistance (Note 2)                                        |                |

| • WL-CSP-48B 3x3.4, θ <sub>JA</sub>                                        | 27.2°C/W       |

| Lead Temperature (Soldering, 10 sec.)                                      | 260°C          |

| Junction Temperature                                                       | 150°C          |

| Storage Temperature Range                                                  | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                |                |

| HBM (Human Body Model)                                                     | 2kV            |

| MM (Machine Model)                                                         | 200V           |

| Recommended Operating Conditions                                           |                |

| Recommended Operating Conditions (Note 4)                                  | 5)/ to 10)/    |

| Supply Input Voltage Range, RECT                                           |                |

| Input Current, RECT                                                        | 1.3A           |

| Output Current, OUT        | - 1.5A           |

|----------------------------|------------------|

| Sink Current, ADEN         | - 1mA            |

| Sink Current, COM          | - 500mA          |

| Ambient Temperature Range  | - –40°C to 85°C  |

| Junction Temperature Range | - –40°C to 125°C |

### **Electrical Characteristics**

(T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter                               | Symbol     | Test Conditions                           | Min | Тур  | Мах | Unit |

|-----------------------------------------|------------|-------------------------------------------|-----|------|-----|------|

| Input                                   |            |                                           |     |      |     |      |

| RECT Under-voltage Lockout<br>Threshold | VRECT_UVLO | $V_{RECT}$ Rising : 0V $\rightarrow$ 3V   | 2.6 | 2.7  | 2.8 | V    |

| RECT UVLO Hysteresis                    |            | VRECT Falling : $3V \rightarrow 0V$       |     | 250  |     | mV   |

| RECT Over-Voltage Threshold             |            | $V_{RECT}$ Rising : 7V $\rightarrow$ 13V  | 11  | 11.5 | 12  | V    |

| RECT Over-Voltage<br>Hysteresis         | VRECT_OVP  | $V_{RECT}$ Falling : 13V $\rightarrow$ 7V |     | 150  |     | mV   |

|                                                                                          | 1                    | 1                                 |      | 1    |      |      |

|------------------------------------------------------------------------------------------|----------------------|-----------------------------------|------|------|------|------|

| Parameter                                                                                | Symbol               | Test Conditions                   | Min  | Тур  | Мах  | Unit |

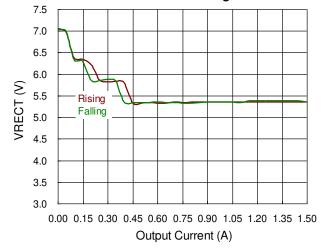

| Dynamic VRECT Setting-1                                                                  | VRECT_SET1           | (Note 5)                          |      | 7    |      |      |

| Dynamic VRECT Setting-2                                                                  | VRECT_SET2           | (Note 5)                          |      | 6.3  |      | V    |

| Dynamic VRECT Setting-3                                                                  | VRECT_SET3           | (Note 5)                          |      | 5.8  |      |      |

| Dynamic VRECT Setting-4                                                                  | VRECT_SET4           | (Note 5)                          |      | 5.3  |      | V    |

| IOUT Hysteresis for Dynamic<br>VRECT Settings                                            | IOUT_TH_HYS          | (Note 5)                          |      | 5    |      | %    |

| RECT Quiescent Current                                                                   | lq                   |                                   |      | 8    |      | mA   |

| Regulator Output                                                                         |                      |                                   |      |      |      |      |

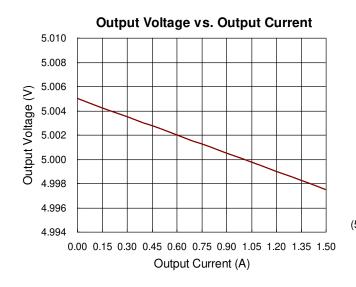

|                                                                                          |                      | IOUT = 1mA                        | 4.95 | 5    | 5.05 |      |

| OUT Regulation Voltage                                                                   | Vout_reg             | Iout = 1A                         | 4.94 | 4.99 | 5.04 | V    |

|                                                                                          |                      | IOUT = 1.5A                       | 4.90 | 4.96 | 5.02 |      |

| Regulator Drop-out Voltage                                                               | VDROP                | VRECT –VOUT, IOUT = 1A            |      | 100  | 200  | mV   |

| Output Current Limit Tolerance                                                           | IOUT_LIMIT           | louт =1.5A                        | -10  | -    | 10   | %    |

| OUT Leakage Current                                                                      | IOUT_LKG             | Disabled, V <sub>OUT</sub> = 5V   |      | 40   |      | μA   |

| Synchronous Rectifier                                                                    |                      | ·                                 |      |      |      |      |

| Programmable I <sub>OUT</sub> Threshold<br>Range to Enable<br>Half-Synchronous Rectifier |                      | I <sub>OUT</sub> Rising (Note 5)  | 50   |      | 500  |      |

| Programmable I <sub>OUT</sub> Threshold<br>Range to Enable<br>Full-Synchronous Rectifier | I <sub>SR_TH</sub>   | I <sub>OUT</sub> Rising (Note 5)  | 150  |      | 750  | mA   |

| Programmable I <sub>OUT</sub> Hysteresis<br>Range                                        |                      | I <sub>OUT</sub> Falling (Note 5) | 25   |      | 100  |      |

| Rectifier Diode Voltage in<br>Asynchronous Mode                                          | VDIODE               | I <sub>AC-VRECT</sub> = 250mA     |      | 0.65 |      | V    |

| TS Sense/Control Input                                                                   |                      |                                   |      |      |      |      |

| TS Thermoregulation<br>Threshold                                                         | VTS_REG              | V <sub>TS</sub> Falling (Note 5)  |      | 786  |      | mV   |

| Too-Hot Protection Threshold                                                             | V <sub>TS_HOT</sub>  | V <sub>TS</sub> Falling (Note 5)  |      | 278  |      | mV   |

| Too-Cold Protection Threshold                                                            | V <sub>TS_COLD</sub> | V <sub>TS</sub> Rising (Note 5)   |      | 1.82 |      | V    |

| TS Output Current                                                                        | Its                  |                                   |      | 60   |      | μA   |

| <b>Over-Temperature Protection</b>                                                       |                      |                                   |      |      |      |      |

| Over-Temperature Protection<br>Threshold                                                 | т.                   | (Note 5)                          |      | 150  |      | *    |

| Over-Temperature Protection<br>Hysteresis                                                | ΤJ                   | (Note 5)                          |      | 20   |      | °C   |

| CHG Indicator Output                                                                     |                      |                                   |      |      |      |      |

| CHG Low-Level Output<br>Voltage                                                          | V <sub>CHG_L</sub>   | I <sub>SINK</sub> = 5mA           |      |      | 100  | mV   |

| CHG Leakage Current when disabled                                                        | ICHG_LKG             | V <sub>CHG</sub> = 20V            |      |      | 1    | μA   |

|                                                                                          |                      |                                   |      |      |      |      |

| Parameter                                                                   | Symbol             | Test Conditions                         | Min      | Тур  | Мах  | Unit |

|-----------------------------------------------------------------------------|--------------------|-----------------------------------------|----------|------|------|------|

| COM Outputs                                                                 | -                  |                                         | <b>I</b> |      |      |      |

| COM1, COM2 N-FET<br>On-Resistance                                           | Ron_сом            | V <sub>RECT</sub> = 2.6V                |          | 0.7  |      | Ω    |

| COM1, COM2 Signaling<br>Frequency                                           | fсом               |                                         |          | 2    |      | kHz  |

| COM1, COM2 Leakage<br>Current                                               | ICOM_LKG           | $V_{COM1} = V_{COM2} = 20V$             |          |      | 1    | μA   |

| CLAMP Outputs                                                               |                    |                                         |          |      |      |      |

| CLMP1, CLMP2 N-FET<br>On-Resistance                                         | Ron_CLM            |                                         |          | 0.5  |      | Ω    |

| Adapter Power Enable Contro                                                 | bl                 |                                         |          |      |      |      |

| ADD Detection Voltage<br>Threshold                                          | Vadd               | $V_{ADD}$ Rising : 0V $\rightarrow$ 5V  | 3        | 3.6  | 4    | V    |

| ADD Detection Voltage<br>Hysteresis                                         | VADD               | $V_{ADD}$ Falling : 5V $\rightarrow$ 0V |          | 400  |      | mV   |

| ADD Input Leakage Current                                                   | Iadd_lkg           | $V_{ADD} = 5V$ , $V_{RECT} = 0V$        |          |      | 60   | μA   |

| Pull-up Resistance from ADEN<br>to OUT pin when Adapter<br>mode is disabled | R <sub>ADD</sub>   | $V_{ADD} = 0V, V_{OUT} = 5V$            |          | 275  | 350  | Ω    |

| ADD to ADEN Voltage when<br>Adapter Mode is Enabled                         | VAD_EN             | Vadd = 5V, Vadd – Vaden                 | 3        | 4.25 | 5    | V    |

| GPIO Input/Output                                                           |                    |                                         |          |      |      |      |

| GPIO Input Voltage<br>(Logic-Low)                                           | VIL                |                                         | 0        |      | 0.8  | V    |

| GPIO Input Voltage<br>(Logic-High)                                          | VIH                |                                         | 2        |      | 5    | V    |

| GPIO Output Voltage<br>(Logic-Low)                                          | Vol                |                                         |          |      | 0.4  | V    |

| GPIO Output Voltage<br>(Logic-High)                                         | Vон                |                                         | 2.6      | 3.3  | 3.6  | V    |

| Received Power (WPC Related                                                 | d Measureme        | ents)                                   |          |      | -    |      |

| Received Power Accuracy                                                     | P <sub>RX_AC</sub> | $I_{OUT} = 0A \text{ to } 1A  (Note 5)$ |          |      | 0.25 | W    |

| I <sup>2</sup> C Compatible Interface (N                                    | lote 5)            |                                         |          |      |      |      |

| Logic Input (SDA, SCL) Low<br>Level                                         | V <sub>SCL_L</sub> |                                         |          |      | 0.6  | V    |

| Logic Input (SDA, SCL) High<br>Level                                        | V <sub>SCL_H</sub> |                                         | 1.2      |      |      | V    |

| SCL Clock Frequency                                                         | fclk               |                                         | 10       |      | 400  | kHz  |

| Output Fall Time                                                            | tfl2COUT           |                                         |          |      | 250  | ns   |

| Bus Free Time Between<br>Stop/Start                                         | tbuf               |                                         | 1.3      |      |      | μs   |

| Hold Time Start Condition                                                   | thd_sta            |                                         | 0.6      |      |      | μS   |

| Setup Time for Start Condition                                              | tsu_sta            |                                         | 0.6      |      |      | μS   |

#### 9

# **RT1650**

| Parameter                                | Symbol               | Test Conditions                   | Min | Тур | Max | Unit |

|------------------------------------------|----------------------|-----------------------------------|-----|-----|-----|------|

| SCL Low Time                             | tLOW                 |                                   | 1.3 |     |     | μS   |

| SCL High Time                            | tнigн                |                                   | 0.6 |     |     | μS   |

| Data Setup Time                          | tsu_dat              |                                   | 100 |     |     | ns   |

| Data Hold Time                           | thd_dat              |                                   | 0   |     | 900 | ns   |

| Setup Time for Stop Condition            | tsu_sto              |                                   | 0.6 |     |     | μs   |

| Mode Control                             |                      |                                   |     |     |     |      |

| Logic Input (MODE0, MODE1)<br>Low Level  | V <sub>MODE_L</sub>  |                                   |     |     | 0.6 | V    |

| Logic Input (MODE0, MODE1)<br>High Level | V <sub>MODE_</sub> H |                                   | 1.2 |     |     | V    |

| Communication Interface                  |                      | ·                                 |     |     |     |      |

| FSK Modulation Frequency<br>Change       | ffsk                 | f <sub>OP</sub> = 175kHz (Note 5) | 3   | 5   | 7   | kHz  |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

Note 3. Devices are ESD sensitive. Handling precaution recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Specification is guaranteed by design and/or correlation with statistical process control.

Copyright © 2015 Richtek Technology Corporation. All rights reserved.

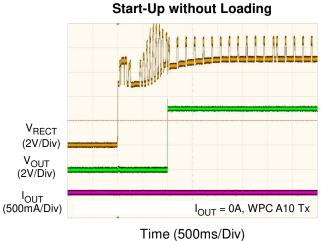

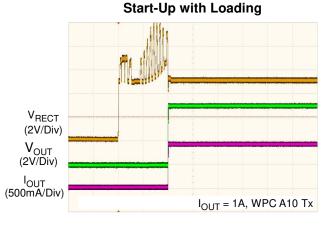

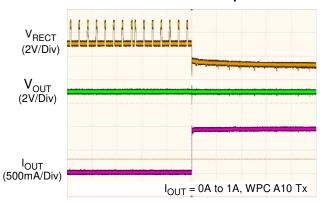

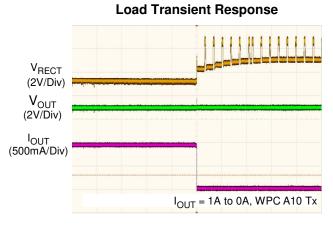

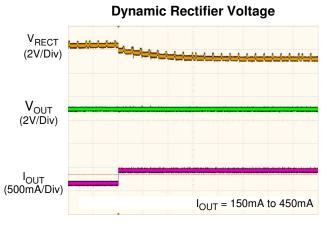

### **Typical Operating Characteristics**

Rectifier Voltage

Copyright © 2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Time (500ms/Div)

Time (500ms/Div)

Load Transient Response

Time (500ms/Div)

Time (500ms/Div)

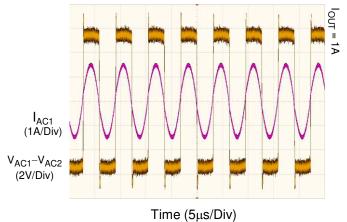

Synchronous Rectifier

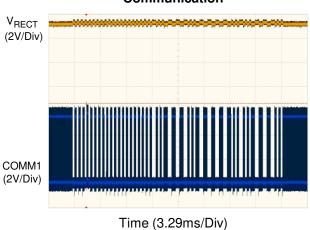

Communication

Time (100ms/Div)

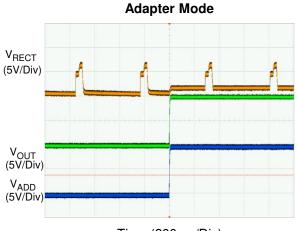

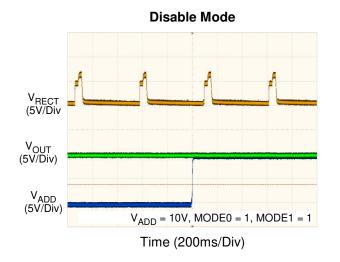

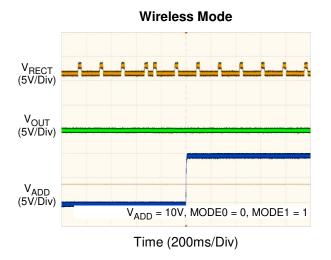

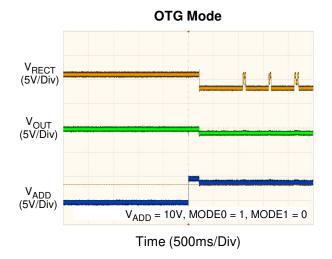

### **Default Mode**

**RT1650**

Time (200ms/Div)

Time (200ms/Div)

Copyright © 2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **Functional Description**

#### **Description of the Wireless Power System**

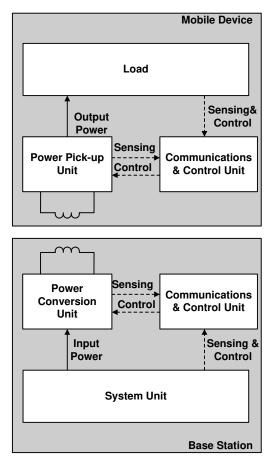

A wireless power system is composed by a power transmitter with one or more primary coils and a power receiver in a mobile system. Power transmitter will transfer power via a DC-to-AC inverter to drive a strong-coupled inductor to power receiver in a mobile device. The power transferred to power receiver is controlled by itself. The power receiver sends communication packets with control error voltage information to the power transmitter for power tracking. The bit rate of the communication link from receiver to transmitter is 2kbps.

Figure 1. Wireless Power System

#### Start-up

When the receiver is placed on the power pad, the receiver coil is inductively coupled to the magnetic flux generated by the coil in the power pad which consequently induces a voltage in the receiver coil. The internal synchronous rectifier feeds this voltage to the RECT pin which has the filter capacitor. The RT1650 communicates to the transmitter by switching on and off the COM FETs.

#### Power Transfer phases

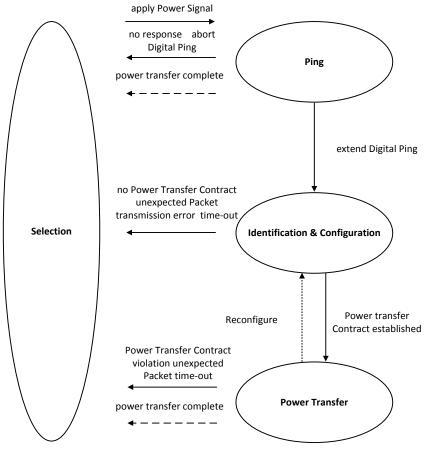

There are 4 power transfer phases for the WPC V1.1.

- Selection : As soon as the Power Transmitter applies a Power Signal, the Power Receiver shall enter the selection phase.

- Ping : The power Receiver should send the Digital Ping Packet to power Transmitter then into next phase. If not, the system shall revert to the Selection phase. The power Receiver also can send the End Power transfer Packet to stop the power Transmitter.

# **RT1650**

- Identification & Configuration : In this phase, the Power Receiver identifies the revision of the System Description Wireless Power Transfer the Power Receiver complies and configuration information such as the maximum power that the Power Receiver intends to provide at its output. The Power Transmitter uses this information to create a Power Transfer Contract.

- Power Transfer : In this phase, the Power Transmitter continues to provide power to the Power Receiver. The power Receiver sends the Control Error Packet for adjusting the Primary Cell current. The Power Transmitter stops to provide power when the Received Power Packet is too low to trigger the FOD function or End Power Transfer Packet is sent from power Receiver.

Figure 2. WPC V1.1 Low Power Transfer Phases

### **Micro Controller Unit**

#### Memory Map

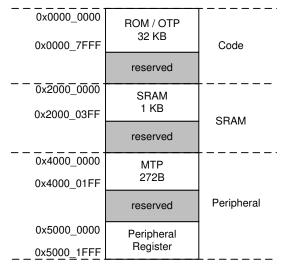

The memory mapping of MCU can be divided into 3 blocks, Code, SRAM and Peripheral. Each region has its recommend usage, and the memory access behavior could depend on which memory region you are accessing to.

#### Code

The size of the code region is 32KB. It is primarily used to store program code, including the exception vector table, which is a part of the program image. In OTP version of chip, the programmable user firmware will be stored in this area.

#### SRAM

The SRAM region starts from 0x2000 0000 and the total access size is 1KB. It's primarily used to store data, including stack.

#### Peripheral

There are 2 peripheral blocks in RT1650, MTP and peripheral registers. MTP (Multiple Time Programmable

Memory) is primarily used to save non-volatile user setting data and part of MTP store internal factory setting. User firmware can control some of chip hardware behavior via peripheral registers. It also could be an interface to communicate with external I<sup>2</sup>C via the registers.

### Figure 3. Memory Map

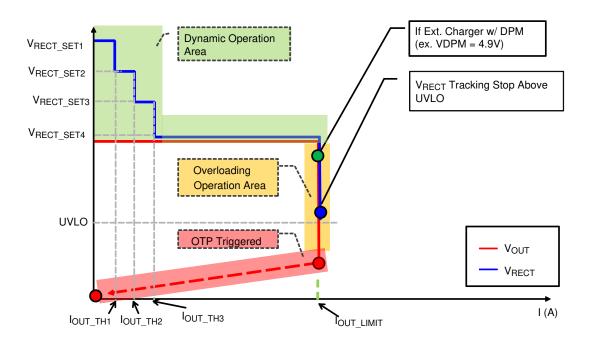

#### **Programmable Dynamic Rectifier Voltage Control**

The RT1650 provides a programmable Dynamic Rectifier Voltage Control function to optimize the transient response and power efficiency for applications. Table 1 and Figure 4 show an example to summarize how the rectifier behavior is dynamically adjusted based the registers  $V_{RECT SETx}[7:0]$  (x = 1 to 4), which are available to be programmed by users.

| , , , , , , , , , , , , , , , , , , , , |                          |  |  |  |

|-----------------------------------------|--------------------------|--|--|--|

| Output Current, IOUT                    | Rectifier Voltage Target |  |  |  |

| < IOUT_TH1                              | VRECT_SET1               |  |  |  |

| IOUT_TH1 to IOUT_TH2                    | VRECT_SET2               |  |  |  |

| lout_th2 to lout_th3                    | Vrect_set3               |  |  |  |

| > IOUT_TH3                              | VRECT_SET4               |  |  |  |

#### Table 1. Dynamic Rectifier Voltage Setting

Figure 4. Dynamic Rectifier Voltage vs. Output Current

Copyright @ 2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com DS1650-00

### **Thermal Management**

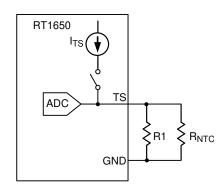

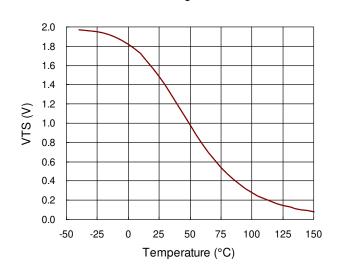

The RT1650 provides an external device thermal management function with an external NTC thermistor and a resistor connected between TS pin and GND pin shown as Figure 5. User can use this function to control the temperature of the coil, battery or other device. An internal current source ( $60\mu A$ ) is provided to the external NTC thermistor and generates a voltage at the TS pin. The TS voltage is detected and sent to the ADC converter for external device thermal manage control.

# Figure 5. NTC Circuit for Device Temperature Detection and Thermoregulation

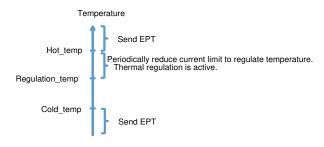

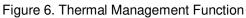

The thermal management function is shown as Figure 6. If the temperature is higher than Hot\_temp or lower than Cold\_temp threshold, the RT1650 will send the EPT to disable the power transfer. When the detected temperature increases and reaches the desired Regulation\_temp, RT1650 will decrease the current limit to reduce the output current to regulate the temperature. When the detected temperature is lower than the Regulation\_temp, the current limit will increase to the default value. This function is shown as Figure 7.

**RT1650**

Figure 7. Thermoregulation Control

The NTC thermistor should be placed as close as possible to the device such as battery or mobile device. The recommended NTC thermistor is NCP15WF104F03RC (tolerance ±1%,  $\beta$  = 4250k). The typical resistance of the NTC is 100k $\Omega$  at 25°C. The recommended resistance for R<sub>1</sub> is 33k $\Omega$  (±1%).The value of the NTC thermistor at the desired temperature can be estimated by the following equation.

$$R_{NTC\_Reg} = R_{O}e^{\beta \left(\frac{1}{T_{Reg}} - \frac{1}{T_{0}}\right)}$$

$$R_{eq} = \frac{R_{1} \times R_{NTC\_Reg}}{R_{1} + R_{NTC\_Reg}}$$

where  $T_{Reg}$  is the desired regulation temperature in degree Kelvin. R<sub>O</sub> is the nominal resistance at temperature T<sub>0</sub> and  $\beta$  is the temperature coefficient of the NTC thermistor. Req is the equivalent resistor of NTC thermistor in parallel with R<sub>1</sub>.

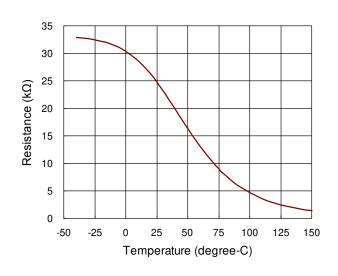

Figure 8 shows the equivalent resistance of the thermistor in parallel with  $R_1$  resistor varies with operating temperature. Figure 9 shows the VTS voltage with operating temperature. Customer can select the desire temperature and calculate the mapping data by the following equation.

#### Data = (VTS/2 x 1024)

If the thermal management function is not used ( $R_{NTC}$  = open), the resistor R1 = 24k $\Omega$  must be connected between the TS and GND pins

Figure 8. Equivalent Resistance for Temperature Sensing

### Communication

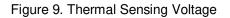

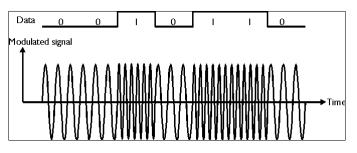

The RT1650 supports two communication modulations, Amplitude Shift Keying (ASK), Frequency Shift Keying (FSK), to communicate with the power transmitter. For ASK modulation, the RT1650 provides two integrated communication N-FETs which are connected to the COM1 and COM2 pins. These N-FETs are used for modulating the secondary load current which allows the RT1650 to communicate Control Error and configuration information to the transmitter. Figure 10 shows the RT1650 operating with capacitive load modulation. When the N-FETs are turned-on, there is effectively a capacitor connected between AC1 and AC2. The impedance seen by the coil will be reflected in the primary as a change in current.

Figure 10. Capacitive Load Modulation

The RT1650 supports FSK demodulation to receive the power signal from the transmitter shown as Figure 11. The change in frequency between high and low states is dependent on the operating frequency. The power transmitter should modulate the power signal at specific times during the Negotiation phase to avoid interrupting communication packets from the receiver. The FSK modulation scheme should be compliant with WPC Volume II V0.9.

Figure 11. FSK Modulation Power Signal

### Bit Encoding Scheme

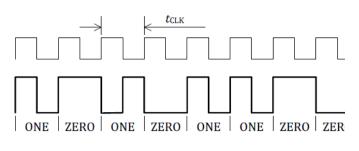

According to WPC protocol, the RT1650 uses a differential bi-phase encoding scheme to modulate data bits onto the Power Signal. The internal clock signal has a frequency 2kHz. The Receiver shall encode a ONE bit using two transitions in the Power Signal, such that the first transition coincides with the rising edge of the clock signal, and the second transition coincides with the falling edge of the clock signal. The Receiver shall encode a ZERO bit using a single transition in the Power Signal, which coincides with the rising edge of the clock signal. Figure 12 shows an example of the differential bi-phase encoding.

Figure 12. Example of the Differential Bi-phase Encoding

#### End Power Transfer Packet (WPC Header 0x02)

The End Power Transfer (EPT) packet is a special command for the RT1650 to request the transmitter to terminate power transfer. Table 2 specifies the reasons coulomb and their responding data field value. The condition column corresponds to the values sent by the RT1650 for a given reason.

| Reason              | Value | Condition                                               |

|---------------------|-------|---------------------------------------------------------|

| Unknown             | 0x00  | V <sub>ADD</sub> > 3.6V                                 |

| Charge<br>Complete  | 0x01  | From $I^2C$ , MODE0 = High<br>or V <sub>TS</sub> = High |

| Internal Fault      | 0x02  | T <sub>J</sub> > 150°C                                  |

| Over<br>Temperature | 0x03  | VTS < VTS_HOT, VTS ><br>VTS_COLD or VTS = Low           |

| Over Voltage        | 0x04  | Not Sent                                                |

| Over Current        | 0x05  | Not Sent                                                |

| Battery<br>Failure  | 0x06  | From I <sup>2</sup> C                                   |

| Reconfigure         | 0x07  | Not Sent                                                |

| No<br>Response      | 0x08  | V <sub>RECT</sub> target doesn't converge               |

#### Table 2. End Power Transfer (EPT) packet

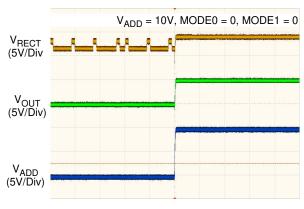

#### **Operation Mode Control**

The RT1650 provides 2 input pins for operating mode control. Table 4 shows an example of operating mode control for wireless power and external adapter power. In default mode, both MODE0 and MODE1 are low, the wireless power is enabled and the adapter power has a higher priority. The wireless power is the normally operation. Once the adapter power is detected, the wireless power will be turned off and the ADEN will be pulled low to turn on the external switch for connecting the adapter power to system load. When the MODE1 is pulled to high, the adapter power will be turned off by the external switch and enters wireless mode to allow wireless power operation only In adapter mode, the wireless power is turned off always and ADEN is pulled low to turn on external switch for adapter power In this mode, it allows an external charger operating in USB OTG mode to connect the OUT pin to power the USB at ADD pin. If both MODE0 and MODE1 pins are pulled to high, the wireless power and adapter power are disabled.

#### Table 4. Operation Mode Control

| Mode     | MODE0 | MODE1 | Wireless<br>Power | Adapter<br>Power | OTG     |

|----------|-------|-------|-------------------|------------------|---------|

| Default  | 0     | 0     | ON                | ON(*)            | OFF     |

| Wireless | 0     | 1     | ON                | OFF              | OFF     |

| Adapter  | 1     | 0     | OFF               | ON               | Allowed |

| Disable  | 1     | 1     | OFF               | OFF              | OFF     |

(\*)Note: If both adapter power and wireless power are present, adapter power is given higher priority.

### I<sup>2</sup>C Interface

The RT1650 provides  $I^2C$  interface to communicate with external host device. Besides OTP firmware programming and MTP setting programming can be approached through the  $I^2C$  interface, the external host can also communicate with the RT1650 to achieve more flexible applications. For example, the host can read the ADC information via the  $I^2C$  Interface. In addition, the  $I^2C$  is used to read the internal status and the power source is from the VRECT. If the wireless function disable or in the adapter mode, the  $I^2C$  can't be accessed. Table 3 shows the register definition. It's not fixed, the registers definition can be costumed by firmware. If user need to read other information via  $I^2C$ , please discuss with RICHTEK firmware engineer.

I<sup>2</sup>C Slave

0100010X (in binary format)

0x44 / 0x45 (hex format, include R/W bit)

| M | SB |   |   |   |   |   | LS  | ЗB |

|---|----|---|---|---|---|---|-----|----|

| 0 | 1  | 0 | 0 | 0 | 1 | 0 | R/W |    |

| Address | MSB | LSB | Name                         | Description                                                                                                   |  |

|---------|-----|-----|------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| 0x64    | 7   | 0   | Vrect                        | Vrect (4V to 8V), unit = 15.68mV                                                                              |  |

| 0x66    | 7   | 0   | Vout                         | Vout (3V to 6V), unit = 11.76mV                                                                               |  |

| 0x67    | 7   | 0   | lout                         | lout (0A to 2A), unit = 7.84mA                                                                                |  |

| 0x78    | 7   | 0   | last CE packet               | last CE packet                                                                                                |  |

| 0x79    | 7   | 0   | last RP packet               | last RP packet                                                                                                |  |

| 0x7A    | 7   | 0   | Received Power [7:0] (mW)    | low byte of Received Power (mW)                                                                               |  |

| 0x7B    | 6   | 0   | Received Power [14:8] (mW)   | high byte of Received Power (mW)                                                                              |  |

| 0x7B    | 7   | 7   | Received Power updating flag | 0: Received Power is valid<br>1: Received Power is updating, not valid                                        |  |

| 0x10    | 7   | 7   | Vout enable                  | 0: Vout is disable<br>1: Vout is enable                                                                       |  |

| 0x02    | 7   | 0   | freq_cnt[7:0]                | Frequency = 1000 / ((freq_cnt[13:0] *<br>0.11) /128) KHz                                                      |  |

| 0x03    | 5   | 0   | freq_cnt[13:8]               |                                                                                                               |  |

| 0x7C    | 3   | 0   | WPC phase status             | WPC status<br>0:booting<br>1: ping phase<br>2: ID_CF phase<br>3: Negotiation phase<br>4: power transfer phase |  |

#### Table 3. RT1650 Register Definition

#### **GPIO Interface**

The RT1650 provides a programmable General Purpose Input/Output (GPIO) pin. The GPIO can be used as an input or used as a status indicator for different application. Before use this GPIO, user should discuss its functions with RICHTEK and then RICHTEK code its function into firmware.

GPIO can be programmed as an output port, be a status indicator. For example,

► To control LED flashing when Rx position search

- ► To indicate thermal regulation is active

- To indicate battery is full or charging is complete

GPIO can be programmed as input port, to connect external signal and inform MCU. For example,

- ▶ Enable/Disable the output

- Enable the End Power Packet

Option for GPIO

- Internal pull-up option (pull-up to 3.3V)

- Internal pull-low option

| Symbol | Description                                      | Min  | Тур  | Max  |

|--------|--------------------------------------------------|------|------|------|

| Vil    | input logic low voltage                          |      |      | 0.8V |

| Vih    | input logic high voltage                         | 2V   |      | 5V   |

| Vol    | output low voltage                               |      |      | 0.4V |

| Voh    | output high voltage when push-pull architecture  | 2.6V | 3.3V |      |

| Voh    | output high voltage when open-drain architecture |      | Hi-Z |      |

### Table 5. RT1650 GPIO Specification

#### **Indicator Output**

An open-drain output pin, CHG, is provided to indicate the status of wireless power receiver. The CHG pin can be connected to a LED for charge status indicator. When the output of the RT1650 is enabled, the open-drain N-FET at CHG pin will be pulled to low level.

#### **Input Over-Voltage Protection**

When the input voltage increases suddenly, the RT1650 adjusts voltage-control loop to maintain regulator output voltage and sends control error packets to the transmitter every 30ms until the input voltage comes back to the VRECT target level (refer to Dynamic Rectifier Voltage Control Section). Once the VRECT voltage exceeds its over-voltage threshold (11.5V typ.), the RT1650 turns on the N-FETs at CLMP1 and CLMP2 pins to shunt the input current through external capacitors. By the way the CLAMP function may affect the communication signal to let the Tx re-start up.

### **Over-Temperature Protection**

The RT1650 provides an Over Temperature Protection

(OTP) feature to prevent excessive power dissipation from overheating the device. The OTP function shuts down the linear regulator operation when the junction temperature exceeds 150°C. Once the junction temperature cools down by around 20°C, the receiver will automatically resume operating.

GPIO can be push-pull or open-drain architecture

when GPIO programmed as an output.

### **Foreign Object Detection**

The RT1650 is a WPC 1.1.1 compatible device. In order to enable a power transmitter to monitor the power loss across the interface as one of the possible methods to limit the temperature rise of foreign objects, the RT1650 reports its received power to the power transmitter. The received power equals the power that is available from the output of the power receiver plus any power that is lost in producing that output power (the power loss in the secondary coil and series resonant capacitor, the power loss in the shielding of the power receiver, the power loss in the rectifier). In WPC1.1.1 specification, Foreign Object Detection (FOD) is enforced. This means the RT1650 will send received power information with known accuracy to the transmitter. The received power is sensed as the Figure 13.

Figure 13. Received Power Sensed

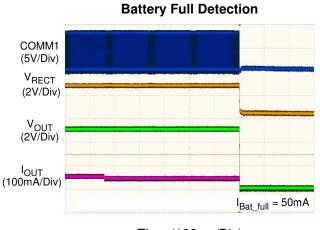

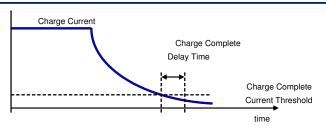

### **Battery Charge Complete Detection**

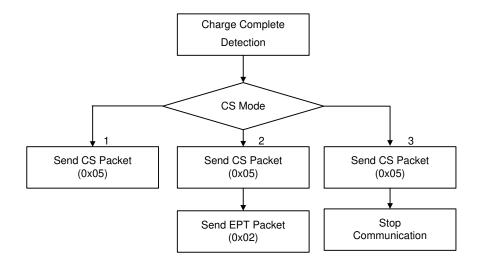

The RT1650 supports battery charge complete detection function. A programmable charge complete current threshold and a programmable charge complete delay time are provided. This function can be used to send the Charge Status packet (0x05) to the transmitter for indicating a full charged status 100%. Note that this packet does not turn off the transmitter.

The charge complete current threshold is adjustable from 0mA to 510mA and the default value is 50mA. The charge complete time is also adjustable from 0 seconds to 3825 seconds and the default value is 180 seconds.

Figure 14. Battery Charge Complete Detection

There are 3 operation modes when the charge complete status is detected. The first mode is to send a CS packet (0x05) to transmitter only. The CS packet does not turn off the transmitter. In the second mode, the RT1650 will send a CS packet (0x05) and an EPT packet to transmitter. In the third mode, the RT1650 will send a CS packet (0x05) and stop communication with the transmitter.

#### **Receiver Coil and Resonant Capacitors**

According to WPC specification, the dual resonant circuit of the power receiver comprises the receiver coil and capacitors C1 and C2. The receiver coil design is related to system design. Coil shape, material, inductance and shielding need to be considered. Shielding provides protection from interference between wireless power system and mobile electronic device. The recommended coil self-inductance is between  $8\mu$ H to  $13\mu$ H. The capacitance of the resonant capacitors can be calculated by the following equations.

$$C1 = \frac{1}{L'_{S} \times (2\pi f_{S})^{2}}$$

$$C2 = \frac{1}{L_{S} \times (2\pi f_{d})^{2} - \frac{1}{C1}}$$

In these equations, fs is resonant frequency with typical value 100kHz; and fd is another resonant frequency with typical value 1000kHz. L's is coil self-inductance when placed on the interface surface of a transmitter; and Ls is the self-inductance when placed away from the transmitter.

### **Firmware Setting**

Please refer to another document for detailed description of firmware setting.

#### **Thermal Considerations**

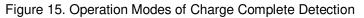

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WL-CSP-48B 3x3.4 package, the thermal resistance,  $\theta_{JA}$ , is 27.2°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C - 25°C) / (27.2°C/W) = 3.67W for WL-CSP-48B 3x3.4 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure

16 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

#### Layout Considerations

Follow the PCB layout guidelines for optimal performance of the IC.

- Keep the traces of main current paths as short and wide as possible.

- Place the capacitors as close as possible to the IC.

- Power ground should be as large as possible and connected to a power plane for thermal dissipation.

Power trace should be as short and wide as possible.

Power ground should be as large as possible and connect to the ground plane for thermal dissipation.

Figure 17. PCB Layout Guide

Copyright © 2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com

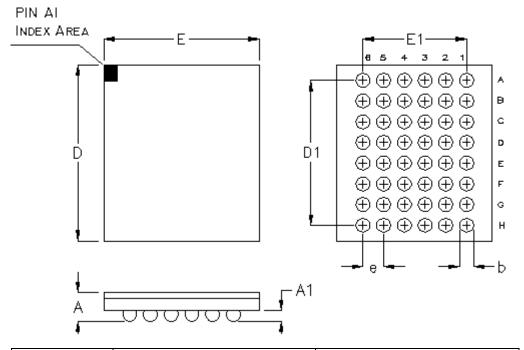

### **Outline Dimension**

| Symbol | Dimensions I | In Millimeters | Dimensions In Inches |       |  |

|--------|--------------|----------------|----------------------|-------|--|

| Symbol | Min.         | Max.           | Min.                 | Max.  |  |

| A      | 0.450        | 0.500          | 0.018                | 0.020 |  |

| A1     | 0.170        | 0.230          | 0.007                | 0.009 |  |

| b      | 0.240        | 0.300          | 0.009                | 0.012 |  |

| D      | 3.350        | 3.450          | 0.132                | 0.136 |  |

| D1     | 2.800        |                | 0.110                |       |  |

| E      | 2.950        | 3.050          | 0.116                | 0.120 |  |

| E1     | 2.0          | 000            | 0.079                |       |  |

| е      | 0.4          | 100            | 0.016                |       |  |

48B WL-CSP 3x3.4 Package (BSC)

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.