Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Power Management IC with Single Cell Li-Battery Switching Charger Integrated Power Path Controller

### **General Description**

The RT5037 is a highly integrated smart power management IC which includes: switch-mode single cell Li-lon/Li-Polymer battery charger, LDO, synchronize Buck regulator, Load Switch, and RTC-OSC for portable applications. The RT5037 also features USB On-The-Go (OTG) support.

The RT5037 optimizes the charging task by using a control algorithm to vary the charge rate via different modes, including pre-charge mode, fast charge mode, and constant voltage mode. The key charge parameters can be programmed via the I<sup>2</sup>C interface. The RT5037 resumes the charge cycle whenever the battery voltage falls below an internal threshold and automatically enters sleep mode when the input power supply is removed.

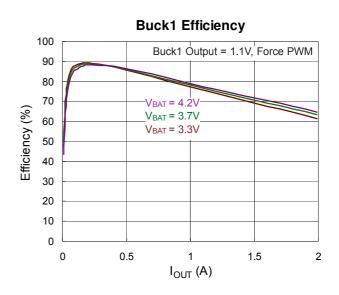

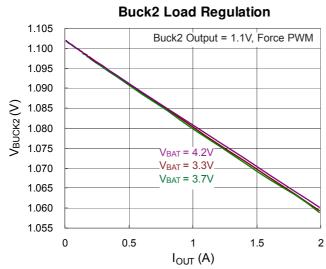

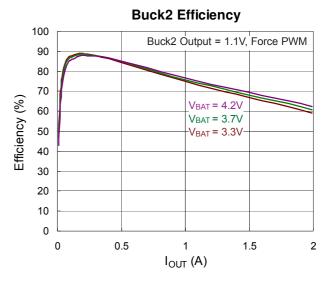

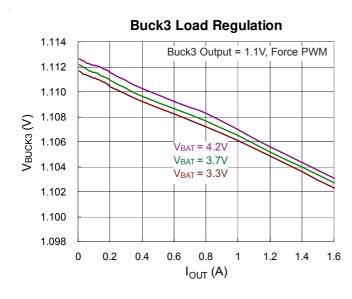

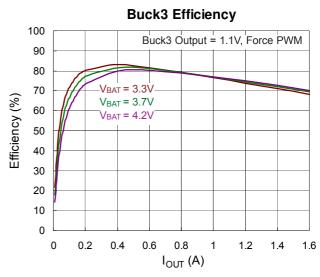

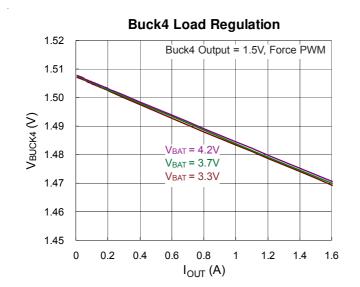

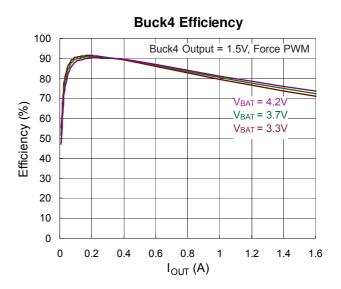

Four integrated Synchronize Buck Regulators are designed to provide MAX 2/2/1.6/1.6A application with high efficiency.

Four integrated LDOs are designed to provide MAX 0.35/0.35/0.35/0.35A application.

Two Load Switches are integrated with load Ron. And a Real Time Clock (RTC) includes time counter and a 32768Hz oscillator for portable applications.

The RT5037 also provides rich protection functions: Over Current Protection, Under Voltage Protection, Over Voltage Protection, Over Temperature Protection, and Over Load Protection.

### **Ordering Information**

Package Type

QW: WQFN-40L 5x5 (W-Type)

Lead Plating System

G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Battery Charger

- ▶ High Accuracy Voltage/Current Regulation

- ► Average Input Current Regulation(AICR) : 0.1/0.5/ 0.7/0.9/1/1.5/2A

- ▶ Minimum Input Voltage Regulation(MIVR) : 4.2V to 4.8V

- ▶ Charge Voltage Regulation: 3.65V to 4.4V

- ▶ Charge Current Regulation: 0.5A to 2A

- ➤ Synchronous 0.75/1.5MHz Fixed Frequency PWM Controller With Up To 95% Duty Cycle

- ▶ Reverse Leakage Protection To Prevent Battery Drainage

- ▶ Thermal Regulation

- ▶ IRQ Output For Communication With I<sup>2</sup>C

- **▶** Battery Temperature Detection

- ▶ Reverse Boost to Support OTG 1A

- 4 LDOs

- ▶ MAX Output Current 0.35/0.35/0.35/0.35A

- I<sup>2</sup>C Programmable Output Level

- 4 LV Buck Regulators

- ▶ MAX Output Current 2/2/1.6/1.6A

- ▶ I<sup>2</sup>C Programmable Output Level

- No Schottky Barrier Diode Required

- ▶ 1.5M/3MHz Fixed Frequency Operation

- Auto Discharge Function

- RTC Timer and Oscillator

- 2 Load Switches

# **Applications**

- Cellular Telephones

- Personal Information Appliances

- Tablet PC, Power Bank

- Portable Instruments

RT5037 Preliminary RI

### RICHTEK

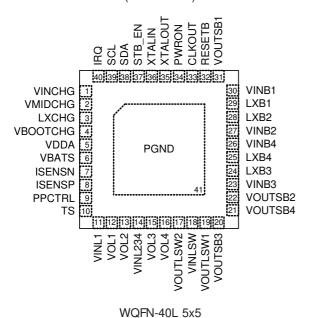

# **Pin Configurations**

(TOP VIEW)

# **Marking Information**

RT5037 GQW YMDNN RT5037GQW: Product Number

YMDNN : Date Code

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                          |

|---------|----------|-------------------------------------------------------------------------------------------------------|

| 1       | VINCHG   | Charger Input Voltage For Adaptor/USB Power Source.                                                   |

| 2       | VMIDCHG  | Connection Point Between Reverse Blocking and High Side MOSFET.                                       |

| 3       | LXCHG    | Internal Switch Node To Output Inductor Connection of Switching Charger                               |

| 4       | VBOOTCHG | Bootstrap Power Node For Switching Charger                                                            |

| 5       | VDDA     | Internal Power For Analog Blocks, Put 1µF To GND.                                                     |

| 6       | VBATS    | Battery Voltage Regulation Node for Charger.                                                          |

| 7       | ISENSN   | Charging Current Sensing Negative Node.                                                               |

| 8       | ISENSP   | Charging Current Sensing Positive Node                                                                |

| 9       | PPCTRL   | External Power Path Control. Used to control external power P-MOSFET to achieve power path operation. |

| 10      | TS       | Battery Temperature Detection.                                                                        |

| 11      | VINL1    | Input Power for LDO1.                                                                                 |

| 12      | VOL1     | Output Voltage Regulation Node for LDO1.                                                              |

| 14      | VINL234  | Input Power for LDO2, LDO3, LDO 4.                                                                    |

| 13      | VOL2     | Output Voltage Regulation Node for LDO2.                                                              |

| 15      | VOL3     | Output Voltage Regulation Node for LDO3.                                                              |

| 16      | VOL4     | Output Voltage Regulation Node for LDO4.                                                              |

| 17      | VOUTLSW2 | Output Pin for Load Switch 2.                                                                         |

| 18      | VINLSW   | Input Pin for Load Switches GOOD.                                                                     |

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                              |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19               | VOUTLSW1 | Output Pin for Load Switch 1.                                                                                                                                                                                             |

| 20               | VOUTSB3  | Output Voltage Regulation Node for Buck3.                                                                                                                                                                                 |

| 21               | VOUTSB4  | Output Voltage Regulation Node for Buck4.                                                                                                                                                                                 |

| 22               | VOUTSB2  | Output Voltage Regulation Node for Buck2.                                                                                                                                                                                 |

| 23               | VINB3    | Input Power for Buck3.                                                                                                                                                                                                    |

| 24               | LXB3     | Internal Switch Node to Output Inductor Connection for Buck3.                                                                                                                                                             |

| 25               | LXB4     | Internal Switch Node to Output Inductor Connection for Buck4.                                                                                                                                                             |

| 26               | VINB4    | Input Power for Buck4.                                                                                                                                                                                                    |

| 27               | VINB2    | Input Power for Buck2.                                                                                                                                                                                                    |

| 28               | LXB2     | Internal Switch Node to Output Inductor Connection for Buck2.                                                                                                                                                             |

| 29               | LXB1     | Internal Switch Node to Output Inductor Connection for Buck1.                                                                                                                                                             |

| 30               | VINB1    | Input Power for Buck1.                                                                                                                                                                                                    |

| 31               | VOUTSB1  | Output Voltage Regulation Node for Buck1.                                                                                                                                                                                 |

| 32               | RESETB   | Power-On Reset Output and Reset Key Input. Open drain, Connect A Pull-Up Resister. The pin is high impedance after RT5037 booting completely, otherwise, the pin is short to GND. Low pulse to triggers soft reset event. |

| 33               | CLKOUT   | RTC 32768Hz Clock Output. Open drain.                                                                                                                                                                                     |

| 34               | PWRON    | Power On Key Input. Low pulse to triggers power-on event.                                                                                                                                                                 |

| 35               | XTALOUT  | Crystal Output. This pin's parasitic capacitance should be kept as low as possible. Noise interference should also be avoided.                                                                                            |

| 36               | XTALIN   | Crystal Input. This pin's parasitic capacitance should be kept as low as possible. Noise interference should also be avoided.                                                                                             |

| 37               | STB_EN   | Standby Mode control pin. From low to high will trigger standby mode and from high to low will leave standby mode.                                                                                                        |

| 38               | SDA      | Data Input For I <sup>2</sup> C. Open Drain, Connect A Pull-Up Resister.                                                                                                                                                  |

| 39               | SCL      | Clock Input For I <sup>2</sup> C. Open Drain, Connect A Pull-Up Resister                                                                                                                                                  |

| 40               | IRQ      | IRQ Output Node. Open drain.                                                                                                                                                                                              |

| 41 (Exposed Pad) | PGND     | The exposed pad must be soldered to a large PCB and connected to PGND for maximum thermal dissipation and current flow.                                                                                                   |

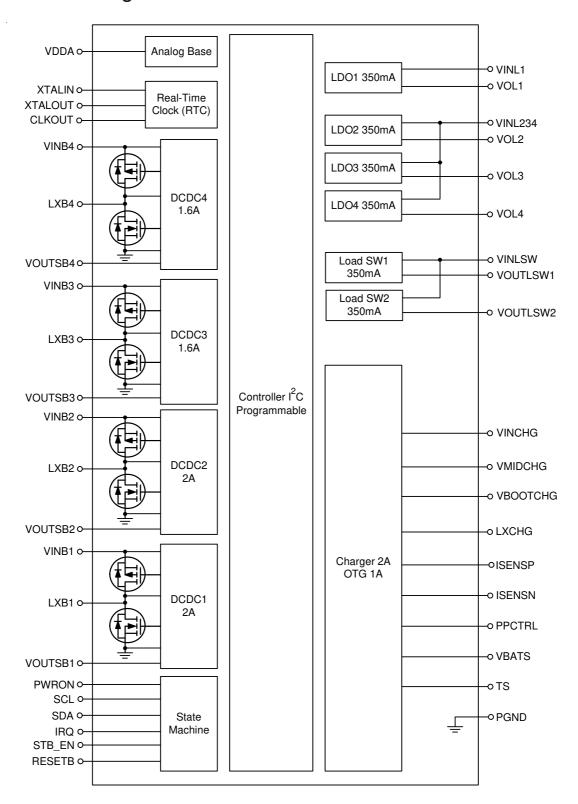

# **Function Block Diagram**

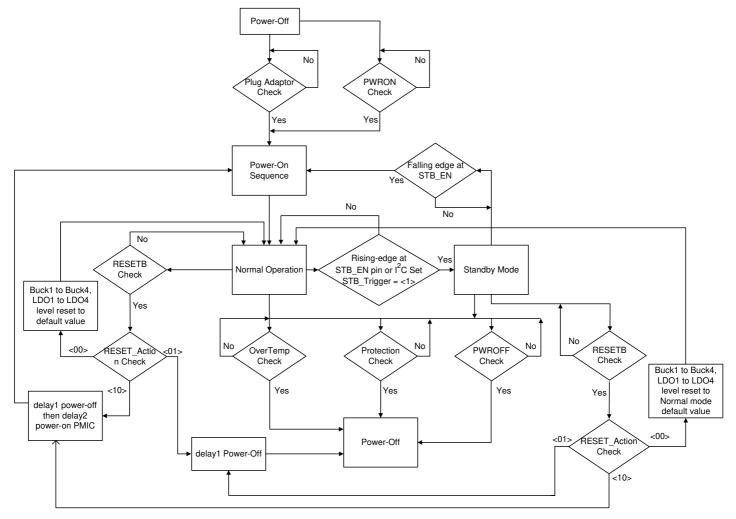

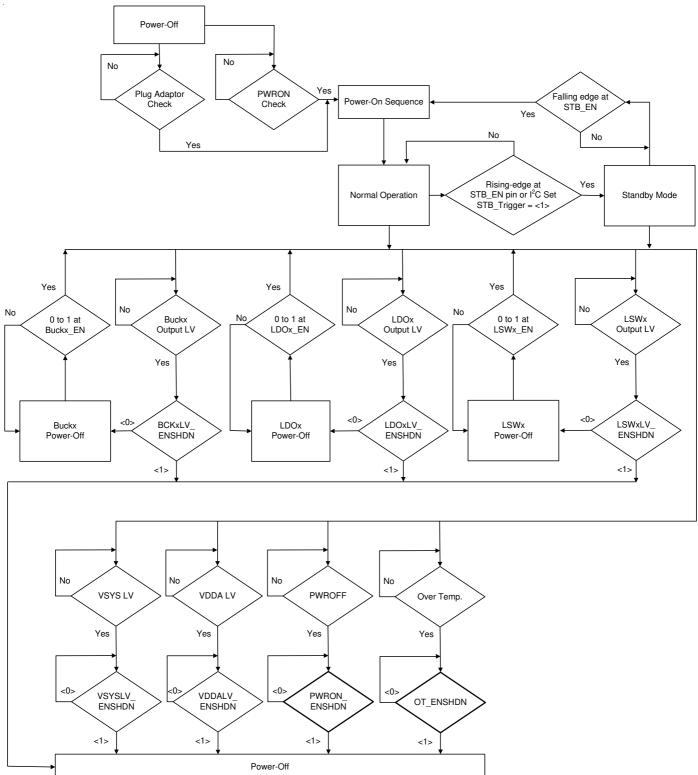

### Flow Chart

#### **Power Channel Flow Chart**

Note: RESETB Check: From "LOW" to "HIGH" rising input into RESETB pin with 100ms debouncing time

RT5037 Preliminary

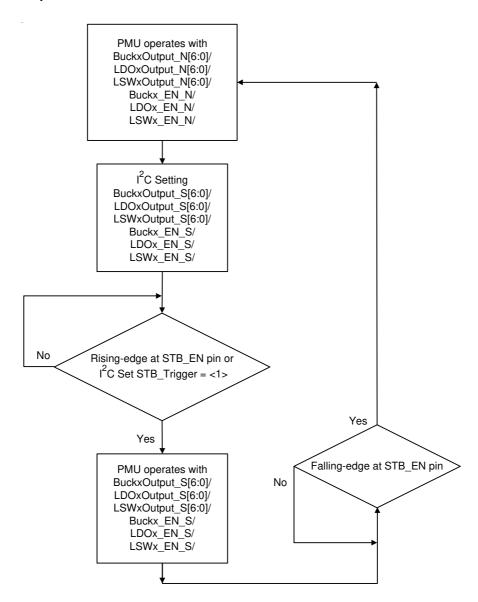

### Stand-By and Wake-Up Flow Chart

### **Protection Flow Chart**

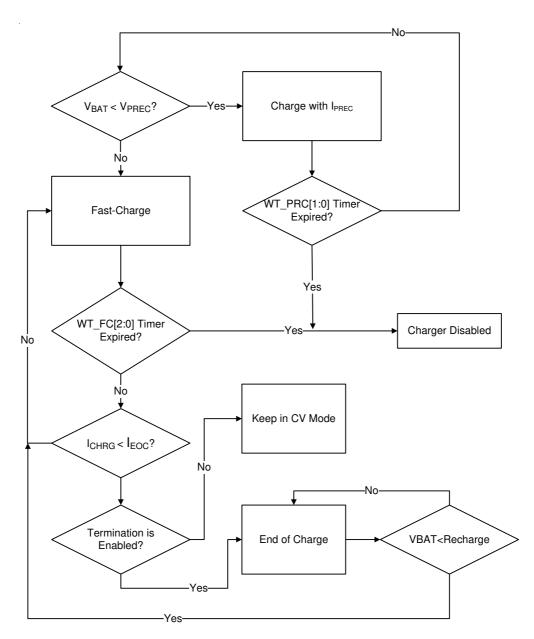

### **Charger Flow Chart**

# Absolute Maximum Ratings (Note 1)

| • | Supply Input Voltage                         | -0.3V to 10V   |

|---|----------------------------------------------|----------------|

| • | VMIDCHG, VBOOTCHG                            | -0.3V to 10V   |

| • | LXCHG                                        | -0.3V to 6V    |

| • | VMIDCHG-VINCHG, VBOOTCHG-LXCHG               | -0.3V to 6V    |

| • | Others                                       | -0.3V to 6V    |

| • | Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                |

|   | WQFN-40L 5x5                                 | 3.63W          |

| • | Package Thermal Resistance (Note 2)          |                |

|   | WQFN-40L 5x5, $\theta_{JA}$                  |                |

|   | WQFN-40L 5x5, $\theta_{JC}$                  | 6°C/W          |

| • | Junction Temperature                         | 150°C          |

| • | Lead Temperature (Soldering, 10 sec.)        | 260°C          |

| • | Storage Temperature Range                    | –65°C to 150°C |

| • | ESD Susceptibility (Note 3)                  |                |

|   | HBM (Human Body Model)                       | 2kV            |

|   | MM (Machine Model)                           | 200V           |

|   |                                              |                |

### **Recommended Operating Conditions** (Note 4)

| • | Supply Input Voltage       | 4.3V to 5.5V   |

|---|----------------------------|----------------|

| • | Junction Temperature Range | –40°C to 125°C |

| • | Ambient Temperature Range  | –40°C to 85°C  |

### **Electrical Characteristics**

$(VINCHG = 5V,\ V_{ISENSN} = 4.2V,\ L = 1\mu H,\ C_{VINCHG} = 4.7\mu F,\ C_{VBATS} = 4.7\mu F,\ T_A = 25^{\circ}C,\ unless\ otherwise\ specified)$

| Parameter                       | Symbol | Test Conditions                                                                              | Min | Тур  | Max | Unit |

|---------------------------------|--------|----------------------------------------------------------------------------------------------|-----|------|-----|------|

| Input Power Source              |        |                                                                                              |     |      |     |      |

| VINCHG Operation Range          |        |                                                                                              | 4.3 |      | 5.5 | V    |

| VINCHG Supply Current           |        | Charger is switching, ICHG = 0,<br>Buck loading = 0, LDOs loading = 0                        |     | 10   |     | mA   |

| VINCHG Supply Current           |        | Charger is not switching, ICHG = 0,<br>Bucks loading = 0, LDOs loading = 0                   |     |      | 5   | mA   |

| Leakage Current from<br>Battery |        | VISENSN = 3.8V, VINCHG = 0V,<br>Charger, Bucks and LDOs and<br>LSWs are OFF. SCL = SDA = 0V. |     |      | 50  | μΑ   |

| Protection                      |        |                                                                                              |     |      |     |      |

| VINCHG OVP Threshold<br>Voltage |        |                                                                                              | 5.6 | 5.75 | 5.9 | ٧    |

| VINCHG OVP Hysteresis           |        |                                                                                              |     | 100  |     | mV   |

| ISENSN OVP                      |        |                                                                                              | 110 | 117  | 124 | %    |

| ISENSN OVP Hysteresis           |        |                                                                                              |     | 10   |     | %    |

| Over Temperature<br>Protection  |        | (Note 4)                                                                                     |     | 165  |     | °C   |

| Parameter                                        | Symbol               | Test Conditions                                             | Min  | Тур     | Max  | Unit |

|--------------------------------------------------|----------------------|-------------------------------------------------------------|------|---------|------|------|

| OTP Hysteresis                                   |                      |                                                             |      | 10      |      | °C   |

| Thermal Regulation<br>Threshold                  |                      | Charge Current Begins To<br>Reduce (Note 4)                 |      | 120     |      | °C   |

| Input Power Source Detection                     | n                    |                                                             |      |         |      |      |

| Poor Source Detect<br>Threshold                  |                      | Bad Voltage Source<br>Detection                             | 3.6  | 3.8     | 4    | V    |

| Poor Source Detect Deglitch                      |                      |                                                             |      | 30      |      | ms   |

| Poor Source Detect<br>Hysteresis                 |                      | VINCHG Rising                                               | 100  |         | 200  | mV   |

| Current Sink to GND                              |                      | During Poor Source<br>Detection                             |      | 45      |      | mA   |

| Detection Interval                               |                      | Input Power Source Detection                                |      | 2       |      | S    |

| Sleep Mode Comparator                            |                      |                                                             |      |         |      |      |

| Sleep-Mode Entry Threshold VINCHG – ISENSN       | V <sub>SLP</sub>     | 3V < ISENSN < VBATREG,<br>VINCHG Falling                    | 0    | 0.04    | 0.1  | ٧    |

| Sleep-Mode Exit Hysteresis<br>VINCHG - ISENSN    | V <sub>SLPEXIT</sub> | 3V < ISENSN < V <sub>BATREG</sub> ,<br>VINCHG Rising        | 40   | 120     | 200  | mV   |

| Sleep-Mode Deglitch Time                         | t <sub>SLP</sub>     | VINCHG Rising Above V <sub>SLP</sub> + V <sub>SLPEXIT</sub> |      | 128     |      | ms   |

| Under Voltage Lockout (UVL                       | .O) Thresho          | ld for VINCHG                                               |      |         |      |      |

| Charger Active Threshold<br>Voltage              |                      | VINCHG Rising,                                              | 3.05 | 3.3     | 3.45 | V    |

| Charger Active Hysteresis                        |                      | VINCHG Falling                                              |      | 150     |      | mV   |

| Minimum Input Voltage Reg                        | ulation (MIV         | R)                                                          |      |         |      |      |

| Minimum Input Voltage<br>Regulation              | V <sub>MIVR</sub>    | I <sup>2</sup> C per 0.1V                                   | 4.2  |         | 4.8  | V    |

| V <sub>MIVR</sub> Accuracy                       |                      |                                                             | -5   |         | 5    | %    |

|                                                  |                      | IAICR = 100mA                                               | 80   | 90      | 100  |      |

| Average Input Current Regulation (AICR) Accuracy | IAICR                | IAICR = 500mA                                               | 400  | 450     | 500  | mA   |

| riogulation (Alon) Accuracy                      |                      | I <sub>AICR</sub> = 1000mA                                  | 800  | 900     | 1000 |      |

| VDDA Regulator                                   |                      |                                                             |      |         |      |      |

| VDDA Voltogo                                     |                      | V <sub>VINCHG</sub> > 4.5V                                  |      | 4.5     |      | V    |

| VDDA Voltage                                     |                      | Vvinchg < Visensn                                           |      | VISENSN |      | V    |

| VDDA UVLO                                        |                      | VDDA Falling                                                | 2.4  | 2.5     | 2.6  | V    |

| VDDA UVLO Hysteresis                             |                      | VDDA Rising                                                 |      | 0.2     |      |      |

| Battery Voltage Regulation                       |                      |                                                             |      |         |      |      |

| Battery Voltage Regulation                       | V <sub>BATREG</sub>  | I <sup>2</sup> C Programmable Per<br>25mV                   | 3.65 |         | 4.4  | V    |

| VBATREG Accuracy                                 |                      | 0 to 85°C                                                   | -1   |         | 1    | %    |

| Parameter                     | Symbol                | Test Conditions                                                                                                  | Min        | Тур | Max | Unit  |

|-------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-------|

| Re-Charge<br>Threshold        | (VBATREG –<br>VREC)   | V <sub>VBATS</sub> Falling, (V <sub>BATREG</sub> – V <sub>REC</sub> ) = programmable                             | 100        |     | 300 | mV    |

| Re-Charge Deglitch            | t <sub>REC</sub>      |                                                                                                                  |            | 128 |     | ms    |

| Charging Current Re           | egulation             |                                                                                                                  |            |     |     |       |

| Output Charging<br>Current    | I <sub>CHG</sub>      | $I^2$ C Per 0.1A, R <sub>SENSE</sub> = 20mΩ                                                                      | 0.7        |     | 2   | А     |

| I <sub>CHG</sub> Accuracy     |                       | $R_{SENSE} = 20 m\Omega$                                                                                         | -100       |     | 100 | mA    |

| Pre-Charge<br>Threshold       | V <sub>PREC</sub>     | I <sup>2</sup> C Per 0.1V, rising threshold                                                                      | 2.3        |     | 3.8 | V     |

| V <sub>PREC</sub> Accuracy    |                       |                                                                                                                  | <b>–</b> 5 |     | 5   | %     |

| Pre-Charge Current            | I <sub>PREC</sub>     | I <sup>2</sup> C Per 100mA, from VBATS<br>U100 mode : I <sub>PREC</sub> will fix 50mA                            | 150        |     | 450 | mA    |

| I <sub>PREC</sub> Accuracy    |                       |                                                                                                                  | -20        |     | 20  | %     |

| Charge Termination            | Detection             |                                                                                                                  |            |     |     |       |

| End of Charge<br>Current      | I <sub>EOC</sub>      | $I^2$ C per 50mA, R <sub>SENSE</sub> = 20mΩ<br>U100 mode : IEOC will fix 50mA                                    | 150        |     | 600 | mA    |

| I <sub>EOC</sub> Accuracy     |                       | $R_{SENSE} = 20 m\Omega$                                                                                         | -100       |     | 100 | mA    |

| Deglitch Time for EOC         | t <sub>EOC</sub>      | I <sub>CHG</sub> < I <sub>EOC</sub> , V <sub>ISENSN</sub> > V <sub>REC</sub><br>I <sup>2</sup> C 32/64/128/256us | 32         |     | 256 | μs    |

| Charger Timer Prote           | ection                |                                                                                                                  | •          |     | •   |       |

| FastCharge Timer              |                       | I <sup>2</sup> C per 2 Hrs                                                                                       | 4          |     | 16  | Hrs   |

| PreCharge Timer               |                       | I <sup>2</sup> C 0.5/1/2/4 Hrs                                                                                   | 0.5        |     | 4   | Hrs   |

| Battery Detection<br>Current  | IBATDET               | As RNTC is disable, after EOC Done                                                                               |            | 0.5 |     | mA    |

| Battery Detection<br>Time     | tBATDET               | As RNTC is disable, after EOC Done                                                                               |            | 256 |     | ms    |

| NTC Monitor                   |                       |                                                                                                                  |            |     |     |       |

| HOT Threshold                 | V <sub>VTS_HOT</sub>  | VTS falling, the ratio of VOL1,<br>VINCHG > V <sub>IN(MIN)</sub>                                                 |            | 28  |     | %VOL1 |

| WARM Threshold                | V <sub>VTS_WARM</sub> | VTS falling, the ratio of VOL1,<br>VINCHG > V <sub>IN(MIN)</sub>                                                 |            | 34  |     | %VOL1 |

| COOL Threshold                | Vvts_cool             | VTS rising, the ratio of VOL1,<br>VINCHG > V <sub>IN(MIN)</sub>                                                  |            | 64  |     | %VOL1 |

| COLD Threshold                | V <sub>VTS_COLD</sub> | VTS rising, the ratio of VOL1,<br>VINCHG > V <sub>IN(MIN)</sub>                                                  |            | 74  |     | %VOL1 |

| Accuracy of VTS               |                       |                                                                                                                  | -2         |     | 2   | %VOL1 |

| Low Temperature<br>Hysteresis | ΔV <sub>VTS</sub>     |                                                                                                                  |            | 1   |     | %VPTS |

| Disable Threshold             | V <sub>VTS_OFF</sub>  | TS function disable                                                                                              |            |     | 5   | %VPTS |

| Battery Absent<br>Detection   | V <sub>BAT_ABS</sub>  | VTS rising, the ratio of VPTS, VINCHG > V <sub>IN(MIN)</sub>                                                     |            | 90  |     | %VPTS |

| Parameter                             | Symbol              | Test Conditions                                                                | Min   | Тур | Max | Unit |

|---------------------------------------|---------------------|--------------------------------------------------------------------------------|-------|-----|-----|------|

| PWM Switching Char                    | ger                 |                                                                                |       | •   |     |      |

| Reverse Block<br>On-Resistance        | RREV                | From VINCHG to VMIDCHG, as I <sub>AICR</sub> disable or I <sub>AICR</sub> = 2A |       | 90  |     | mΩ   |

| High-Side<br>On-Resistance            | R <sub>HS</sub>     | From VMIDCHG to LXCHG                                                          |       | 200 |     | mΩ   |

| Low-Side<br>On-Resistance             | R <sub>LS</sub>     | From CHGLX to PGND                                                             |       | 90  |     | mΩ   |

| Charging Efficiency                   |                     | $V_{VINCHG} = 5V$ , $V_{ISENSN} = 4V$ , and $I_{CHG} = 1.5A$ ,                 |       | 85  |     | %    |

| Oscillator Frequency                  | fosc                | I <sup>2</sup> C for 0.75/1.5 MHz                                              |       | 1.5 |     | MHz  |

| Frequency Accuracy                    |                     |                                                                                | -10   |     | 10  | %    |

| Maximum Duty<br>Cycle                 |                     | At Minimum Voltage Input                                                       |       | 95  |     | %    |

| Minimum Duty Cycle                    |                     |                                                                                | 0     |     |     | %    |

| Peak OCP as<br>Charger Mode           |                     |                                                                                | 2.4   | 3   | 3.6 | Α    |

| Reverse Boost Mode                    | Operation           |                                                                                | •     | •   |     |      |

| Output Voltage<br>Level               |                     | To VMIDCHG, $I^2$ C per 25mV VMIDCHG setting $\geq V_{VBATS} + 0.4$            | 3.625 |     | 5.2 | V    |

| Output Voltage<br>Accuracy            |                     |                                                                                | -3    |     | 3   | %    |

| Efficiency                            |                     | VMIDCHG = 5V, V <sub>ISENSN</sub> = 4V, and Loading = 1A,                      |       | 85  |     | %    |

| MAX Output Current for VINCHG         |                     | As V <sub>ISENSN</sub> > 3.5V                                                  | 1     |     |     | Α    |

| Peak Over Current<br>Protection       |                     |                                                                                | 2.4   | 3.0 | 3.6 | Α    |

| VMIDCHG OVP as<br>Reverse Boost       |                     |                                                                                |       | 5.5 |     | ٧    |

| VMIDCHG OVP<br>Hysteresis             |                     |                                                                                |       | 200 |     | mV   |

| Minimum Battery<br>Voltage for Boost. | V <sub>BATMIN</sub> | As Boost Start-Up. I <sup>2</sup> C programmable Per 0.1V                      | 2.9   |     | 3.6 | V    |

| I <sup>2</sup> C Characteristics      |                     |                                                                                |       |     |     |      |

| Output Low Voltage                    | V <sub>OL</sub>     | I <sub>DS</sub> = 10mA                                                         |       |     | 0.4 | V    |

| SCL /SDA Input                        | V <sub>IH</sub>     | Logic High Threshold                                                           | 1.4   |     |     | V    |

| Threshold Voltage                     | V <sub>IL</sub>     | Logic Low Threshold                                                            |       |     | 0.4 | V    |

| SCL Clock                             |                     |                                                                                |       |     | 400 | kHz  |

| Parameter                                 | Symbol           | Test Conditions                                                                                         | Min | Тур  | Max | Unit |

|-------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Control I/O Pin                           |                  |                                                                                                         | ļ   | ļ    |     | ļ.   |

| Output Low Voltage<br>(IRQ, RESETB)       | V <sub>OL</sub>  | I <sub>DS</sub> = 10mA                                                                                  |     |      | 0.4 | V    |

| Logic Input Threshold                     | ViH              | Logic High Threshold                                                                                    | 1.4 |      |     | V    |

| Voltage (PWRON)                           | VIL              | Logic Low Threshold                                                                                     |     |      | 0.4 | V    |

| LDO1 to LDO4, LSW1, LS                    | SW2              |                                                                                                         |     |      |     |      |

| VINL1,VINL234 Input<br>Voltage Range      | VVINL1,234       |                                                                                                         | 2.7 |      | 5.5 | V    |

| LDO1 to LDO4<br>Adjustable Output Range   |                  | I <sup>2</sup> C per 25mV                                                                               | 0.8 |      | 3.3 | V    |

| PSRR                                      |                  | $\begin{array}{c} V_{VINL1,234}=4V,F=1kHz,\\ C_{VOL1to4}=1\mu F \end{array}$                            |     | 60   |     | dB   |

| LDO1 to LDO4 MAX<br>Current               |                  |                                                                                                         | 350 |      |     | mA   |

| Output Current Limit for LDO1 to LDO4     |                  |                                                                                                         | 500 |      |     | mA   |

| Drop Out Voltage                          |                  | V <sub>VINL1, 234</sub> = 3V, I <sub>OUT</sub> = 150mA                                                  |     |      | 150 | mV   |

| Internal Off Discharge                    |                  |                                                                                                         |     | 1    |     | kΩ   |

| VINLSW1, VINLSW2                          |                  |                                                                                                         | 2.7 |      | 5.5 | V    |

| LSW Drop Out Voltage                      |                  | V <sub>VINLSW1, 2</sub> = 3.3V,<br>I <sub>OUT</sub> = 500mA                                             |     | 0.2  |     | V    |

| Output Current Limit for LSW1, LSW2       |                  |                                                                                                         | 600 |      |     | mA   |

| Synchronize Buck Regula                   | ator1 to Buck Re | egulator4                                                                                               |     |      |     |      |

| VINB1 to VINB4 Input<br>Voltage Range     | VBUCKVIN         |                                                                                                         | 2.7 |      | 5.5 | V    |

| Quiescent Current from VINB1 to VINB4     |                  | Loading = 0mA, no switch, Each one                                                                      |     | 25   | 40  | μА   |

| Shutdown Current from VINB1 to VINB4      |                  | Each one                                                                                                |     | 0.1  | 1   | μΑ   |

| Buck1 to Buck4<br>Adjustable Output Range | VVOUTSB1 to 4    | I <sup>2</sup> C per 25mV                                                                               | 0.8 |      | 3.3 | V    |

| Output Voltage Accuracy                   |                  | $\begin{array}{c} \text{VVINB1 to 4} = 2.7 \text{V to 5.5V}, \\ \text{VOUT} \ > 1 \text{V} \end{array}$ | -3  |      | 3   | %    |

| Output Voltage Accuracy                   |                  | $V_{VINB1 \text{ to } 4} = 2.7V \text{ to } 5.5V,$<br>$V_{OUT} \le 1V$                                  | -30 |      | 30  | mV   |

| High-Side<br>On-Resistance                |                  | VVINB1 to 4 = 3.6V                                                                                      |     | 0.20 |     | Ω    |

| Low -Side<br>On-Resistance                |                  | VVINB1 to 4 = 3.6V                                                                                      |     | 0.20 |     | Ω    |

| Buck 1, 2 Output Current capability       |                  | DC                                                                                                      |     | 2    |     | Α    |

| Buck 1, 2 Output Current capability       |                  | Peak                                                                                                    |     | 2.5  |     | Α    |

| Parameter                              | Symbol          | Test Conditions                                                        | Min          | Тур    | Max | Unit |

|----------------------------------------|-----------------|------------------------------------------------------------------------|--------------|--------|-----|------|

| Output Voltage<br>Accuracy             |                 | VVINL1 to 4 = 2.7V to 5.5V,<br>VOUT > 1V                               | -3           |        | 3   | %    |

| Output Voltage<br>Accuracy             |                 | $V_{VINL1 \text{ to } 4} = 2.7V \text{ to } 5.5V,$<br>$V_{OUT} \le 1V$ | -30          |        | 30  | mV   |

| Buck 3, 4 Output<br>Current capability |                 | DC                                                                     |              | 1.6    |     | Α    |

| Buck 3, 4 Output<br>Current capability |                 | Peak                                                                   |              | 2      |     | Α    |

| Oscillator Frequency                   |                 | $V_{VINB1 to 4} = 3.6V$ , Loading = 200mA                              |              | 1.5    |     | MHz  |

| Maximum Duty Cycle                     |                 |                                                                        | 100          |        |     | %    |

| Soft-Start Time                        | T <sub>SS</sub> |                                                                        |              | 150    |     | μS   |

| Discharge Time                         |                 | $C_{OUT}$ of Buck = $10\mu F$ , (Note 5)                               |              |        | 10  | ms   |

| Line Regulation                        |                 |                                                                        |              | 0.1    |     | %/V  |

| RTC                                    |                 |                                                                        |              |        |     |      |

| RTC Operation Voltage                  |                 |                                                                        | 2.4          |        | 4.5 | V    |

| RTC Quiescent<br>Current               |                 | RTCPWR > UVLO Threshold,<br>XIN = XOUT = 14pF                          |              |        | 3   | μА   |

| RTC Clock                              |                 |                                                                        |              | 32.768 |     | kHz  |

| RTC Clock Accuracy                     |                 | RTC Operation Voltage = 1.6V to 3.3V                                   | -10          |        | 10  | ppm  |

| RTC Clock Output<br>High               |                 | Pin C32K Source Out 0.1mA                                              | VDDA<br>-0.3 |        |     | ٧    |

| RTC Clock Output Low                   |                 | Pin C32K Sink 0.1mA                                                    |              |        | 0.3 | V    |

| RTC OSC Startup<br>Time                |                 |                                                                        |              | 0.5    | 1   | s    |

- Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Guarantee By Design.

www.richtek.com

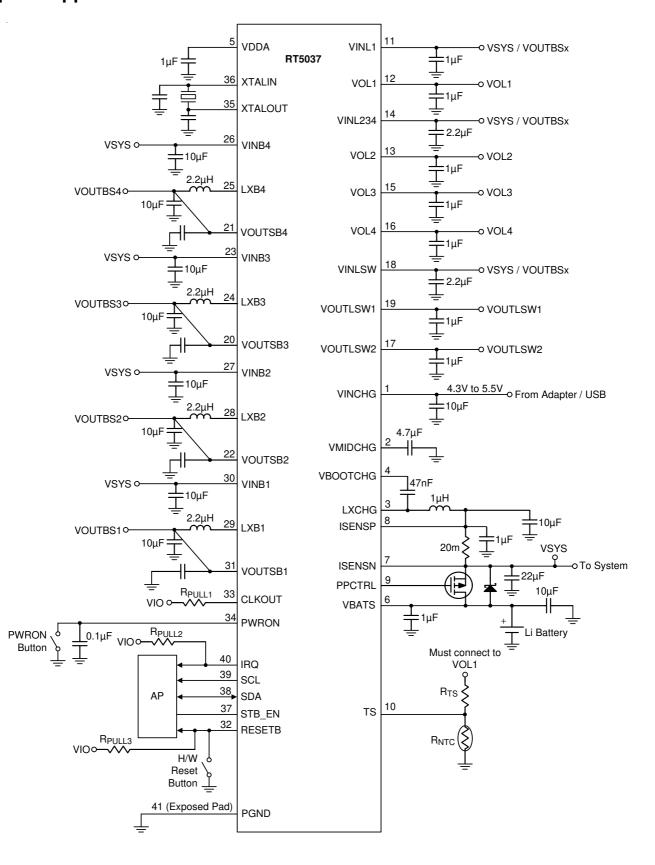

# **Typical Application Circuit**

RT5037 Preliminary RICHTEK

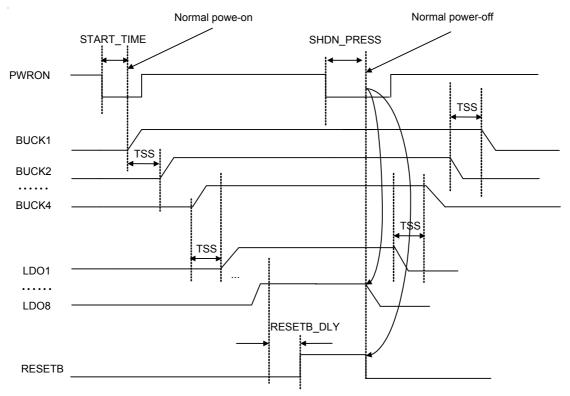

# **Timing Diagram**

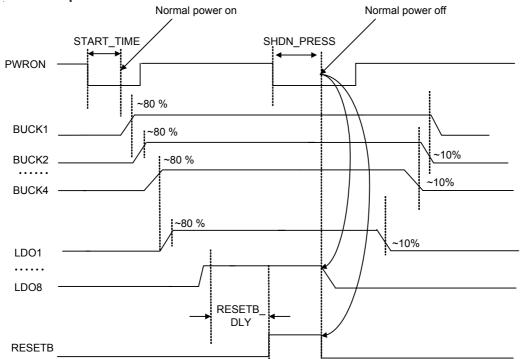

### PMIC - POWER On/Off DIAGRAM

### Timing Based On/Off Sequence

### Level Based On/Off Sequence

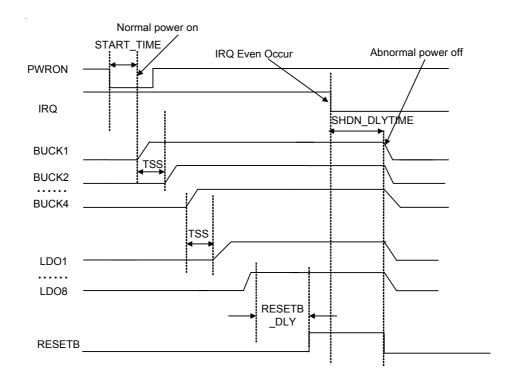

### **Abnormal Off**

RT5037 Preliminary

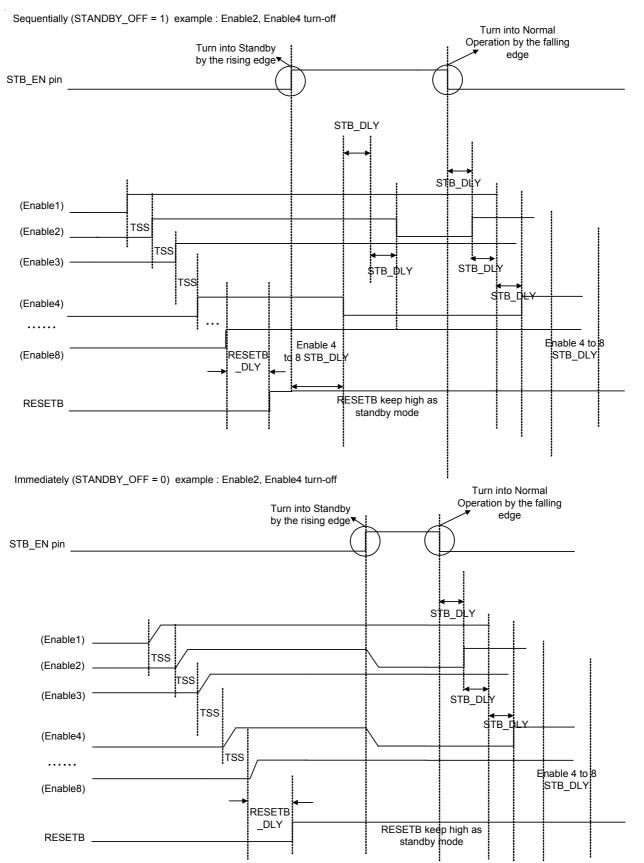

### Standby mode and wake up by power-on

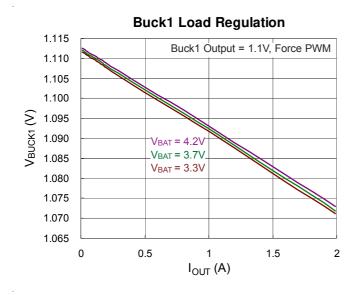

# **Typical Operating Characteristics**

### **Application Information**

#### **Switching Charger**

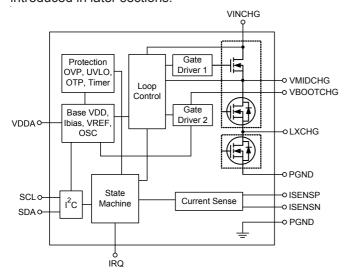

The switching charger integrates a synchronous PWM controller with power MOSFETs to provide Minimum Input Voltage Regulation (MIVR), Average Input Current Regulation (AICR), high accuracy current and voltage regulation, and charge termination. The charger also features OTG-Boost (On-The-Go).

The switching charger has two operation modes: charge mode, and boost mode (OTG-Boost). In charge mode, the switching charger supports a precision charging system for single cell. In boost mode, the switching charger works as the boost converter and boosts the voltage from battery to VINCHG pin for sourcing the OTG devices.

Notice that the switching charger does not integrate input power source (AC adapter or USB input) charging detection. Thus, the switching charger does not set the charge current automatically. The charge current needs to be set via I<sup>2</sup>C interface by the host. The switching charger application mechanism and I<sup>2</sup>C compatible interface are introduced in later sections.

Figure 1. Switching Charger Function Block Diagram

### **Charge Mode Operation**

### Minimum Input Voltage Regulation (MIVR)

The switching charger features Minimum Input Voltage Regulation function to prevent input voltage drop due to insufficient current provided by the adaptor or USB input. If MIVR function is enabled, the input voltage decreases when the over current of the input power source occurs. VINCHG is regulated at a predetermined voltage level which can be set as 4.2V to 4.8V per 0.1V by I<sup>2</sup>C interface. At this time, the current drawn by the switching charger equals to the maximum current value that the input power can provide at the predetermined voltage level, instead of the set value.

Table 1. MIVR Register Setting Table

| MIVR[2:0] | V <sub>MIVR</sub> |

|-----------|-------------------|

| 000       | Disable           |

| 001       | 4.2V              |

| 010       | 4.3V              |

| 011       | 4.4V              |

| 100       | 4.5V (default)    |

| 101       | 4.6V              |

| 110       | 4.7V              |

| 111       | 4.8V              |

#### Charge Profile

The switching charger provides a precision Li-ion or Lipolymer charging solution for single-cell applications. Input current limit, charge current, termination current, charge voltage and input voltage MIVR are all programmable via the I<sup>2</sup>C interface. In charge mode, the switching charger has five control loops to regulate input current, charge current, charge voltage, input voltage MIVR and device junction temperature. During the charging process, all five loops (if MIVR is enabled) are enabled and the dominant one will take over the control.

For normal charging process, the Li-ion or Li-polymer battery is charged in three charging modes depending on the battery voltage. At the beginning of the charging process, the switching charger is in pre-charge mode. When the battery voltage rises above pre-charge threshold

RICHTEK is a registered trademark of Richtek Technology Corporation.

RT5037 Preliminary

voltage (V<sub>PREC</sub>), the switching charger enters fast-charge mode. Once the battery voltage is close to the regulation voltage (V<sub>BATREG</sub>), the switching charger enters constant voltage mode.

### **Pre-Charge Mode**

For life-cycle consideration, the battery cannot be charged with large current under low battery condition. When the VBATS pin voltage is below pre-charge threshold voltage (V<sub>PREC</sub>), the charger is in pre-charge mode with a weak charge current witch equals to the pre-charge current (I<sub>PREC</sub>). In pre-charge mode, the charger basically works as a Linear Charger. The pre-charge current also acts as the current limit when the VBATS pin is shorted.

The Pre-Charge current levels are 150mA to 450mA programmed by I<sup>2</sup>C per 100mA.

Table 2. VPREC Register Setting Table

| VPREC[2:0] | Pre-Charge Threshold |

|------------|----------------------|

| 0000       | 2.3V                 |

| 0001       | 2.4V                 |

| 0010       | 2.5V                 |

| 0011       | 2.6V                 |

| 0100       | 2.7V                 |

| 0101       | 2.8V                 |

| 0110       | 2.9V                 |

| 0111       | 3V                   |

| 1000       | 3.1V                 |

| 1001       | 3.2V                 |

| 1010       | 3.3V                 |

| 1011       | 3.4V                 |

| 1100       | 3.5V (Default)       |

| 1101       | 3.6V                 |

| 1110       | 3.7V                 |

| 1111       | 3.8V                 |

Table 3. IPREC Register Setting Table

| IPREC[1:0] | Pre-Charge Current |

|------------|--------------------|

| 00         | 150mA (Default)    |

| 01         | 250mA              |

| 10         | 350mA              |

| 11         | 450mA              |

### **Fast-Charge Mode and Settings**

As the VBATS pin rises above V<sub>PREC</sub>, the charger enters fast-charge mode and starts switching. Notice that the switching charger does not integrate input power source (AC adapter or USB input) detection. Thus, the switching charger does not set the charge current automatically. Unlike the linear charger (LDO), the switching charger (Buck converter) is a current amplifier. The current drawn by the switching charger is different from the current into the battery. The user can set the Average Input Current Regulation (AICR) and output charge current (I<sub>CHRG</sub>) respectively.

### Cycle-by-Cycle Current Limit

The charger of the switching charger has an embedded cycle-by-cycle current limit for inductor. Once the inductor current touches the threshold, the charger stops charging immediately to prevent over current from damaging the device. Notice that, the mechanism cannot be disabled by any way.

### **Average Input Current Regulation (AICR)**

The AICR setting is controlled by I<sup>2</sup>C. The AICR100 mode limits the input current to 100mA. The AICR500 mode limits the input current to 500mA.. If the application does not need input current limit, it can be disabled also.

The AICR levels are as below table and programmed by I<sup>2</sup>C and suitable for USB port and several TA types (5V/ 0.7A, 5V/1A, 5V/2A).

Table 4. AICR Register Setting Table

| AICR[2:0] | I <sub>AICR</sub> |

|-----------|-------------------|

| 000       | Disable           |

| 001       | 0.1A              |

| 010       | 0.5A              |

| 011       | 0.7A              |

| 100       | 0.9A (Default)    |

| 101       | 1A                |

| 110       | 1.5A              |

| 111       | 2A                |

#### Charge Current (I<sub>CHRG</sub>)

The charge current into the battery is determined by the sense resistor ( $R_{SENSE}$ ) and ICC setting by I<sup>2</sup>C. The voltage between the ISENSP and ISENSN pins is regulated to the voltage control by ICC setting.

As the R<sub>SENSE</sub> is  $20m\Omega$ , the Fast-Charge currents are 700mA to 2A programmed by I<sup>2</sup>C per 100mA.

**Table 5. ICHG Register Setting Table**

| ICHG[3:0] | VCC  | ICHG R <sub>SENSE</sub> is $20m\Omega$ |

|-----------|------|----------------------------------------|

| 0000      | 10mV | 0.5A                                   |

| 0001      | 12mV | 0.6A                                   |

| 0010      | 14mV | 0.7A                                   |

| 0011      | 16mV | 0.8A                                   |

| 0100      | 18mV | 0.9A                                   |

| 0101      | 20mV | 1A                                     |

| 0110      | 22mV | 1.1A                                   |

| 0111      | 24mV | 1.2A                                   |

| 1000      | 26mV | 1.3A                                   |

| 1001      | 28mV | 1.4A                                   |

| 1010      | 30mV | 1.5A (Default)                         |

| 1011      | 32mV | 1.6A                                   |

| 1100      | 34mV | 1.7A                                   |

| 1101      | 36mV | 1.8A                                   |

| 1110      | 38mV | 1.9A                                   |

| 1111      | 40mV | 2A                                     |

### **Constant Voltage Mode and Settings**

The switching charger enters constant voltage mode when the ISENSN voltage is close to the output-charge voltage ( $V_{BATREG}$ ). Once in this mode, the charge current begins to decrease. For default settings (charge current termination is disabled), the switching charger does not turn off and always regulates the battery voltage at  $V_{BATREG}$ . However, once the charge current termination is enabled, the charger terminates if the charge current is below termination current ( $I_{EOC}$ ) in constant-voltage mode. The charge current termination function is controlled by the  $I^2C$  interface. After termination, a new charge cycle restarts when one of the following conditions is detected:

- ► The VBATS pin voltage falls below the VBATREG as V<sub>REC</sub> threshold.

- → VINCHG Power-On Reset (POR).

- ▶ Charge or Termination Enable bit toggle or Charger reset (via I<sup>2</sup>C interface).

### **Output Charge Voltage (VBATREG)**

The output-charge voltage is set by the I<sup>2</sup>C interface. Its range is from 3.65V to 4.4V per 25mV.

### **Termination Current (IEOC)**

If the charger current termination is enabled (TE bit = "1"), the end-of-charge current is determined by both the termination current sense voltage ( $V_{EOC}$ ) and sense resistor ( $R_{SENSE}$ ). As  $R_{SENSE}$  is  $20m\Omega$ ,  $I_{EOC}$  is set by the  $I^2C$  interface from 150mA to 600mA per 50mA.

Table 6. EOC Register Setting Table

| EOC[2:0] | VEOC    | IEOC R <sub>SENSE</sub> is 20m $\Omega$ |

|----------|---------|-----------------------------------------|

| 000      | Disable | Disable                                 |

| 001      | 3mV     | 150mA                                   |

| 010      | 4mV     | 200mA                                   |

| 011      | 5mV     | 250mA (default)                         |

| 100      | 6mV     | 300mA                                   |

| 101      | 8mV     | 400mA                                   |

| 110      | 10mV    | 500mA                                   |

| 111      | 12mV    | 600mA                                   |

RT5037 Preliminary RICHTEK

### Input Voltage Protection in Charge Mode

During charge mode, there are two protection mechanisms against if input power source capability is less than the charging current setting. One is AICR and the other is minimum input voltage regulation. A suitable level of AICR can prevent VINCHG drop by the insufficient capability. As the AICR setting is not suitable, MIVR will regulate the VINCHG in the setting level and sink the maximum current of power source.

### Sleep Mode ( $V_{VINCHG} - V_{VBATS} < V_{SLP}$ )

The switching charger enters sleep mode if the voltage drop between the VINCHG and VBATS pins falls below VSLP. In sleep mode, the reverse blocking switch and PWM are all turned off. This function prevents battery drain during poor or no input power source.

### **Input Over Voltage Protection**

When VINCHG rises above the input over voltage threshold, the switching charger stops charging and then sets fault status bits. The condition is released when VINCHG falls below OVP threshold. The switching charger then resumes charging operation.

### **Reverse Boost Mode Operation (OTG)**

### **Trigger and Operation**

The switching charger features OTG-Boost support. When OTG function is enabled, the synchronous boost control loop takes over the power MOSFETs and reverses the power flow from the battery to the VINCHG pin. In normal boost mode, the VMIDCHG pin is regulated to 5V (typ.) to support other OTG devices connected to the USB connector.

### **Output Over-Voltage Protection**

In boost mode, the output over voltage protection is triggered when the VMIDCHG voltage is above the output OVP threshold. When OVP occurs, the boost converter stops switching and turns off immediately.

### **Battery Protection**

### **Battery Over-Voltage Protection in Charge Mode**

The switching charger monitors the ISENSN voltage for output over voltage protection. In charge mode, if the ISENSN voltage rises above V<sub>OVP BAT</sub> x V<sub>BATREG</sub>, such as when the battery is suddenly removed, the switching charger stops charging and then sets fault status bits and sends out fault pulse at the STAT pin. The condition is released when the ISENSN voltage falls below (V<sub>OVP BAT</sub> –  $\Delta V_{\text{OVP\_BAT}})$  x  $V_{\text{OVP\_BAT}}.$  The switching charger then resumes charging process with default settings and the fault is cleared.

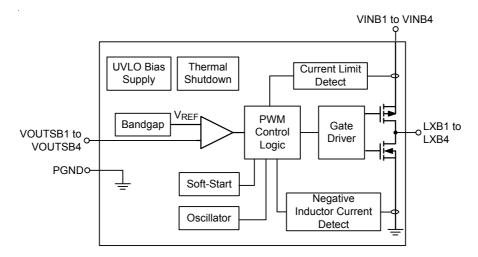

#### **Bucks**

The RT5037 includes a synchronous step-down DC/DC converter that can support the input voltage range from 2.7V to 5.5V. The output current is up to 600mA. The output voltage can be programmable by I<sup>2</sup>C. Following shows the function block of the RT5037 buck.

Figure 2. Buck Function Block Diagram

Normally, the high-side MOSFET is turned on by the PWM control logic block which drives the gate driver block when VOUTSB1 to VOUTSB4 is lower than the internal reference voltage. After VOUTSB1 to VOUTSB4 is higher than the internal reference voltage, the high side MOSFET will be turned off. While the high side MOSFET is turned off, the low side MOSFET is turned on until the current of the inductor is around zero by the negative inductor current detection block.

When the current of high side MOSFET is over the rating current, the high side MOSFET is turned off. When the temperature is over the rating temperature, the high side

MOSFET is turned off until the temperature is dropped by the thermal shutdown block. After the thermal shutdown is released, VOUTSB1 to VOUTSB4 will be soft-started again.

### **IRQ** Operation

RT5037 summarize all IRQ items in the register table. All IRQ\_status registers are implemented as reset after read. And IRQ pin is released only after IRQ\_PRez bit is set. If IRQ Mask bit is High, the IRQ\_status bit will not update status. IRQ\_enable will mask IRQ\_status to trigger IRQ Low, so the system can decide which interrupt is necessary.