# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **DDR Termination Regulator**

#### **General Description**

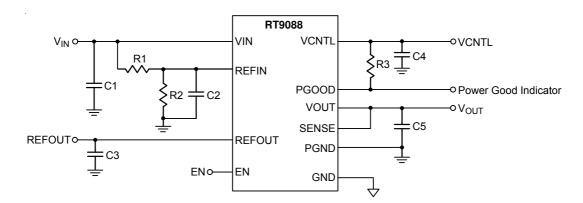

The RT9088 is a sink/source tracking termination regulator. It is specifically designed for low-cost and low-external component count systems. The RT9088 possesses a high speed operating amplifier that provides fast load transient response and only requires a minimum  $30\mu$ F ceramic output capacitor. The RT9088 supports remote sensing functions and all features required to power the DDRIII and Low Power DDRIII / DDRIV VTT bus termination according to the JEDEC specification. In addition, the RT9088 provides an open-drain PGOOD signal to monitor the output regulation and an EN signal that can be used to discharge VTT during S3 (suspend to RAM) for DDR applications.

The RT9088 is available in the thermal efficient package, WDFN-10L 3x3.

### **Marking Information**

63= : Product Code YMDNN : Date Code

### Features

- VIN Input Voltage Range: 1.1V to 3.5V

- VCNTL Input Voltage Range: 2.9V to 5.5V

- Support Ceramic Capacitors

- Power Good Indicator

- 10mA Source/Sink Reference Output

- Meet DDRI, DDRII JEDEC Spec

- Support DDRIII, Low Power DDRIII/DDRIV VTT Applications

- Soft-Start Function

- UVLO and OCP Protection

- Thermal Shutdown

### **Applications**

- Notebook/Desktop/Server

- Telecom/Datacom, GSM Base Station, LCD-TV/PDP-TV, Copier/Printer, Set-Top Box

#### **Simplified Application Circuit**

### **Ordering Information**

RT9088

Package Type QW : WDFN-10L 3x3 (W-Type)

—Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Functional Pin Description**

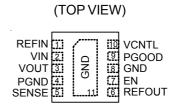

### **Pin Configurations**

WDFN-10L 3x3

| Pin No.                | Pin Name | Pin Function                                                                                                                                                             |

|------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | REFIN    | Reference Input.                                                                                                                                                         |

| 2                      | VIN      | Power Input of the Regulator.                                                                                                                                            |

| 3                      | VOUT     | Power Output of the Regulator.                                                                                                                                           |

| 4                      | PGND     | Power Ground of the Regulator.                                                                                                                                           |

| 5                      | SENSE    | Voltage Sense Input for the Regulator. Connect to positive terminal of the output capacitor or the load.                                                                 |

| 6                      | REFOUT   | Reference Output. Connect to GND through a 0.1µF ceramic capacitor.                                                                                                      |

| 7                      | EN       | Enable Control Input. For DDR VTT application, connect EN to SLP_S3. For other applications, use EN as the ON/OFF function.                                              |

| 9                      | PGOOD    | Power Good Open-Drain Output. Connect a pull-up resistor between this pin and VCNTL pin.                                                                                 |

| 10                     | VCNTL    | Control Voltage Input. Connect this pin to the 3.3V or 5V power supply. A ceramic decoupling capacitor with a value $4.7\mu$ F is required.                              |

| 8,<br>11 (Exposed Pad) | GND      | Analog Ground. Connect to negative terminal of the output capacitor. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation. |

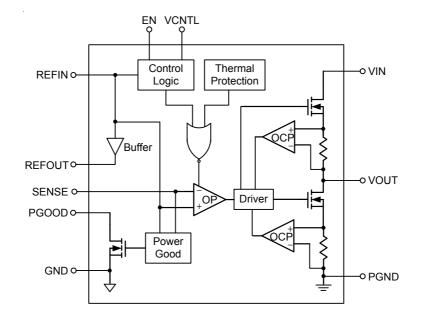

### **Function Block Diagram**

### Operation

The RT9088 is a linear sink/source DDR termination regulator with current capability up to 3A. The RT9088 builds in a high-side N-MOSFET which provides current sourcing and a low-side N-MOSFET which provides current sinking. All the control circuits are supplied by the power VCNTL. In normal operation, the error amplifier OP adjusts the gate driving voltage of the power MOSFET to achieve SENSE voltage well tracking the REFIN voltage.

Both the source and sink currents are detected by the internal sensing resistor, and the OCP function will work to limit the current to a designed value when overload happens. Furthermore, the current will be folded back to be one half if VOUT is out of the power good window.

#### Buffer

This function provides REFOUT output equal to REFIN with 10mA source/sink current capability.

#### **Power Good**

When the SENSE voltage is in the power good window and lasts for a certain delay time, then the PGOOD pin will be high impedance and the PGOOD voltage will be pulled high by the external resistor.

#### **Control Logic**

This block includes VCNTL UVLO, REFIN UVLO and Enable/Disable functions, and provides logic control to the whole chip.

#### **Thermal Protection**

Both the high-side and low-side power MOSFETs will be turned off when the junction temperature is higher than typically 160°C, and be released to normal operation when junction temperature falls below 120°C typically.

# **RT9088**

### Absolute Maximum Ratings (Note 1)

| <ul> <li>Supply Voltage, VIN, VCNTL</li></ul>                                                    | 0.3V to 6V     |

|--------------------------------------------------------------------------------------------------|----------------|

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> <li>WDFN-10L 3x3</li></ul> | ۸۱/۲۵ ک        |

| Package Thermal Resistance (Note 2)                                                              | 3.27 W         |

| WDFN-10L 3x3, $\theta_{JA}$                                                                      | 30.5°C/W       |

| WDFN-10L 3x3, $\theta_{JC}$                                                                      | 7.5°C/W        |

| Lead Temperature (Soldering, 10 sec.)                                                            | 260°C          |

| Junction Temperature                                                                             | 150°C          |

| Storage Temperature Range                                                                        | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                                      |                |

| HBM (Human Body Model)                                                                           | 2kV            |

### Recommended Operating Conditions (Note 4)

| Control Input Voltage, VCNTL | - 2.9V to 5.5V |

|------------------------------|----------------|

| Supply Input Voltage, VIN    | - 1.1V to 3.5V |

| Junction Temperature Range   | 40°C to 125°C  |

| Ambient Temperature Range    | 40°C to 85°C   |

### **Electrical Characteristics**

$(V_{\text{IN}} = 1.5\text{V}, V_{\text{EN}} = V_{\text{CNTL}} = 3.3\text{V}, V_{\text{REFIN}} = V_{\text{SENSE}} = 0.75\text{V}, C_{\text{OUT}} = 10\mu\text{F x 3}, T_{\text{A}} = 25^{\circ}\text{C}, \text{ unless otherwise specified})$

| Parameter                           | Symbol                | Test Conditions                                                                     | Min | Тур   | Max | Unit |

|-------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-----|-------|-----|------|

| Supply Current                      |                       |                                                                                     |     |       |     |      |

| VCNTL Supply Current                | IVCNTL                | V <sub>EN</sub> = V <sub>CNTL</sub> , No Load                                       | 0.7 | 1     | mA  |      |

| VCNTL Shutdown Current              | ISHDN_VCNTL           | V <sub>EN</sub> = 0V, V <sub>REFIN</sub> = 0V, No Load                              |     | 65    | 80  | μA   |

|                                     |                       | $V_{EN}$ = 0V, $V_{REFIN}$ > 0.4V, No Load                                          |     | 200   | 400 | μA   |

| VIN Supply Current                  | I <sub>VIN</sub>      | V <sub>EN</sub> = V <sub>CNTL</sub> , No Load                                       |     | 1     | 50  | μA   |

| VIN Shutdown Current                | I <sub>SHDN_VIN</sub> | V <sub>EN</sub> = 0V, No Load                                                       |     | 0.1   | 50  | μA   |

| Output                              |                       | •                                                                                   |     |       |     | •    |

|                                     | Vout                  | V <sub>IN</sub> = 1.5V, V <sub>REFIN</sub> = 0.75V,<br>I <sub>OUT</sub> = 0A        |     | 0.75  |     | V    |

| VTT Output Voltage                  |                       | V <sub>IN</sub> = 1.35V, V <sub>REFIN</sub> = 0.675V,<br>I <sub>OUT</sub> = 0A      |     | 0.675 |     | V    |

|                                     |                       | $V_{IN}$ = 1.2V, $V_{REFIN}$ = 0.6V,<br>$I_{OUT}$ = 0A                              |     | 0.6   |     | V    |

|                                     |                       | $I_{OUT} = \pm 2A$ , $V_{LDOIN} = 1.5V$ ,<br>$V_{REFOUT} = 0.75V$                   | -25 |       | 25  |      |

| REFIN, VTT Output<br>Voltage Offset | V <sub>OUT_OS</sub>   | I <sub>OUT</sub> = ±2A, V <sub>LDOIN</sub> = 1.35V,<br>V <sub>REFOUT</sub> = 0.675V | -25 |       | 25  | mV   |

|                                     |                       | $I_{OUT} = \pm 2A$ , $V_{LDOIN} = 1.2V$ ,<br>$V_{REFOUT} = 0.6V$                    | -25 |       | 25  |      |

# **RT9088**

| Parameter                     |            | Symbol                     | Test Conditions                                                                   | Min | Тур | Max  | Unit |  |

|-------------------------------|------------|----------------------------|-----------------------------------------------------------------------------------|-----|-----|------|------|--|

| VOUT Source Curr              | rent Limit | I <sub>LIM_VOUT_SR</sub>   | VOUT in PGOOD Window                                                              | 3.5 |     | 5.5  | Α    |  |

| VOUT Sink Curren              | ıt Limit   | I <sub>LIM_VOUT_SK</sub>   | VOUT in PGOOD Window 3.5                                                          |     |     | 5.5  | Α    |  |

| VOUT Discharge<br>Resistance  |            | RDISCHARGE                 | $V_{REFIN}$ = 0V, $V_{OUT}$ = 0.3V,<br>$V_{EN}$ = 0V                              |     | 18  | 25   | Ω    |  |

| Power Good Com                | parator    | •                          |                                                                                   |     | -   |      |      |  |

| PGOOD Threshold               |            |                            | V <sub>SENSE</sub> lower threshold with respect to REFOUT                         | -25 | -20 | -15  | %    |  |

|                               |            | Vth_pgood                  | V <sub>SENSE</sub> upper threshold with respect to REFOUT                         | 15  | 20  | 25   |      |  |

|                               |            |                            | PGOOD Hysteresis                                                                  |     | 5   |      | 1    |  |

| PGOOD Start-Up [              | Delay      | T <sub>PGDELAY1</sub>      | Start-up rising delay, V <sub>SENSE</sub><br>within PGOOD range                   |     | 2   |      | ms   |  |

| Output Low Voltage            | е          | VLOW_PGOOD                 | I <sub>PGOOD</sub> = 4mA                                                          |     |     | 0.4  | V    |  |

| PGOOD Falling De              | elay       | T <sub>PGDELAY2</sub>      | Falling delay, V <sub>SENSE</sub> is out of PGOOD range                           |     | 10  |      | μS   |  |

| Leakage Current               |            | ILEAKAGE _PGOOD            | $V_{SENSE} = V_{REFIN}$ (PGOOD<br>high impedance),<br>$V_{PGOOD} = V_{IN} + 0.3V$ |     |     | 1    | μA   |  |

| <b>REFIN and REFO</b>         | UT         | •                          |                                                                                   |     | -   |      |      |  |

| REFIN Input Current           |            | I <sub>REFIN</sub>         | V <sub>EN</sub> = V <sub>CNTL</sub>                                               |     |     | 1    | μA   |  |

| REFIN Voltage Ra              | nge        | V <sub>REFIN</sub>         |                                                                                   | 0.5 |     | 1.8  | V    |  |

| REFIN Under-Volta             | age        | VUVLO_REFIN                | REFIN Rising                                                                      | 360 | 390 | 420  | ) mV |  |

| Lockout                       |            |                            | Hysteresis                                                                        |     | 20  |      |      |  |

|                               |            |                            | –10mA < I <sub>REFOUT</sub> < 10mA,<br>V <sub>REFIN</sub> = 0.75V                 | -15 |     | 15   |      |  |

| REFOUT Voltage T<br>to VREFIN | Tolerance  | VTOL_REFOUT                | −10mA < I <sub>REFOUT</sub> < 10mA,<br>V <sub>REFIN</sub> = 0.675V                | -15 |     | 15   | mV   |  |

|                               |            |                            | –10mA < I <sub>REFOUT</sub> < 10mA,<br>V <sub>REFIN</sub> = 0.6V                  | -15 |     | 15   |      |  |

| REFOUT Source C<br>Limit      | Current    | ILIM_REFOUT_SR             | V <sub>REFOUT</sub> = 0V                                                          | 10  | 40  |      | mA   |  |

| REFOUT Sink Current Limit     |            | I <sub>LIM_REFOUT_SK</sub> | V <sub>REFOUT</sub> = REFIN + 1V                                                  | 10  | 40  |      | mA   |  |

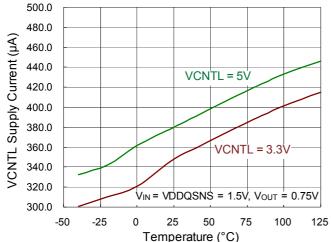

| UVLO/EN                       |            |                            |                                                                                   |     |     |      |      |  |

| UVLO Threshold                |            | VUVLO_VCNTL                | Rising                                                                            | 2.5 | 2.7 | 2.85 | V    |  |

|                               |            |                            | Hysteresis                                                                        |     | 120 |      | mV   |  |

|                               | .ogic-High | V <sub>IN_H</sub>          |                                                                                   | 1.7 |     |      | V    |  |

| Voltage L                     | ogic-Low   | V <sub>IN_L</sub>          |                                                                                   |     |     | 0.3  | v    |  |

| Thermal Shutdow               | /n         |                            |                                                                                   |     |     |      |      |  |

| Thermal Shutdown              |            | T <sub>SD</sub>            | Shutdown Temperature                                                              |     | 160 |      | - °C |  |

| Threshold                     |            | י סט<br>                   | Hysteresis                                                                        |     | 15  |      |      |  |

# **RT9088**

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

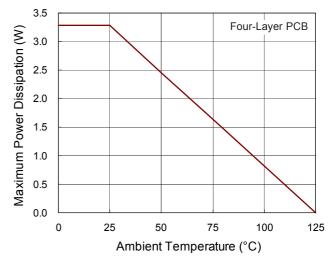

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

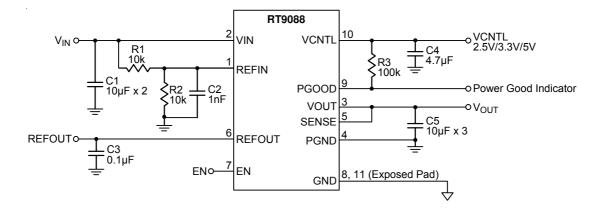

### **Typical Application Circuit**

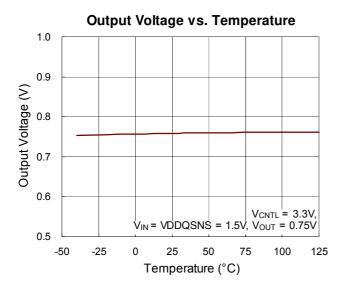

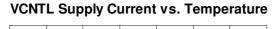

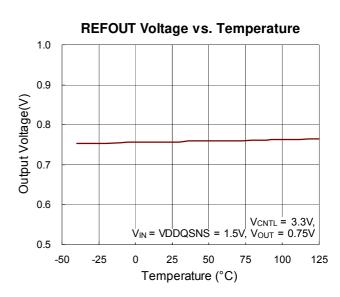

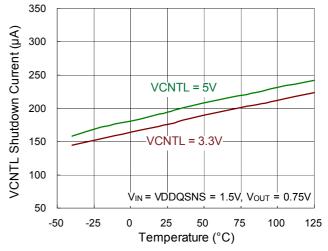

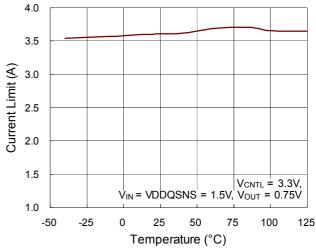

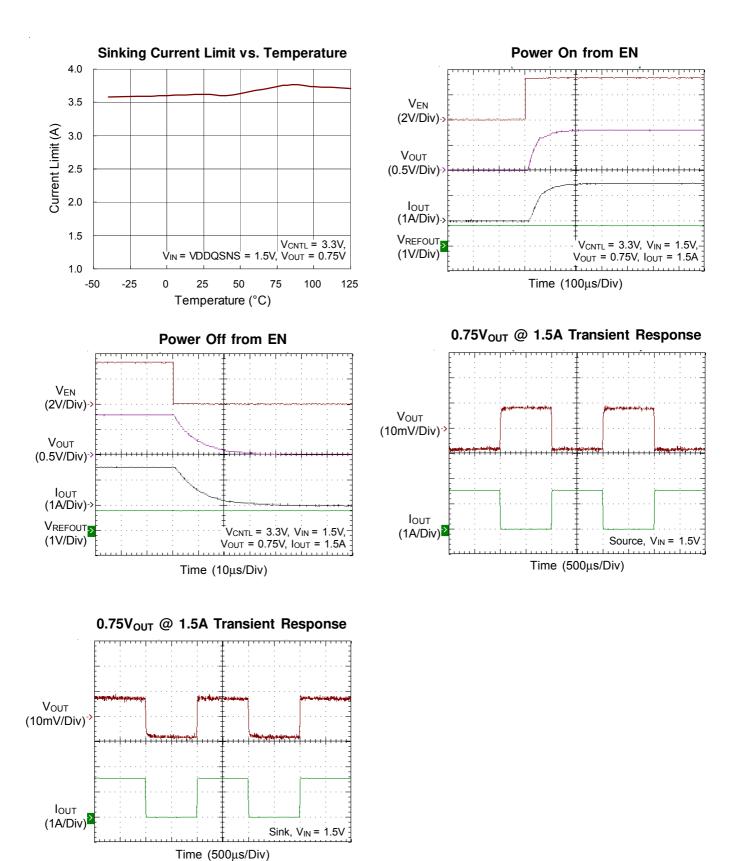

### **Typical Operating Characteristics**

VCNTL Shutdown Current vs. Temperature

Sourcing Current Limit vs. Temperature

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

8

### **Application Information**

The RT9088 is a 3.5A sink/source tracking termination regulator. It is specifically designed for low-cost and low-external component count system such as notebook PC applications. The RT9088 possesses a high speed operating amplifier that provides fast load transient response and only requires two  $10\mu$ F ceramic input capacitors and three  $10\mu$ F ceramic output capacitors.

#### **Capacitor Selection**

Good bypassing is recommended from VLDOIN to GND to help improve AC performance. A  $10\mu$ F or greater input capacitor located as close as possible to the IC is recommended. The input capacitor must be located at a distance of less than 0.5 inches from the VLDOIN pin of the IC.

Adding a  $1\mu$ F ceramic capacitor close to the VIN pin and it should be kept away from any parasitic impedance from the supply power. For stable operation, the total capacitance of the ceramic capacitor at the VTT output terminal must be larger than  $30\mu$ F. The RT9088 is designed specifically to work with low ESR ceramic output capacitor in space saving and performance consideration. Larger output capacitance can reduce the noise and improve load transient response, stability and PSRR. The output capacitor should be located near the VTT output terminal pin as close as possible.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For

WDFN-10L 3x3 package, the thermal resistance,  $\theta_{JA}$ , is 30.5°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})}$  = (125°C - 25°C) / (30.5°C/W) = 3.27W for WDFN-10L 3x3 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve of Maximum Power Dissipation

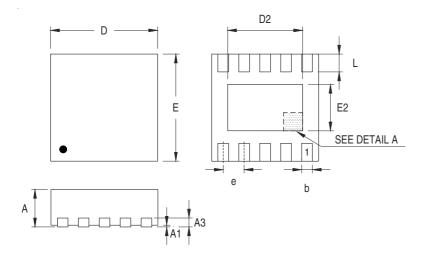

### **Outline Dimension**

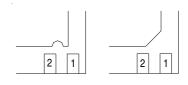

DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions | n Millimeters | Dimensions In Inches |       |  |

|--------|------------|---------------|----------------------|-------|--|

|        | Min        | Max           | Min                  | Max   |  |

| А      | 0.700      | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000      | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250         | 0.007                | 0.010 |  |

| b      | 0.180      | 0.300         | 0.007                | 0.012 |  |

| D      | 2.950      | 3.050         | 0.116                | 0.120 |  |

| D2     | 2.300      | 2.650         | 0.091                | 0.104 |  |

| E      | 2.950      | 3.050         | 0.116                | 0.120 |  |

| E2     | 1.500      | 1.750         | 0.059                | 0.069 |  |

| е      | 0.500      |               | 0.020                |       |  |

| L      | 0.350      | 0.450         | 0.014                | 0.018 |  |

W-Type 10L DFN 3x3 Package

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.