# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

The S-1004 Series is a high-accuracy voltage detector developed using CMOS technology. The detection voltage is fixed

Apart from the power supply pin, the detection voltage input pin (SENSE pin) is also prepared, so the output is stable even

The release signal can be delayed by setting a capacitor externally, and the release delay time accuracy at Ta = +25°C is

internally with an accuracy of  $\pm 1.0\%$  ( $-V_{DET(S)} \ge 2.2$  V). It operates with current consumption of 500 nA typ.

• Detection voltage: 1.0 V to 5.0 V (0.1 V step)

Two output forms Nch open-drain output and CMOS output are available.

• Detection voltage accuracy:  $\pm 1.0\%$  (2.2 V  $\leq -V_{DET(S)} \leq 5.0$  V)  $\pm 22 \text{ mV} (1.0 \text{ V} \le -V_{\text{DET}(S)} < 2.2 \text{ V})$

500 nA typ.

5% ± 2%

0.95 V to 10.0 V

- Current consumption:

- Operation voltage range:

- Hysteresis width:

- Release delay time accuracy:

- ±15% (C<sub>D</sub> = 4.7 nF, Ta = +25°C) • Output form: Nch open-drain output (Active "L")

- CMOS output (Active "L")

- Operation temperature range: Ta =  $-40^{\circ}$ C to  $+85^{\circ}$ C

- · Lead-free (Sn 100%), halogen-free

### Applications

- · Power supply monitor for microcomputer and reset for CPU

- Constant voltage power supply monitor for TV, Blu-ray recorder and home appliance

- · Power supply monitor for portable devices such as notebook PC, digital still camera and mobile phone

#### Packages

- SOT-23-5

- SNT-6A

## **BUILT-IN DELAY CIRCUIT (EXTERNAL DELAY TIME SETTING) VOLTAGE DETECTOR WITH SENSE PIN**

S-1004 Series

Rev.2.1 01

# SII

if the SENSE pin falls to 0 V.

© SII Semiconductor Corporation, 2014

www.sii-ic.com

±15%.

Features

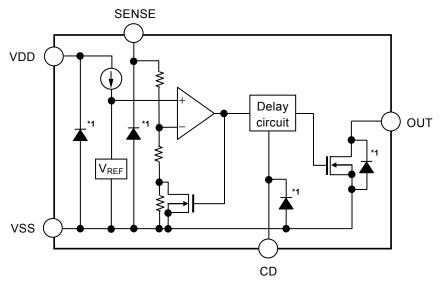

#### Block Diagrams

1. S-1004 Series NA / NB type (Nch open-drain output)

| Function     | Status     |

|--------------|------------|

| Output logic | Active "L" |

\*1. Parasitic diode

Figure 1

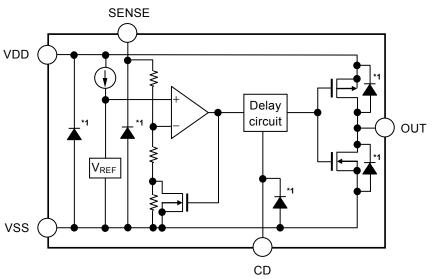

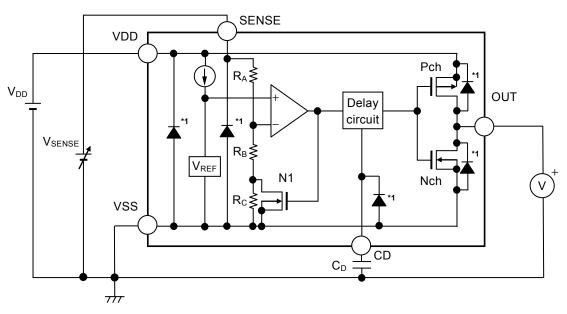

#### 2. S-1004 Series CA / CB type (CMOS output)

**\*1.** Parasitic diode

Figure 2

| Function     | Status     |

|--------------|------------|

| Output logic | Active "L" |

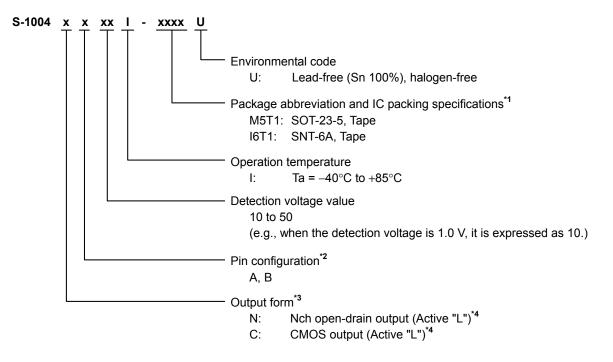

#### Product Name Structure

Users can select the output form and detection voltage value for the S-1004 Series. Refer to "1. Product name" regarding the contents of product name, "2. Function list of product types" regarding the product types, "3. Packages" regarding the package drawings and "4. Product name list" regarding details of product name.

#### 1. Product name

- \*1. Refer to the tape drawing.

- \*2. Refer to "■ Pin Configurations".

- \*3. Refer to "2. Function list of product types".

- \*4. If you request the product with output logic active "H", contact our sales office.

#### 2. Function list of product types

Table 1

| Product Type | Output Form           | Output Logic | Pin Configuration | Package          |

|--------------|-----------------------|--------------|-------------------|------------------|

| NA           | Neb open drein eutrut | Active "L"   | А                 | SOT-23-5, SNT-6A |

| NB           | Nch open-drain output | Active "L"   | В                 | SOT-23-5         |

| CA           | CMOS output           | Active "L"   | А                 | SOT-23-5, SNT-6A |

| СВ           |                       | Active "L"   | В                 | SOT-23-5         |

#### 3. Packages

| Table 2 Package Drawing C | odes |

|---------------------------|------|

|---------------------------|------|

| Package Name | Dimension    | Таре         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| SOT-23-5     | MP005-A-P-SD | MP005-A-C-SD | MP005-A-R-SD | -            |

| SNT-6A       | PG006-A-P-SD | PG006-A-C-SD | PG006-A-R-SD | PG006-A-L-SD |

#### 4. Product name list

#### 4.1 S-1004 Series NA type

Output form: Nch open-drain output (Active "L")

| Table 3                           |                   |                   |

|-----------------------------------|-------------------|-------------------|

| Detection Voltage                 | SOT-23-5          | SNT-6A            |

| $1.0 \text{ V} \pm 22 \text{ mV}$ | S-1004NA10I-M5T1U | S-1004NA10I-I6T1U |

| $1.1 \text{ V} \pm 22 \text{ mV}$ | S-1004NA11I-M5T1U | S-1004NA11I-I6T1U |

| $1.2 \text{ V} \pm 22 \text{ mV}$ | S-1004NA12I-M5T1U | S-1004NA12I-I6T1U |

| $1.3 \text{ V} \pm 22 \text{ mV}$ | S-1004NA13I-M5T1U | S-1004NA13I-I6T1U |

| $1.4 \text{ V} \pm 22 \text{ mV}$ | S-1004NA14I-M5T1U | S-1004NA14I-I6T1U |

| $1.5 \text{ V} \pm 22 \text{ mV}$ | S-1004NA15I-M5T1U | S-1004NA15I-I6T1U |

| $1.6 \text{ V} \pm 22 \text{ mV}$ | S-1004NA16I-M5T1U | S-1004NA16I-I6T1U |

| $1.7 \text{ V} \pm 22 \text{ mV}$ | S-1004NA17I-M5T1U | S-1004NA17I-I6T1U |

| $1.8 \text{ V} \pm 22 \text{ mV}$ | S-1004NA18I-M5T1U | S-1004NA18I-I6T1U |

| $1.9 \text{ V} \pm 22 \text{ mV}$ | S-1004NA19I-M5T1U | S-1004NA19I-I6T1U |

| $2.0 \text{ V} \pm 22 \text{ mV}$ | S-1004NA20I-M5T1U | S-1004NA20I-I6T1U |

| $2.1~V\pm22~mV$                   | S-1004NA21I-M5T1U | S-1004NA21I-I6T1U |

| $2.2~V\pm1.0\%$                   | S-1004NA22I-M5T1U | S-1004NA22I-I6T1U |

| $2.3~V\pm1.0\%$                   | S-1004NA23I-M5T1U | S-1004NA23I-I6T1U |

| $2.4 \text{ V} \pm 1.0\%$         | S-1004NA24I-M5T1U | S-1004NA24I-I6T1U |

| $2.5 \text{ V} \pm 1.0\%$         | S-1004NA25I-M5T1U | S-1004NA25I-I6T1U |

| 2.6 V ± 1.0%                      | S-1004NA26I-M5T1U | S-1004NA26I-I6T1U |

| 2.7 V ± 1.0%                      | S-1004NA27I-M5T1U | S-1004NA27I-I6T1U |

| 2.8 V ± 1.0%                      | S-1004NA28I-M5T1U | S-1004NA28I-I6T1U |

| 2.9 V ± 1.0%                      | S-1004NA29I-M5T1U | S-1004NA29I-I6T1U |

| 3.0 V ± 1.0%                      | S-1004NA30I-M5T1U | S-1004NA30I-I6T1U |

| 3.1 V ± 1.0%                      | S-1004NA31I-M5T1U | S-1004NA31I-I6T1U |

| 3.2 V ± 1.0%                      | S-1004NA32I-M5T1U | S-1004NA32I-I6T1U |

| 3.3 V ± 1.0%                      | S-1004NA33I-M5T1U | S-1004NA33I-I6T1U |

| 3.4 V ± 1.0%                      | S-1004NA34I-M5T1U | S-1004NA34I-I6T1U |

| 3.5 V ± 1.0%                      | S-1004NA35I-M5T1U | S-1004NA35I-I6T1U |

| 3.6 V ± 1.0%                      | S-1004NA36I-M5T1U | S-1004NA36I-I6T1U |

| 3.7 V ± 1.0%                      | S-1004NA37I-M5T1U | S-1004NA37I-I6T1U |

| 3.8 V ± 1.0%                      | S-1004NA38I-M5T1U | S-1004NA38I-I6T1U |

| 3.9 V ± 1.0%                      | S-1004NA39I-M5T1U | S-1004NA39I-I6T1U |

| 4.0 V ± 1.0%                      | S-1004NA40I-M5T1U | S-1004NA40I-I6T1U |

| 4.1 V ± 1.0%                      | S-1004NA41I-M5T1U | S-1004NA41I-I6T1U |

| 4.2 V ± 1.0%                      | S-1004NA42I-M5T1U | S-1004NA42I-I6T1U |

| 4.3 V ± 1.0%                      | S-1004NA43I-M5T1U | S-1004NA43I-I6T1U |

| 4.4 V ± 1.0%                      | S-1004NA44I-M5T1U | S-1004NA44I-I6T1U |

| 4.5 V ± 1.0%                      | S-1004NA45I-M5T1U | S-1004NA45I-I6T1U |

| 4.6 V ± 1.0%                      | S-1004NA46I-M5T1U | S-1004NA46I-I6T1U |

| 4.7 V ± 1.0%                      | S-1004NA47I-M5T1U | S-1004NA47I-I6T1U |

| 4.8 V ± 1.0%                      | S-1004NA48I-M5T1U | S-1004NA48I-I6T1U |

| $4.9 \text{ V} \pm 1.0\%$         | S-1004NA49I-M5T1U | S-1004NA49I-I6T1U |

| $5.0 \text{ V} \pm 1.0\%$         | S-1004NA50I-M5T1U | S-1004NA50I-I6T1U |

#### 4. 2 S-1004 Series NB type

Output form: Nch open-drain output (Active "L")

| Table 4                           |                   |  |

|-----------------------------------|-------------------|--|

| Detection Voltage                 | SOT-23-5          |  |

| $1.0 \text{ V} \pm 22 \text{ mV}$ | S-1004NB10I-M5T1U |  |

| $1.1 \text{ V} \pm 22 \text{ mV}$ | S-1004NB11I-M5T1U |  |

| $1.2 \text{ V} \pm 22 \text{ mV}$ | S-1004NB12I-M5T1U |  |

| 1.3 V ± 22 mV                     | S-1004NB13I-M5T1U |  |

| 1.4 V ± 22 mV                     | S-1004NB14I-M5T1U |  |

| 1.5 V ± 22 mV                     | S-1004NB15I-M5T1U |  |

| $1.6 \text{ V} \pm 22 \text{ mV}$ | S-1004NB16I-M5T1U |  |

| 1.7 V ± 22 mV                     | S-1004NB17I-M5T1U |  |

| $1.8 \text{ V} \pm 22 \text{ mV}$ | S-1004NB18I-M5T1U |  |

| $1.9 \text{ V} \pm 22 \text{ mV}$ | S-1004NB19I-M5T1U |  |

| $2.0 \text{ V} \pm 22 \text{ mV}$ | S-1004NB20I-M5T1U |  |

| $2.1 \text{ V} \pm 22 \text{ mV}$ | S-1004NB21I-M5T1U |  |

| $2.2~V\pm1.0\%$                   | S-1004NB22I-M5T1U |  |

| $2.3~V\pm1.0\%$                   | S-1004NB23I-M5T1U |  |

| $2.4~V\pm1.0\%$                   | S-1004NB24I-M5T1U |  |

| $2.5~V\pm1.0\%$                   | S-1004NB25I-M5T1U |  |

| $2.6~V\pm1.0\%$                   | S-1004NB26I-M5T1U |  |

| $2.7~V\pm1.0\%$                   | S-1004NB27I-M5T1U |  |

| $2.8~V\pm1.0\%$                   | S-1004NB28I-M5T1U |  |

| 2.9 V ± 1.0%                      | S-1004NB29I-M5T1U |  |

| 3.0 V ± 1.0%                      | S-1004NB30I-M5T1U |  |

| $3.1 \text{ V} \pm 1.0\%$         | S-1004NB31I-M5T1U |  |

| $3.2 \text{ V} \pm 1.0\%$         | S-1004NB32I-M5T1U |  |

| $3.3 \text{ V} \pm 1.0\%$         | S-1004NB33I-M5T1U |  |

| 3.4 V ± 1.0%                      | S-1004NB34I-M5T1U |  |

| $3.5~V\pm1.0\%$                   | S-1004NB35I-M5T1U |  |

| $3.6 \text{ V} \pm 1.0\%$         | S-1004NB36I-M5T1U |  |

| 3.7 V ± 1.0%                      | S-1004NB37I-M5T1U |  |

| 3.8 V ± 1.0%                      | S-1004NB38I-M5T1U |  |

| 3.9 V ± 1.0%                      | S-1004NB39I-M5T1U |  |

| $4.0 \text{ V} \pm 1.0\%$         | S-1004NB40I-M5T1U |  |

| 4.1 V ± 1.0%                      | S-1004NB41I-M5T1U |  |

| 4.2 V ± 1.0%                      | S-1004NB42I-M5T1U |  |

| 4.3 V ± 1.0%                      | S-1004NB43I-M5T1U |  |

| 4.4 V ± 1.0%                      | S-1004NB44I-M5T1U |  |

| $4.5 \text{ V} \pm 1.0\%$         | S-1004NB45I-M5T1U |  |

| 4.6 V ± 1.0%                      | S-1004NB46I-M5T1U |  |

| 4.7 V ± 1.0%                      | S-1004NB47I-M5T1U |  |

| 4.8 V ± 1.0%                      | S-1004NB48I-M5T1U |  |

| 4.9 V ± 1.0%                      | S-1004NB49I-M5T1U |  |

| 5.0 V ± 1.0%                      | S-1004NB50I-M5T1U |  |

#### BUILT-IN DELAY CIRCUIT (EXTERNAL DELAY TIME SETTING) VOLTAGE DETECTOR WITH SENSE PIN S-1004 Series Rev.2.1\_01

#### 4.3 S-1004 Series CA type

Output form: CMOS output (Active "L")

|                                   | Table 5           |                   |

|-----------------------------------|-------------------|-------------------|

| Detection Voltage                 | SOT-23-5          | SNT-6A            |

| $1.0 \text{ V} \pm 22 \text{ mV}$ | S-1004CA10I-M5T1U | S-1004CA10I-I6T1U |

| $1.1 \text{ V} \pm 22 \text{ mV}$ | S-1004CA11I-M5T1U | S-1004CA11I-I6T1U |

| $1.2 \text{ V} \pm 22 \text{ mV}$ | S-1004CA12I-M5T1U | S-1004CA12I-I6T1U |

| $1.3 \text{ V} \pm 22 \text{ mV}$ | S-1004CA13I-M5T1U | S-1004CA13I-I6T1U |

| $1.4 \text{ V} \pm 22 \text{ mV}$ | S-1004CA14I-M5T1U | S-1004CA14I-I6T1U |

| $1.5 \text{ V} \pm 22 \text{ mV}$ | S-1004CA15I-M5T1U | S-1004CA15I-I6T1U |

| $1.6 \text{ V} \pm 22 \text{ mV}$ | S-1004CA16I-M5T1U | S-1004CA16I-I6T1U |

| $1.7 \text{ V} \pm 22 \text{ mV}$ | S-1004CA17I-M5T1U | S-1004CA17I-I6T1U |

| $1.8 \text{ V} \pm 22 \text{ mV}$ | S-1004CA18I-M5T1U | S-1004CA18I-I6T1U |

| $1.9 \text{ V} \pm 22 \text{ mV}$ | S-1004CA19I-M5T1U | S-1004CA19I-I6T1U |

| $2.0 \text{ V} \pm 22 \text{ mV}$ | S-1004CA20I-M5T1U | S-1004CA20I-I6T1U |

| $2.1 \text{ V} \pm 22 \text{ mV}$ | S-1004CA21I-M5T1U | S-1004CA21I-I6T1U |

| $2.2~V\pm1.0\%$                   | S-1004CA22I-M5T1U | S-1004CA22I-I6T1U |

| $2.3~V\pm1.0\%$                   | S-1004CA23I-M5T1U | S-1004CA23I-I6T1U |

| $2.4~V\pm1.0\%$                   | S-1004CA24I-M5T1U | S-1004CA24I-I6T1U |

| $2.5~V\pm1.0\%$                   | S-1004CA25I-M5T1U | S-1004CA25I-I6T1U |

| $2.6~V\pm1.0\%$                   | S-1004CA26I-M5T1U | S-1004CA26I-I6T1U |

| $2.7~V\pm1.0\%$                   | S-1004CA27I-M5T1U | S-1004CA27I-I6T1U |

| $2.8~V\pm1.0\%$                   | S-1004CA28I-M5T1U | S-1004CA28I-I6T1U |

| $2.9~\text{V}\pm1.0\%$            | S-1004CA29I-M5T1U | S-1004CA29I-I6T1U |

| $3.0~V\pm1.0\%$                   | S-1004CA30I-M5T1U | S-1004CA30I-I6T1U |

| $3.1~V\pm1.0\%$                   | S-1004CA31I-M5T1U | S-1004CA31I-I6T1U |

| $3.2~V\pm1.0\%$                   | S-1004CA32I-M5T1U | S-1004CA32I-I6T1U |

| $3.3~V\pm1.0\%$                   | S-1004CA33I-M5T1U | S-1004CA33I-I6T1U |

| $3.4~V\pm1.0\%$                   | S-1004CA34I-M5T1U | S-1004CA34I-I6T1U |

| $3.5~V\pm1.0\%$                   | S-1004CA35I-M5T1U | S-1004CA35I-I6T1U |

| $3.6~V\pm1.0\%$                   | S-1004CA36I-M5T1U | S-1004CA36I-I6T1U |

| $3.7~V\pm1.0\%$                   | S-1004CA37I-M5T1U | S-1004CA37I-I6T1U |

| 3.8 V ± 1.0%                      | S-1004CA38I-M5T1U | S-1004CA38I-I6T1U |

| 3.9 V ± 1.0%                      | S-1004CA39I-M5T1U | S-1004CA39I-I6T1U |

| 4.0 V ± 1.0%                      | S-1004CA40I-M5T1U | S-1004CA40I-I6T1U |

| 4.1 V ± 1.0%                      | S-1004CA41I-M5T1U | S-1004CA41I-I6T1U |

| $4.2~V\pm1.0\%$                   | S-1004CA42I-M5T1U | S-1004CA42I-I6T1U |

| $4.3~V\pm1.0\%$                   | S-1004CA43I-M5T1U | S-1004CA43I-I6T1U |

| $4.4~V\pm1.0\%$                   | S-1004CA44I-M5T1U | S-1004CA44I-I6T1U |

| $4.5~V\pm1.0\%$                   | S-1004CA45I-M5T1U | S-1004CA45I-I6T1U |

| $4.6~V\pm1.0\%$                   | S-1004CA46I-M5T1U | S-1004CA46I-I6T1U |

| $4.7~V\pm1.0\%$                   | S-1004CA47I-M5T1U | S-1004CA47I-I6T1U |

| $4.8~V\pm1.0\%$                   | S-1004CA48I-M5T1U | S-1004CA48I-I6T1U |

| $4.9~V\pm1.0\%$                   | S-1004CA49I-M5T1U | S-1004CA49I-I6T1U |

| $5.0~V\pm1.0\%$                   | S-1004CA50I-M5T1U | S-1004CA50I-I6T1U |

| 0.0 0 ± 1.070                     |                   |                   |

#### 4.4 S-1004 Series CB type

Output form: CMOS output (Active "L")

| Table 6                           |                   |  |

|-----------------------------------|-------------------|--|

| Detection Voltage                 | SOT-23-5          |  |

| $1.0 \text{ V} \pm 22 \text{ mV}$ | S-1004CB10I-M5T1U |  |

| $1.1 \text{ V} \pm 22 \text{ mV}$ | S-1004CB11I-M5T1U |  |

| $1.2 V \pm 22 mV$                 | S-1004CB12I-M5T1U |  |

| $1.3 \text{ V} \pm 22 \text{ mV}$ | S-1004CB13I-M5T1U |  |

| 1.4 V ± 22 mV                     | S-1004CB14I-M5T1U |  |

| 1.5 V ± 22 mV                     | S-1004CB15I-M5T1U |  |

| 1.6 V ± 22 mV                     | S-1004CB16I-M5T1U |  |

| 1.7 V ± 22 mV                     | S-1004CB17I-M5T1U |  |

| $1.8 \text{ V} \pm 22 \text{ mV}$ | S-1004CB18I-M5T1U |  |

| $1.9 \text{ V} \pm 22 \text{ mV}$ | S-1004CB19I-M5T1U |  |

| $2.0 \text{ V} \pm 22 \text{ mV}$ | S-1004CB20I-M5T1U |  |

| $2.1 \text{ V} \pm 22 \text{ mV}$ | S-1004CB21I-M5T1U |  |

| $2.2~V\pm1.0\%$                   | S-1004CB22I-M5T1U |  |

| $2.3~V\pm1.0\%$                   | S-1004CB23I-M5T1U |  |

| $2.4~V\pm1.0\%$                   | S-1004CB24I-M5T1U |  |

| $2.5~V\pm1.0\%$                   | S-1004CB25I-M5T1U |  |

| 2.6 V ± 1.0%                      | S-1004CB26I-M5T1U |  |

| 2.7 V ± 1.0%                      | S-1004CB27I-M5T1U |  |

| 2.8 V ± 1.0%                      | S-1004CB28I-M5T1U |  |

| 2.9 V ± 1.0%                      | S-1004CB29I-M5T1U |  |

| 3.0 V ± 1.0%                      | S-1004CB30I-M5T1U |  |

| 3.1 V ± 1.0%                      | S-1004CB31I-M5T1U |  |

| 3.2 V ± 1.0%                      | S-1004CB32I-M5T1U |  |

| 3.3 V ± 1.0%                      | S-1004CB33I-M5T1U |  |

| 3.4 V ± 1.0%                      | S-1004CB34I-M5T1U |  |

| $3.5 \text{ V} \pm 1.0\%$         | S-1004CB35I-M5T1U |  |

| 3.6 V ± 1.0%                      | S-1004CB36I-M5T1U |  |

| 3.7 V ± 1.0%                      | S-1004CB37I-M5T1U |  |

| 3.8 V ± 1.0%                      | S-1004CB38I-M5T1U |  |

| 3.9 V ± 1.0%                      | S-1004CB39I-M5T1U |  |

| $4.0 \text{ V} \pm 1.0\%$         | S-1004CB40I-M5T1U |  |

| $4.1 \text{ V} \pm 1.0\%$         | S-1004CB41I-M5T1U |  |

| $4.2 \text{ V} \pm 1.0\%$         | S-1004CB42I-M5T1U |  |

| $4.3 \text{ V} \pm 1.0\%$         | S-1004CB43I-M5T1U |  |

| 4.4 V ± 1.0%                      | S-1004CB44I-M5T1U |  |

| $4.5 \text{ V} \pm 1.0\%$         | S-1004CB45I-M5T1U |  |

| 4.6 V ± 1.0%                      | S-1004CB46I-M5T1U |  |

| 4.7 V ± 1.0%                      | S-1004CB47I-M5T1U |  |

| 4.8 V ± 1.0%                      | S-1004CB48I-M5T1U |  |

| 4.9 V ± 1.0%                      | S-1004CB49I-M5T1U |  |

| $5.0 V \pm 1.0\%$                 | S-1004CB50I-M5T1U |  |

#### Pin Configurations

#### 1. S-1004 Series NA / CA type

1.1 SOT-23-5

| 5<br>日 |   | 4<br>日 |  |

|--------|---|--------|--|

| 日      | 日 | 日      |  |

| 1      | 2 | 3      |  |

Figure 3

#### 1.2 SNT-6A

Figure 4

| Pin No. | Symbol | Description                        |

|---------|--------|------------------------------------|

| 1       | OUT    | Voltage detection output pin       |

| 2       | VDD    | Power supply pin                   |

| 3       | VSS    | GND pin                            |

| 4       | CD     | Connection pin for delay capacitor |

| 5       | SENSE  | Detection voltage input pin        |

|         |        |                                    |

Table 7 Pin Configuration A

#### Pin No. Symbol Description OUT Voltage detection output pin 1 2 VDD Power supply pin 3 SENSE Detection voltage input pin 4 Connection pin for delay capacitor CD 5 NC\*1 No connection GND pin 6 vss

Table 8 Pin Configuration A

\*1. The NC pin is electrically open.

The NC pin can be connected to the VDD pin or the VSS pin.

#### 2. S-1004 Series NB / CB type

#### 2.1 SOT-23-5

Top view

Figure 5

#### Table 9 Pin Configuration B

| Pin No. | Symbol | Description                        |

|---------|--------|------------------------------------|

| 1       | OUT    | Voltage detection output pin       |

| 2       | VSS    | GND pin                            |

| 3       | VDD    | Power supply pin                   |

| 4       | SENSE  | Detection voltage input pin        |

| 5       | CD     | Connection pin for delay capacitor |

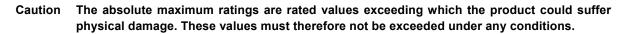

#### Absolute Maximum Ratings

#### Table 10

| (Ta = +25°C unless otherwis   |                               |                                 |                                                |      |  |

|-------------------------------|-------------------------------|---------------------------------|------------------------------------------------|------|--|

|                               | Item                          | Symbol                          | Absolute Maximum Rating                        | Unit |  |

| Power supply voltage          |                               | $V_{\text{DD}} - V_{\text{SS}}$ | 12.0                                           | V    |  |

| CD pin input voltage          |                               | Vcd                             | $V_{\text{SS}} - 0.3$ to $V_{\text{DD}} + 0.3$ | V    |  |

| SENSE pin input voltage       |                               | VSENSE                          | V <sub>SS</sub> – 0.3 to 12.0                  | V    |  |

| Output voltage                | Nch open-drain output product | Maria                           | V <sub>SS</sub> – 0.3 to 12.0                  | V    |  |

| Output voltage                | CMOS output product           | Vout                            | $V_{\text{SS}} - 0.3$ to $V_{\text{DD}} + 0.3$ | V    |  |

| Output current                |                               | Іоит                            | 50                                             | mA   |  |

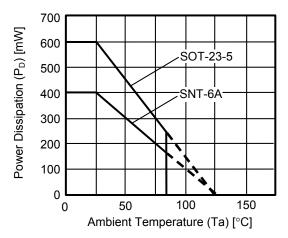

| SOT-23-5                      |                               |                                 | 600* <b>1</b>                                  | mW   |  |

| Power dissipation             | SNT-6A                        | PD                              | 400 <sup>*1</sup>                              | mW   |  |

| Operation ambient temperature |                               | T <sub>opr</sub>                | -40 to +85                                     | °C   |  |

| Storage tempera               | ature                         | T <sub>stg</sub>                | -40 to +125                                    | °C   |  |

\*1. When mounted on board

[Mounted board]

(1) Board size: 114.3 mm  $\times$  76.2 mm  $\times$  t1.6 mm

(2) Name: JEDEC STANDARD51-7

Figure 6 Power Dissipation of Package (When Mounted on Board)

#### Electrical Characteristics

#### 1. Nch open-drain output product

Table 11

|                                                   |                                               |                                                                                                                                 |                                                                               | (Ta =                                                              | ∺+25°C u                      | nless othe                                                         | erwise s       | pecified)        |

|---------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------|----------------|------------------|

| Item                                              | Symbol                                        | Condition                                                                                                                       |                                                                               | Min.                                                               | Тур.                          | Max.                                                               | Unit           | Test<br>Circuit  |

| Detection voltage*1 –V                            |                                               | $0.95 \text{ V} \leq \text{V}_{\text{DD}} \leq 10.0 \text{ V}$                                                                  | $1.0 \ V \leq -V_{DET(S)} < 2.2 \ V$                                          | -V <sub>DET(S)</sub><br>- 0.022                                    | -Vdet(s)                      | $-V_{DET(S)} + 0.022$                                              | V              | 1                |

|                                                   | -VDET                                         |                                                                                                                                 | $2.2~V \leq -V_{DET(S)} \leq 5.0~V$                                           | $\begin{array}{c} -V_{\text{DET(S)}} \\ \times \ 0.99 \end{array}$ | -Vdet(s)                      | $\begin{array}{c} -V_{\text{DET(S)}} \\ \times \ 1.01 \end{array}$ | V              | 1                |

| Hysteresis width                                  | V <sub>HYS</sub>                              | _                                                                                                                               |                                                                               | -V <sub>DET</sub><br>× 0.03                                        | $-V_{\text{DET}} \times 0.05$ | $-V_{DET} \times 0.07$                                             | V              | 1                |

| Current<br>consumption <sup>*2</sup>              | lss                                           | V <sub>DD</sub> = 10.0 V, V <sub>SENSE</sub> = -V <sub>DET(S)</sub> + 1.0 V                                                     |                                                                               | -                                                                  | 0.50                          | 0.90                                                               | μA             | 2                |

| Operation voltage                                 | Vdd                                           |                                                                                                                                 | -                                                                             | 0.95                                                               | _                             | 10.0                                                               | V              | 1                |

| Output current                                    | Іоит                                          | Output transistor<br>Nch<br>$V_{DS}^{*3} = 0.5 V$<br>$V_{SENSE} = 0.0 V$                                                        | $V_{DD} = 0.95 V$<br>$V_{DD} = 1.2 V$<br>$V_{DD} = 2.4 V$<br>$V_{DD} = 4.8 V$ | 0.59<br>0.73<br>1.47<br>1.86                                       | 1.00<br>1.33<br>2.39<br>2.50  | _<br><br>_                                                         | mA<br>mA<br>mA | 3<br>3<br>3<br>3 |

| Leakage current                                   | Ileak                                         | Output transistor<br>Nch<br>$V_{DD} = 10.0 \text{ V}, \text{ V}_{DS}^{*3} = 10.0 \text{ V}, \text{ V}_{SENSE} = 10.0 \text{ V}$ |                                                                               | -                                                                  | _                             | 0.08                                                               | μA             | 3                |

| Detection voltage<br>temperature<br>coefficient*4 | Δ–V <sub>DET</sub><br>ΔTa • –V <sub>DET</sub> | Ta = -40°C to +85°C                                                                                                             |                                                                               | _                                                                  | ±100                          | ±350                                                               | ppm/°C         | 1                |

| Detection<br>delay time <sup>*5</sup>             | <b>t</b> det                                  | V <sub>DD</sub> = 5.0 V                                                                                                         |                                                                               | -                                                                  | 40                            | _                                                                  | μs             | 4                |

| Release<br>delay time <sup>*6</sup>               | treset                                        | $V_{DD} = -V_{DET(S)} + 1.0 \text{ V}, C_D = 4.7 \text{ nF}$                                                                    |                                                                               | 10.79                                                              | 12.69                         | 14.59                                                              | ms             | 4                |

| SENSE pin<br>resistance                           | Rsense                                        | $\begin{array}{l} 1.0 \ V \leq -V_{DET(S)} < 1.2 \ V \\ 1.2 \ V \leq -V_{DET(S)} \leq 5.0 \ V \end{array}$                      |                                                                               | 5.0<br>6.0                                                         | 19.0<br>30.0                  | 42.0<br>98.0                                                       | ΜΩ<br>ΜΩ       | 2<br>2           |

\*1. -V<sub>DET</sub>: Actual detection voltage value, -V<sub>DET(S)</sub>: Set detection voltage value (the center value of the detection voltage range in **Table 3** or **Table 4**)

**\*2.** The current flowing through the SENSE pin resistance is not included.

\*3. V<sub>DS</sub>: Drain-to-source voltage of the output transistor

\*4. The temperature change of the detection voltage [mV/°C] is calculated by using the following equation.

$$\frac{\Delta - V_{\text{DET}}}{\Delta Ta} \left[ \text{mV/}^{\circ}\text{C} \right]^{*1} = -V_{\text{DET}(S)} (\text{typ.}) \left[ \text{V} \right]^{*2} \times \frac{\Delta - V_{\text{DET}}}{\Delta Ta \bullet - V_{\text{DET}}} \left[ \text{ppm/}^{\circ}\text{C} \right]^{*3} \div 1000$$

- \*1. Temperature change of the detection voltage

- **\*2.** Set detection voltage

- **\*3.** Detection voltage temperature coefficient

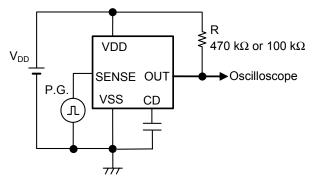

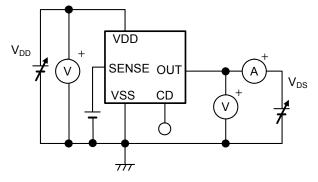

- \*5. The time period from when the pulse voltage of 6.0 V  $\rightarrow -V_{DET(S)} 2.0$  V or 0 V is applied to the SENSE pin to when V<sub>OUT</sub> reaches V<sub>DD</sub> / 2, after the output pin is pulled up to 5.0 V by the resistance of 470 kΩ.

- \*6. The time period from when the pulse voltage of 0.95 V  $\rightarrow$  10.0 V is applied to the SENSE pin to when V<sub>OUT</sub> reaches V<sub>DD</sub>  $\times$  90%, after the output pin is pulled up to V<sub>DD</sub> by the resistance of 100 kΩ.

#### BUILT-IN DELAY CIRCUIT (EXTERNAL DELAY TIME SETTING) VOLTAGE DETECTOR WITH SENSE PIN Rev.2.1\_01 S-1004 Series

Table 12

#### 2. CMOS output product

|                                                               |                                                                 |                                                                                                            |                                         | (Ta =                                                              | -<br>+25°C u           | nless othe                                                         | erwise sp | pecified)       |

|---------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------|------------------------|--------------------------------------------------------------------|-----------|-----------------|

| Item                                                          | Symbol                                                          | Condition                                                                                                  |                                         | Min.                                                               | Тур.                   | Max.                                                               | Unit      | Test<br>Circuit |

| Detection voltage <sup>*1</sup> –Vi                           |                                                                 | 0.95 V ≤ Vpp ≤ 10.0 V                                                                                      | $1.0~V \leq -V_{\text{DET}(S)} < 2.2~V$ | -V <sub>DET(S)</sub><br>- 0.022                                    | -Vdet(s)               | -V <sub>DET(S)</sub><br>+ 0.022                                    | V         | 1               |

|                                                               | - V DET                                                         | $0.95 V \leq V DD \leq 10.0 V$                                                                             | $2.2~V \leq -V_{DET(S)} \leq 5.0~V$     | $\begin{array}{c} -V_{\text{DET(S)}} \\ \times \ 0.99 \end{array}$ | -Vdet(s)               | $\begin{array}{c} -V_{\text{DET(S)}} \\ \times \ 1.01 \end{array}$ | V         | 1               |

| Hysteresis width                                              | V <sub>HYS</sub>                                                | -                                                                                                          |                                         | $-V_{DET} \times 0.03$                                             | $-V_{DET} \times 0.05$ | $-V_{DET} \times 0.07$                                             | V         | 1               |

| Current<br>consumption <sup>*2</sup>                          | lss                                                             | $V_{DD}$ = 10.0 V, $V_{SENSE}$ = $-V_{DET(S)}$ + 1.0 V                                                     |                                         | _                                                                  | 0.50                   | 0.90                                                               | μA        | 2               |

| Operation voltage                                             | Vdd                                                             |                                                                                                            | _                                       | 0.95                                                               | _                      | 10.0                                                               | V         | 1               |

|                                                               | Nch<br>V <sub>DS</sub> *3 = 0.5 V<br>V <sub>SENSE</sub> = 0.0 V | $V_{DS}^{*3} = 0.5 V$<br>$V_{SENSE} = 0.0 V$<br>Output transistor                                          | V <sub>DD</sub> = 0.95 V                | 0.59                                                               | 1.00                   | _                                                                  | mA        | 3               |

|                                                               |                                                                 |                                                                                                            | V <sub>DD</sub> = 1.2 V                 | 0.73                                                               | 1.33                   | _                                                                  | mA        | 3               |

|                                                               |                                                                 |                                                                                                            | V <sub>DD</sub> = 2.4 V                 | 1.47                                                               | 2.39                   | _                                                                  | mA        | 3               |

| Output current                                                |                                                                 |                                                                                                            | V <sub>DD</sub> = 4.8 V                 | 1.86                                                               | 2.50                   | _                                                                  | mA        | 3               |

|                                                               |                                                                 |                                                                                                            | V <sub>DD</sub> = 4.8 V                 | 1.62                                                               | 2.60                   | -                                                                  | mA        | 5               |

|                                                               |                                                                 | -                                                                                                          | V <sub>DD</sub> = 6.0 V                 | 1.78                                                               | 2.86                   | -                                                                  | mA        | 5               |

| Detection voltage<br>temperature<br>coefficient <sup>*4</sup> | Δ–V <sub>DET</sub><br>ΔTa • –V <sub>DET</sub>                   | Ta = -40°C to +85°C                                                                                        |                                         | _                                                                  | ±100                   | ±350                                                               | ppm/°C    | 1               |

| Detection<br>delay time <sup>*5</sup>                         | tdet                                                            | V <sub>DD</sub> = 5.0 V                                                                                    |                                         | _                                                                  | 40                     | _                                                                  | μs        | 4               |

| Release<br>delay time <sup>*6</sup>                           | treset                                                          | $V_{DD} = -V_{DET(S)} + 1.0 \text{ V}, \text{ C}_{D} = 4.7 \text{ nF}$                                     |                                         | 10.79                                                              | 12.69                  | 14.59                                                              | ms        | 4               |

| SENSE pin                                                     | Rsense                                                          | $\begin{array}{l} 1.0 \ V \leq -V_{DET(S)} < 1.2 \ V \\ 1.2 \ V \leq -V_{DET(S)} \leq 5.0 \ V \end{array}$ |                                         | 5.0                                                                | 19.0                   | 42.0                                                               | MΩ        | 2               |

| resistance                                                    | RSENSE                                                          |                                                                                                            |                                         | 6.0                                                                | 30.0                   | 98.0                                                               | MΩ        | 2               |

\*1. -V<sub>DET</sub>: Actual detection voltage value, -V<sub>DET(S)</sub>: Set detection voltage value (the center value of the detection voltage range in **Table 5** or **Table 6**)

\*2. The current flowing through the SENSE pin resistance is not included.

\*3. V<sub>DS</sub>: Drain-to-source voltage of the output transistor

\*4. The temperature change of the detection voltage [mV/°C] is calculated by using the following equation.

$$\frac{\Delta - V_{\text{DET}}}{\Delta Ta} \left[ \text{mV/}^{\circ}\text{C} \right]^{*1} = -V_{\text{DET}(S)} (\text{typ.}) \left[ \text{V} \right]^{*2} \times \frac{\Delta - V_{\text{DET}}}{\Delta Ta \bullet - V_{\text{DET}}} \left[ \text{ppm/}^{\circ}\text{C} \right]^{*3} \div 1000$$

- \*1. Temperature change of the detection voltage

- \*2. Set detection voltage

- **\*3.** Detection voltage temperature coefficient

- \*5. The time period from when the pulse voltage of 6.0 V  $\rightarrow -V_{DET(S)} 2.0$  V or 0 V is applied to the SENSE pin to when V<sub>OUT</sub> reaches V<sub>DD</sub> / 2.

- \*6. The time period from when the pulse voltage of 0.95 V  $\rightarrow$  10.0 V is applied to the SENSE pin to when V<sub>OUT</sub> reaches V<sub>DD</sub>  $\times$  90%.

#### BUILT-IN DELAY CIRCUIT (EXTERNAL DELAY TIME SETTING) VOLTAGE DETECTOR WITH SENSE PIN S-1004 Series Rev.2.1\_01

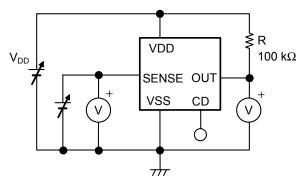

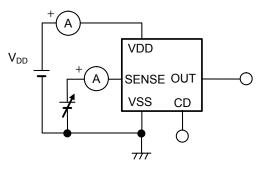

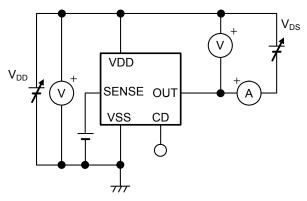

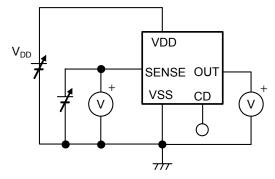

#### Test Circuits

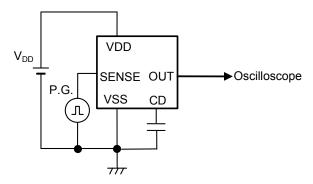

Figure 7 Test Circuit 1 (Nch open-drain output product)

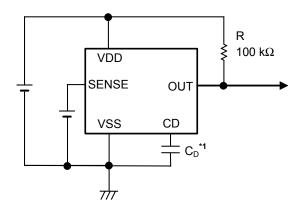

Figure 9 Test Circuit 2

Figure 11 Test Circuit 4 (Nch open-drain output product)

Figure 13 Test Circuit 5

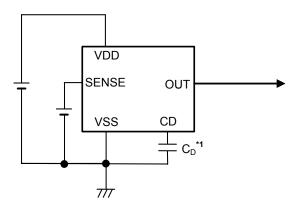

Figure 8 Test Circuit 1 (CMOS output product)

Figure 10 Test Circuit 3

Figure 12 Test Circuit 4 (CMOS output product)

#### Standard Circuits

#### 1. Nch open-drain output product

\*1. The delay capacitor (C<sub>D</sub>) should be connected directly to the CD pin and the VSS pin.

#### Figure 14

#### 2. CMOS output product

\*1. The delay capacitor ( $C_D$ ) should be connected directly to the CD pin and the VSS pin.

#### Figure 15

Caution The above connection diagram and constant will not guarantee successful operation. Perform thorough evaluation using the actual application to set the constant.

#### Explanation of Terms

#### 1. Detection voltage (–VDET)

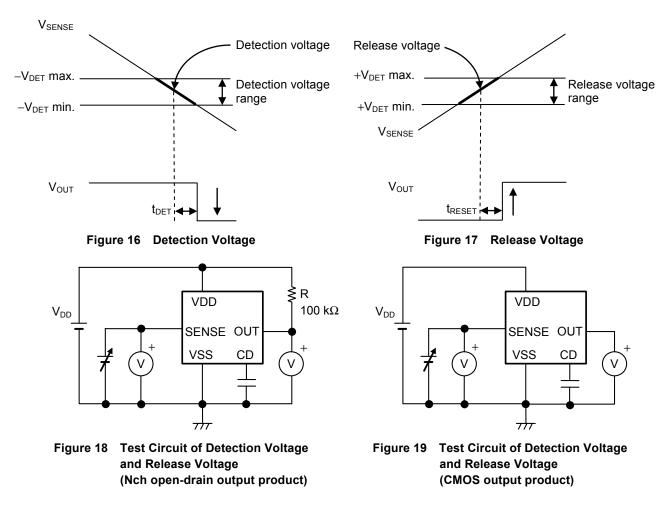

The detection voltage is a voltage at which the output in **Figure 18** or **Figure 19** turns to "L". The detection voltage varies slightly among products of the same specification. The variation of detection voltage between the specified minimum ( $-V_{DET}$  min.) and the maximum ( $-V_{DET}$  max.) is called the detection voltage range (Refer to **Figure 16**).

Example: In the S-1004Cx18, the detection voltage is either one in the range of 1.778 V  $\leq$  -V<sub>DET</sub>  $\leq$  1.822 V. This means that some S-1004Cx18 have -V<sub>DET</sub> = 1.778 V and some have -V<sub>DET</sub> = 1.822 V.

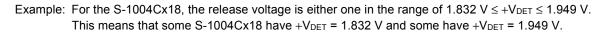

#### 2. Release voltage (+VDET)

The release voltage is a voltage at which the output in **Figure 18** or **Figure 19** turns to "H". The release voltage varies slightly among products of the same specification. The variation of release voltage between the specified minimum ( $+V_{DET}$  min.) and the maximum ( $+V_{DET}$  max.) is called the release voltage range (Refer to **Figure 17**). The range is calculated from the actual detection voltage ( $-V_{DET}$ ) of a product and is in the range of  $-V_{DET} \times 1.03 \le +V_{DET} \le -V_{DET} \times 1.07$ .

#### 3. Hysteresis width (VHYS)

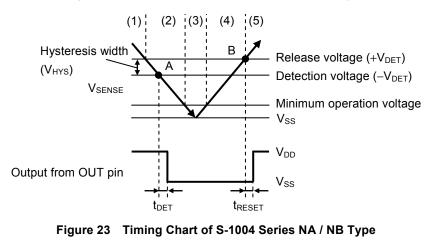

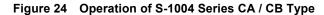

The hysteresis width is the voltage difference between the detection voltage and the release voltage (the voltage at point B – the voltage at point A = V<sub>HYS</sub> in **"Figure 23 Timing Chart of S-1004 Series NA / NB Type"** and **"Figure 25 Timing Chart of S-1004 Series CA / CB Type"**). Setting the hysteresis width between the detection voltage and the release voltage, prevents malfunction caused by noise on the input voltage.

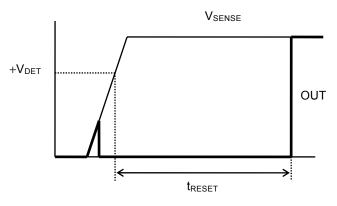

#### 4. Release delay time (treset)

The release delay time is the time period from when the input voltage to the SENSE pin exceeds the release voltage ( $+V_{DET}$ ) to when the output from the OUT pin inverts. The release delay time changes according to the delay capacitor ( $C_D$ ).

Figure 20 Release Delay Time

#### 5. Feed-through current

The feed-through current is a current that flows instantaneously to the VDD pin at the time of detection and release of a voltage detector. The feed-through current is large in CMOS output product, small in Nch open-drain output product.

#### 6. Oscillation

In applications where an input resistor is connected (**Figure 21**), taking a CMOS output (active "L") product for example, the feed-through current which is generated when the output goes from "L" to "H" (at the time of release) causes a voltage drop equal to [feed-through current]  $\times$  [input resistance]. Since the VDD pin and the SENSE pin are shorted as in **Figure 21**, the SENSE pin voltage drops at the time of release. Then the SENSE pin voltage drops below the detection voltage and the output goes from "H" to "L". In this status, the feed-through current stops and its resultant voltage drop disappears, and the output goes from "L" to "H". The feed-through current is then generated again, a voltage drop appears, and repeating the process finally induces oscillation.

Figure 21 Example for Bad Implementation Due to Detection Voltage Change

#### Operation

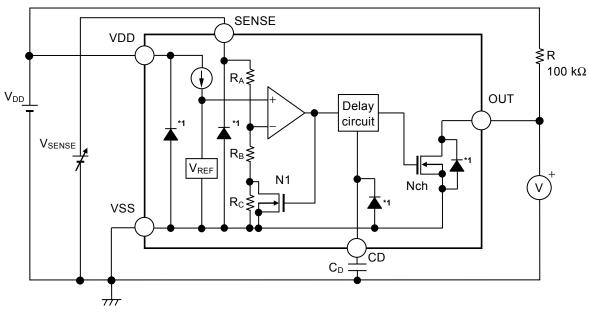

#### 1. Basic operation

#### 1.1 S-1004 Series NA / NB type

(1) When the power supply voltage (V<sub>DD</sub>) is the minimum operation voltage or higher, and the SENSE pin voltage (V<sub>SENSE</sub>) is the release voltage (+V<sub>DET</sub>) or higher, the Nch transistor is turned off to output V<sub>DD</sub> ("H") when the output is pulled up. Since the Nch transistor (N1) is turned off, the input voltage to the comparator is  $(R_B + R_C) \cdot V_{SENSE}$

$R_A + R_B + R_C$

(2) Even if V<sub>SENSE</sub> decreases to +V<sub>DET</sub> or lower, V<sub>DD</sub> is output when V<sub>SENSE</sub> is higher than the detection voltage (-V<sub>DET</sub>).

When  $V_{\text{SENSE}}$  decreases to  $-V_{\text{DET}}$  or lower (point A in **Figure 23**), the Nch transistor is turned on. And then  $V_{\text{SS}}$  ("L") is output from the OUT pin after the elapse of the detection delay time ( $t_{\text{DET}}$ ).

At this time, N1 is turned on, and the input voltage to the comparator is  $\frac{R_B \bullet V_{SENSE}}{R_A + R_B}$ .

- (3) Even if V<sub>SENSE</sub> further decreases to the IC's minimum operation voltage or lower, the output from the OUT pin is stable when V<sub>DD</sub> is minimum operation voltage or higher.

- (4) Even if  $V_{SENSE}$  exceeds  $-V_{DET}$ ,  $V_{SS}$  is output when  $V_{SENSE}$  is lower than  $+V_{DET}$ .

- (5) When V<sub>SENSE</sub> increases to +V<sub>DET</sub> or higher (point B in **Figure 23**), the Nch transistor is turned off. And then V<sub>DD</sub> is output from the OUT pin after the elapse of the release delay time (t<sub>RESET</sub>) when the output is pulled up.

\*1. Parasitic diode

Figure 22 Operation of S-1004 Series NA / NB Type

#### 1.2 S-1004 Series CA / CB type

- (1) When the power supply voltage (V<sub>DD</sub>) is the minimum operation voltage or higher, and the SENSE pin voltage (V<sub>SENSE</sub>) is the release voltage (+V<sub>DET</sub>) or higher, the Nch transistor is turned off and the Pch transistor is turned on to output V<sub>DD</sub> ("H"). Since the Nch transistor (N1) is turned off, the input voltage to the comparator is (R<sub>B</sub> + R<sub>C</sub>) • V<sub>SENSE</sub>

- $R_A + R_B + R_C$

- (2) Even if V<sub>SENSE</sub> decreases to +V<sub>DET</sub> or lower, V<sub>DD</sub> is output when V<sub>SENSE</sub> is higher than the detection voltage (-V<sub>DET</sub>).

When  $V_{\text{SENSE}}$  decreases to  $-V_{\text{DET}}$  or lower (point A in **Figure 25**), the Nch transistor is turned on and the Pch transistor is turned off. And then  $V_{\text{SS}}$  ("L") is output from the OUT pin after the elapse of the detection delay time ( $t_{\text{DET}}$ ).

At this time, N1 is turned on, and the input voltage to the comparator is  $\frac{R_B \bullet V_{SENSE}}{R_A + R_B}$ .

- (3) Even if V<sub>SENSE</sub> further decreases to the IC's minimum operation voltage or lower, the output from the OUT pin is stable when V<sub>DD</sub> is minimum operation voltage or higher.

- (4) Even if  $V_{SENSE}$  exceeds  $-V_{DET}$ ,  $V_{SS}$  is output when  $V_{SENSE}$  is lower than  $+V_{DET}$ .

- (5) When V<sub>SENSE</sub> increases to +V<sub>DET</sub> or higher (point B in **Figure 25**), the Nch transistor is turned off and the Pch transistor is turned on. And then V<sub>DD</sub> is output from the OUT pin after the elapse of the release delay time (t<sub>RESET</sub>).

**\*1.** Parasitic diode

Figure 25 Timing Chart of S-1004 Series CA / CB Type

#### 2. SENSE pin

#### 2.1 Error when detection voltage is set externally

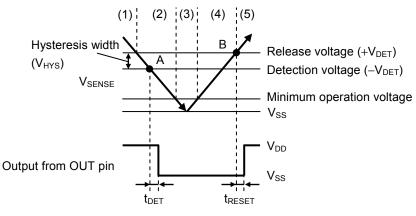

By connecting a node that was resistance-divided by the resistor ( $R_A$ ) and the resistor ( $R_B$ ) to the SENSE pin as seen in **Figure 26**, the detection voltage can be set externally.

For conventional products without the SENSE pin,  $R_A$  cannot be too large since the resistance-divided node must be connected to the VDD pin. This is because a feed-through current will flow through the VDD pin when it goes from detection to release, and if  $R_A$  is large, problems such as oscillation or larger error in the hysteresis width may occur.

In the S-1004 Series,  $R_A$  and  $R_B$  are easily made larger since the resistance-divided node can be connected to the SENSE pin through which no feed-through current flows. However, be careful of error in the current flowing through the internal resistance ( $R_{SENSE}$ ) that will occur.

Although  $R_{SENSE}$  in the S-1004 Series is large (5 M $\Omega$  min.) to make the error small,  $R_A$  and  $R_B$  should be selected such that the error is within the allowable limits.

#### 2. 2 Selection of R<sub>A</sub> and R<sub>B</sub>

In **Figure 26**, the relation between the external setting detection voltage ( $V_{DX}$ ) and the actual detection voltage ( $-V_{DET}$ ) is ideally calculated by the equation below.

$$V_{DX} = -V_{DET} \times \left(1 + \frac{R_A}{R_B}\right)$$

... (1)

However, in reality there is an error in the current flowing through  $R_{SENSE}$ . When considering this error, the relation between  $V_{DX}$  and  $-V_{DET}$  is calculated as follows.

$$V_{DX} = -V_{DET} \times \left(1 + \frac{R_A}{R_B || R_{SENSE}}\right)$$

$$= -V_{DET} \times \left(1 + \frac{R_A}{\frac{R_B \times R_{SENSE}}{R_B + R_{SENSE}}}\right)$$

$$= -V_{DET} \times \left(1 + \frac{R_A}{R_B}\right) + \frac{R_A}{R_{SENSE}} \times -V_{DET} \qquad \cdots (2)$$

By using equations (1) and (2), the error is calculated as  $-V_{DET} \times \frac{R_A}{R_{SENSE}}$ .

The error rate is calculated as follows by dividing the error by the right-hand side of equation (1).

$$\frac{R_A \times R_B}{R_{SENSE} \times (R_A + R_B)} \times 100 \, [\%] = \frac{R_A \parallel R_B}{R_{SENSE}} \times 100 \, [\%] \qquad \cdots (3)$$

As seen in equation (3), the smaller the resistance values of  $R_A$  and  $R_B$  compared to  $R_{SENSE}$ , the smaller the error rate becomes.

Also, the relation between the external setting hysteresis width ( $V_{HX}$ ) and the hysteresis width ( $V_{HYS}$ ) is calculated by equation below. Error due to  $R_{SENSE}$  also occurs to the relation in a similar way to the detection voltage.

$$V_{HX} = V_{HYS} \times \left(1 + \frac{R_A}{R_B}\right) \qquad \cdots (4)$$

Figure 26 Detection Voltage External Setting Circuit

Caution If R<sub>A</sub> and R<sub>B</sub> are large, the SENSE pin input impedance becomes higher and may cause a malfunction due to noise. In this case, connect a capacitor between the SENSE pin and the VSS pin.

#### 2.3 Power on sequence

Apply power in the order, the VDD pin then the SENSE pin.

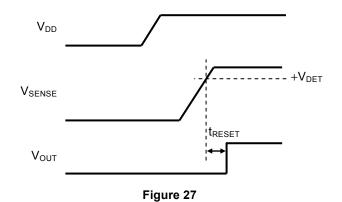

As seen in **Figure 27**, when  $V_{SENSE} \ge +V_{DET}$ , the OUT pin output ( $V_{OUT}$ ) rises and the S-1004 Series becomes the release status (normal operation).

## Caution If power is applied in the order the SENSE pin then the VDD pin, an erroneous release may occur even if V<sub>SENSE</sub> < +V<sub>DET</sub>.

#### 2.4 Precautions when shorting between the VDD pin and the SENSE pin

#### 2.4.1 Input resistor

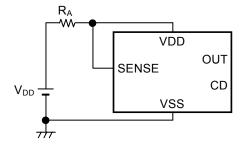

Do not connect the input resistor (R<sub>A</sub>) when shorting between the VDD pin and the SENSE pin.

A feed-through current flows through the VDD pin at the time of release. When connecting the circuit shown as **Figure 28**, the feed-through current of the VDD pin flowing through R<sub>A</sub> will cause a drop in V<sub>SENSE</sub> at the time of release.

At that time, oscillation may occur if  $V_{\text{SENSE}} \leq -V_{\text{DET}}$ .

Figure 28

#### 2. 4. 2 Parasitic resistance and parasitic capacitance

Due to the difference in parasitic resistance and parasitic capacitance of the VDD pin and the SENSE pin, power may be applied to the SENSE pin first.

Note that an erroneous release may occur if this happens (refer to "2.3 Power on sequence").

Caution In CMOS output product, make sure that the VDD pin input impedance does not become too high, regardless of the above. Since a feed-through current is large, a malfunction may occur if the VDD pin voltage changes greatly at the time of release.

#### 2. 5 Malfunction when VDD falls

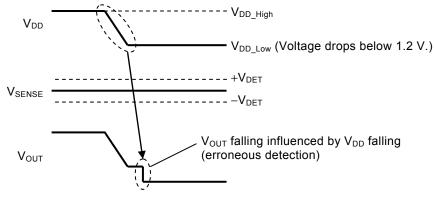

As seen in **Figure 29**, note that if the VDD pin voltage (V<sub>DD</sub>) drops steeply below 1.2 V when  $-V_{DET} < V_{SENSE} < +V_{DET}$ , erroneous detection may occur.

When  $V_{DD\_Low} \ge 1.2$  V, erroneous detection does not occur.

When  $V_{DD\_Low} < 1.2$  V, the more the  $V_{DD}$  falling amplitude increases or the shorter the falling time becomes, the easier the erroneous detection.

Perform thorough evaluation in actual application.

Figure 29

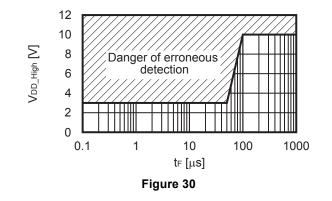

The S-1004Cx50 example in Figure 30 shows an example of erroneous detection boundary conditions.

Remark Test conditions Product name: S-1004Cx50 VSENSE:  $-V_{DET(S)} + 0.1 V$ VDD\_High: VDD pin voltage before falling VDD pin voltage after falling (0.95 V) VDD\_Low:  $\Delta V_{DD}$ :  $V_{DD_High} - V_{DD_Low}$ t⊧: Falling time of V\_DD from V\_DD\_High –  $\Delta$ V\_DD × 10% to V\_DD\_Low +  $\Delta$ V\_DD × 10% ----- VDD\_High ----- VDD High  $-\Delta V$ DD  $\times$  10% Vdd VDD Low +  $\Delta$ VDD × 10% VDD\_Low

t⊧

Figure 31

#### 3. Delay circuit

The delay circuit has the function that adjusts the release delay time (tRESET) from when the SENSE pin voltage (VSENSE) reaches release voltage (+VDET) to when the output from OUT pin inverts.

tRESET is determined by the delay coefficient, the delay capacitor (C<sub>D</sub>), and the release delay time when the CD pin is open (t<sub>RESET0</sub>), and calculated by the equation below.

Table 13

$t_{RESET}$  [ms] = Delay coefficient × C<sub>D</sub> [nF] +  $t_{RESET0}$  [ms]

| Operation   | Delay Coefficient |      |      |  |  |  |

|-------------|-------------------|------|------|--|--|--|

| Temperature | Min.              | Тур. | Max. |  |  |  |

| Ta = +85°C  | 1.78              | 2.29 | 3.13 |  |  |  |

| Ta = +25°C  | 2.30              | 2.66 | 3.07 |  |  |  |

| Ta = -40°C  | 2.68              | 3.09 | 3.57 |  |  |  |

| Table 14            |                  |                                                  |          |  |  |  |

|---------------------|------------------|--------------------------------------------------|----------|--|--|--|

| Operation           | Release Delay Ti | Release Delay Time when CD Pin is Open (tRESETO) |          |  |  |  |

| Temperature         | Min.             | Тур.                                             | Max.     |  |  |  |

| Ta = +85°C          | 0.020 ms         | 0.049 ms                                         | 0.130 ms |  |  |  |

| Ta = +25°C          | 0.021 ms         | 0.059 ms                                         | 0.164 ms |  |  |  |

| $Ta = -40^{\circ}C$ | 0.024 ms         | 0 074 ms                                         | 0.202 ms |  |  |  |

- Caution 1. Mounted board layout should be made in such a way that no current flows into or flows from the CD pin since the impedance of the CD pin is high, otherwise correct delay time cannot be provided.

- 2. There is no limit for the capacitance of C<sub>D</sub> as long as the leakage current of the capacitor can be ignored against the built-in constant current value (30 nA to 200 nA).

- 3. The detection delay time (tDET) cannot be adjusted by CD.

#### 4. Other characteristics

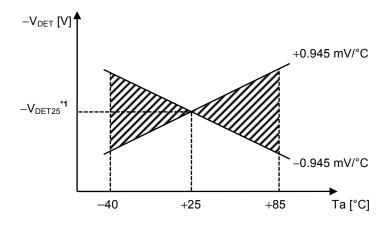

#### 4.1 Temperature characteristics of detection voltage

The shaded area in **Figure 32** shows the temperature characteristics of detection voltage in the operation temperature range.

\*1.  $-V_{DET25}$  is a detection voltage value at Ta = +25°C.

#### Figure 32 Temperature Characteristics of Detection Voltage (Example for -VDET = 2.7 V)

#### 4. 2 Temperature characteristics of release voltage

The temperature change  $\frac{\Delta + V_{\text{DET}}}{\Delta Ta}$  of the release voltage is calculated by using the temperature change  $\frac{\Delta - V_{\text{DET}}}{\Delta Ta}$  of the detection voltage as follows:

$$\frac{\Delta + V_{\text{DET}}}{\Delta \text{Ta}} = \frac{+V_{\text{DET}}}{-V_{\text{DET}}} \times \frac{\Delta - V_{\text{DET}}}{\Delta \text{Ta}}$$

The temperature change of the release voltage and the detection voltage has the same sign consequently.

#### 4. 3 Temperature characteristics of hysteresis voltage

The temperature change of the hysteresis voltage is expressed as  $\frac{\Delta + V_{DET}}{\Delta Ta} - \frac{\Delta - V_{DET}}{\Delta Ta}$  and is calculated as follows:

$$\frac{\Delta + V_{DET}}{\Delta Ta} - \frac{\Delta - V_{DET}}{\Delta Ta} = \frac{V_{HYS}}{-V_{DET}} \times \frac{\Delta - V_{DET}}{\Delta Ta}$$

#### Precautions

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- In CMOS output product of the S-1004 Series, the feed-through current flows at the time of detection and release. If the VDD pin input impedance is high, malfunction may occur due to the voltage drop by the feed-through current when releasing.

- In CMOS output product, oscillation may occur if a pull-down resistor is connected and falling speed of the SENSE pin voltage (V<sub>SENSE</sub>) is slow near the detection voltage when the VDD pin and the SENSE pin are shorted.

- When designing for mass production using an application circuit described herein, the product deviation and temperature characteristics of the external parts should be taken into consideration. SII Semiconductor Corporation shall not bear any responsibility for patent infringements related to products using the circuits described herein.

- SII Semiconductor Corporation claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

#### Characteristics (Typical Data)

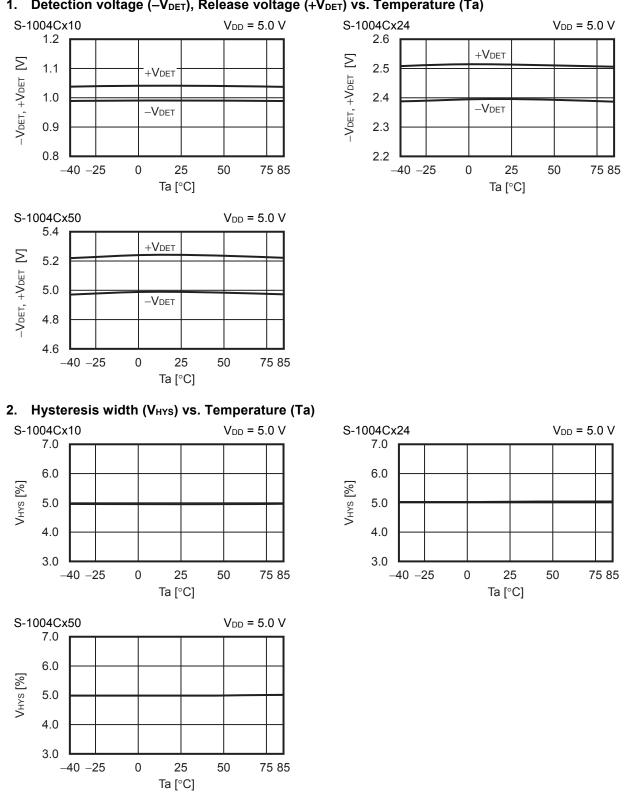

#### 1. Detection voltage (–V<sub>DET</sub>), Release voltage (+V<sub>DET</sub>) vs. Temperature (Ta)

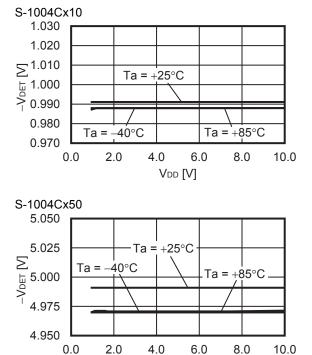

#### 3. Detection voltage (-VDET) vs. Power supply voltage (VDD)

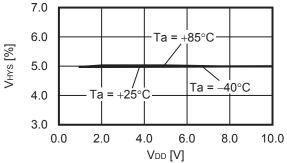

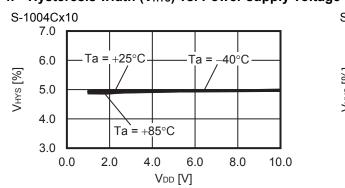

4. Hysteresis width (V<sub>HYS</sub>) vs. Power supply voltage (V<sub>DD</sub>)

VDD [V]

S-1004Cx50