Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### S-1410/1411 Series

www.ablic.com

# $$105^{\circ}\text{C}$$ OPERATION, 3.8 $\mu\text{A}$ CURRENT CONSUMPTION WATCHDOG TIMER WITH RESET FUNCTION

© ABLIC Inc., 2015-2018 Rev.2.3\_00

The S-1410/1411 Series is a watchdog timer developed using CMOS technology, which can operate with low current consumption of  $3.8 \,\mu\text{A}$  typ. The reset function and the low voltage detection function are available.

#### ■ Features

Detection voltage:

2.0 V to 5.0 V, selectable in 0.1 V step

• Detection voltage accuracy: ±1.5%

• Input voltage:  $V_{DD} = 0.9 \text{ V to } 6.0 \text{ V}$

Hysteresis width: 5% typ.

Current consumption: 3.8 μA typ.

• Reset time-out period: 14.5 ms typ. (C<sub>POR</sub> = 2200 pF)

Watchdog operation is switchable: Enable, Disable

Watchdog operation voltage range: V<sub>DD</sub> = 2.5 V to 6.0 V

Watchdog mode switching function\*1:

Time-out mode, window mode

• Watchdog input edge is selectable: Rising edge, falling edge, both rising and falling edges

• Product type is selectable: S-1410 Series

(Product with  $\overline{W}$  / T pin (Output:  $\overline{WDO}$  pin))

S-1411 Series

(Product without  $\overline{W}$  / T pin (Output:  $\overline{RST}$  pin,  $\overline{WDO}$  pin))

• Operation temperature range: Ta = -40°C to +105°C

• Lead-free (Sn 100%), halogen-free

#### ■ Application

• Power supply monitoring and system monitoring in microcontroller mounted apparatus

#### ■ Packages

- TMSOP-8

- HSNT-8(2030)

<sup>\*1.</sup> The S-1411 Series is fixed to the window mode.

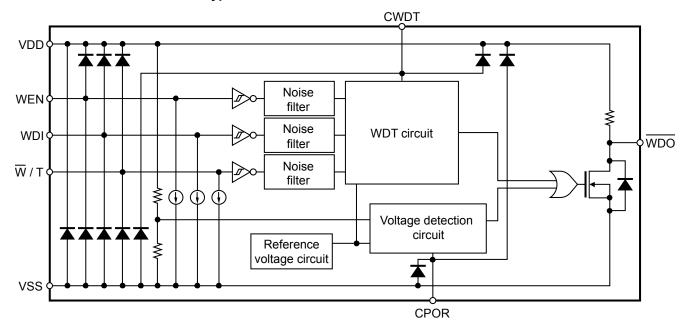

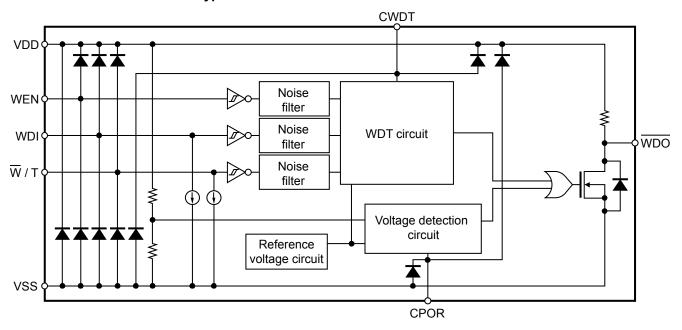

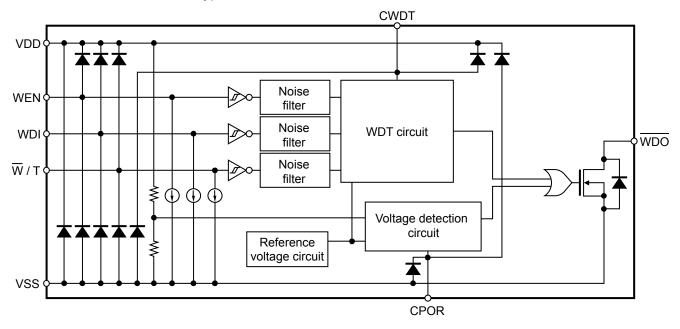

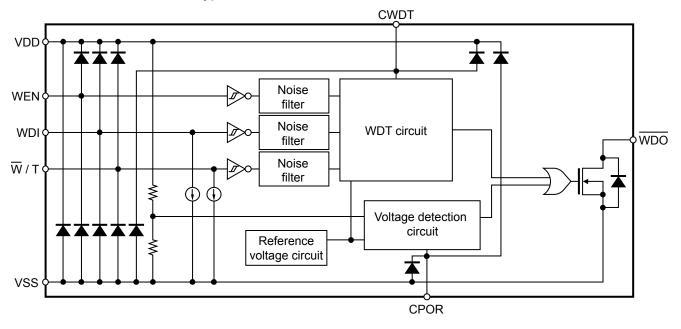

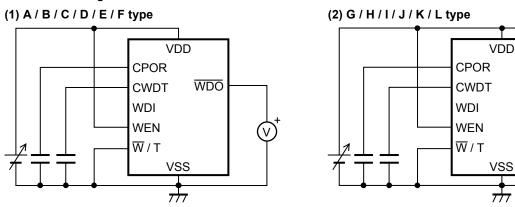

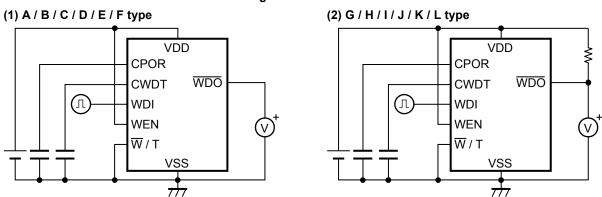

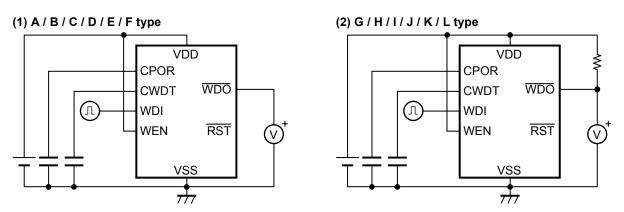

#### **■** Block Diagrams

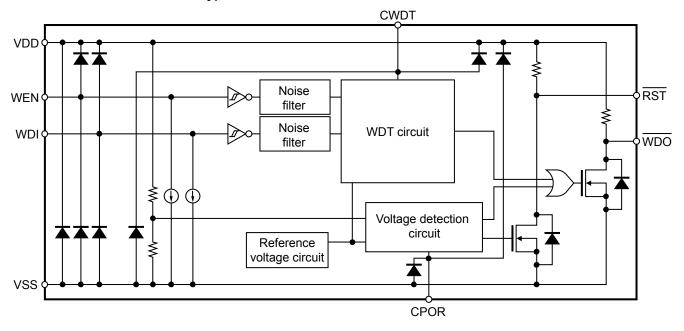

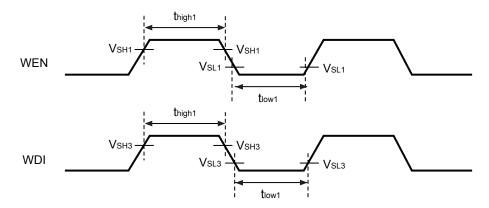

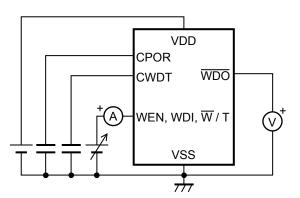

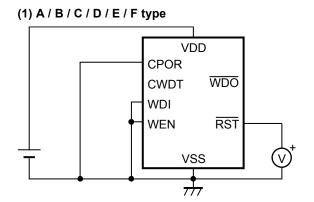

#### 1. S-1410 Series A / B / C Type

Figure 1

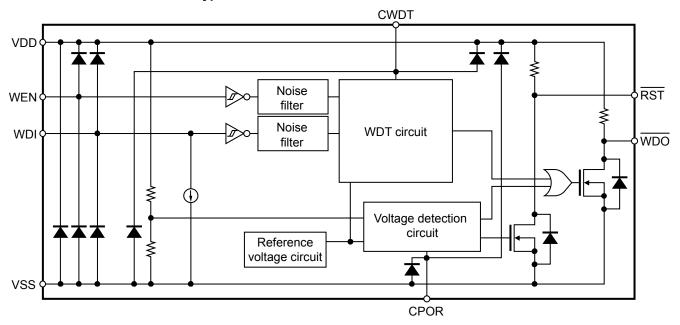

#### 2. S-1410 Series D / E / F Type

Figure 2

2 ABLIC Inc.

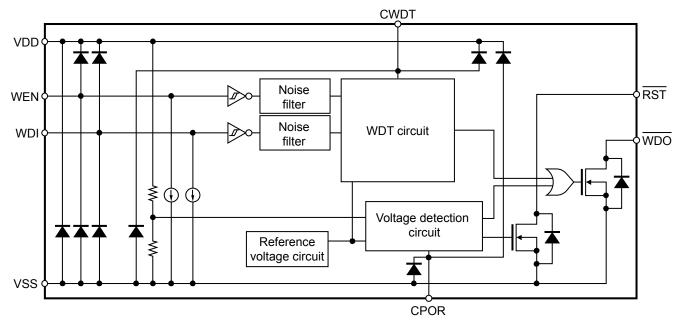

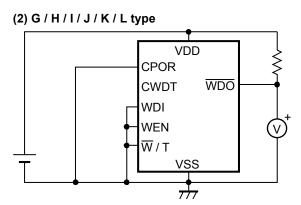

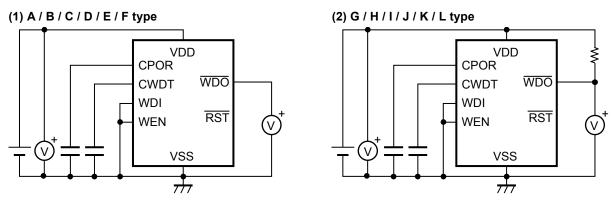

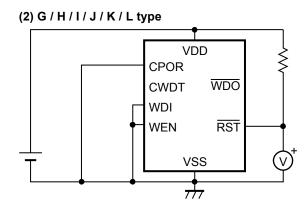

#### 3. S-1410 Series G / H / I Type

Figure 3

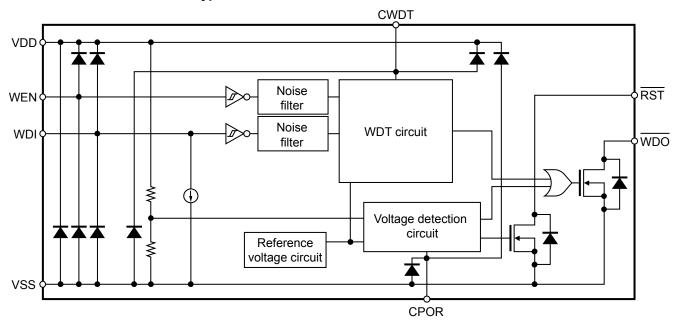

#### 4. S-1410 Series J / K / L Type

Figure 4

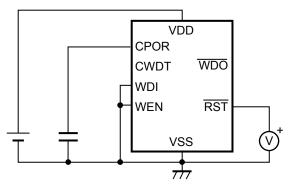

#### 5. S-1411 Series A / B / C Type

Figure 5

#### 6. S-1411 Series D / E / F Type

Figure 6

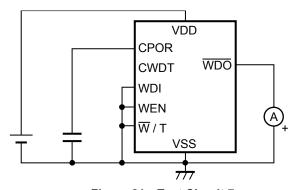

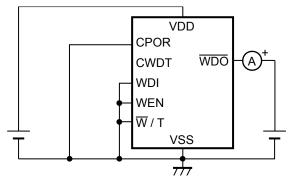

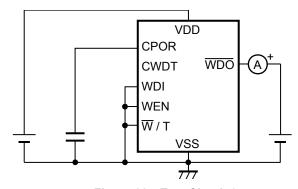

#### 7. S-1411 Series G / H / I Type

Figure 7

#### 8. S-1411 Series J / K / L Type

Figure 8

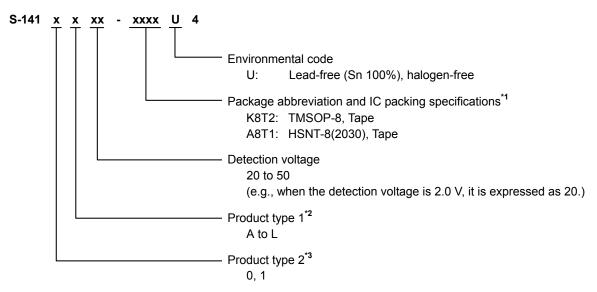

#### **■ Product Name Structure**

Users can select the product type, detection voltage, and package type for the S-1410/1411 Series. Refer to "1. Product name" regarding the contents of product name, "2. Product type list" regarding the product types, "3. Packages" regarding the package drawings.

#### 1. Product name

- **\*1.** Refer to the tape drawing.

- \*2. Refer to "2. Product type list".

- \*3. 0: S-1410 Series (Product with  $\overline{W}$  / T pin)

The  $\overline{\text{WDO}}$  pin outputs the signals which are from the watchdog timer circuit and the voltage detection circuit.

1: S-1411 Series (Product without  $\overline{W}$  / T pin)

The WDO pin outputs the signals which are from the watchdog timer circuit and the voltage detection circuit.

The  $\overline{\mathsf{RST}}$  pin outputs the signal which is from the voltage detection circuit.

The watchdog mode is fixed to the window mode.

#### 2. Product type list

Table 1

| Product Type | WEN Pin Logic | Constant Current Source Pull-down for WEN Pin | Input Edge                    | Output Pull-up<br>Resistor |

|--------------|---------------|-----------------------------------------------|-------------------------------|----------------------------|

| Α            | Active "H"    | Available                                     | Rising edge                   | Available                  |

| В            | Active "H"    | Available                                     | Falling edge                  | Available                  |

| С            | Active "H"    | Available                                     | Both rising and falling edges | Available                  |

| D            | Active "L"    | Unavailable                                   | Rising edge                   | Available                  |

| Е            | Active "L"    | Unavailable                                   | Falling edge                  | Available                  |

| F            | Active "L"    | Unavailable                                   | Both rising and falling edges | Available                  |

| G            | Active "H"    | Available                                     | Rising edge                   | Unavailable                |

| Н            | Active "H"    | Available                                     | Falling edge                  | Unavailable                |

| I            | Active "H"    | Available                                     | Both rising and falling edges | Unavailable                |

| J            | Active "L"    | Unavailable                                   | Rising edge                   | Unavailable                |

| K            | Active "L"    | Unavailable                                   | Falling edge                  | Unavailable                |

| L            | Active "L"    | Unavailable                                   | Both rising and falling edges | Unavailable                |

#### 3. Packages

Table 2 Package Drawing Codes

| Package Name | Dimension    | Tape         | Reel         | Land         |  |  |  |  |  |

|--------------|--------------|--------------|--------------|--------------|--|--|--|--|--|

| TMSOP-8      | FM008-A-P-SD | FM008-A-C-SD | FM008-A-R-SD | _            |  |  |  |  |  |

| HSNT-8(2030) | PP008-A-P-SD | PP008-A-C-SD | PP008-A-R-SD | PP008-A-L-SD |  |  |  |  |  |

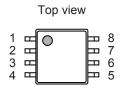

#### **■** Pin Configurations

#### 1. TMSOP-8

Figure 9

Table 3 S-1410 Series

| Pin No. | Symbol  | Description                          |  |  |

|---------|---------|--------------------------------------|--|--|

| 1       | W / T*1 | Watchdog mode switching pin          |  |  |

| 2       | CPOR    | Reset time-out period adjustment pin |  |  |

| 3       | CWDT    | Watchdog time adjustment pin         |  |  |

| 4       | VSS     | GND pin                              |  |  |

| 5       | WEN     | Watchdog enable pin                  |  |  |

| 6       | WDO     | Watchdog output and reset output pin |  |  |

| 7       | WDI     | Watchdog input pin                   |  |  |

| 8       | VDD     | Voltage input pin                    |  |  |

Table 4 S-1411 Series

| Pin No. | Symbol | Description                          |  |  |  |

|---------|--------|--------------------------------------|--|--|--|

| 1       | RST    | Reset output pin                     |  |  |  |

| 2       | CPOR   | Reset time-out period adjustment pin |  |  |  |

| 3       | CWDT   | Watchdog time adjustment pin         |  |  |  |

| 4       | VSS    | GND pin                              |  |  |  |

| 5       | WEN    | Watchdog enable pin                  |  |  |  |

| 6       | WDO    | Watchdog output pin                  |  |  |  |

| 7       | WDI    | Watchdog input pin                   |  |  |  |

| 8       | VDD    | Voltage input pin                    |  |  |  |

<sup>\*1.</sup>  $\overline{W}$  / T pin = "H": Time-out mode  $\overline{W}$  / T pin = "L": Window mode

#### 2. HSNT-8(2030)

Bottom view

Figure 10

Table 5 S-1410 Series

| Pin No. | Symbol  | Description                          |

|---------|---------|--------------------------------------|

| 1       | W / T*2 | Watchdog mode switching pin          |

| 2       | CPOR    | Reset time-out period adjustment pin |

| 3       | CWDT    | Watchdog time adjustment pin         |

| 4       | VSS     | GND pin                              |

| 5       | WEN     | Watchdog enable pin                  |

| 6       | WDO     | Watchdog output and reset output pin |

| 7       | WDI     | Watchdog input pin                   |

| 8       | VDD     | Voltage input pin                    |

Table 6 S-1411 Series

| Pin No. Symbol |      | Description                          |  |  |

|----------------|------|--------------------------------------|--|--|

| 1              | RST  | Reset output pin                     |  |  |

| 2              | CPOR | Reset time-out period adjustment pin |  |  |

| 3              | CWDT | Watchdog time adjustment pin         |  |  |

| 4              | VSS  | GND pin                              |  |  |

| 5              | WEN  | Watchdog enable pin                  |  |  |

| 6              | WDO  | Watchdog output pin                  |  |  |

| 7              | WDI  | Watchdog input pin                   |  |  |

| 8              | VDD  | Voltage input pin                    |  |  |

- **\*1.** Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2.  $\overline{W}$  / T pin = "H": Time-out mode  $\overline{W}$  / T pin = "L": Window mode

#### ■ Pin Functions

Refer to "■ Operations" for details.

#### 1. $\overline{W}$ / T pin (S-1410 Series only)

This is a pin to switch the watchdog mode.

The S-1410 Series changes to the time-out mode when the  $\overline{W}$  / T pin is "H", and changes to the window mode when the  $\overline{W}$  / T pin is "L". Switching the mode is prohibited during the operation.

The  $\overline{W}$  / T pin is connected to a constant current source (0.3  $\mu$ A typ.) and is pulled down internally.

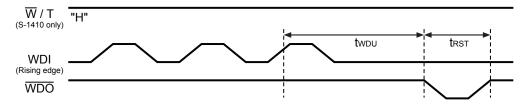

#### 1. 1 Time-out mode ( $\overline{W}$ / T pin = "H")

The S-1410 Series detects an abnormality when not inputting an edge to the WDI pin during the watchdog time-out period ( $t_{WDU}$ ). And then "L" is output from the  $\overline{WDO}$  pin.

Figure 11 Abnormality Detection in Time-out Mode

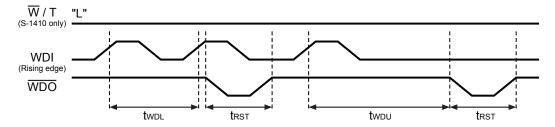

#### 1. 2 Window mode ( $\overline{W}$ / T pin = "L")

When not inputting an edge to the WDI pin during  $t_{WDU}$ , or when an edge is input to the WDI pin again within a specific period of time (the discharge time due to an edge detection + 1 charge-discharge time ( $t_{WDL}$ )) after inputting an edge to the WDI pin, the  $\overline{WDO}$  pin output changes from "H" to "L".

Figure 12 Abnormality Detection in Window Mode

#### 2. RST pin (S-1411 Series only)

This is a reset output pin. It outputs "L" when detecting a low voltage.

Be sure to connect an external pull-up resistor ( $R_{\text{extR}}$ ) to the  $\overline{\text{RST}}$  pin in the product without an output pull-up resistor.

#### 3. WDO pin

#### 3. 1 S-1410 Series

This pin combines the reset output and the watchdog output (time-out detection, double pulse detection). Be sure to connect an external pull-up resistor ( $R_{extW}$ ) to the  $\overline{WDO}$  pin in the product without an output pull-up resistor. **Table 7** shows the  $\overline{WDO}$  pin output status.

Operation Status

| On south an Otation            | WDO Pin         |                 |  |  |

|--------------------------------|-----------------|-----------------|--|--|

| Operation Status               | ₩ / T Pin = "H" | ₩ / T Pin = "L" |  |  |

| Normal operation               | "H"             | "H"             |  |  |

| Low voltage detection          | "L"             | "L"             |  |  |

| Time-out detection             | "L"             | "L"             |  |  |

| Double pulse detection         | "H"             | "L"             |  |  |

| When watchdog timer is Disable | "H"             | "H"             |  |  |

#### 3. 2 S-1411 Series

This is the watchdog output (time-out detection, double pulse detection) pin.

Be sure to connect an external pull-up resistor ( $R_{extW}$ ) to the  $\overline{WDO}$  pin in the product without an output pull-up resistor. **Table 8** shows the  $\overline{WDO}$  pin and  $\overline{RST}$  pin output statuses.

**Operation Status** WDO Pin RST Pin Normal operation "H" "H" Low voltage detection "L" "L" Time-out detection "H" Double pulse detection "L" "H" When watchdog timer is Disable "H" "H"

Table 8

#### 4. CPOR pin

This is a pin to connect an adjustment capacitor for reset output delay time ( $C_{POR}$ ) in order to generate the reset time-out period ( $t_{RST}$ ).  $C_{POR}$  is charged and discharged by an internal constant current circuit, and the charge-discharge duration is  $t_{RST}$ .

t<sub>RST</sub> is calculated by using the following equation. Take into consideration C<sub>POR</sub> variation.

$$t_{RST}$$

= 6,500,000 ×  $C_{POR}$  [F] + 0.0002

#### 5. CWDT pin

This is a pin to connect an adjustment capacitor for watchdog output delay time ( $C_{WDT}$ ) in order to generate the watchdog time-out period ( $t_{WDU}$ ) and the watchdog double pulse detection time ( $t_{WDL}$ ).  $C_{WDT}$  is charged and discharged by an internal constant current circuit.

t<sub>WDU</sub> is calculated by using the following equation. Take into consideration C<sub>WDT</sub> variation.

$$t_{WDU} = 50,000,000 \times C_{WDT} [F] + 0.0011$$

Moreover, twoL is calculated by using the following equation.

$$t_{WDL} = \frac{t_{WDU}}{32}$$

# 105°C OPERATION, 3.8 $\mu$ A CURRENT CONSUMPTION WATCHDOG TIMER WITH RESET FUNCTION S-1410/1411 Series Rev.2.3 $_{00}$

#### 6. WEN pin

This is a pin to switch Enable / Disable of the watchdog timer.

The voltage detection circuit independently operates at all times regardless of the watchdog timer operation.

#### 6. 1 S-1410/1411 Series A / B / C / G / H / I type (WEN pin logic active "H" product)

The watchdog timer becomes Enable if the input is "H", and the charge-discharge operation is performed at the CWDT pin.

The WEN pin is connected to a constant current source (0.3 µA typ.) and is pulled down internally.

#### 6. 2 S-1410/1411 Series D / E / F / J / K / L type (WEN pin logic active "L" product)

The watchdog timer becomes Enable if the input is "L", and the charge-discharge operation is performed at the CWDT pin.

The WEN pin is not pulled down internally.

#### 7. WDI pin

This is an input pin to receive a signal from the monitored object. By inputting an edge at an appropriate timing, the WDI pin confirms the normal operation of the monitored object.

The WDI pin is connected to a constant current source (0.3 µA typ.) and is pulled down internally.

#### ■ Absolute Maximum Ratings

Table 9

(Ta = +25°C unless otherwise specified)

| Item                           |                  | Symbol               | Absolute Maximum Rating                      | Unit |

|--------------------------------|------------------|----------------------|----------------------------------------------|------|

| VDD pin voltage                |                  | $V_{DD}$             | $V_{SS} - 0.3$ to $V_{SS} + 7.0$             | V    |

| WDI pin voltage                |                  | $V_{WDI}$            | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+7.0$ | V    |

| WEN pin voltage                |                  | $V_{WEN}$            | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+7.0$ | V    |

| $\overline{W}$ / T pin voltage |                  | $V_{\overline{W}/T}$ | $V_{SS}-0.3$ to $V_{DD}+0.3 \le V_{SS}+7.0$  | V    |

| CPOR pin voltage               |                  | V <sub>CPOR</sub>    | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+7.0$ | V    |

| CWDT pin voltage               |                  | V <sub>CWDT</sub>    | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+7.0$ | V    |

| RST pin voltage                | A/B/C/D/E/F type |                      | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+7.0$ | V    |

| KST pili voltage               | G/H/I/J/K/L type | V <sub>RST</sub>     | $V_{SS} - 0.3$ to $V_{SS} + 7.0$             | V    |

| WDO pin voltage                | A/B/C/D/E/F type | V <sub>WDO</sub>     | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+7.0$ | V    |

| VVDO pili voltage              | G/H/I/J/K/L type | ▼ WDO                | $V_{SS} - 0.3$ to $V_{SS} + 7.0$             | V    |

| Operation ambient temperature  |                  | T <sub>opr</sub>     | −40 to +105                                  | °C   |

| Storage temperatur             | re               | T <sub>stg</sub>     | −40 to +150                                  | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

#### ■ Thermal Resistance Value

Table 10

| Item                        | Symbol       | Condition    |         | Min. | Тур. | Max. | Unit |

|-----------------------------|--------------|--------------|---------|------|------|------|------|

|                             |              |              | Board A | -    | 160  | -    | °C/W |

|                             |              |              | Board B | 1    | 133  | 1    | °C/W |

|                             |              | TMSOP-8      | Board C | ı    | -    | ı    | °C/W |

|                             | $	heta_{JA}$ |              | Board D | ı    | _    | ı    | °C/W |

| Junction-to-ambient thermal |              |              | Board E | ı    | -    | ı    | °C/W |

| resistance*1                |              | HSNT-8(2030) | Board A | 1    | 181  | 1    | °C/W |

|                             |              |              | Board B | -    | 135  | -    | °C/W |

|                             |              |              | Board C | 1    | 40   | -    | °C/W |

|                             |              |              | Board D | 1    | 42   | ı    | °C/W |

|                             |              |              | Board E | I    | 32   |      | °C/W |

<sup>\*1.</sup> Test environment: compliance with JEDEC STANDARD JESD51-2A

**Remark** Refer to "■ **Power Dissipation**" and "**Test Board**" for details.

#### ■ Recommended Operation Conditions

Table 11

| 14010 11                                            |                      |                                               |      |      |      |      |  |  |

|-----------------------------------------------------|----------------------|-----------------------------------------------|------|------|------|------|--|--|

| Item                                                | Symbol               | Condition                                     | Min. | Тур. | Max. | Unit |  |  |

| VDD nin voltage                                     | .,                   | Detector block                                | 0.9  | _    | 6.0  | V    |  |  |

| VDD pin voltage                                     | $V_{DD}$             | Watchdog timer block                          | 2.5  | _    | 6.0  | V    |  |  |

| Set detection voltage                               | -V <sub>DET(S)</sub> | 0.1 V step                                    | 2.0  | -    | 5.0  | V    |  |  |

| External pull-up resistor for RST pin               | R <sub>extR</sub>    | S-1411 Series G / H / I / J / K / L type      | 10   | 100  | -    | kΩ   |  |  |

| External pull-up resistor for WDO pin               | R <sub>extW</sub>    | S-1410/1411 Series G / H / I / J / K / L type | 10   | 100  | -    | kΩ   |  |  |

| Adjustment capacitor for reset output delay time    | C <sub>POR</sub>     | -                                             | 0.1  | 2.2  | 1000 | nF   |  |  |

| Adjustment capacitor for watchdog output delay time | C <sub>WDT</sub>     | _                                             | 0.1  | 0.47 | 1000 | nF   |  |  |

#### **■** Electrical Characteristics

#### 1. S-1410 Series

Table 12 (1 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specified)

| Item                                 | Symbol             | Condi                                                                                   | •                        | Min.                       | Тур.                   | Max.                         | Unit | Test<br>Circuit |

|--------------------------------------|--------------------|-----------------------------------------------------------------------------------------|--------------------------|----------------------------|------------------------|------------------------------|------|-----------------|

| Detection voltage*1                  | -V <sub>DET</sub>  |                                                                                         |                          | $-V_{DET(S)} \times 0.985$ | -V <sub>DET(S)</sub>   | -V <sub>DET(S)</sub> × 1.015 | V    | 1               |

| Hysteresis width                     | V <sub>HYS</sub>   |                                                                                         |                          | -V <sub>DET</sub> × 0.03   | $-V_{DET} \times 0.05$ | -V <sub>DET</sub> × 0.07     | ٧    | 1               |

| Current consumption during operation | I <sub>SS1</sub>   | When watchdog to                                                                        | imer operates            | _                          | 3.8                    | 7.8                          | μΑ   | 2               |

| Reset time-out period                | t <sub>RST</sub>   | C <sub>POR</sub> = 2200 pF                                                              |                          | 8.7                        | 14.5                   | 20                           | ms   | 3               |

| Watchdog time-out period             | $t_{\text{WDU}}$   | $C_{WDT}$ = 470 pF                                                                      |                          | 15                         | 24.6                   | 34                           | ms   | 3               |

| Watchdog double pulse detection time | t <sub>WDL</sub>   | C <sub>WDT</sub> = 470 pF                                                               |                          | 461                        | 769                    | 1077                         | μs   | 4               |

| Watchdog output voltage "H"          | $V_{WOH}$          | A/B/C/D/E/F                                                                             | type only                | $V_{DD} - 1.0$             | -                      | _                            | V    | 5               |

| Watchdog output voltage "L"          | V <sub>WOL</sub>   | External pull-up resistor of 100 k $\Omega$ is connected for G / H / I / J / K / L type |                          | _                          | -                      | 0.4                          | ٧    | 6               |

| Watchdog output pull-up current      | I <sub>WUP</sub>   | $V_{\overline{WDO}} = 0 \text{ V},$<br>A/B/C/D/E/F                                      | type only                | _                          | -0.85                  | -0.4                         | μΑ   | 7               |

|                                      |                    |                                                                                         | V <sub>DD</sub> = 1.5 V  | 0.6                        | 1.1                    | -                            | mA   | 8               |

| Matabalan a ta ta anasat             |                    |                                                                                         | V <sub>DD</sub> = 1.8 V  | 1.1                        | 1.6                    | -                            | mA   | 8               |

| Watchdog output current              | I <sub>WOUT</sub>  | $V_{DS} = 0.4 V$                                                                        | $V_{DD} = 2.5 \text{ V}$ | 2.1                        | 2.6                    | -                            | mA   | 8               |

|                                      |                    |                                                                                         | V <sub>DD</sub> = 3.0 V  | 2.8                        | 3.3                    | -                            | mA   | 8               |

| Watchdog output leakage current      | I <sub>WLEAK</sub> | V <sub>DS</sub> = 6.0 V, V <sub>DD</sub> = 6.0 V                                        |                          | _                          | _                      | 0.096                        | μΑ   | 9               |

| Input pin voltage 1 "H"              | V <sub>SH1</sub>   | WEN pin                                                                                 |                          | $0.7 \times V_{DD}$        | _                      | -                            | V    | 10              |

| Input pin voltage 1 "L"              | V <sub>SL1</sub>   | WEN pin                                                                                 |                          |                            | _                      | $0.3 \times V_{DD}$          | V    | 10              |

| Input pin voltage 2 "H"              | V <sub>SH2</sub>   | _                                                                                       |                          | $0.7 \times V_{DD}$        | _                      | _                            | V    | 10              |

| Input pin voltage 2 "L"              | V <sub>SL2</sub>   | $\overline{W}$ / T pin                                                                  |                          | _                          | -                      | $0.3 \times V_{DD}$          | V    | 10              |

| Input pin voltage 3 "H"              | V <sub>SH3</sub>   | WDI pin                                                                                 |                          | $0.7 \times V_{DD}$        | _                      |                              | V    | 10              |

| Input pin voltage 3 "L"              | $V_{SL3}$          | WDI pin                                                                                 |                          |                            | -                      | $0.3 \times V_{DD}$          | V    | 10              |

Table 12 (2 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specified)

| (WEN pirriogic active 11 product, VDI |                    |                                                                               |                                                                | 0.0 1, 10 | 1200 | arnoco our | 01 11100 0 | poomoa          |

|---------------------------------------|--------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------|-----------|------|------------|------------|-----------------|

| Item                                  | Symbol             | Condition                                                                     |                                                                | Min.      | Тур. | Max.       | Unit       | Test<br>Circuit |

| Input pin current 1 "H"               |                    | WEN pin,                                                                      | A/B/C<br>/G/H/I<br>type                                        | -         | 0.3  | 1.0        | μΑ         | 10              |

|                                       | I <sub>SH1</sub>   | V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 6.0 V                         | D/E/F<br>/J/K/L<br>type                                        | -0.1      | П    | 0.1        | μΑ         | 10              |

| Input pin current 1 "L"               | I <sub>SL1</sub>   | WEN pin, V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 0 V                  |                                                                | -0.1      | -    | 0.1        | μΑ         | 10              |

| Input pin current 2 "H"               | I <sub>SH2</sub>   | $\overline{W}$ / T pin,<br>V <sub>DD</sub> = 6.0 V, Input pin voltage = 6.0 V |                                                                | _         | 0.3  | 1.0        | μΑ         | 10              |

| Input pin current 2 "L"               | I <sub>SL2</sub>   | W / T pin,<br>V <sub>DD</sub> = 6.0 V, Input pin voltage = 0 V                |                                                                | -0.1      | -    | 0.1        | μΑ         | 10              |

| Input pin current 3 "H"               | I <sub>SH3</sub>   |                                                                               | WDI pin, V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 6.0 V |           | 0.3  | 1.0        | μΑ         | 10              |

| Input pin current 3 "L"               | I <sub>SL3</sub>   | WDI pin, $V_{DD} = 6.0 \text{ V}$<br>Input pin voltage = 0                    |                                                                | -0.1      | 1    | 0.1        | μΑ         | 10              |

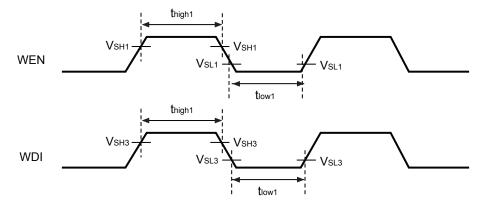

| Input pulse width "H"*2               | t <sub>high1</sub> |                                                                               |                                                                | 1.5       | _    | _          | μs         | 10              |

| Input pulse width "L"*2               | t <sub>low1</sub>  | _                                                                             |                                                                | 1.5       | ı    | _          | μs         | 10              |

| Watchdog output delay time            | twout              | -                                                                             |                                                                | -         | 25   | 40         | μs         | 3               |

| Reset output delay time               | t <sub>ROUT</sub>  | _                                                                             |                                                                | _         | 25   | 40         | μs         | 3               |

| Input setup time                      | t <sub>iset</sub>  | _                                                                             |                                                                | 1.0       | -    | _          | μs         | 3               |

- \*1. -V<sub>DET</sub>: Actual detection voltage, -V<sub>DET(S)</sub>: Set detection voltage

- \*2. The input pulse width "H" (t<sub>high1</sub>) and the input pulse width "L" (t<sub>low1</sub>) are defined as shown in **Figure 13**. Inputs to the WEN pin and the WDI pin should be greater than or equal to the min. value specified in "■ **Electrical Characteristics**".

Figure 13

#### 2. S-1411 Series

#### Table 13 (1 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specified)

| (WEN pin logic active "H" product, $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specifi |                    |                                                                                         |                                      |                            |                              |                     |                 |    |  |  |

|---------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|--------------------------------------|----------------------------|------------------------------|---------------------|-----------------|----|--|--|

| Item                                                                                              | Symbol             | Condi                                                                                   | Min.                                 | Тур.                       | Max.                         | Unit                | Test<br>Circuit |    |  |  |

| Detection voltage <sup>*1</sup>                                                                   | -V <sub>DET</sub>  | _                                                                                       | $-V_{\text{DET(S)}} \\ \times 0.985$ | -V <sub>DET(S)</sub>       | -V <sub>DET(S)</sub> × 1.015 | V                   | 11              |    |  |  |

| Hysteresis width                                                                                  | V <sub>HYS</sub>   | -                                                                                       | -V <sub>DET</sub> × 0.03             | $-V_{DET} \times 0.05$     | -V <sub>DET</sub> × 0.07     | V                   | 11              |    |  |  |

| Current consumption during operation                                                              | I <sub>SS1</sub>   | When watchdog timer operates                                                            |                                      | _                          | 3.8                          | 7.8                 | μΑ              | 12 |  |  |

| Reset time-out period                                                                             | t <sub>RST</sub>   | C <sub>POR</sub> = 2200 pF                                                              | 8.7                                  | 14.5                       | 20                           | ms                  | 13              |    |  |  |

| Watchdog time-out period                                                                          | $t_{WDU}$          | C <sub>WDT</sub> = 470 pF                                                               |                                      | 15                         | 24.6                         | 34                  | ms              | 13 |  |  |

| Watchdog double pulse detection time                                                              | t <sub>WDL</sub>   | C <sub>WDT</sub> = 470 pF                                                               |                                      | 461                        | 769                          | 1077                | μs              | 14 |  |  |

| Reset output voltage "H"                                                                          | $V_{ROH}$          | A / B / C / D / E / F type only                                                         |                                      | $V_{DD} - 1.0$             | _                            | _                   | V               | 15 |  |  |

| Reset output voltage "L"                                                                          | V <sub>ROL</sub>   | External pull-up resistor of 100 k $\Omega$ is connected for G / H / I / J / K / L type |                                      | _                          | _                            | 0.4                 | V               | 16 |  |  |

| Reset output pull-up current                                                                      | I <sub>RUP</sub>   | $V_{\overline{RST}} = 0 V$ ,<br>A / B / C / D / E / F type only                         |                                      | _                          | -0.85                        | -0.4                | μΑ              | 17 |  |  |

|                                                                                                   | I <sub>ROUT</sub>  | V <sub>DS</sub> = 0.4 V                                                                 | V <sub>DD</sub> = 1.5 V              | 0.6                        | 1.1                          | _                   | mA              | 18 |  |  |

| Reset output current                                                                              |                    |                                                                                         | V <sub>DD</sub> = 1.8 V              | 1.1                        | 1.6                          | _                   | mA              | 18 |  |  |

|                                                                                                   |                    |                                                                                         | V <sub>DD</sub> = 2.5 V              | 2.1                        | 2.6                          | _                   | mA              | 18 |  |  |

|                                                                                                   |                    |                                                                                         | V <sub>DD</sub> = 3.0 V              | 2.8                        | 3.3                          | _                   | mA              | 18 |  |  |

| Reset output leakage current                                                                      | I <sub>RLEAK</sub> | V <sub>DS</sub> = 6.0 V, V <sub>DD</sub> = 6.0 V                                        |                                      | _                          | _                            | 0.096               | μΑ              | 19 |  |  |

| Watchdog output voltage "H"                                                                       | $V_{WOH}$          | A / B / C / D / E / F type only                                                         |                                      | $V_{DD} - 1.0$             | _                            | _                   | V               | 20 |  |  |

| Watchdog output voltage "L"                                                                       | V <sub>woL</sub>   | External pull-up resistor of 100 k $\Omega$ is connected for G / H / I / J / K / L type |                                      | _                          | _                            | 0.4                 | V               | 21 |  |  |

| Watchdog output pull-up current                                                                   | I <sub>WUP</sub>   | $V_{\overline{WDO}} = 0 \text{ V},$<br>A / B / C / D / E / F type only                  |                                      | _                          | -0.85                        | -0.4                | μΑ              | 22 |  |  |

| Watchdog output current                                                                           | I <sub>WOUT</sub>  | V <sub>DS</sub> = 0.4 V                                                                 | V <sub>DD</sub> = 1.5 V              | 0.6                        | 1.1                          | _                   | mA              | 23 |  |  |

|                                                                                                   |                    |                                                                                         | V <sub>DD</sub> = 1.8 V              | 1.1                        | 1.6                          | _                   | mA              | 23 |  |  |

|                                                                                                   |                    |                                                                                         | V <sub>DD</sub> = 2.5 V              | 2.1                        | 2.6                          | _                   | mA              | 23 |  |  |

|                                                                                                   |                    |                                                                                         | V <sub>DD</sub> = 3.0 V              | 2.8                        | 3.3                          |                     | mA              | 23 |  |  |

| Watchdog output leakage current                                                                   | I <sub>WLEAK</sub> | V <sub>DS</sub> = 6.0 V, V <sub>DD</sub> = 6.0 V                                        |                                      | _                          | -                            | 0.096               | μА              | 24 |  |  |

| Input pin voltage 1 "H"                                                                           | V <sub>SH1</sub>   | WEN pin                                                                                 |                                      | $0.7 \times V_{DD}$        | -                            | _                   | V               | 25 |  |  |

| Input pin voltage 1 "L"                                                                           | $V_{SL1}$          | WEN pin                                                                                 |                                      | _                          | _                            | $0.3 \times V_{DD}$ | V               | 25 |  |  |

| Input pin voltage 3 "H"                                                                           | V <sub>SH3</sub>   | WDI pin                                                                                 |                                      | $0.7 \times V_{\text{DD}}$ | _                            | _                   | V               | 25 |  |  |

| Input pin voltage 3 "L"                                                                           | $V_{SL3}$          | WDI pin                                                                                 |                                      | _                          | _                            | $0.3 \times V_{DD}$ | V               | 25 |  |  |

Table 13 (2 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ ,  $Ta = +25^{\circ}\text{C}$  unless otherwise specified)

| Item                       | Symbol             | Condition                                                         |                         | Min. | Тур. | Max. | Unit | Test<br>Circuit |

|----------------------------|--------------------|-------------------------------------------------------------------|-------------------------|------|------|------|------|-----------------|

| Input pin current 1 "H"    | I <sub>SH1</sub>   | WEN pin,<br>V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 6.0 V | A/B/C<br>/G/H/I<br>type | -    | 0.3  | 1.0  | μΑ   | 25              |

|                            |                    |                                                                   | D/E/F<br>/J/K/L<br>type | -0.1 | _    | 0.1  | μΑ   | 25              |

| Input pin current 1 "L"    | I <sub>SL1</sub>   | WEN pin, $V_{DD} = 6.0 \text{ V}$ ,<br>Input pin voltage = 0 V    |                         | -0.1 | _    | 0.1  | μΑ   | 25              |

| Input pin current 3 "H"    | I <sub>SH3</sub>   | WDI pin, $V_{DD} = 6.0 \text{ V}$ ,<br>Input pin voltage = 6.0 V  |                         | -    | 0.3  | 1.0  | μΑ   | 25              |

| Input pin current 3 "L"    | I <sub>SL3</sub>   | WDI pin, $V_{DD} = 6.0 \text{ V}$ ,<br>Input pin voltage = 0 V    |                         | -0.1 | _    | 0.1  | μΑ   | 25              |

| Input pulse width "H"*2    | t <sub>high1</sub> | _                                                                 |                         | 1.5  | _    | -    | μs   | 25              |

| Input pulse width "L"*2    | t <sub>low1</sub>  | _                                                                 |                         | 1.5  | _    | _    | μs   | 25              |

| Watchdog output delay time | t <sub>wout</sub>  | _                                                                 |                         | _    | 25   | 40   | μs   | 13              |

| Reset output delay time    | t <sub>ROUT</sub>  | -                                                                 |                         | _    | 25   | 40   | μs   | 13              |

| Input setup time           | t <sub>iset</sub>  |                                                                   |                         | 1.0  |      | _    | μs   | 13              |

- \*1.  $-V_{DET}$ : Actual detection voltage,  $-V_{DET(S)}$ : Set detection voltage

- \*2. The input pulse width "H" (thigh1) and the input pulse width "L" (tlow1) are defined as shown in Figure 14. Inputs to the WEN pin and the WDI pin should be greater than or equal to the min. value specified in "■ Electrical Characteristics".

Figure 14

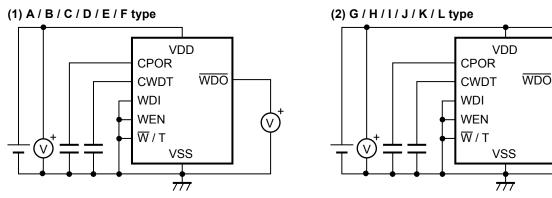

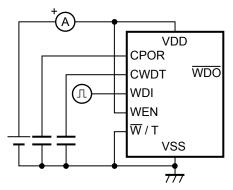

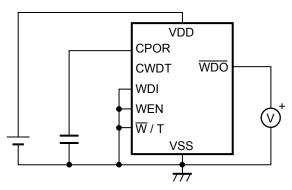

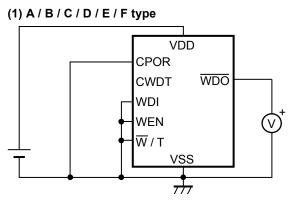

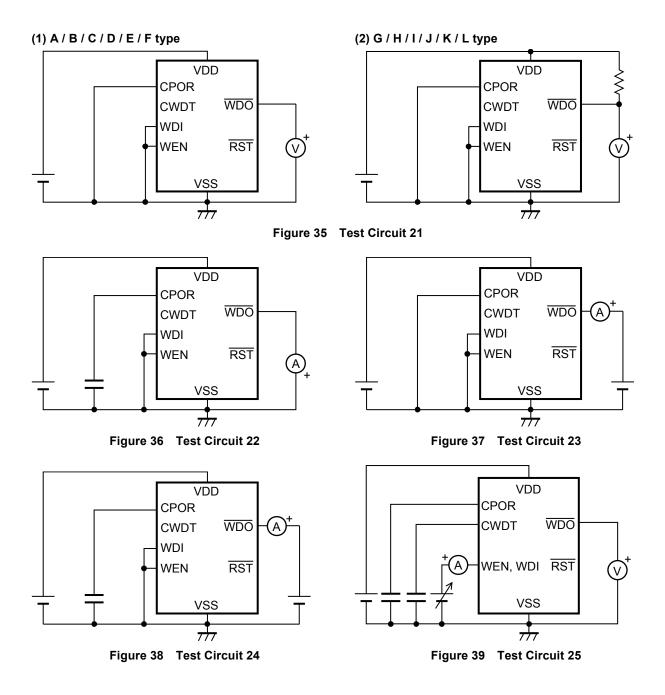

#### ■ Test Circuits

Refer to " $\blacksquare$  Recommended Operation Conditions" when setting constants of external pull-up resistors ( $R_{extR}$ ,  $R_{extW}$ ) and external capacitors ( $C_{POR}$ ,  $C_{WDT}$ ).

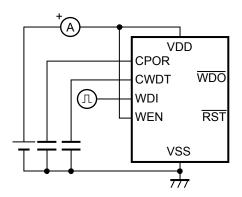

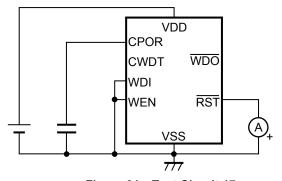

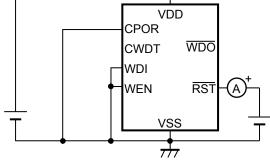

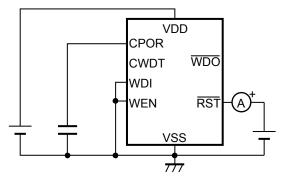

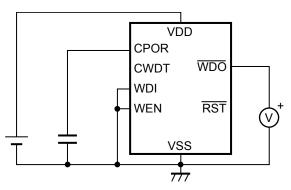

#### 1. S-1410 Series

Figure 15 Test Circuit 1

Figure 16 Test Circuit 2

Figure 17 Test Circuit 3

**WDO**

Figure 18 Test Circuit 4

18

Figure 19 Test Circuit 5

Figure 20 Test Circuit 6

Figure 21 Test Circuit 7

Figure 22 Test Circuit 8

Figure 23 Test Circuit 9

Figure 24 Test Circuit 10

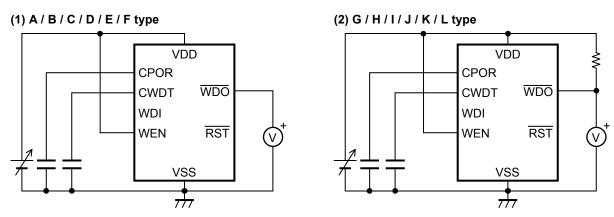

#### 2. S-1411 Series

Figure 25 Test Circuit 11

Figure 26 Test Circuit 12

Figure 27 Test Circuit 13

Figure 28 Test Circuit 14

Figure 29 Test Circuit 15

Figure 30 Test Circuit 16

Figure 31 Test Circuit 17

Figure 32 Test Circuit 18

Figure 33 Test Circuit 19

Figure 34 Test Circuit 20

#### ■ Operations

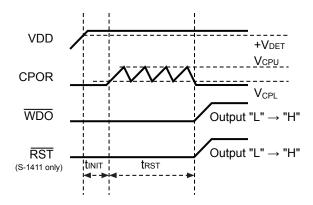

#### 1. From power-on to reset release

The S-1410/1411 Series initiates the initialization if the VDD pin voltage exceeds the release voltage ( $+V_{DET}$ ). The charge-discharge operation to the CPOR pin is initiated after the passage of the initialization time ( $t_{INIT}$ ), and the  $\overline{WDO}$  pin output and the  $\overline{RST}$  pin output change from "L" to "H" after the operation is performed 4 times.

**Remark**  $V_{CPU}$ : CPOR charge upper limit threshold (1.25 V typ.)  $V_{CPL}$ : CPOR charge lower limit threshold (0.20 V typ.)

Figure 40

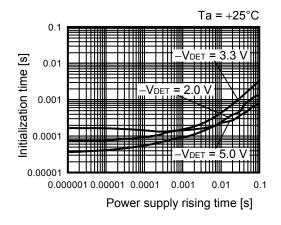

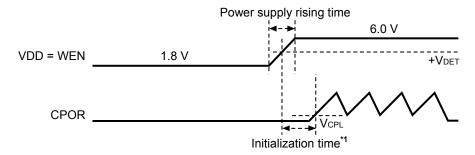

$t_{INIT}$  changes according to the power supply rising time. Refer to **Figure 41** for the relation between  $t_{INIT}$  and the power supply rising time.

Figure 41 Power Supply Rising Time Dependency of Initialization Time

\*1. The initialization time is the time period from when the VDD pin voltage reaches +V<sub>DET</sub> to when C<sub>POR</sub> rises.

Figure 42 Initialization Time

#### 2. From reset release to initiation of charge-discharge operation to CWDT pin

The charge-discharge operation to the CWDT pin differs depending on the status of the WEN pin at the reset release.

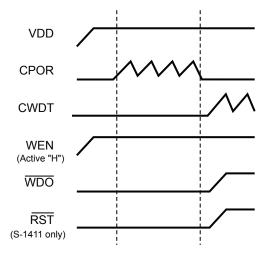

#### 2. 1 When WEN pin is "H" at reset release (Active "H")

Since the watchdog timer is Enable, the S-1410/1411 Series initiates the charge-discharge operation to the CWDT pin.

Figure 43 WEN Pin = "H"

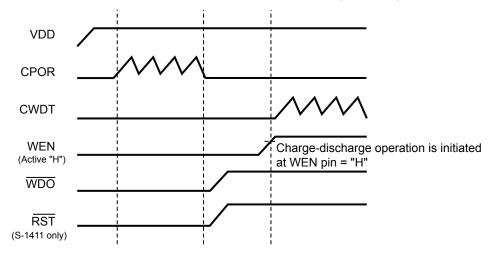

#### 2. 2 When WEN pin is "L" at reset release (Active "H")

Since the watchdog timer is Disable after the CPOR pin performs the charge-discharge operation 4 times, the S-1410/1411 Series does not initiate the charge-discharge operation to the CWDT pin. If the input to the WEN pin changes to "H" in this status, the S-1410/1411 Series initiates the charge-discharge operation to the CWDT pin.

Figure 44 WEN Pin = "L" → "H"

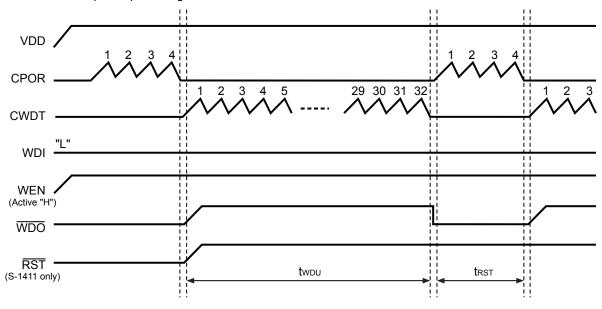

#### 3. Watchdog time-out detection

The watchdog timer detects a time-out after the charge-discharge operation to the CWDT pin is performed 32 times, then the  $\overline{\text{WDO}}$  pin output changes from "H" to "L".

Figure 45

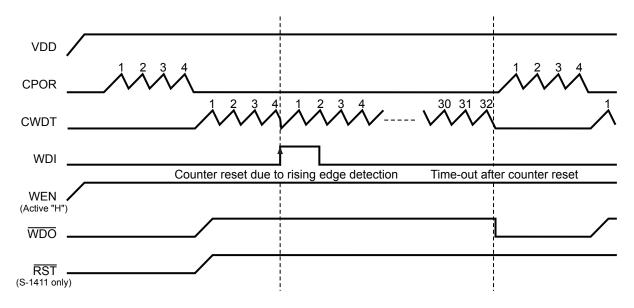

#### 4. Internal counter reset due to edge detection

When the WDI pin detects an edge during the charge-discharge operation to the CWDT pin, the internal counter which counts the number of times of the charge-discharge operation is reset. The CWDT pin initiates the discharge operation when an edge is detected, and initiates the charge-discharge operation again after the discharge operation is completed.

# 4. 1 Counter reset due to rising edge detection (S-141xAxx, S-141xDxx, S-141xGxx, S-141xJxx)

Figure 46