Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### www.sii-ic.com

## 2-WIRE REAL-TIME CLOCK

© SII Semiconductor Corporation, 2007-2016

Rev.3.1 02

The S-35399A03 is a CMOS 2-wire real-time clock IC which operates with the very low current consumption in the wide range of operation voltage. The operation voltage is 1.3 V to 5.5 V so that the S-35399A03 can be used for various power supplies from main supply to backup battery. Due to the 0.34  $\mu$ A current consumption and wide range of power supply voltage at time keeping, The S-35399A03 makes the battery life longer. In the system which operates with a backup battery, the included free registers can be used as the function for user's backup memory. Users always can take back the information in the registers which is stored before power-off the main power supply, after the voltage is restored.

The S-35399A03 has the function to correct advance / delay of the clock data speed, in the wide range, which is caused by the crystal oscillation circuit's frequency deviation. Correcting according to the temperature change by combining this function and a temperature sensor, it is possible to make a high precise clock function which is not affected by the ambient temperature. Moreover, the S-35399A03 has a 24-bit binary up counter. This counter counts up every 60 seconds from power-on so that users are able to grasp the elapsed time from power-on up to 30 years.

### **■** Features

• Low current consumption:

$0.34 \mu A \text{ typ.} (V_{DD} = 3.0 \text{ V}, \text{ Ta} = +25^{\circ}\text{C})$

Wide range of operating voltage: 1.3 V to 5.5 V

- · Built-in clock correction function

- Built-in 24-bit binary up counter

- · Built-in free user register

- 2-wire (I<sup>2</sup>C-bus) CPU interface

- Built-in alarm interrupter

- Built-in flag generator during detection of low power voltage or at power-on

- Auto calendar up to the year 2099, automatic leap year calculation function

- Built-in constant voltage circuit

- Built-in 32.768 kHz crystal oscillator (built-in C<sub>d</sub>, external C<sub>g</sub>)

- Lead-free, Sn 100%, halogen-free\*

- \*1. Refer to "■ Product Name Structure" for details.

### ■ Applications

- · Mobile game device

- Mobile AV device

- Digital still camera

- · Digital video camera

- Electronic power meter

- DVD recorder

- TV, VCR

- · Mobile phone, PHS

### ■ Package

• 8-Pin SOP (JEDEC)

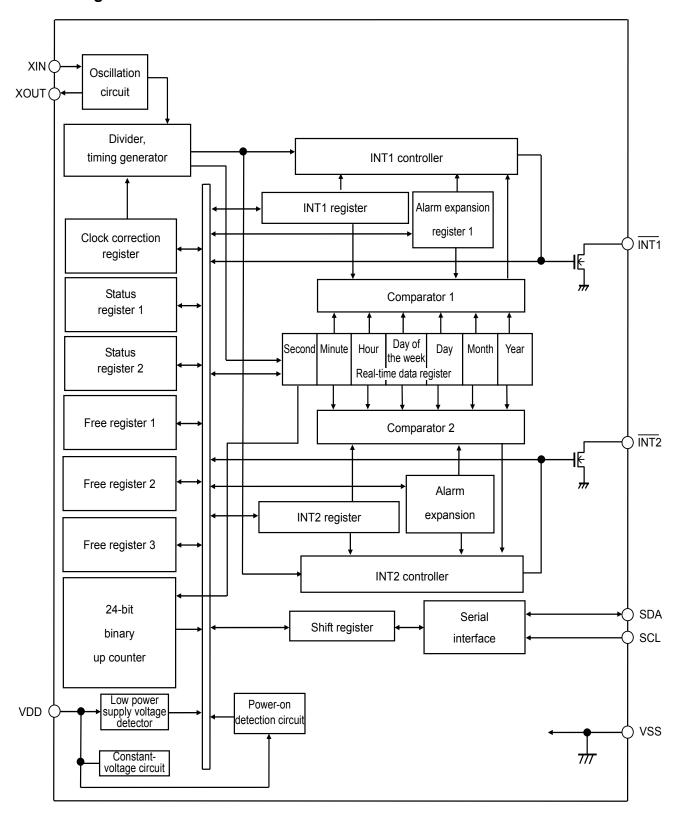

## **■** Block Diagram

Figure 1

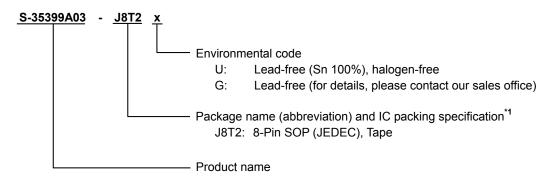

## **■ Product Name Structure**

### 1. Product name

\*1. Refer to the tape drawing.

### 2. Package

Table 1 Package Drawing Codes

| Packa             | age Name               | Dimension    | Tape         | Reel         |

|-------------------|------------------------|--------------|--------------|--------------|

| 0 D: 00D (JEDEO)  | Environmental code = G | FJ008-A-P-SD | FJ008-D-C-SD | FJ008-D-R-SD |

| 8-Pin SOP (JEDEC) | Environmental code = U | FJ008-A-P-SD | FJ008-D-C-SD | FJ008-D-R-S1 |

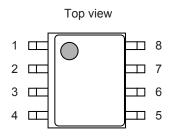

## **■** Pin Configuration

## 1. 8-Pin SOP (JEDEC)

Figure 2 S-35399A03-J8T2x

Table 2 List of Pins

|   | Pin No | Symbol | Description                       | I/O    | Configuration                                                       |

|---|--------|--------|-----------------------------------|--------|---------------------------------------------------------------------|

| ĺ | 1      | ĪNT1   | Output pin for interrupt signal 1 | Output | Nch open-drain output (no protective diode at VDD)                  |

| I | 2      | XOUT   | Connection pins                   |        |                                                                     |

| Ì | 3      | XIN    | for crystal oscillator            | _      | _                                                                   |

| Ī | 4      | VSS    | GND pin                           |        | _                                                                   |

|   | 5      | ĪNT2   | Output pin for interrupt signal 2 | Output | Nch open-drain output (no protective diode at VDD)                  |

|   | 6      | SCL    | Input pin for serial clock        | Input  | CMOS input<br>(no protective diode at VDD)                          |

|   | 7      | SDA    | I/O pin for serial data           |        | Nch open-drain output<br>(no protective diode at VDD)<br>CMOS input |

|   | 8      | VDD    | Pin for positive power supply     | _      | -                                                                   |

Remark 1. x: G or U

**2.** Please select products of environmental code = U for Sn 100%, halogen-free products.

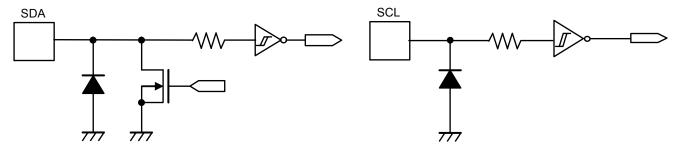

#### ■ Pin Functions

### 1. SDA (I/O for serial data) pin

This pin is a data input / output pin of I<sup>2</sup>C-bus interface. This pin inputs / outputs data by synchronizing with a clock pulse from the SCL pin. This pin has CMOS input and Nch open-drain output. Generally in use, pull up this pin to the VDD potential via a resistor, and connect it to any other device having open drain or open collector output with wired-OR connection.

#### 2. SCL (input for serial clock) pin

This pin is to input a clock pulse for I<sup>2</sup>C-bus interface. The SDA pin inputs / outputs data by synchronizing with the clock pulse.

### 3. XIN, XOUT (crystal oscillator connect) pins

Connect a crystal oscillator between XIN and XOUT.

### 4. INT1 (output for interrupt signal 1) pin

This pin outputs a signal of interrupt, or a clock pulse. By using the status register 2, users can select either of; alarm 1 interrupt, output of user-set frequency, per-minute edge interrupt, minute-periodical interrupt 1, minute-periodical interrupt 2, or 32.768 kHz output. This pin has Nch open-drain output.

### 5. INT2 (output for interrupt signal 2) pin

This pin outputs a signal of interrupt, or a clock pulse. By using the status register 2, users can select either of; alarm 2 interrupt, output of user-set frequency, per-minute edge interrupt or minute-periodical interrupt 1. This pin has Nch open-drain output.

#### 6. VDD (positive power supply) pin

Connect this VDD pin with a positive power supply. Regarding the values of voltage to be applied, refer to **"E Recommended Operation Conditions"**.

#### 7. VSS pin

Connect this VSS pin to GND.

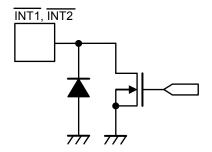

#### ■ Equivalent Circuits of Pins

Figure 3 SDA Pin

Figure 4 SCL Pin

Figure 5 INT1 Pin, INT2 Pin

## ■ Absolute Maximum Ratings

Table 3

| Item                            | Symbol           | Applied Pin     | Absolute Maximum Rating              | Unit |

|---------------------------------|------------------|-----------------|--------------------------------------|------|

| Power supply voltage            | $V_{DD}$         | _               | $V_{\rm SS}-0.3$ to $V_{\rm SS}+6.5$ | V    |

| Input voltage                   | V <sub>IN</sub>  | SCL, SDA        | $V_{SS} - 0.3$ to $V_{SS} + 6.5$     | V    |

| Output voltage                  | V <sub>OUT</sub> | SDA, INT1, INT2 | $V_{SS} - 0.3$ to $V_{SS} + 6.5$     | V    |

| Operating ambient temperature*1 | T <sub>opr</sub> | -               | -40 to +85                           | °C   |

| Storage temperature             | T <sub>stg</sub> | _               | -55 to +125                          | °C   |

<sup>\*1.</sup> Conditions with no condensation or frost. Condensation or frost causes short-circuiting between pins, resulting in a malfunction.

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

## **■** Recommended Operation Conditions

Table 4

$(V_{SS} = 0 V)$

| Item                                    | Symbol           | Condition           | Min.                    | Тур. | Max. | Unit |

|-----------------------------------------|------------------|---------------------|-------------------------|------|------|------|

| Power supply voltage*1                  | $V_{DD}$         | Ta = -40°C to +85°C | 1.3                     | 3.0  | 5.5  | V    |

| Time keeping power supply voltage*2     | V <sub>DDT</sub> | Ta = -40°C to +85°C | V <sub>DET</sub> – 0.15 | 1    | 5.5  | ٧    |

| Crystal oscillator C <sub>L</sub> value | C <sub>L</sub>   | _                   | _                       | 6    | 7    | pF   |

<sup>\*1.</sup> The power supply voltage that allows communication under the conditions shown in Table 9 of "■ AC Electrical Characteristics".

#### ■ Oscillation Characteristics

Table 5

$(Ta = +25^{\circ}C, V_{DD} = 3.0 \text{ V}, V_{SS} = 0 \text{ V}, SSP-T7-FL crystal oscillator } (C_{L} = 6 \text{ pF}, 32.768 \text{ kHz}) \text{ manufactured by Seiko Instruments Inc.})$

| Item                             | Symbol           | Condition                        | Min. | Тур. | Max. | Unit  |

|----------------------------------|------------------|----------------------------------|------|------|------|-------|

| Oscillation start voltage        | $V_{STA}$        | Within 10 seconds                | 1.1  | -    | 5.5  | V     |

| Oscillation start time           | t <sub>STA</sub> | _                                | _    | _    | 1    | S     |

| IC-to-IC frequency deviation*1   | δΙC              | -                                | -10  | -    | +10  | ppm   |

| Frequency voltage deviation      | δV               | V <sub>DD</sub> = 1.3 V to 5.5 V | -3   | -    | +3   | ppm/V |

| External capacitance             | Cg               | Applied to XIN pin               | _    | 1    | 9.1  | pF    |

| Internal oscillation capacitance | C <sub>d</sub>   | Applied to XOUT pin              |      | 8    | -    | pF    |

<sup>\*1.</sup> Reference value

<sup>\*2.</sup> The power supply voltage that allows time keeping. For the relationship with V<sub>DET</sub> (low power supply voltage detection voltage), refer to "■ Characteristics (Typical Data)".

## **■ DC Electrical Characteristics**

Table 6 DC Characteristics ( $V_{DD} = 3.0 \text{ V}$ )

(Ta = -40 °C to +85°C,  $V_{SS}$  = 0 V, SSP-T7-FL crystal oscillator (C<sub>L</sub> = 6 pF, 32.768 kHz,  $C_0$  = 9.1 pF) manufactured by Seiko Instruments Inc.)

| (10 - 40 0 to 100 0, 155 -             |                  | Ĭ               | л (С <u>L — 6 рг, 32.766 кн</u> 2, С <sub>g</sub> —                  |                     | •    | 1                   | ,    |

|----------------------------------------|------------------|-----------------|----------------------------------------------------------------------|---------------------|------|---------------------|------|

| Item                                   | Symbol           | Applied Pin     | Condition                                                            | Min.                | Тур. | Max.                | Unit |

| Current consumption 1                  | $I_{DD1}$        | _               | Out of communication                                                 | _                   | 0.34 | 0.97                | μΑ   |

| Current consumption 2                  | I <sub>DD2</sub> | -               | Out of communication<br>(when 32.768 kHz is<br>output from INT1 pin) | -                   | 0.60 | 1.47                | μΑ   |

| Current consumption 3                  | I <sub>DD3</sub> | _               | During communication (SCL = 100 kHz)                                 | _                   | 9    | 14                  | μΑ   |

| Input current leakage 1                | I <sub>IZH</sub> | SCL, SDA        | $V_{IN} = V_{DD}$                                                    | -0.5                | 1    | 0.5                 | μΑ   |

| Input current leakage 2                | I <sub>IZL</sub> | SCL, SDA        | $V_{IN} = V_{SS}$                                                    | -0.5                | 1    | 0.5                 | μΑ   |

| Output current leakage 1               | I <sub>OZH</sub> | SDA, INT1, INT2 | $V_{OUT} = V_{DD}$                                                   | -0.5                | -    | 0.5                 | μΑ   |

| Output current leakage 2               | I <sub>OZL</sub> | SDA, INT1, INT2 | V <sub>OUT</sub> = V <sub>SS</sub>                                   | -0.5                | ı    | 0.5                 | μΑ   |

| Input voltage 1                        | $V_{IH}$         | SCL, SDA        | _                                                                    | $0.8 \times V_{DD}$ | 1    | $V_{SS} + 5.5$      | V    |

| Input voltage 2                        | $V_{IL}$         | SCL, SDA        | _                                                                    | $V_{\text{SS}}-0.3$ | 1    | $0.2 \times V_{DD}$ | V    |

| Output current 1                       | I <sub>OL1</sub> | INT1, INT2      | V <sub>OUT</sub> = 0.4 V                                             | 3                   | 5    |                     | mA   |

| Output current 2 I <sub>OL2</sub>      |                  | SDA             | V <sub>OUT</sub> = 0.4 V                                             | 5                   | 10   | _                   | mA   |

| Power supply voltage detection voltage | $V_{DET}$        | _               | -                                                                    | 0.65                | 1    | 1.35                | >    |

## Table 7 DC Characteristics ( $V_{DD} = 5.0 \text{ V}$ )

(Ta =  $-40^{\circ}$ C to  $+85^{\circ}$ C,  $V_{SS}$  = 0 V, SSP-T7-FL crystal oscillator ( $C_L$  = 6 pF, 32.768 kHz,  $C_g$  = 9.1 pF) manufactured by Seiko Instruments Inc.)

| Item                                                                                | Symbol           | Applied Pin        | Condition                                                            | Min.                | Тур. | Max.                | Unit |

|-------------------------------------------------------------------------------------|------------------|--------------------|----------------------------------------------------------------------|---------------------|------|---------------------|------|

| Current consumption 1                                                               | I <sub>DD1</sub> | -                  | Out of communication                                                 | _                   | 0.36 | 1.18                | μΑ   |

| Current consumption 2                                                               | I <sub>DD2</sub> | ı                  | Out of communication<br>(when 32.768 kHz is<br>output from INT1 pin) | _                   | 0.82 | 2.17                | μΑ   |

| Current consumption 3                                                               | I <sub>DD3</sub> | -                  | During communication (SCL = 100 kHz)                                 | _                   | 20   | 30                  | μА   |

| Input current leakage 1 I <sub>IZH</sub> SCL, SDA V <sub>IN</sub> = V <sub>DD</sub> |                  |                    |                                                                      | -0.5                | ı    | 0.5                 | μΑ   |

| Input current leakage 2                                                             | I <sub>IZL</sub> | SCL, SDA           | V <sub>IN</sub> = V <sub>SS</sub>                                    | -0.5                | -    | 0.5                 | μΑ   |

| Output current leakage 1                                                            | I <sub>OZH</sub> | SDA, INT1,<br>INT2 | $V_{OUT} = V_{DD}$                                                   | -0.5                | -    | 0.5                 | μА   |

| Output current leakage 2                                                            | I <sub>OZL</sub> | SDA, INT1,<br>INT2 | V <sub>OUT</sub> = V <sub>SS</sub>                                   | -0.5                | -    | 0.5                 | μА   |

| Input voltage 1                                                                     | $V_{IH}$         | SCL, SDA           | -                                                                    | $0.8 \times V_{DD}$ | ı    | $V_{SS} + 5.5$      | V    |

| Input voltage 2                                                                     | $V_{IL}$         | SCL, SDA           | _                                                                    | $V_{\text{SS}}-0.3$ | ı    | $0.2 \times V_{DD}$ | V    |

| Output current 1                                                                    | I <sub>OL1</sub> | INT1, INT2         | V <sub>OUT</sub> = 0.4 V                                             | 5                   | 8    | _                   | mA   |

| Output current 2 I <sub>OL2</sub> S                                                 |                  | SDA                | V <sub>OUT</sub> = 0.4 V                                             | 6                   | 13   | _                   | mA   |

| Power supply voltage detection voltage                                              | $V_{DET}$        | -                  | -                                                                    | 0.65                | 1    | 1.35                | ٧    |

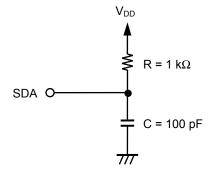

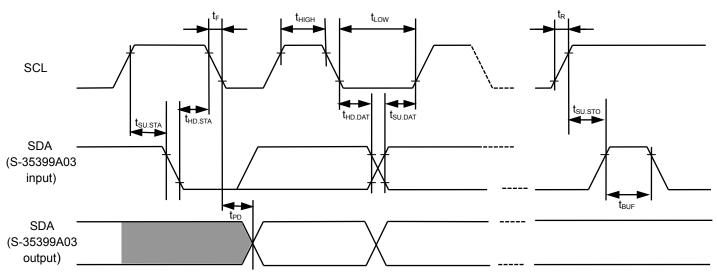

### ■ AC Electrical Characteristics

**Table 8 Measurement Conditions**

| Input pulse voltage          | $V_{IH} = 0.8 \times V_{DD}$ , $V_{IL} = 0.2 \times V_{DD}$ |

|------------------------------|-------------------------------------------------------------|

| Input pulse rise / fall time | 20 ns                                                       |

| Output determination voltage | $V_{OH} = 0.5 \times V_{DD}$ , $V_{OL} = 0.5 \times V_{DD}$ |

| Output load                  | 100 pF + pull-up resistor 1 kΩ                              |

Remark The power supplies of the IC and load have the same electrical potential.

Figure 6 Output Load Circuit

Table 9 AC Electrical Characteristics

$(Ta = -40^{\circ}C \text{ to } +85^{\circ}C)$

| ltore                            | Cymahal             | V              | <sub>DD</sub> *2 ≥ 1.3 | V    | $V_D$          | $_{D}^{*2} \ge 3.0$ | V    | l lmit |

|----------------------------------|---------------------|----------------|------------------------|------|----------------|---------------------|------|--------|

| Item                             | Symbol              | Min. Typ. Max. |                        | Min. | Min. Typ. Max. |                     | Unit |        |

| SCL clock frequency              | f <sub>SCL</sub>    | 0              | _                      | 100  | 0              | _                   | 400  | kHz    |

| SCL clock low time               | $t_{LOW}$           | 4.7            | _                      | _    | 1.3            | _                   | _    | μs     |

| SCL clock high time              | t <sub>HIGH</sub>   | 4              | _                      | _    | 0.6            | _                   | _    | μs     |

| SDA output delay time*1          | t <sub>PD</sub>     | _              | _                      | 3.5  | 1              | _                   | 0.9  | μs     |

| Start condition setup time       | t <sub>SU.STA</sub> | 4.7            | _                      | _    | 0.6            | _                   | _    | μs     |

| Start condition hold time        | t <sub>HD.STA</sub> | 4              | _                      | _    | 0.6            | _                   | _    | μs     |

| Data input setup time            | t <sub>SU.DAT</sub> | 250            | _                      | _    | 100            | _                   | _    | ns     |

| Data input hold time             | t <sub>HD.DAT</sub> | 0              | _                      | _    | 0              | _                   | _    | μs     |

| Stop condition setup time        | t <sub>su.sto</sub> | 4.7            | _                      | _    | 0.6            | _                   | _    | μs     |

| SCL, SDA rise time               | t <sub>R</sub>      | _              | _                      | 1    | 1              | _                   | 0.3  | μs     |

| SCL, SDA fall time               | t <sub>F</sub>      | _              | _                      | 0.3  | _              | _                   | 0.3  | μs     |

| Bus release time t <sub>BU</sub> |                     | 4.7            | _                      | _    | 1.3            | _                   | _    | μs     |

| Noise suppression time           | tı                  | _              | _                      | 100  | _              | _                   | 50   | ns     |

<sup>\*1.</sup> Since the output format of the SDA pin is Nch open-drain output, SDA output delay time is determined by the values of the load resistance (R<sub>L</sub>) and load capacity (C<sub>L</sub>) outside the IC. Therefore, use this value only as a reference value.

\*2. Regarding the power supply voltage, refer to "■ Recommended Operation Conditions".

Figure 7 Bus Timing

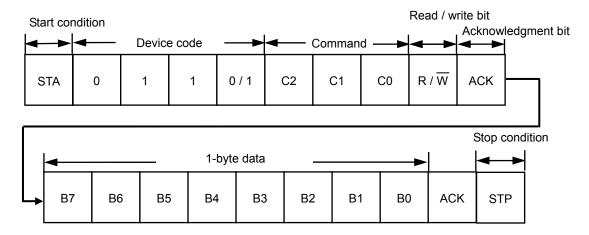

### ■ Configuration of Data Communication

#### 1. Data Communication

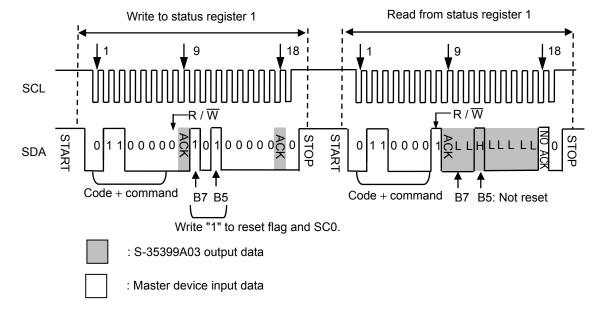

For data communication, the master device in the system generates a start condition for the S-35399A03. Next, the master device transmits 4-bit device code "0110" or "0111", and 3-bit command and 1-bit read / write command to the SDA line. After that, output or input is performed from B7 of data. If data I/O has been completed, finish communication by inputting a stop condition to the S-35399A03. The master device generates an acknowledgment signal for every 1-byte. Regarding details, refer to "■ Serial Interface". Device code "0110" is compatible with the SII Semiconductor Corporation S-35390A/392A as software. Regarding details, refer to "2. Configuration of command".

Figure 8 Data Communication

### 2. Configuration of command

13 types of command are available for the S-35399A03. The S-35399A03 reads / writes the various registers by inputting these codes and commands. The S-35399A03 does not perform any operation with any codes and commands other than those below.

Table 10 List of Commands

|      |       |          |                | Command                              |                                       | Comma                          |                      | Da                | ata         |            |             |                   |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|------|-------|----------|----------------|--------------------------------------|---------------------------------------|--------------------------------|----------------------|-------------------|-------------|------------|-------------|-------------------|-------------------|-----------|----|--|--|--|--|--------------------------------------|----------|----------|----------|----------|------------|------------|-------|--------------|

| Code | C2    | C1       | C0             | Description                          | В7                                    | В6                             | B5                   | B4                | В3          | B2         | B1          | В0                |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0     | 0        | 0              | Status register 1 access             | RESET*1                               |                                | SC0 <sup>*2</sup>    | SC1 <sup>*2</sup> | INT1*3      | INT2*3     | BLD*4       | POC*4             |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0     | 0        | 1              | Status register 2 access             | INT1FE                                | INT1ME                         | INT1AE               | 32kE              | INT2FE      | INT2ME     | INT2AE      | TEST*5            |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      | Y1                                    | Y2                             | Y4                   | Y8                | Y10         | Y20        | Y40         | Y80               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      | M1                                    | M2                             | M4                   | M8                | M10         | _*6        | _*6         | _*6               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | Real-time data 1 access              | D1                                    | D2                             | D4                   | D8                | D10         | D20        | _*6         | _*6               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0 1 0 | 0        | (year data to) | W1                                   | W2                                    | W4                             | _*6                  | _*6               | <b>_</b> *6 | _*6        | _*6         |                   |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      |                                       | (year data to)                 | H1                   | H2                | H4          | H8         | H10         | H20               | AM/PM             | _*6<br>*c |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      | m1                                    | m2                             | m4                   | m8                | m10         | m20        | m40         | _*6<br>_*6        |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      | s1                                    | s2                             | s4                   | s8                | s10         | s20        | s40         |                   |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | Real-time data 2 access              | H1                                    | H2                             | H4                   | H8                | H10         | H20        | AM/PM       | _*6<br>*c         |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0     | 1        | 1              | (hour data to)                       | m1                                    | m2                             | m4                   | m8                | m10         | m20        | m40         | _*6<br>*6         |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | ,                                    | s1                                    | s2                             | s4                   | s8                | s10         | s20        | s40         | _*6               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | INT1 register access                 | W1                                    | W2                             | W4                   | _*6               | _*6         | _*6        | _*6         | A1WE              |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

| 0110 |       |          |                | (alarm time 1: week / hour / minute) | H1                                    | H2                             | H4                   | Н8                | H10         | H20        | AM/PM       | A1HE              |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 4     |          |                | (INT1AE = 1, INT1ME = 0,             | m1                                    | m2                             | m4                   | m8                | m10         | m20        | m40         | A1mE              |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 1     | 0        | 0              | INT1FE = 0) INT1 register access     |                                       |                                |                      |                   |             |            |             |                   |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

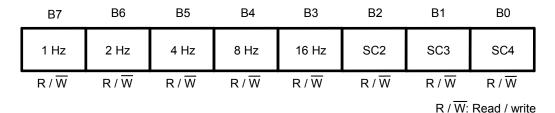

|      |       |          |                | (output of user-set frequency)       | 1 Hz                                  | 2 Hz                           | 4 Hz                 | 8 Hz              | 16 Hz       | SC2*2      | SC3*2       | SC4 <sup>*2</sup> |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | (INT1ME = 0, INT1FE = 1)             | 1112                                  | 2112                           | 7112                 | 0112              | 10112       | 002        | 000         | 004               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       | 1 0 1    |                | INT2 register access                 | 10/4                                  | 14/0                           | 3474                 | _*6               | _*6         | _*6        | _*6         | 4 0) 4 (5         |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      |                                       |                                |                      |                   |             |            |             |                   |                   |           |    |  |  |  |  | (alarm time 2: week / hour / minute) | W1       | W2       | W4       |          |            |            |       | A2WE         |

|      |       |          |                |                                      |                                       |                                |                      |                   |             |            |             |                   |                   |           |    |  |  |  |  | (INT2AE = 1, INT2ME = 0,             | H1<br>m1 | H2<br>m2 | H4<br>m4 | H8<br>m8 | H10<br>m10 | H20<br>m20 | AM/PM | A2HE<br>A2mE |

|      | 1     |          | 1              | INT2FE = 0)                          | 11111                                 | 1112                           | 1114                 | 1110              | 11110       | 11120      | m40         | AZIIIL            |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                |                                      |                                       |                                | INT2 register access |                   |             |            |             |                   | **                | *0        | +0 |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

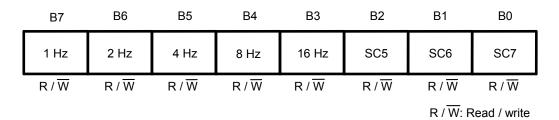

|      |       |          |                |                                      |                                       | (output of user-set frequency) | 1 Hz                 | 2 Hz              | 4 Hz        | 8 Hz       | 16 Hz       | SC5 <sup>*2</sup> | SC6 <sup>*2</sup> | SC7*2     |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | (INT2ME = 0, INT2FE = 1)             |                                       |                                |                      |                   |             |            |             |                   |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 1     | 1        | 0              | Clock correction register access     | V0                                    | V1                             | V2                   | V3                | V4          | V5         | V6          | V7                |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 1     | 1        | 1              | Free register 1 access               | F10                                   | F11                            | F12                  | F13<br>C512k      | F14         | F15<br>C2M | F16         | F17<br>C8M        |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0     | 0        | 0              | Up counter access*7                  | C64k<br>C256                          | C128k<br>C512                  | C256k<br>C1k         | C512k             | C1M<br>C4k  | C2M<br>C8k | C4M<br>C16k | C8M<br>C32k       |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | U     | ١        | ١              | Op counter access                    | C256                                  | C2                             | C1k                  | C2k               | C4K<br>C16  | C32        | C16k        | C32k<br>C128      |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0     | 0        | 1              | Free register 2 access               | F20                                   | F21                            | F22                  | F23               | F24         | F25        | F26         | F27               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 0     | 1        | 0              | Free register 3 access               | F30                                   | F31                            | F32                  | F33               | F34         | F35        | F36         | F37               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

| 0111 | 0111  | <u> </u> | ,              | •                                    | Y1                                    | Y2                             | Y4                   | Y8                | Y10         | Y20        | Y40         | Y80               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

| ]    |       | 0        | 0              | Alarm expansion register 1 access    | M1                                    | M2                             | M4                   | M8                | M10         | _*6        | A1YE        | A1ME              |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | (alarm time 1: year / month / day)   | D1                                    | D2                             | D4                   | D8                | D10         | D20        | _*6         | A1DE              |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | Alama anada a a aista a Caraca       | Y1                                    | Y2                             | Y4                   | Y8                | Y10         | Y20        | Y40         | Y80               |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      | 1     | 0        | 0 1            | 0 1                                  | 0 1 Alarm expansion register 2 access | M1                             | M2                   | M4                | M8          | M10        | _*6         | A2YE              | A2ME              |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

|      |       |          |                | (alarm time 2: year / month / day)   | D1                                    | D2                             | D4                   | D8                | D10         | D20        | _*6         | A2DE              |                   |           |    |  |  |  |  |                                      |          |          |          |          |            |            |       |              |

**<sup>\*1.</sup>** Write-only flag. The S-35399A03 initializes by writing "1" in this register.

<sup>\*2.</sup> Scratch bit. This is a register which is available for read / write operations and can be used by users freely.

<sup>\*3.</sup> Read-only flag. Valid only when using the alarm function. When the alarm time matches, this flag is set to "1", and it is cleared to "0" when reading.

<sup>\*4.</sup> Read-only flag. "POC" is set to "1" when power is applied. It is cleared to "0" when reading. Regarding "BLD", refer to "■ Low Power Supply Voltage Detection Circuit".

<sup>\*5.</sup> Test bit for SII Semiconductor Corporation. Be sure to set to "0" in use.

<sup>\*6.</sup> No effect when writing. It is "0" when reading.

<sup>\*7.</sup> The up counter is a read-only register.

## ■ Configuration of Registers

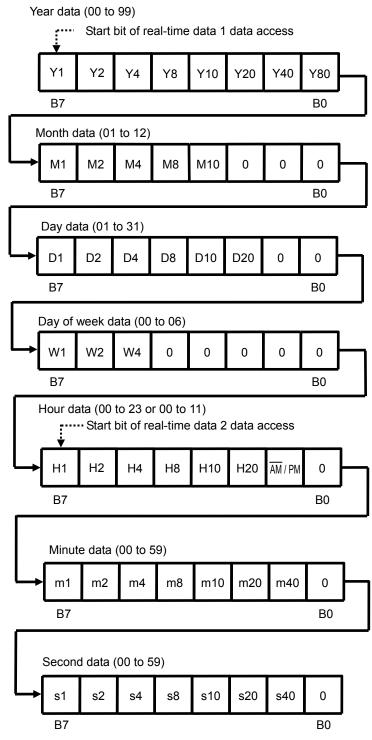

#### 1. Real-time data register

The real-time data register is a 7-byte register that stores the data of year, month, day, day of the week, hour, minute, and second in the BCD code. To write / read real-time data 1 access, transmit / receive the data of year in B7, month, day, day of the week, hour, minute, second in B0, in 7-byte. When you skip the procedure to access the data of year, month, day, day of the week, read / write real-time data 2 access. In this case, transmit / receive the data of hour in B7, minute, second in B0, in 3-byte.

The S-35399A03 transfers a set of data of time to the real-time data register when it recognizes a reading instruction. Therefore, the S-35399A03 keeps precise time even if time-carry occurs during the reading operation of the real-time data register.

Figure 9 Real-Time Data Register

### Year data (00 to 99): Y1, Y2, Y4, Y8, Y10, Y20, Y40, Y80

Sets the lower two digits in the Western calendar year (00 to 99) and links together with the auto calendar function until 2099.

Example: 2053 (Y1, Y2, Y4, Y8, Y10, Y20, Y40, Y80) = (1, 1, 0, 0, 1, 0, 1, 0)

#### Month data (01 to 12): M1, M2, M4, M8, M10

Example: December (M1, M2, M4, M8, M10, 0, 0, 0) = (0, 1, 0, 0, 1, 0, 0, 0)

#### Day data (01 to 31): D1, D2, D4, D8, D10, D20

The count value is automatically changed by the auto calendar function.

1 to 31: Jan., Mar., May, July, Aug., Oct., Dec., 1 to 30: April, June, Sep., Nov.

1 to 29: Feb. (leap year), 1 to 28: Feb. (non-leap year)

Example: 29 (D1, D2, D4, D8, D10, D20, 0, 0) = (1, 0, 0, 1, 0, 1, 0, 0)

#### Day of the week data (00 to 06): W1, W2, W4

A septenary up counter. Day of the week is counted in the order of 00, 01, 02, ..., 06, and 00. Set up day of the week and the count value.

#### Hour data (00 to 23 or 00 to 11): H1, H2, H4, H8, H10, H20, AM / PM

In 12-hour mode, write 0; AM, 1; PM in the AM / PM bit. In 24-hour mode, users can write either 0 or 1. 0 is read when the hour data is from 00 to 11, and 1 is read when from 12 to 23.

```

Example (12-hour mode): 11 p.m. (H1, H2, H4, H8, H10, H20, \overline{AM} / PM, 0) = (1, 0, 0, 0, 1, 0, 1, 0)

Example (24-hour mode): 22 (H1, H2, H4, H8, H10, H20, \overline{AM} / PM, 0) = (0, 1, 0, 0, 0, 1, 1, 0)

```

#### Minute data (00 to 59): m1, m2, m4, m8, m10, m20, m40

```

Example: 32 minutes (m1, m2, m4, m8, m10, m20, m40, 0) = (0, 1, 0, 0, 1, 1, 0, 0)

Example: 55 minutes (m1, m2, m4, m8, m10, m20, m40, 0) = (1, 0, 1, 0, 1, 0, 1, 0)

```

### Second data (00 to 59): s1, s2, s4, s8, s10, s20, s40

Example: 19 seconds (s1, s2, s4, s8, s10, s20, s40, 0) = (1, 0, 0, 1, 1, 0, 0, 0)

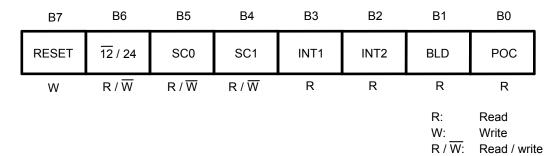

#### 2. Status register 1

Status register 1 is a 1-byte register that is used to display and set various modes. The bit configuration is shown below.

Figure 10 Status Register 1

#### **B0: POC**

This flag is used to confirm whether the power is on. The power-on detection circuit operates at power-on and B0 is set to "1". This flag is read-only. Once it is read, it is automatically set to "0". When this flag is "1", be sure to initialize. Regarding the operation after power-on, refer to "■ Power-on Detection Circuit and Register Status".

#### B1: BLD

This flag is set to "1" when the power supply voltage decreases to the level of detection voltage  $(V_{DET})$  or less. Users can detect a drop in the power supply voltage. Once this flag is set to "1", it is not set to "0" again even if the power supply increases to the level of detection voltage  $(V_{DET})$  or more. This flag is read-only. When this flag is "1", be sure to initialize. Regarding the operation of the power supply voltage detection circuit, refer to "**Low Power Supply Voltage Detection Circuit**".

#### B2, B3: INT2, INT1

This flag indicates the time set by alarm and when the time has reached it. This flag is set to "1" when the time that users set by using the alarm interrupt function has come. The INT1 flag at alarm 1 interrupt mode and the INT2 flag at alarm 2 interrupt mode are set to "1". Set "0" in INT1AE (B5 in the status register 2) or in INT2AE (B1 in the status register 2) after reading "1" in the INT1 flag or in the INT2 flag. This flag is read-only. Once this flag is read, it is set to "0" automatically.

### B4, B5: SC1, SC0

These flags configure a 2-bit SRAM type register that can be freely set by users.

### B6: $\overline{12}/24$

This flag is used to set 12-hour or 24-hour mode. Set the flag ahead of write operation of the real-time data register in case of 24-hour mode.

- 0: 12-hour mode

- 1: 24-hour mode

#### **B7: RESET**

The internal IC is initialized by setting this bit to "1". This bit is Write-only. It is always "0" when reading. When applying the power supply voltage to the IC, be sure to write "1" to this bit to initialize the circuit. Regarding each status of registers after initialization, refer to "■ Register Status After Initialization".

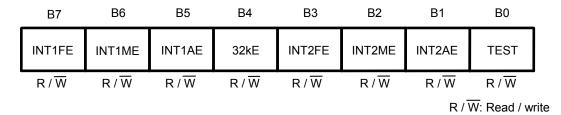

#### 3. Status register 2

Status register 2 is a 1-byte register that is used to display and set various modes. The bit configuration is shown below.

Figure 11 Status Register 2

#### **B0: TEST**

This is a test flag for SII Semiconductor Corporation. Be sure to set this flag to "0" in use. If this flag is set to "1", be sure to initialize to set "0".

#### B1: INT2AE, B2: INT2ME, B3: INT2FE

These bits are used to select the output mode for the  $\overline{\text{INT2}}$  pin. **Table 11** shows how to select the mode. To use an alarm 2 interrupt, set alarm interrupt mode, then access the INT2 register and the alarm expansion register 2.

Table 11 Output Modes for INT2 Pin

| INT2AE | INT2ME | INT2FE | INT2 Pin Output Mode                     |  |

|--------|--------|--------|------------------------------------------|--|

| 0      | 0      | 0      | No interrupt                             |  |

| _*1    | 0      | 1      | Output of user-set frequency             |  |

| _*1    | 1      | 0      | Per-minute edge interrupt                |  |

| _*1    | 1      | 1      | Minute-periodical interrupt 1 (50% duty) |  |

| 1      | 0      | 0      | Alarm 2 interrupt                        |  |

<sup>\*1.</sup> Don't care (both of 0 and 1 are acceptable).

## B4: 32kE, B5: INT1AE, B6: INT1ME, B7: INT1FE

These bits are used to select the output mode for the  $\overline{\text{INT1}}$  pin. **Table 12** shows how to select the mode. To use an alarm 1 interrupt, set alarm interrupt mode, then access the INT1 register and the alarm expansion register 1.

Table 12 Output Modes for INT1 Pin

| 32kE | INT1AE | INT1ME | INT1FE | INT1 Pin Output Mode                     |  |  |  |

|------|--------|--------|--------|------------------------------------------|--|--|--|

| 0    | 0      | 0      | 0      | No interrupt                             |  |  |  |

| 0    | _*1    | 0      | 1      | Output of user-set frequency             |  |  |  |

| 0    | _*1    | 1      | 0      | Per-minute edge interrupt                |  |  |  |

| 0    | 0      | 1      | 1      | Minute-periodical interrupt 1 (50% duty) |  |  |  |

| 0    | 1      | 0      | 0      | Alarm 1 interrupt                        |  |  |  |

| 0    | 1      | 1      | 1      | Minute-periodical interrupt 2            |  |  |  |

| 1    | _*1    | _*1    | _*1    | 32.768 kHz output                        |  |  |  |

**<sup>\*1.</sup>** Don't care (both of 0 and 1 are acceptable).

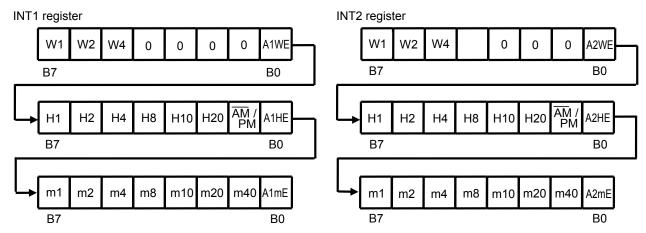

#### 4. INT1 register and INT2 register

The INT1 and INT2 registers are to set up the output of user-set frequency, or to set up alarm interrupt. Users are able to switch the output mode by using the status register 2. If selecting to use the output mode for alarm interrupt by status register 2; this register works as the alarm-time data register. If selecting the output of user-set frequency by status register 2; this register works as the data register to set the frequency for clock output. From each  $\overline{\text{INT1}}$  and  $\overline{\text{INT2}}$  pin, a clock pulse and alarm interrupt are output.

#### 4. 1 Alarm interrupt

Users can set the alarm time (the data of day of the week, hour, minute) by using the INT1 and INT2 registers which are 3-byte data registers. The configuration of register is as well as the data register of day of the week, hour, minute, in the real-time data register; is expressed by the BCD code. Do not set a nonexistent day. Users are necessary to set up the alarm-time data according to the 12 / 24 hour mode that they set by using the status register 1.

Figure 12 INT1 Register and INT2 Register (Alarm Time-Data)

The INT1 register has A1WE, A1HE, A1mE at B0 in each byte. It is possible to make data valid; the data of day of the week, hour, minute which are in the corresponding byte; by setting these bits to "1". This is as well in A2WE, A2HE, A2mE in the INT2 register. Regarding set-up of year, month, day, refer to "8. Alarm expansion register 1 and alarm expansion register 2".

Setting example: alarm time "7:00 pm" in the INT1 register

#### (1) 12-hour mode (status register 1 B6 = 0)

Set up 7:00 PM

Data written to INT1 register

| Day of week | _*1 | _*1 | _*1 | _*1 | _*1 | _*1 | _*1 | 0  |

|-------------|-----|-----|-----|-----|-----|-----|-----|----|

| Hour        | 1   | 1   | 1   | 0   | 0   | 0   | 1   | 1  |

| Minute      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1  |

|             | B7  |     |     |     |     |     |     | В0 |

<sup>\*1.</sup> Don't care (both of 0 and 1 are acceptable).

#### (2) 24-hour mode (status register 1 B6 = 1)

Set up 19:00 PM

Data written to INT1 register

|             |     | 9   | _   |     |     |          | _               |    |

|-------------|-----|-----|-----|-----|-----|----------|-----------------|----|

| Day of week | _*1 | _*1 | _*1 | _*1 | _*1 | _*1<br>_ | _*1             | 0  |

| Hour        | 1   | 0   | 0   | 1   | 1   | 0        | 1 <sup>*2</sup> | 1  |

| Minute      | 0   | 0   | 0   | 0   | 0   | 0        | 0               | 1  |

|             | B7  |     |     |     | •   |          |                 | В0 |

<sup>\*1.</sup> Don't care (both of 0 and 1 are acceptable).

<sup>\*2.</sup> Set up the AM / PM flag along with the time setting.

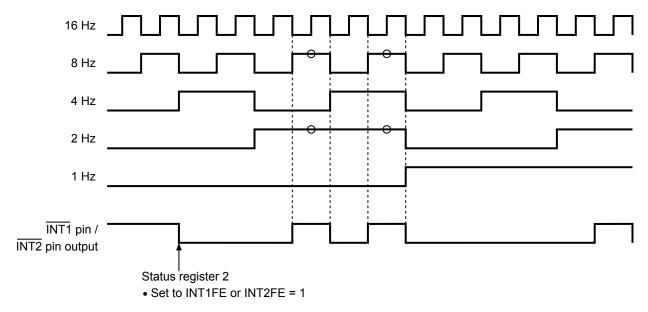

### 4. 2 Output of user-set frequency

The INT1 and INT2 registers are 1-byte data registers to set up the output frequency. Setting each bit B7 to B3 in the register to "1", the frequency which corresponds to the bit is output in the AND-form. SC2 to SC4 in the INT1 register, and SC5 to SC7 in the INT2 register are 3-bit SRAM type registers that can be freely set by users.

Figure 13 INT1 Register (Data Register for Output Frequency)

Figure 14 INT2 Register (Data Register for Output Frequency)

**Example:** B7 to B3 = 50h

Figure 15 Example of Output from INT1 Register (Data Register for Output Frequency)

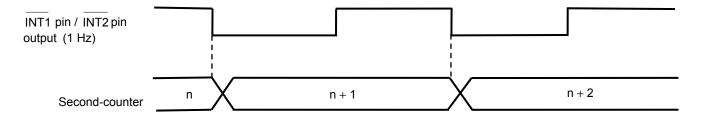

1 Hz clock output is synchronized with second-counter of the S-35399A03.

Figure 16 1 Hz Clock Output and Second-counter

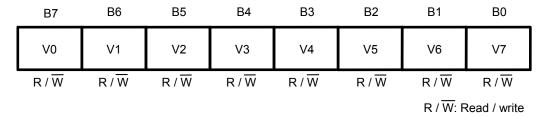

#### 5. Clock correction register

The clock correction register is a 1-byte register that is used to correct advance / delay of the clock. When not using this function, set this register to "00h". Regarding the register values, refer to "■ Function of Clock Correction".

Figure 17 Clock Correction Register

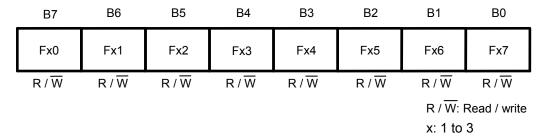

#### 6. Free registers 1 to 3

These free registers are 1-byte SRAM type registers that can be set freely by users.

Figure 18 Free Register

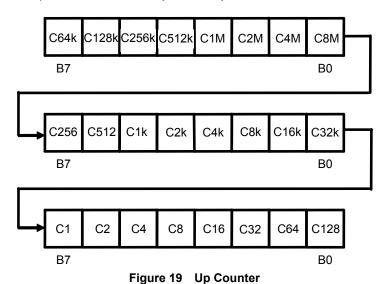

#### 7. Up counter

The up counter is a 24-bit read-only register. It starts binary counting from "000000 h" from power-on and continues counting as long as power is being applied. It continues counting when initialization, instead of returning to "000000 h". At power-on, registers are cleared by the power-on detection circuit so that the up counter is cleared to "000000 h". If the power-on detection circuit does not operate successfully, the counter may start from the indefinite status. For successful operation of the power-on detection circuit, refer to "

Power-on Detection Circuit and Register Status". Regarding the operation timing of the up counter, refer to "

Up-Count Operation".

Table 13 Example of Count Value and Reading Data in Register

| Count Value | Reading Data in Register |  |  |

|-------------|--------------------------|--|--|

| 000001 h    | 000080 h                 |  |  |

| 000002 h    | 000040 h                 |  |  |

| •           | •                        |  |  |

| •           | •                        |  |  |

| •           | •                        |  |  |

| EFFFFF h    | F7FFFF h                 |  |  |

| •           | •                        |  |  |

| •           | •                        |  |  |

| •           | •                        |  |  |

| FFFFFF h    | FFFFFF h                 |  |  |

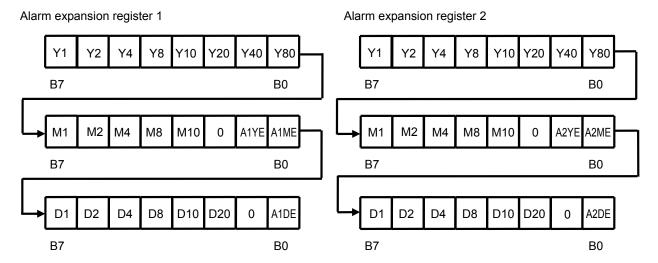

#### 8. Alarm expansion register 1 and alarm expansion register 2

The alarm expansion register 1 and 2 are 3-byte registers. They are expansion registers for the INT1 and INT2 registers which output alarm interrupt. Users are able to set the alarm time; the data of year, month, day. The configuration of register is expressed by BCD code as well as the data register of year, month, day in the real-time register.

Figure 20 Alarm Expansion Register 1 and Alarm Expansion Register 2

To make the year data of alarm expansion register 1 valid, set A1YE to "1". For the month data, set A1ME to "1", for the day data, set A1DE to "1". Set as well A2ME, A2YE, A2DE in the alarm expansion register 2. Regarding how to set the data of day of the week, hour, and minute, refer to "4. 1 Alarm interrupt" in "4. INT1 register and INT2 register".

Setting example: Setting alarm time "January 31, 2015" in the alarm expansion register 1

| Writing to alarm expansion register 1 |    |   |   |   |   |     |          |    |  |

|---------------------------------------|----|---|---|---|---|-----|----------|----|--|

| Year                                  | 1  | 0 | 1 | 0 | 1 | 0   | 0        | 0  |  |

| Month                                 | 1  | 0 | 0 | 0 | 0 | _*1 | 1        | 1  |  |

| Day                                   | 1  | 0 | 0 | 0 | 1 | 1   | _*1<br>_ | 1  |  |

|                                       | В7 |   |   |   |   |     |          | В0 |  |

**\*1.** Don't care (both of 0 and 1 are acceptable.)

## ■ Power-on Detection Circuit and Register Status

The power-on detection circuit operates by power-on the S-35399A03, as a result each register is cleared; each register is set as follows.

Real-time data register: 00 (Y), 01 (M), 01 (D), 0 (day of the week), 00 (H), 00 (M), 00 (S) Status register 1: "01h" Status register 2: "80h" INT1 register: "80h" INT2 register: "00h" Clock correction register: "00h" Free register 1: "00h" Free register 2: "00h" Free register 3: "00h" Up counter: "00 00 00h" "00h" Alarm expansion register 1: Alarm expansion register 2: "00h"

"1" is set in the POC flag (80 in the status register 1) to indicate that power has been applied. To correct the oscillation frequency, the status register 2 goes in the mode the output of user-set frequency, so that 1 Hz clock pulse is output from the INT1 pin. When "1" is set in the POC flag, be sure to initialize. The POC flag is set to "0" due to initialization so that the output of user-set frequency mode is cleared (Refer to "

Register Status After Initialization").

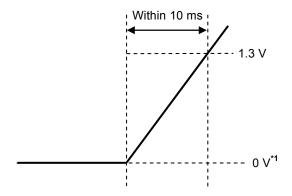

For the regular operation of power-on detection circuit, as seen in **Figure 21**, the period to power-up the S-35399A03 is that the voltage reaches 1.3 V within 10 ms after setting the IC's power supply voltage at 0 V. When the power-on detection circuit is not working normally is; the POC flag (B0 in the status register 1) is not in "1", or 1 Hz is not output from the  $\overline{\text{INT}}$ 1 pin. In this case, power-on the S-35399A03 once again because the internal data may be in the indefinite status.

Moreover, regarding the processing right after power-on, refer to "■ Flowchart of Initialization and Example of Real-time Data Set-up".

\*1. 0 V indicates that there are no potential differences between the VDD pin and VSS pin of the S-35399A03.

Figure 21 How to Raise the Power Supply Voltage

## ■ Register Status After Initialization

The status of each register after initialization is as follows.

Real-time data register: 00 (Y), 01 (M), 01 (D), 0 (day of the week), 00 (H), 00 (M), 00 (S)

Status register 1: "0 B6 B5 B4 0 0 0 0 b"

(In B6, B5, B4, the data of B6, B5, B4 in the status register 1 at initialization is set.

Refer to Figure 22.)

Status register 2: "00h"

INT1 register: "00h"

INT2 register: "00h"

Clock correction register: "00h"

Free register 1: "00h"

Free register 2: "00h"

Free register 3: "00h"

Up counter: Is not initialized and continues counting.

Alarm expansion register 1: "00h" Alarm expansion register 2: "00h"

Figure 22 Data of Status Register 1 at Initialization

## ■ Low Power Supply Voltage Detection Circuit

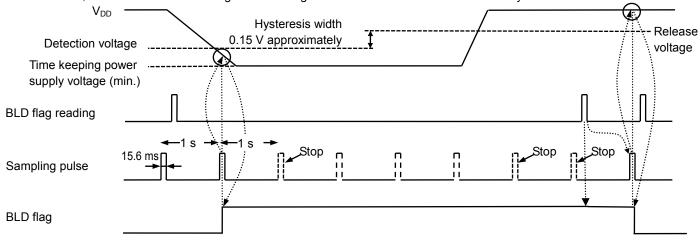

The S-35399A03 has a low power supply voltage detection circuit, so that users can monitor drops in the power supply voltage by reading the BLD flag (B1 in the status register 1). There is a hysteresis width of approx. 0.15 V typ. between detection voltage and release voltage (refer to "

Characteristics (Typical Data)"). The low power supply voltage detection circuit does the sampling operation only once in one sec for 15.6 ms.

If the power supply voltage decreases to the level of detection voltage ( $V_{DET}$ ) or less, "1" is set to the BLD flag so that sampling operation stops. Once "1" is detected in the BLD flag, no sampling operation is performed even if the power supply voltage increases to the level of release voltage or more, and "1" is held in the BLD flag.

Furthermore, the S-35399A03 does not initialize the internal circuit even if "1" is set to the BLD flag. If the BLD flag is "1" even after the power supply voltage is recovered, the internal circuit may be in the indefinite status. In this case, be sure to initialize the circuit. Without initializing, if the next BLD flag reading is done after sampling, the BLD flag gets reset to "0". In this case, be sure to initialize although the BLD flag is in "0" because the internal circuit may be in the indefinite status.

Figure 23 Timing of Low Power Supply Voltage Detection Circuit

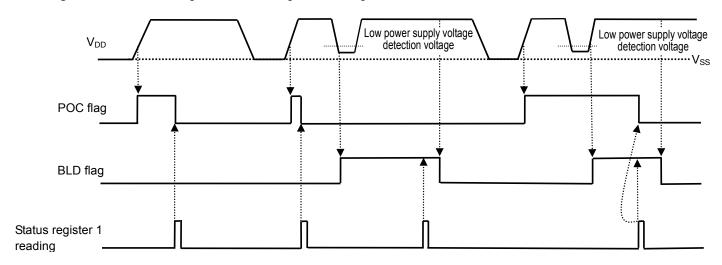

### ■ Circuits Power-on and Low Power Supply Voltage Detection

Figure 24 shows the changes of the POC flag and BLD flag due to V<sub>DD</sub> fluctuation.

Figure 24 POC Flag and BLD Flag

#### ■ Correction of Nonexistent Data and End-of-Month

When users write the real-time data, the S-35399A03 checks it. In case that the data is invalid, the S-35399A03 does the following procedures.

### 1. Processing of nonexistent data

Table 14 Processing of Nonexistent Data

| Register         |         | Normal Data | Nonexistent Data            | Result |

|------------------|---------|-------------|-----------------------------|--------|

| Year data        |         | 00 to 99    | 00 to 99 XA to XF, AX to FX |        |

| Month data       |         | 01 to 12    | 00, 13 to 19, XA to XF      | 01     |

| Day data         |         | 01 to 31    | 00, 32 to 39, XA to XF      | 01     |

| Day of week data |         | 0 to 6      | 7                           | 0      |

| Hour data*1      | 24-hour | 0 to 23     | 24 to 29, 3X, XA to XF      | 00     |

| Hour data        | 12-hour | 0 to 11     | 12 to 20, XA to XF          | 00     |

| Minute data      |         | 00 to 59    | 60 to 79, XA to XF          | 00     |

| Second data*2    |         | 00 to 59    | 60 to 79, XA to XF          | 00     |

<sup>\*1.</sup> In 12-hour mode, write the AM / PM flag (B1 in hour data in the real-time data register).

#### 2. Correction of end-of-month

A nonexistent day, such as February 30 and April 31, is set to the first day of the next month.

In 24-hour mode, the  $\overline{AM}$  / PM flag in the real-time data register is omitted. However in the flag of reading, users are able to read 0; 0 to 11, 1; 12 to 23.

<sup>\*2.</sup> Processing of nonexistent data, regarding second data, is done by a carry pulse which is generated in 1 second, after writing. At this point the carry pulse is sent to the minute-counter.

## ■ INT1, INT2 Pin Output Modes

These are selectable for the output mode for  $\overline{\text{INT1}}$  and  $\overline{\text{INT2}}$  pins;

Alarm interrupt, the output of user-set frequency, per-minute edge interrupt output, minute-periodical interrupt output 1. In the INT1 pin output mode, in addition to the above modes, minute-periodical interrupt output 2 and 32.768 kHz output are also selectable.

To swith the output mode, use the status register 2. Refer to "3. status register 2" in " Configuration of Registers". When switching the output mode, be careful of the output status of the pin. Especially, when using alarm interrupt / output of frequency, switch the output mode after setting "00h" in the INT1 / INT2 register. In 32.768 kHz output / per-minute edge interrupt output / minute-periodical interrupt output, it is unnecessary to set data in the INT1 / INT2 register for users. Refer to the followings regarding each operation of output modes.

#### 1. Alarm interrupt output

Alarm interrupt output is the function to output "L" from the  $\overline{\text{INT1}}$  /  $\overline{\text{INT2}}$  pin, at the alarm time which is set by user has come. If setting the pin output to "H", turn off the alarm function by setting "0" in INT1AE / INT2AE in the status register 2. To set the alarm time, set the data of day of the week, hour, minute in the INT1 / INT2 register, set the data of year, month, day in the alarm expansion register 1 or 2. Refer to "4. INT1 register and INT2 register" and "8. Alarm expansion register 1 and alarm expansion register 2" in "■ Configuration of Registers".

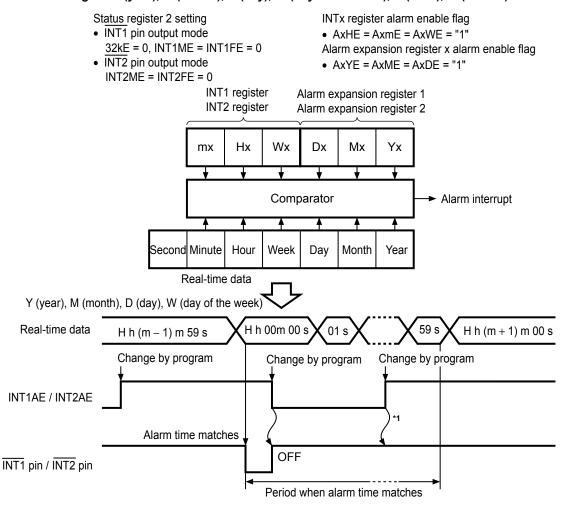

#### 1. 1 Alarm setting of "Y (year), M (month), D (day), W (day of the week), H (hour), m (minute)"

\*1. If users clear INT1AE / INT2AE once; "L" is not output from the INT1 / INT2 pin by setting INT1AE / INT2AE enable again, within a period when the alarm time matches real-time data.

Figure 25 Alarm Interrupt Output Timing

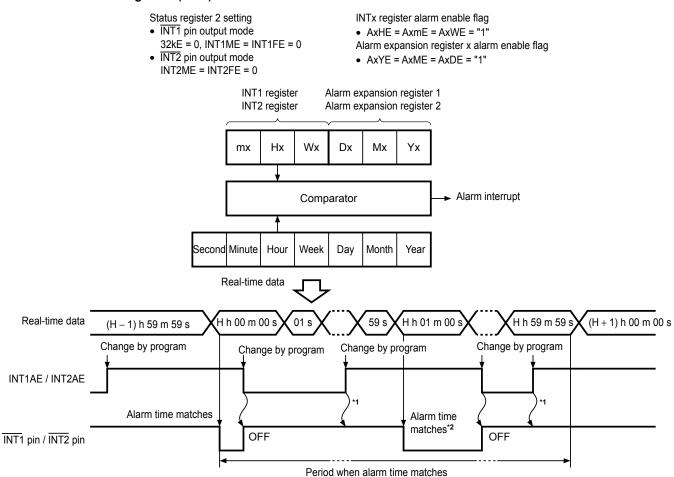

#### 1. 2 Alarm setting of "H (hour)"

- \*1. If users clear INT1AE / INT2AE once; "L" is not output from the INT1 / INT2 pin by setting INT1AE / INT2AE enable again, within a period when the alarm time matches real-time data.

- \*2. If turning the alarm output on by changing the program, within the period when the alarm time matches real-time data, "L" is output again from the  $\overline{\text{INT1}}$  /  $\overline{\text{INT2}}$  pin when the minute is counted up.

Figure 26 Alarm Interrupt Output Timing

#### 2. Output of user-set frequency

The output of user-set frequency is the function to output the frequency which is selected by using data, from the  $\overline{\text{INT1}}$  /  $\overline{\text{INT2}}$  pin, in the AND-form. Set up the data of frequency in the INT1 / INT2 register.

Refer to "4. INT1 register and INT2 register" in "■ Configuration of Registers".

Status register 2 setting

• INT1 pin output mode 32kE = 0, INT1AE = Don't care (0 or 1), INT1ME = 0

INT2 pin output mode INT2AE = Don't care (0 or 1), INT2ME = 0

Change by program

INT1FE / INT2FE

Free-run output starts

OFF

INT1 pin / INT2 pin

Figure 27 Output Timing of User-set Frequency