Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# S-5725 Series

### HIGH-SPEED BIPOLAR HALL EFFECT LATCH

### www.sii-ic.com

© SII Semiconductor Corporation, 2011-2015

Rev.2.5 01

The S-5725 Series, developed by CMOS technology, is a high-accuracy Hall IC that operates with a high-sensitivity, a high-speed detection and low current consumption.

The output voltage changes when the S-5725 Series detects the intensity level of magnetic flux density and a polarity change. Using the S-5725 Series with a magnet makes it possible to detect the rotation status in various devices.

High-density mounting is possible by using the small SOT-23-3 or the super-small SNT-4A packages.

Due to its high-accuracy magnetic characteristics, the S-5725 Series can make operation's dispersion in the system combined with magnet smaller.

Caution This product is intended to use in general electronic devices such as consumer electronics, office equipment, and communications devices. Before using the product in medical equipment or automobile equipment including car audio, keyless entry and engine control unit, contact to SII Semiconductor Corporation is indispensable.

### ■ Features

• Pole detection: Bipolar latch

• Detection logic for magnetism\*1:  $V_{OUT} = L$  at S pole detection

V<sub>OUT</sub> = "H" at S pole detection

• Output form\*1: Nch open-drain output, CMOS output

• Magnetic sensitivity\*1:  $B_{OP} = 0.8 \text{ mT typ.}$

$B_{OP} = 1.8 \text{ mT typ.}$  $B_{OP} = 3.0 \text{ mT typ.}$

$B_{OP} = 7.0 \text{ mT typ.}$

• Operating cycle (current consumption)\*1:  $t_{CYCLE} = 50 \,\mu s \,(I_{DD} = 1400.0 \,\mu A) \,typ.$

$t_{\text{CYCLE}}$  = 1.25 ms (I<sub>DD</sub> = 60.0  $\mu$ A) typ.  $t_{\text{CYCLE}}$  = 6.05 ms (I<sub>DD</sub> = 13.0  $\mu$ A) typ.

Power supply voltage range: V<sub>DD</sub> = 2.7 V to 5.5 V

Operation temperature range: Ta = -40°C to +85°C

Built-in power-down circuit: Extends battery life (only SNT-4A)

• Lead-free (Sn 100%), halogen-free

\*1. The option can be selected.

## ■ Applications

- Plaything, portable game

- Home appliance

- Housing equipment

- Industrial equipment

### ■ Packages

- SOT-23-3

- SNT-4A

# **■** Block Diagrams

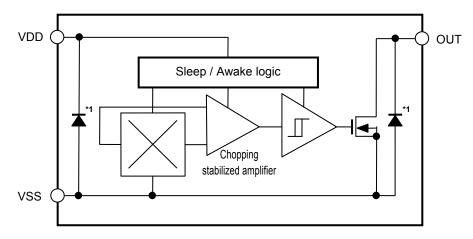

# 1. Nch open-drain output product

### 1. 1 Product without power-down function

\*1. Parasitic diode

Figure 1

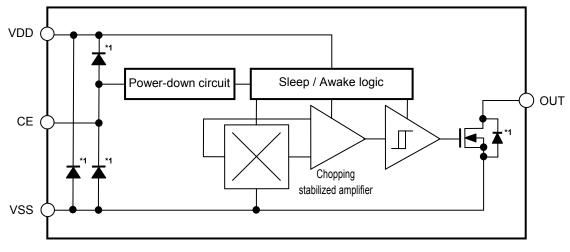

### 1. 2 Product with power-down function (SNT-4A)

\*1. Parasitic diode

Figure 2

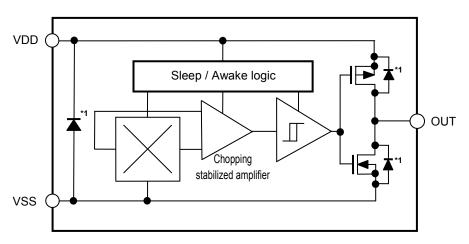

### 2. CMOS output product

### 2. 1 Product without power-down function

\*1. Parasitic diode

Figure 3

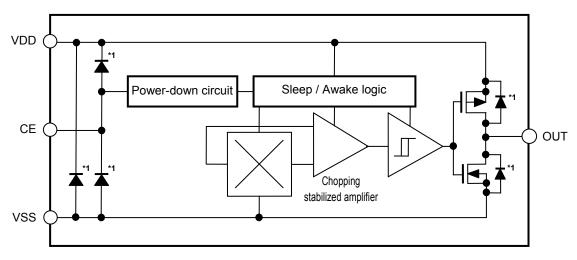

### 2. 2 Product with power-down function (SNT-4A)

\*1. Parasitic diode

Figure 4

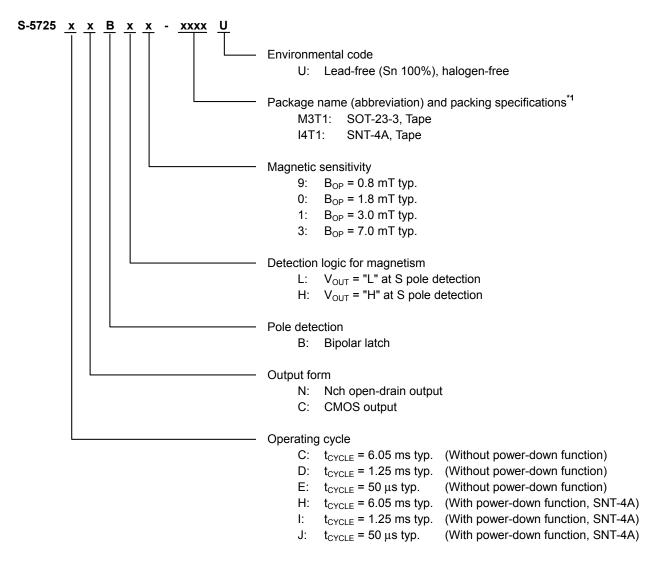

### **■ Product Name Structure**

### 1. Product name

<sup>\*1.</sup> Refer to the tape drawing.

### 2. Packages

Table 1 Package Drawing Codes

| Package Name | Dimension    | Tape         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| SOT-23-3     | MP003-C-P-SD | MP003-C-C-SD | MP003-Z-R-SD | _            |

| SNT-4A       | PF004-A-P-SD | PF004-A-C-SD | PF004-A-R-SD | PF004-A-L-SD |

### 3. Product name list

### 3.1 SOT-23-3

### 3. 1. 1 Nch open-drain output product

Table 2

| Product Name      | Operating Cycle (tcycle) | Power-down<br>Function | Output Form           | Pole<br>Detection | Detection Logic for Magnetism              | Magnetic<br>Sensitivity<br>(Bop) |

|-------------------|--------------------------|------------------------|-----------------------|-------------------|--------------------------------------------|----------------------------------|

| S-5725CNBL9-M3T1U | 6.05 ms typ.             | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 0.8 mT typ.                      |

| S-5725CNBL0-M3T1U | 6.05 ms typ.             | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 1.8 mT typ.                      |

| S-5725CNBL1-M3T1U | 6.05 ms typ.             | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 3.0 mT typ.                      |

| S-5725DNBL1-M3T1U | 1.25 ms typ.             | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 3.0 mT typ.                      |

| S-5725ENBL9-M3T1U | 50 μs typ.               | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 0.8 mT typ.                      |

| S-5725ENBL0-M3T1U | 50 μs typ.               | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 1.8 mT typ.                      |

| S-5725ENBL1-M3T1U | 50 μs typ.               | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 3.0 mT typ.                      |

| S-5725ENBH1-M3T1U | 50 μs typ.               | Unavailable            | Nch open-drain output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 3.0 mT typ.                      |

**Remark** Please contact our sales office for products other than the above.

### 3. 1. 2 CMOS output product

Table 3

| Product Name      | Operating Cycle (t <sub>CYCLE</sub> ) | Power-down<br>Function | Output Form | Pole<br>Detection | Detection Logic for Magnetism              | Magnetic<br>Sensitivity<br>(Bop) |

|-------------------|---------------------------------------|------------------------|-------------|-------------------|--------------------------------------------|----------------------------------|

| S-5725CCBL9-M3T1U | 6.05 ms typ.                          | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 0.8 mT typ.                      |

| S-5725CCBL0-M3T1U | 6.05 ms typ.                          | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 1.8 mT typ.                      |

| S-5725CCBL1-M3T1U | 6.05 ms typ.                          | Unavailable            | CMOS output | Bipolar<br>latch  | V <sub>OUT</sub> = "L" at S pole detection | 3.0 mT typ.                      |

| S-5725DCBL1-M3T1U | 1.25 ms typ.                          | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 3.0 mT typ.                      |

| S-5725ECBL9-M3T1U | 50 μs typ.                            | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 0.8 mT typ.                      |

| S-5725ECBL0-M3T1U | 50 μs typ.                            | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 1.8 mT typ.                      |

| S-5725ECBL1-M3T1U | 50 μs typ.                            | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 3.0 mT typ.                      |

| S-5725ECBH0-M3T1U | 50 μs typ.                            | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                      |

| S-5725ECBH1-M3T1U | 50 μs typ.                            | Unavailable            | CMOS output | Bipolar<br>latch  | V <sub>OUT</sub> = "H" at S pole detection | 3.0 mT typ.                      |

**Remark** Please contact our sales office for products other than the above.

### 3. 2 SNT-4A

### 3. 2. 1 Nch open-drain output product

### Table 4

| Product Name      | Operating Cycle (tcycle) | Power-down<br>Function | Output Form           | Pole<br>Detection | Detection Logic for Magnetism              | Magnetic<br>Sensitivity<br>(Bop) |

|-------------------|--------------------------|------------------------|-----------------------|-------------------|--------------------------------------------|----------------------------------|

| S-5725ENBH3-I4T1U | 50 μs typ.               | Unavailable            | Nch open-drain output | Bipolar<br>latch  | V <sub>OUT</sub> = "H" at S pole detection | 7.0 mT typ.                      |

| S-5725HNBH0-I4T1U | 6.05 ms typ.             | Available              | Nch open-drain output | Bipolar<br>latch  | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                      |

| S-5725INBH0-I4T1U | 1.25 ms typ.             | Available              | Nch open-drain output | Bipolar<br>latch  | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                      |

| S-5725JNBH0-I4T1U | 50 μs typ.               | Available              | Nch open-drain output | Bipolar<br>latch  | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                      |

Remark Please contact our sales office for products other than the above.

### 3. 2. 2 CMOS output product

Table 5

| Product Name      | Operating Cycle (tcycle) | Power-down<br>Function | Output Form | Pole<br>Detection | Detection Logic for Magnetism              | Magnetic<br>Sensitivity<br>(B <sub>OP</sub> ) |

|-------------------|--------------------------|------------------------|-------------|-------------------|--------------------------------------------|-----------------------------------------------|

| S-5725ECBL9-I4T1U | 50 μs typ.               | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 0.8 mT typ.                                   |

| S-5725ECBL0-I4T1U | 50 μs typ.               | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "L" at S pole detection | 1.8 mT typ.                                   |

| S-5725ECBH0-I4T1U | 50 μs typ.               | Unavailable            | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                                   |

| S-5725HCBH0-I4T1U | 6.05 ms typ.             | Available              | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                                   |

| S-5725HCBH1-I4T1U | 6.05 ms typ.             | Available              | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 3.0 mT typ.                                   |

| S-5725ICBH0-I4T1U | 1.25 ms typ.             | Available              | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                                   |

| S-5725ICBH1-I4T1U | 1.25 ms typ.             | Available              | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 3.0 mT typ.                                   |

| S-5725JCBH0-I4T1U | 50 μs typ.               | Available              | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 1.8 mT typ.                                   |

| S-5725JCBH1-I4T1U | 50 μs typ.               | Available              | CMOS output | Bipolar latch     | V <sub>OUT</sub> = "H" at S pole detection | 3.0 mT typ.                                   |

**Remark** Please contact our sales office for products other than the above.

# **■** Pin Configurations

# 1. SOT-23-3

Top view

| Pin No. | Symbol | Pin Description  |

|---------|--------|------------------|

| 1       | VSS    | GND pin          |

| 2       | VDD    | Power supply pin |

| 3       | OUT    | Output pin       |

Table 6

Figure 5

# 2. SNT-4A

Top view

Figure 6

### Table 7

| Pin No. | Symbol | Description                                         |

|---------|--------|-----------------------------------------------------|

| 1       | VDD    | Power supply pin                                    |

| 2       | VSS    | GND pin                                             |

| 3       | CE     | Enabling pin "H": Enables operation "L": Power-down |

| 4       | OUT    | Output pin                                          |

# ■ Absolute Maximum Ratings

Table 8

(Ta =  $+25^{\circ}$ C unless otherwise specified)

|                               | Item                          | Symbol           | Absolute Maximum Rating                               | Unit |

|-------------------------------|-------------------------------|------------------|-------------------------------------------------------|------|

| Power supply voltage          |                               | $V_{DD}$         | $V_{\text{SS}} - 0.3$ to $V_{\text{SS}} + 7.0$        | V    |

| Input voltage                 |                               | V <sub>CE</sub>  | $V_{\text{SS}} - 0.3 \text{ to } V_{\text{DD}} + 0.3$ | V    |

| Output current                |                               | lout             | ±2.0                                                  | mA   |

| Outrout valtage               | Nch open-drain output product | Vaur             | $V_{\text{SS}} - 0.3$ to $V_{\text{SS}} + 7.0$        | V    |

| Output voltage                | CMOS output product           | Vouт             | $V_{\text{SS}} - 0.3$ to $V_{\text{DD}} + 0.3$        | V    |

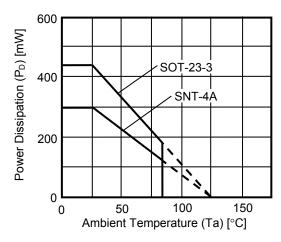

| Dower dissination             | SOT-23-3                      | Po               | 430* <sup>1</sup>                                     | mW   |

| Power dissipation             | SNT-4A                        | FD               | 300 <sup>*1</sup>                                     | mW   |

| Operation ambient temperature |                               | Topr             | -40 to +85                                            | °C   |

| Storage temperatur            | re                            | T <sub>stg</sub> | -40 to +125                                           | °C   |

<sup>\*1.</sup> When mounted on board

[Mounted board]

(1) Board size: 114.3 mm  $\times$  76.2 mm  $\times$  t1.6 mm (2) Name: JEDEC STANDARD51-7

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

Figure 7 Power Dissipation of Package (When Mounted on Board)

# **■** Electrical Characteristics

### 1. Product without power-down function

### 1.1 S-5725CxBxx

Table 9

(Ta = +25°C,  $V_{DD}$  = 5.0 V,  $V_{SS}$  = 0 V unless otherwise specified)

| Item                 | Symbol            | Condition                                              |                                                    |                       | Тур. | Max.  | Unit | Test<br>Circuit |

|----------------------|-------------------|--------------------------------------------------------|----------------------------------------------------|-----------------------|------|-------|------|-----------------|

| Power supply voltage | $V_{DD}$          |                                                        | _                                                  |                       | 5.0  | 5.5   | V    | _               |

| Current consumption  | I <sub>DD</sub>   | Average value                                          |                                                    | _                     | 13.0 | 20.0  | μΑ   | 1               |

|                      |                   | Nch open-drain output product                          | Output transistor Nch, I <sub>OUT</sub> = 2 mA     | _                     | _    | 0.4   | ٧    | 2               |

| Output voltage       | Vouт              | CMOS quitaut aradust                                   | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA  | _                     | _    | 0.4   | ٧    | 2               |

|                      |                   | CMOS output product                                    | Output transistor Pch,<br>I <sub>OUT</sub> = -2 mA | V <sub>DD</sub> – 0.4 | _    | _     | ٧    | 3               |

| Leakage current      | I <sub>LEAK</sub> | Nch open-drain output pro<br>Output transistor Nch, Vo |                                                    | -                     | -    | 1     | μΑ   | 4               |

| Awake mode time      | t <sub>AW</sub>   |                                                        | _                                                  | _                     | 0.05 | _     | ms   | _               |

| Sleep mode time      | tsL               | -                                                      |                                                    | _                     | 6.00 | -     | ms   | _               |

| Operating cycle      | tcycle            | taw + tsl                                              |                                                    | _                     | 6.05 | 12.00 | ms   | _               |

### 1. 2 S-5725DxBxx

Table 10

| Item                 | Symbol            | Con                                                     | Condition                                         |                       | Тур. | Max. | Unit | Test<br>Circuit |

|----------------------|-------------------|---------------------------------------------------------|---------------------------------------------------|-----------------------|------|------|------|-----------------|

| Power supply voltage | $V_{DD}$          |                                                         | _                                                 |                       | 5.0  | 5.5  | V    | _               |

| Current consumption  | I <sub>DD</sub>   | Average value                                           |                                                   | _                     | 60.0 | 90.0 | μΑ   | 1               |

| Output voltage Vo    |                   | Nch open-drain output product                           | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA | _                     | -    | 0.4  | ٧    | 2               |

|                      | V <sub>OUT</sub>  | CMOS output product                                     | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA | -                     | 1    | 0.4  | >    | 2               |

|                      |                   | CMOS output product Output transistor Pch, Iout = -2 mA |                                                   | V <sub>DD</sub> – 0.4 | -    | -    | ٧    | 3               |

| Leakage current      | I <sub>LEAK</sub> | Nch open-drain output pro<br>Output transistor Nch, Vo  |                                                   | _                     | ı    | 1    | μΑ   | 4               |

| Awake mode time      | t <sub>AW</sub>   |                                                         | _                                                 | _                     | 0.05 | _    | ms   | _               |

| Sleep mode time      | tsL               | -                                                       |                                                   | _                     | 1.20 | _    | ms   | _               |

| Operating cycle      | tcycle            | taw + tsl                                               |                                                   | _                     | 1.25 | 2.50 | ms   | _               |

### 1. 3 S-5725ExBxx

Table 11

| Item                 | Symbol          | Condition                                             |                                                   | Min.                  | Тур.   | Max.   | Unit | Test<br>Circuit |

|----------------------|-----------------|-------------------------------------------------------|---------------------------------------------------|-----------------------|--------|--------|------|-----------------|

| Power supply voltage | $V_{DD}$        | _                                                     | _                                                 |                       | 5.0    | 5.5    | V    | _               |

| Current consumption  | I <sub>DD</sub> | Average value                                         |                                                   | _                     | 1400.0 | 2000.0 | μΑ   | 1               |

| Output voltage Vout  |                 | Nch open-drain output product                         | Output transistor Nch, I <sub>OUT</sub> = 2 mA    | _                     | -      | 0.4    | >    | 2               |

|                      | Vоит            | CMOS output made dust                                 | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA | _                     | -      | 0.4    | >    | 2               |

|                      |                 | CMOS output product                                   | Output transistor Pch, I <sub>OUT</sub> = -2 mA   | V <sub>DD</sub> – 0.4 | -      | -      | >    | 3               |

| Leakage current      | ILEAK           | Nch open-drain output pr<br>Output transistor Nch, Vo |                                                   | _                     | _      | 1      | μΑ   | 4               |

| Awake mode time      | t <sub>AW</sub> | -                                                     | -                                                 | _                     | 50     | -      | μs   | _               |

| Sleep mode time      | t <sub>SL</sub> | -                                                     |                                                   | _                     | 0      | _      | μs   | _               |

| Operating cycle      | tcycle          | t <sub>AW</sub> + t <sub>SL</sub>                     |                                                   | _                     | 50     | 100    | μs   | _               |

# 2. Product with power-down function (SNT-4A)

### 2. 1 S-5725HxBxx

Table 12

|                                                              |                  |                                               | (14 120 0, VDD 0.0 V                               | , <b>v</b> 33         | o v arne |                       |          | /               |

|--------------------------------------------------------------|------------------|-----------------------------------------------|----------------------------------------------------|-----------------------|----------|-----------------------|----------|-----------------|

| Item                                                         | Symbol           | Со                                            | ndition                                            | Min.                  | Тур.     | Max.                  | Unit     | Test<br>Circuit |

| Power supply voltage                                         | $V_{DD}$         |                                               | _                                                  | 2.7                   | 5.0      | 5.5                   | V        | _               |

| Current consumption                                          | $I_{DD}$         | Average value                                 |                                                    | _                     | 13.0     | 20.0                  | μΑ       | 1               |

| Current consumption during power-down                        | I <sub>DD2</sub> | V <sub>CE</sub> = V <sub>SS</sub>             |                                                    | _                     | -        | 1                     | μΑ       | 6               |

| Output voltage                                               |                  | Nch open-drain output product                 | Output transistor Nch, I <sub>OUT</sub> = 2 mA     | _                     | -        | 0.4                   | <b>V</b> | 2               |

|                                                              | V <sub>оит</sub> | CMOS output product                           | Output transistor Nch, I <sub>OUT</sub> = 2 mA     | -                     | _        | 0.4                   | ٧        | 2               |

|                                                              |                  |                                               | Output transistor Pch,<br>I <sub>OUT</sub> = -2 mA | V <sub>DD</sub> - 0.4 | _        | _                     | ٧        | 3               |

| Leakage current                                              | ILEAK            | Nch open-drain outpu<br>Output transistor Nch | _                                                  | ı                     | 1        | μΑ                    | 4        |                 |

| Awake mode time                                              | t <sub>AW</sub>  |                                               | _                                                  | _                     | 0.05     | -                     | ms       | -               |

| Sleep mode time                                              | t <sub>SL</sub>  |                                               | _                                                  | _                     | 6.00     | _                     | ms       | _               |

| Operating cycle                                              | tcycle           | taw + tsL                                     |                                                    | -                     | 6.05     | 12.00                 | ms       | _               |

| Enabling pin input voltage "L"                               | V <sub>CEL</sub> |                                               | =                                                  | _                     | ı        | V <sub>DD</sub> × 0.3 | <b>V</b> | _               |

| Enabling pin input voltage "H"                               | V <sub>CEH</sub> |                                               | -                                                  | V <sub>DD</sub> × 0.7 | -        | -                     | ٧        | -               |

| Enabling pin input current "L"                               | ICEL             | $V_{DD} = 5.0 \text{ V}, V_{CE} = 0$          | V                                                  | -1                    | -        | 1                     | μΑ       | 7               |

| Enabling pin input current "H"                               | Ісен             | V <sub>DD</sub> = 5.0 V, V <sub>CE</sub> = 5. | 0 V                                                | -1                    | -        | 1                     | μΑ       | 8               |

| Power-down transition time                                   | toff             |                                               |                                                    | _                     | 1        | 100                   | μs       | _               |

| Enable transition time                                       | t <sub>ON</sub>  |                                               | -                                                  |                       | ı        | 100                   | μs       |                 |

| Output logic update time after inputting "H" to enabling pin | toE              |                                               | -                                                  | _                     | _        | 200                   | μs       | _               |

### 2. 2 S-5725lxBxx

Table 13

| Item                                                         | Symbol           | Co                                                                | ondition                                         | Min.                  | Тур. | Max.                | Unit     | Test<br>Circuit |

|--------------------------------------------------------------|------------------|-------------------------------------------------------------------|--------------------------------------------------|-----------------------|------|---------------------|----------|-----------------|

| Power supply voltage                                         | $V_{DD}$         |                                                                   | _                                                | 2.7                   | 5.0  | 5.5                 | V        | _               |

| Current consumption                                          | $I_{DD}$         | Average value                                                     |                                                  | _                     | 60.0 | 90.0                | μΑ       | 1               |

| Current consumption during power-down                        | I <sub>DD2</sub> | V <sub>CE</sub> = V <sub>SS</sub>                                 |                                                  | -                     | ı    | 1                   | μΑ       | 6               |

|                                                              |                  | Nch open-drain output product                                     | Output transistor Nch, I <sub>OUT</sub> = 2 mA   | -                     | ı    | 0.4                 | >        | 2               |

| Output voltage                                               | Vouт             | CMOS output                                                       | Output transistor Nch, I <sub>OUT</sub> = 2 mA   | _                     | 1    | 0.4                 | >        | 2               |

|                                                              |                  | product                                                           | Output transistor Pch, $I_{OUT} = -2 \text{ mA}$ | V <sub>DD</sub> - 0.4 | ı    | _                   | >        | 3               |

| Leakage current                                              | ILEAK            | Nch open-drain output product Output transistor Nch, Vout = 5.5 V |                                                  | -                     | 1    | 1                   | μΑ       | 4               |

| Awake mode time                                              | t <sub>AW</sub>  | -                                                                 |                                                  | _                     | 0.05 | -                   | ms       | _               |

| Sleep mode time                                              | tsL              |                                                                   | _                                                | _                     | 1.20 | 1                   | ms       | _               |

| Operating cycle                                              | tcycle           | taw + tsl                                                         |                                                  | _                     | 1.25 | 2.50                | ms       | _               |

| Enabling pin input voltage "L"                               | VCEL             |                                                                   | -                                                | _                     | -    | $V_{DD} \times 0.3$ | <b>V</b> | _               |

| Enabling pin input voltage "H"                               | VCEH             |                                                                   | _                                                | V <sub>DD</sub> × 0.7 | -    | -                   | ٧        | -               |

| Enabling pin input current "L"                               | ICEL             | V <sub>DD</sub> = 5.0 V, V <sub>CE</sub> = 0                      | ) V                                              | -1                    | _    | 1                   | μΑ       | 7               |

| Enabling pin input current "H"                               | ICEH             | V <sub>DD</sub> = 5.0 V, V <sub>CE</sub> = 5                      | 5.0 V                                            | -1                    | 1    | 1                   | μΑ       | 8               |

| Power-down transition time                                   | toff             | -                                                                 |                                                  | _                     | 1    | 100                 | μs       | _               |

| Enable transition time                                       | t <sub>ON</sub>  |                                                                   | _                                                | _                     | ı    | 100                 | μs       | _               |

| Output logic update time after inputting "H" to enabling pin | toE              |                                                                   | _                                                | _                     | ı    | 200                 | μs       | _               |

### 2. 3 S-5725JxBxx

Table 14

| Item                                                         | Symbol           | Co                                                                | ondition                                           | Min.                  | Тур.   | Max.                  | Unit | Test<br>Circuit |

|--------------------------------------------------------------|------------------|-------------------------------------------------------------------|----------------------------------------------------|-----------------------|--------|-----------------------|------|-----------------|

| Power supply voltage                                         | $V_{\text{DD}}$  |                                                                   | _                                                  | 2.7                   | 5.0    | 5.5                   | V    | _               |

| Current consumption                                          | $I_{DD}$         | Average value                                                     |                                                    | _                     | 1400.0 | 2000.0                | μΑ   | 1               |

| Current consumption during power-down                        | I <sub>DD2</sub> | V <sub>CE</sub> = V <sub>SS</sub>                                 |                                                    | ı                     | _      | 1                     | μΑ   | 6               |

|                                                              |                  | Nch open-drain output product                                     | Output transistor Nch, I <sub>OUT</sub> = 2 mA     | 1                     | _      | 0.4                   | V    | 2               |

| Output voltage                                               | Vоит             | CMOS output                                                       | Output transistor Nch,<br>I <sub>OUT</sub> = 2 mA  | I                     | _      | 0.4                   | V    | 2               |

|                                                              | product          |                                                                   | Output transistor Pch,<br>I <sub>OUT</sub> = -2 mA | V <sub>DD</sub> – 0.4 | _      | -                     | ٧    | 3               |

| Leakage current                                              | ILEAK            | Nch open-drain output product Output transistor Nch, Vout = 5.5 V |                                                    | 1                     | _      | 1                     | μΑ   | 4               |

| Awake mode time                                              | t <sub>AW</sub>  | _                                                                 |                                                    | -                     | 50     | _                     | μs   | _               |

| Sleep mode time                                              | tsL              |                                                                   |                                                    | ı                     | 0      | _                     | μs   | _               |

| Operating cycle                                              | tcycle           | taw + tsl                                                         |                                                    | _                     | 50     | 100                   | μs   | _               |

| Enabling pin input voltage "L"                               | VCEL             |                                                                   | _                                                  | _                     | -      | V <sub>DD</sub> × 0.3 | V    | -               |

| Enabling pin input voltage "H"                               | Vсен             |                                                                   | _                                                  | V <sub>DD</sub> × 0.7 | -      | -                     | V    | -               |

| Enabling pin input current "L"                               | ICEL             | V <sub>DD</sub> = 5.0 V, V <sub>CE</sub> =                        | 0 V                                                | -1                    | -      | 1                     | μΑ   | 7               |

| Enabling pin input current "H"                               | Ісен             | V <sub>DD</sub> = 5.0 V, V <sub>CE</sub> =                        | 5.0 V                                              | -1                    | _      | 1                     | μΑ   | 8               |

| Power-down transition time                                   | toff             | _                                                                 |                                                    | _                     | _      | 100                   | μs   | _               |

| Enable transition time                                       | ton              |                                                                   | _                                                  | _                     | _      | 100                   | μs   | _               |

| Output logic update time after inputting "H" to enabling pin | t <sub>OE</sub>  |                                                                   | _                                                  | I                     | _      | 200                   | μs   | _               |

### ■ Magnetic Characteristics

### 1. Product with $B_{OP} = 0.8 \text{ mT typ.}$

Table 15

(Ta = +25°C, V<sub>DD</sub> = 5.0 V, V<sub>SS</sub> = 0 V unless otherwise specified)

| Item               |        | Symbol            | Condition                                            | Min. | Тур. | Max. | Unit | Test Circuit |

|--------------------|--------|-------------------|------------------------------------------------------|------|------|------|------|--------------|

| Operation point*1  | S pole | Вор               | _                                                    | 0.1  | 0.8  | 1.5  | mT   | 5            |

| Release point*2    | N pole | B <sub>RP</sub>   | _                                                    | -1.5 | -0.8 | -0.1 | mT   | 5            |

| Hysteresis width*3 |        | B <sub>H</sub> ys | B <sub>HYS</sub> = B <sub>OP</sub> - B <sub>RP</sub> | -    | 1.6  | 1    | mT   | 5            |

### 2. Product with $B_{OP} = 1.8 \text{ mT typ.}$

### Table 16

(Ta = +25°C, V<sub>DD</sub> = 5.0 V, V<sub>SS</sub> = 0 V unless otherwise specified)

| Item               |        | Symbol           | Condition                                             | Min. | Тур. | Max. | Unit | Test Circuit |

|--------------------|--------|------------------|-------------------------------------------------------|------|------|------|------|--------------|

| Operation point*1  | S pole | Вор              | _                                                     | 0.9  | 1.8  | 2.7  | mT   | 5            |

| Release point*2    | N pole | B <sub>RP</sub>  | _                                                     | -2.7 | -1.8 | -0.9 | mT   | 5            |

| Hysteresis width*3 |        | B <sub>HYS</sub> | B <sub>H</sub> ys = B <sub>OP</sub> - B <sub>RP</sub> | _    | 3.6  | -    | mT   | 5            |

### 3. Product with $B_{OP} = 3.0 \text{ mT typ.}$

### Table 17

(Ta =  $+25^{\circ}$ C, V<sub>DD</sub> = 5.0 V, V<sub>SS</sub> = 0 V unless otherwise specified)

|                    |        |                  | (                           | • • • • • • | <b>5.5 1</b> , <b>1</b> 00 | 0 1 0111100 | 0 04.10.11 | ioo opoomou, |

|--------------------|--------|------------------|-----------------------------|-------------|----------------------------|-------------|------------|--------------|

| Item               |        | Symbol           | Condition                   | Min.        | Тур.                       | Max.        | Unit       | Test Circuit |

| Operation point*1  | S pole | Вор              | _                           | 1.4         | 3.0                        | 4.0         | mT         | 5            |

| Release point*2    | N pole | B <sub>RP</sub>  | _                           | -4.0        | -3.0                       | -1.4        | mT         | 5            |

| Hysteresis width*3 |        | B <sub>HYS</sub> | $B_{HYS} = B_{OP} - B_{RP}$ | _           | 6.0                        | ı           | mT         | 5            |

### 4. Product with $B_{OP} = 7.0 \text{ mT typ.}$

### Table 18

(Ta =  $\pm 25^{\circ}$ C, V<sub>DD</sub> = 5.0 V, V<sub>SS</sub> = 0 V unless otherwise specified)

| Item               |        | Symbol           | Condition                                             | Min. | Тур. | Max. | Unit | Test Circuit |

|--------------------|--------|------------------|-------------------------------------------------------|------|------|------|------|--------------|

| Operation point*1  | S pole | Вор              | _                                                     | 5.0  | 7.0  | 8.5  | mT   | 5            |

| Release point*2    | N pole | B <sub>RP</sub>  | _                                                     | -8.5 | -7.0 | -5.0 | mT   | 5            |

| Hysteresis width*3 |        | B <sub>HYS</sub> | B <sub>H</sub> YS = B <sub>OP</sub> - B <sub>RP</sub> | -    | 14.0 | -    | mT   | 5            |

### \*1. Bop: Operation point

B<sub>OP</sub> is the value of magnetic flux density when the output voltage (V<sub>OUT</sub>) changes after the magnetic flux density applied to the S-5725 Series by the magnet (S pole) is increased (by moving the magnet closer).

$V_{\text{OUT}} \text{ retains the status until a magnetic flux density of the N pole higher than } B_{\text{RP}} \text{ is applied.}$

### \*2. BRP: Release point

B<sub>RP</sub> is the value of magnetic flux density when the output voltage (V<sub>OUT</sub>) changes after the magnetic flux density applied to the S-5725 Series by the magnet (N pole) is increased (by moving the magnet closer).

Vout retains the status until a magnetic flux density of the S pole higher than BOP is applied.

### \*3. B<sub>HYS</sub>: Hysteresis width

BHYS is the difference between BOP and BRP.

**Remark** The unit of magnetic density mT can be converted by using the formula 1 mT = 10 Gauss.

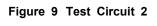

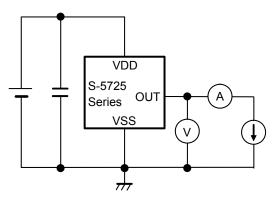

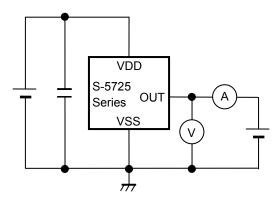

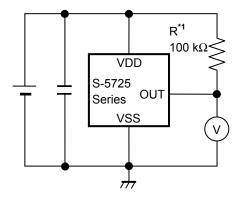

### **■** Test Circuits

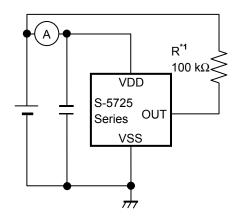

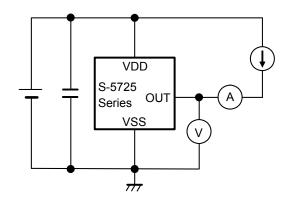

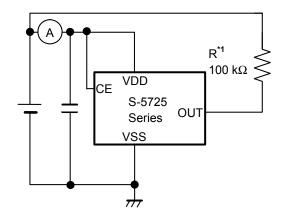

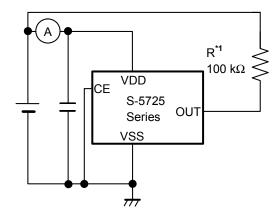

### 1. Product without power-down function

**\*1.** Resistor (R) is unnecessary for the CMOS output product.

Figure 8 Test Circuit 1

Figure 10 Test Circuit 3

Figure 11 Test Circuit 4

**\*1.** Resistor (R) is unnecessary for the CMOS output product.

Figure 12 Test Circuit 5

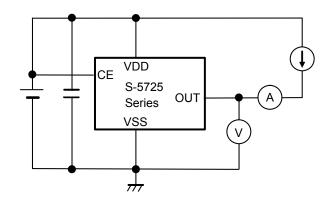

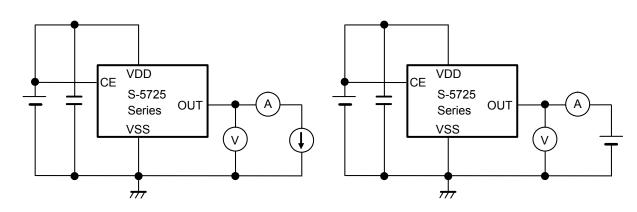

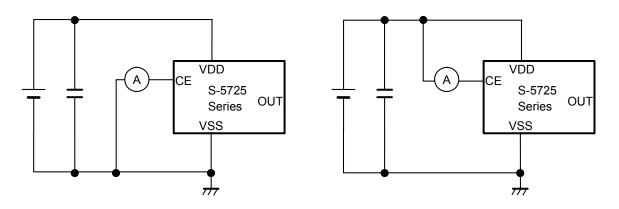

### 2. Product with power-down function (SNT-4A)

**\*1.** Resistor (R) is unnecessary for the CMOS output product.

Figure 13 Test Circuit 1

Figure 14 Test Circuit 2

Figure 15 Test Circuit 3

Figure 16 Test Circuit 4

**\*1.** Resistor (R) is unnecessary for the CMOS output product.

Figure 17 Test Circuit 5

**\*1.** Resistor (R) is unnecessary for the CMOS output product.

Figure 18 Test Circuit 6

Figure 19 Test Circuit 7

Figure 20 Test Circuit 8

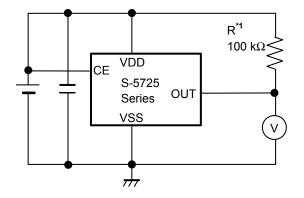

### **■** Standard Circuits

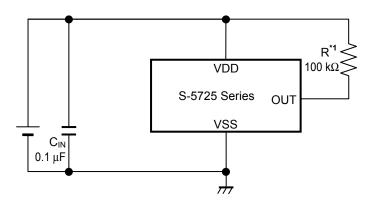

### 1. Product without power-down function

\*1. Resistor (R) is unnecessary for the CMOS output product.

Figure 21

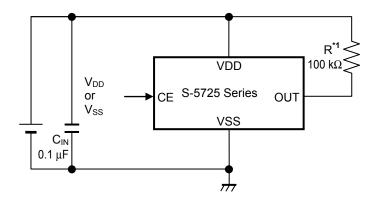

### 2. Product with power-down function (SNT-4A)

\*1. Resistor (R) is unnecessary for the CMOS output product.

Figure 22

Caution The above connection diagram and constant will not guarantee successful operation. Perform thorough evaluation using the actual application to set the constant.

### ■ Operation

### 1. Direction of applied magnetic flux

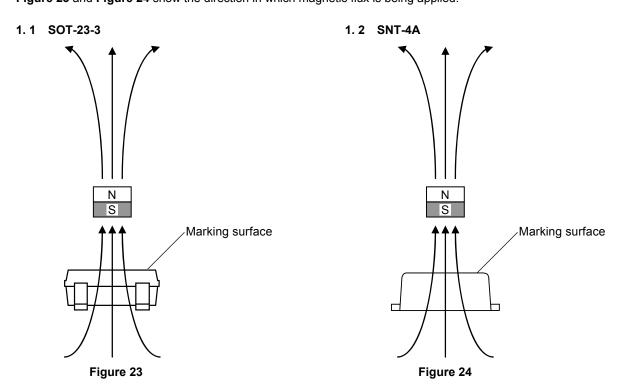

The S-5725 Series detects the magnetic flux density which is vertical to the marking surface. **Figure 23** and **Figure 24** show the direction in which magnetic flux is being applied.

### 2. Position of Hall sensor

Figure 25

Figure 25 and Figure 26 show the position of Hall sensor.

The center of this Hall sensor is located in the area indicated by a circle, which is in the center of a package as described below.

2. 2 SNT-4A

The following also shows the distance (typ. value) between the marking surface and the chip surface of a package.

# The center of Hall sensor; in this φ 0.3 mm 2. 1 SOT-23-3 Top view The center of Hall sensor; in this φ 0.3 mm 2 3 0.7 mm (typ.)

The center of Hall sensor; in this  $\phi$  0.3 mm

4

2

0.16 mm (typ.)

Figure 26

### 3. Basic operation

The S-5725 Series changes the output voltage (V<sub>OUT</sub>) according to the level of the magnetic flux density and a polarity change (N pole or S pole) applied by a magnet.

Definition of the magnetic field is performed every operating cycle indicated in "

Electrical Characteristics".

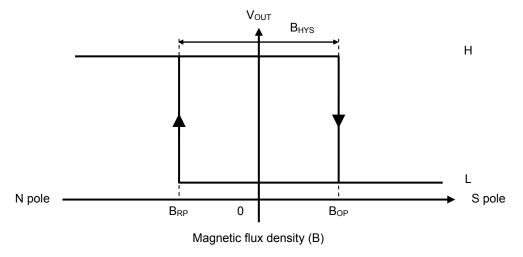

### 3. 1 Product with Vout = "L" at S pole detection

When the magnetic flux density of the S pole perpendicular to the marking surface exceeds the operation point (BoP) after the S pole of a magnet is moved closer to the marking surface of the S-5725 Series,  $V_{OUT}$  changes from "H" to "L". When the N pole of a magnet is moved closer to the marking surface of the S-5725 Series and the magnetic flux density of the N pole is higher than the release point (BRP),  $V_{OUT}$  changes from "L" to "H". In case of BRP < B < BOP,  $V_{OUT}$  retains the status.

Figure 27 shows the relationship between the magnetic flux density and Vout.

Figure 27

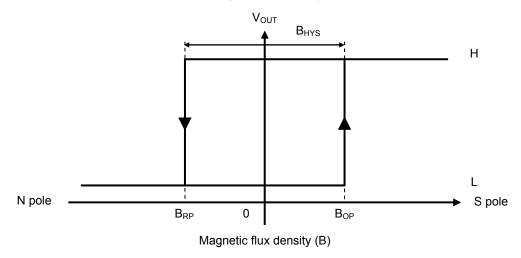

### 3. 2 Product with Vout = "H" at S pole detection

When the magnetic flux density of the S pole perpendicular to the marking surface exceeds  $B_{OP}$  after the S pole of a magnet is moved closer to the marking surface of the S-5725 Series,  $V_{OUT}$  changes from "L" to "H". When the N pole of a magnet is moved closer to the marking surface of the S-5725 Series and the magnetic flux density of the N pole is higher than  $B_{RP}$ ,  $V_{OUT}$  changes from "H" to "L". In case of  $B_{RP} < B < B_{OP}$ ,  $V_{OUT}$  retains the status.

Figure 28 shows the relationship between the magnetic flux density and V<sub>OUT</sub>.

Figure 28

### ■ Precautions

- If the impedance of the power supply is high, the IC may malfunction due to a supply voltage drop caused by feed-through current. Take care with the pattern wiring to ensure that the impedance of the power supply is low.

- Note that the IC may malfunction if the power supply voltage rapidly changes.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- Large stress on this IC may affect on the magnetic characteristics. Avoid large stress which is caused by bend and distortion during mounting the IC on a board or handle after mounting.

- SII Semiconductor Corporation claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

# ■ Marking Specifications

### 1. SOT-23-3

(1) to (3): Product code (Refer to **Product name vs. Product code**.)

(4): Lot number

### Product name vs. Product code

1.1 Nch open-drain output product

| Product Name      | Pro | oduct Co | de  |

|-------------------|-----|----------|-----|

| Product Name      | (1) | (2)      | (3) |

| S-5725CNBL9-M3T1U | Х   | 9        | R   |

| S-5725CNBL0-M3T1U | Х   | 9        | S   |

| S-5725CNBL1-M3T1U | Х   | 9        | J   |

| S-5725DNBL1-M3T1U | Χ   | 9        | K   |

| S-5725ENBL9-M3T1U | Χ   | 9        | ٧   |

| S-5725ENBL0-M3T1U | Х   | 9        | Α   |

| S-5725ENBL1-M3T1U | Х   | 9        | В   |

| S-5725ENBH1-M3T1U | Х   | 9        | L   |

1. 2 CMOS output product

| Product Name      | Pro | oduct Co | de  |

|-------------------|-----|----------|-----|

| Product Name      | (1) | (2)      | (3) |

| S-5725CCBL9-M3T1U | Х   | 9        | Р   |

| S-5725CCBL0-M3T1U | Χ   | 9        | Q   |

| S-5725CCBL1-M3T1U | Х   | 9        | Т   |

| S-5725DCBL1-M3T1U | Χ   | 9        | J   |

| S-5725ECBL9-M3T1U | Χ   | 9        | W   |

| S-5725ECBL0-M3T1U | Х   | 9        | Χ   |

| S-5725ECBL1-M3T1U | Χ   | 9        | С   |

| S-5725ECBH0-M3T1U | Χ   | 9        | Z   |

| S-5725ECBH1-M3T1U | Χ   | 9        | Υ   |

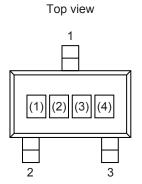

# 2. SNT-4A

Top view

1 (0) (2) (3) 4

2 (1) (2) (3) 3

(1) to (3): Product code (Refer to **Product name vs. Product code**.)

### Product name vs. Product code

2. 1 Nch open-drain output product

| Product Name      | Product Code |     |     |  |  |

|-------------------|--------------|-----|-----|--|--|

| Product Name      | (1)          | (2) | (3) |  |  |

| S-5725ENBH3-I4T1U | Х            | 8   | Α   |  |  |

| S-5725HNBH0-I4T1U | Х            | 9   | D   |  |  |

| S-5725INBH0-I4T1U | Χ            | 9   | F   |  |  |

| S-5725JNBH0-I4T1U | Х            | 9   | Н   |  |  |

2. 2 CMOS output product

| il a cilioo catpat product |     |          |     |

|----------------------------|-----|----------|-----|

| Product Name               | Pro | oduct Co | de  |

| Product Name               | (1) | (2)      | (3) |

| S-5725ECBL9-I4T1U          | Х   | 9        | W   |

| S-5725ECBL0-I4T1U          | Χ   | 9        | Χ   |

| S-5725ECBH0-I4T1U          | Χ   | 9        | Z   |

| S-5725HCBH0-I4T1U          | Χ   | 9        | Е   |

| S-5725HCBH1-I4T1U          | Х   | 9        | М   |

| S-5725ICBH0-I4T1U          | Х   | 9        | G   |

| S-5725ICBH1-I4T1U          | Χ   | 9        | Ν   |

| S-5725JCBH0-I4T1U          | Х   | 9        | -   |

| S-5725JCBH1-I4T1U          | Х   | 9        | 0   |

23

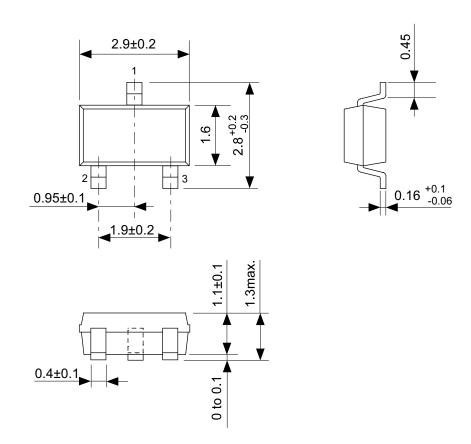

# No. MP003-C-P-SD-1.1

| TITLE  | SOT233-C-PKG Dimensions       |  |  |

|--------|-------------------------------|--|--|

| No.    | MP003-C-P-SD-1.1              |  |  |

| ANGLE  | <b>\$</b>                     |  |  |

| UNIT   | mm                            |  |  |

|        |                               |  |  |

|        |                               |  |  |

|        |                               |  |  |

| SII Se | SII Semiconductor Corporation |  |  |

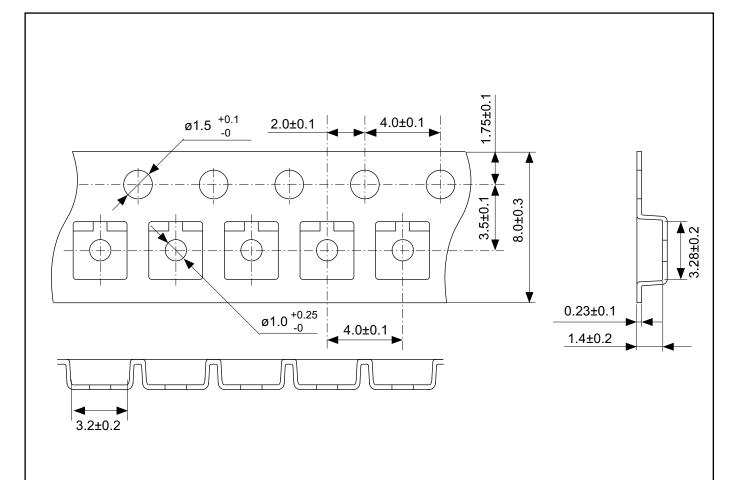

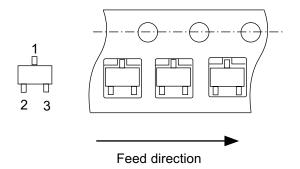

# No. MP003-C-C-SD-2.0

| TITLE  | SOT233-C-Carrier Tape         |  |  |  |

|--------|-------------------------------|--|--|--|

| No.    | MP003-C-C-SD-2.0              |  |  |  |

| ANGLE  |                               |  |  |  |

| UNIT   | mm                            |  |  |  |

|        |                               |  |  |  |

|        |                               |  |  |  |

|        |                               |  |  |  |

| SII Se | SII Semiconductor Corporation |  |  |  |