# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## S-8211E Series

## **BATTERY PROTECTION IC** FOR 1-CELL PACK

Accuracy ±25 mV (+25°C) Accuracy  $\pm 30 \text{ mV} (-5^{\circ}\text{C to} + 55^{\circ}\text{C})$

Accuracy ±50 mV Accuracy ±50 mV Accuracy ±100 mV

Accuracy ±20%

© SII Semiconductor Corporation, 2009-2015

The S-8211E Series has high-accuracy voltage detections circuit and delay circuits. The S-8211E Series is suitable for monitoring overcharge and overdischarge of 1-cell lithium ion / lithium polymer rechargeable battery pack.

### Features

www.sii-ic.com

(1) High-accuracy voltage detection circuit Overcharge detection voltage

|    | <ul> <li>Overcharge release voltage</li> </ul>      | 3.5 V to 4.4 V*1            |  |

|----|-----------------------------------------------------|-----------------------------|--|

|    | <ul> <li>Overdischarge detection voltage</li> </ul> | 2.0 V to 3.0 V (10 mV step) |  |

|    | <ul> <li>Overdischarge release voltage</li> </ul>   | 2.0 V to 3.4 V*2            |  |

| 2) | Detection delay times are generated by an int       | ernal circuit               |  |

|    |                                                     |                             |  |

- (2 (external capacitors are unnecessary) -40°C to +85°C

- (3) Wide operating temperature range

- (4) Low current consumption

- · During operation

- During overdischarge

- (5) Output logic of CO pin is selectable.

- (6) Lead-free, Sn 100%, halogen-free\*3

- \*1. Overcharge release voltage = Overcharge detection voltage Overcharge hysteresis voltage (Overcharge hysteresis voltage can be selected as 0 V or from a range of 0.1 V to 0.4 V in 50 mV step.)

- \*2. Overdischarge release voltage = Overdischarge detection voltage + Overdischarge hysteresis voltage (Overdischarge hysteresis voltage can be selected as 0 V or from a range of 0.1 V to 0.7 V in 100 mV step.)

- \*3. Refer to "

Product Name Structure" for details.

## Applications

- · Lithium-ion rechargeable battery pack

- Lithium-polymer rechargeable battery pack

### Packages

- SOT-23-5

- SNT-6A

3.6 V to 4.5 V (5 mV step)

3.0 μA typ., 5.5 μA max. (+25°C)

2.0 μA typ., 3.5 μA max. (+25°C)

Active "H", Active "L"

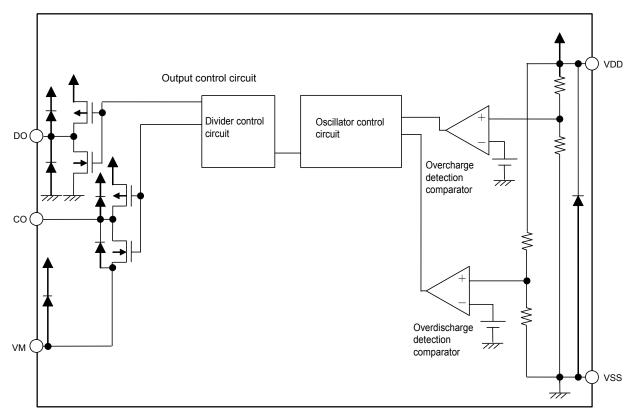

## Block Diagram

Remark All diodes shown in figure are parasitic diodes.

Figure 1

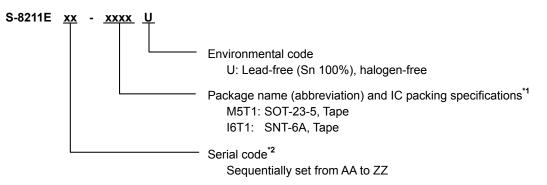

### Product Name Structure

#### 1. Product Name

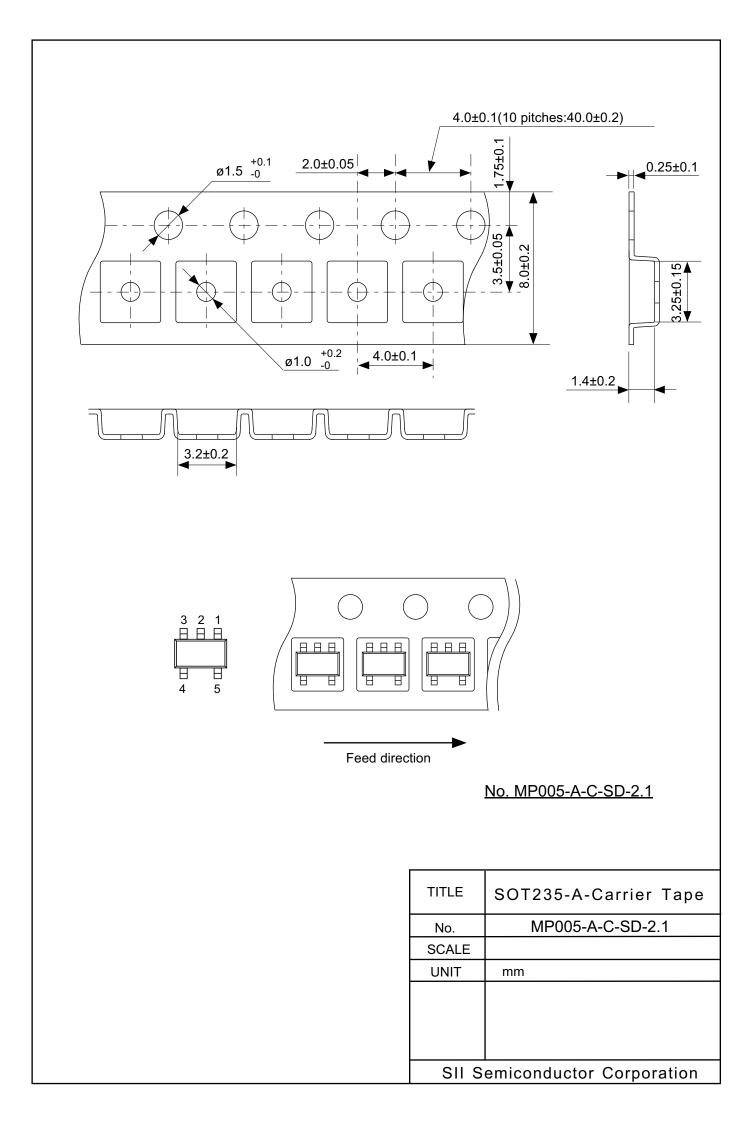

- \*1. Refer to the tape drawing.

- \*2. Refer to "3. Product Name List".

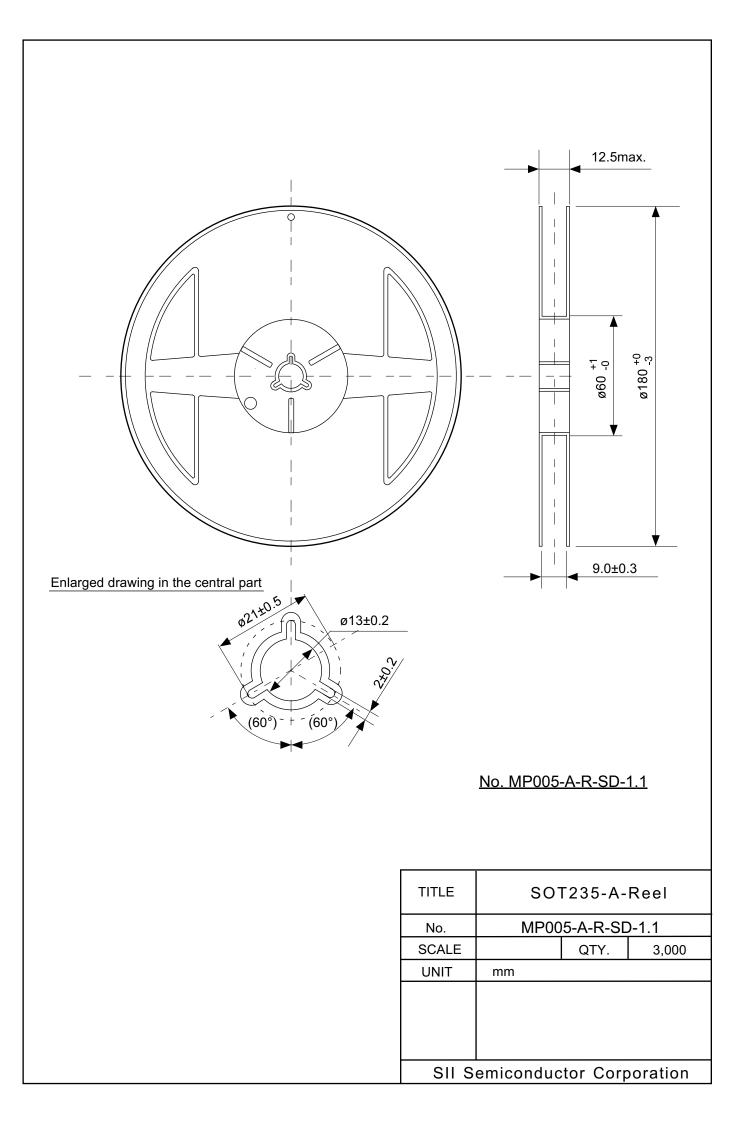

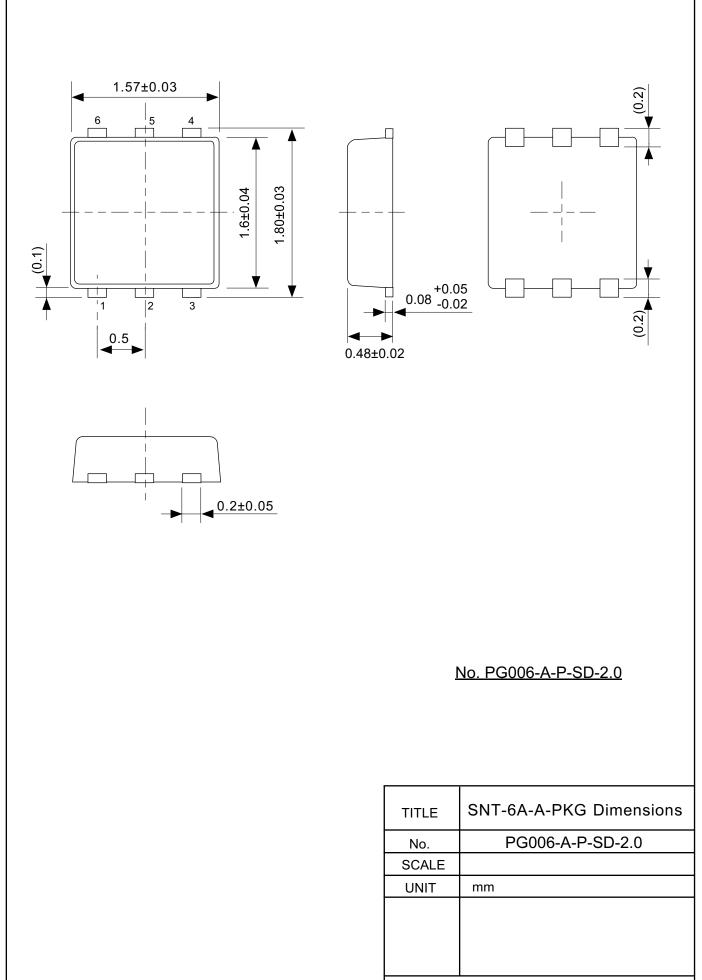

#### 2. Packages

| Deekege Neme |              | Drawin       | g Code       |              |

|--------------|--------------|--------------|--------------|--------------|

| Package Name | Package      | Таре         | Reel         | Land         |

| SOT-23-5     | MP005-A-P-SD | MP005-A-C-SD | MP005-A-R-SD | -            |

| SNT-6A       | PG006-A-P-SD | PG006-A-C-SD | PG006-A-R-SD | PG006-A-L-SD |

#### 3. Product Name List

#### 3.1 SOT-23-5

|                 | Table 1                                     |                                           |                                                             |                                                           |                             |                        |  |  |  |  |  |  |

|-----------------|---------------------------------------------|-------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------|------------------------|--|--|--|--|--|--|

| Product Name    | Overcharge<br>Detection<br>Voltage<br>[Vcu] | Overcharge<br>Release<br>Voltage<br>[VcL] | Overdischarge<br>Detection<br>Voltage<br>[V <sub>DL</sub> ] | Overdischarge<br>Release<br>Voltage<br>[V <sub>DU</sub> ] | Delay Time<br>Combination*1 | CO Pin<br>Output Form  |  |  |  |  |  |  |

| S-8211EAC-M5T1U | 3.600 V                                     | 3.600 V                                   | 2.00 V                                                      | 2.00 V                                                    | (1)                         | CMOS output active "L" |  |  |  |  |  |  |

| S-8211EAF-M5T1U | 3.650 V                                     | 3.550 V                                   | 2.00 V                                                      | 2.30 V                                                    | (2)                         | CMOS output active "L" |  |  |  |  |  |  |

| S-8211EAG-M5T1U | 3.800 V                                     | 3.600 V                                   | 2.00 V                                                      | 2.30 V                                                    | (2)                         | CMOS output active "L" |  |  |  |  |  |  |

| S-8211EAJ-M5T1U | 4.180 V                                     | 4.180 V                                   | 2.50 V                                                      | 3.00 V                                                    | (1)                         | CMOS output active "H" |  |  |  |  |  |  |

| S-8211EAK-M5T1U | 3.600 V                                     | 3.600 V                                   | 2.00 V                                                      | 2.30 V                                                    | (1)                         | CMOS output active "H" |  |  |  |  |  |  |

\*1. Refer to the **Table 3** about the details of the delay time combinations (1), (2).

**Remark** Please contact our sales office for the products with detection voltage value other than those specified above.

#### 3.2 SNT-6A

| Table 2         |                                                          |                                                        |                                                             |                                                           |                             |                        |  |  |  |  |  |

|-----------------|----------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------|------------------------|--|--|--|--|--|

| Product Name    | Overcharge<br>Detection<br>Voltage<br>[V <sub>Cu</sub> ] | Overcharge<br>Release<br>Voltage<br>[V <sub>CL</sub> ] | Overdischarge<br>Detection<br>Voltage<br>[V <sub>DL</sub> ] | Overdischarge<br>Release<br>Voltage<br>[V <sub>DU</sub> ] | Delay Time<br>Combination*1 | CO Pin<br>Output Form  |  |  |  |  |  |

| S-8211EAA-I6T1U | 4.220 V                                                  | 4.220 V                                                | 2.00 V                                                      | 2.00 V                                                    | (2)                         | CMOS output active "L" |  |  |  |  |  |

| S-8211EAB-I6T1U | 4.270 V                                                  | 4.270 V                                                | 2.00 V                                                      | 2.00 V                                                    | (2)                         | CMOS output active "L" |  |  |  |  |  |

| S-8211EAD-I6T1U | 4.220 V                                                  | 4.220 V                                                | 2.50 V                                                      | 2.50 V                                                    | (2)                         | CMOS output active "L" |  |  |  |  |  |

| S-8211EAE-I6T1U | 4.220 V                                                  | 4.220 V                                                | 2.30 V                                                      | 2.30 V                                                    | (2)                         | CMOS output active "L" |  |  |  |  |  |

| S-8211EAH-I6T1U | 4.000 V                                                  | 3.800 V                                                | 3.00 V                                                      | 3.20 V                                                    | (1)                         | CMOS output active "L" |  |  |  |  |  |

| S-8211EAI-I6T1U | 3.800 V                                                  | 3.700 V                                                | 2.30 V                                                      | 2.40 V                                                    | (1)                         | CMOS output active "L" |  |  |  |  |  |

| S-8211EAP-I6T1U | 4.280 V                                                  | 4.080 V                                                | 2.50 V                                                      | 2.50 V                                                    | (1)                         | CMOS output active "L" |  |  |  |  |  |

\*1. Refer to the Table 3 about the details of the delay time combinations (1), (2).

Remark Please contact our sales office for the products with detection voltage value other than those specified above.

| _ |             | Table 3                         |                                    |

|---|-------------|---------------------------------|------------------------------------|

| ſ | Delay Time  | Overcharge Detection Delay Time | Overdischarge Detection Delay Time |

|   | Combination | [tcu]                           | [t <sub>DL</sub> ]                 |

| ſ | (1)         | 1.2 s                           | 150 ms                             |

|   | (2)         | 573 ms                          | 300 ms                             |

Remark The delay times can be changed within the range listed Table 4. For details, please contact our sales office.

| Table 4                            |                 |        |             |        |                               |  |  |  |  |

|------------------------------------|-----------------|--------|-------------|--------|-------------------------------|--|--|--|--|

| Delay Time                         | Symbol          | Se     | lection Rar | nge    | Remark                        |  |  |  |  |

| Overcharge detection delay time    | tcu             | 143 ms | 573 ms      | 1.2 s  | Select a value from the left. |  |  |  |  |

| Overdischarge detection delay time | t <sub>DL</sub> | 38 ms  | 150 ms      | 300 ms | Select a value from the left. |  |  |  |  |

**Remark** The value surrounded by bold lines is the delay time of the standard products.

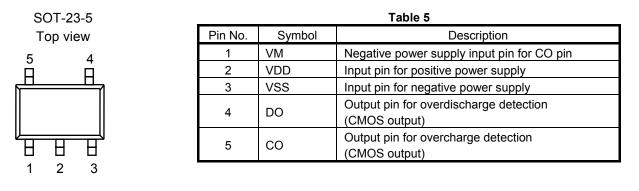

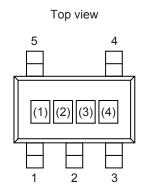

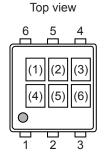

## Pin Configurations

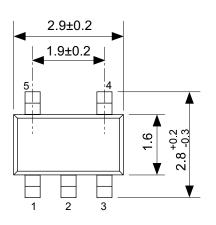

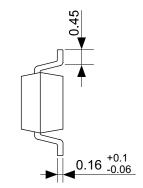

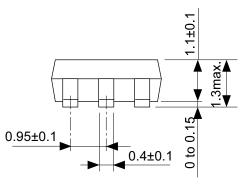

#### 1. SOT-23-5

Figure 2

#### 2. SNT-6A

Figure 3

| Table 6                                    |                           |  |  |  |  |  |  |  |  |

|--------------------------------------------|---------------------------|--|--|--|--|--|--|--|--|

| Pin No. Symbol                             | Description               |  |  |  |  |  |  |  |  |

| 1 NC <sup>*1</sup> No connection           |                           |  |  |  |  |  |  |  |  |

| 2 CO Output pin for overce (CMOS output)   | charge detection          |  |  |  |  |  |  |  |  |

| 3 DO Output pin for overd<br>(CMOS output) | discharge detection       |  |  |  |  |  |  |  |  |

| 4 VSS Input pin for negativ                | e power supply            |  |  |  |  |  |  |  |  |

| 5 VDD Input pin for positive               | e power supply            |  |  |  |  |  |  |  |  |

| 6 VM Negative power sup                    | oply input pin for CO pin |  |  |  |  |  |  |  |  |

\*1. The NC pin is electrically open.

The NC pin can be connected to VDD pin or VSS pin.

### Absolute Maximum Ratings

|                                           |          |                  |             | (Ta = +25°C unless otherw        | ise specified) |

|-------------------------------------------|----------|------------------|-------------|----------------------------------|----------------|

| Iter                                      | n        | Symbol           | Applied pin | Absolute Maximum Ratings         | Unit           |

| Input voltage between VDD pin and VSS pin |          | V <sub>DS</sub>  | VDD         | $V_{SS}-0.3$ to $V_{SS}+12$      | V              |

| VM pin input voltage                      |          | V <sub>VM</sub>  | VM          | $V_{DD} - 28$ to $V_{DD} + 0.3$  | V              |

| DO pin output voltage                     |          | V <sub>DO</sub>  | DO          | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V              |

| CO pin output volta                       | ge       | Vco              | СО          | $V_{VM} - 0.3$ to $V_{DD} + 0.3$ | V              |

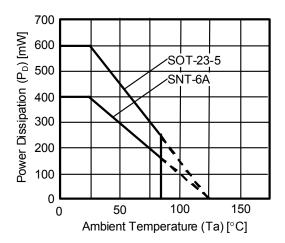

| Dewer dissigntion                         | SOT-23-5 |                  | _           | 600* <sup>1</sup>                | mW             |

| Power dissipation                         | SNT-6A   | PD               | _           | 400*1                            | mW             |

| Operating ambient temperature             |          | T <sub>opr</sub> | _           | -40 to +85                       | °C             |

| Storage temperatur                        | e        | T <sub>stg</sub> | _           | –55 to +125                      | °C             |

|                                           |          |                  |             |                                  |                |

Table 7

\*1. When mounted on board

[Mounted board]

(1) Board size: 114.3 mm × 76.2 mm × t1.6 mm

(2) Board name: JEDEC STANDARD51-7

Figure 4 Power Dissipation of Package (When Mounted on Board)

### Electrical Characteristics

#### 1. Except Detection Delay Time (+25°C)

Table 8

|                                               |                    |                                       |                                    | (Ta =                     | +25°C           | unless o                  | other | wise sp                | ecified)        |

|-----------------------------------------------|--------------------|---------------------------------------|------------------------------------|---------------------------|-----------------|---------------------------|-------|------------------------|-----------------|

| Item                                          | Symbol             | Cond                                  | dition                             | Min.                      | Тур.            | Max.                      | Unit  | Test<br>Condi-<br>tion | Test<br>Circuit |

| DETECTION VOLTAGE                             |                    |                                       |                                    |                           |                 |                           |       |                        |                 |

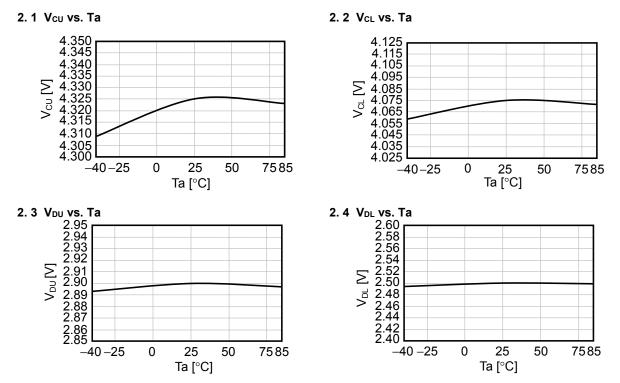

|                                               | Vcu                | 3.60 V to 4.50 V,                     | Adjustable                         | V <sub>CU</sub><br>-0.025 | V <sub>CU</sub> | V <sub>CU</sub><br>+0.025 | V     | 1                      | 1               |

| Overcharge detection voltage                  | VCU                | 3.60 V to 4.50 V,<br>Ta = -5°C to +55 |                                    | V <sub>CU</sub><br>-0.03  | Vcu             | V <sub>CU</sub><br>+0.03  | V     | 1                      | 1               |

|                                               | V <sub>CL</sub>    | 3.50 V to 4.40 V,                     | $V_{CL} \neq V_{CU}$               | V <sub>CL</sub><br>-0.05  | V <sub>CL</sub> | V <sub>CL</sub><br>+0.05  | V     | 1                      | 1               |

| Overcharge release voltage                    |                    | Adjustable                            | V <sub>CL</sub> = V <sub>CU</sub>  | V <sub>CL</sub><br>-0.05  | V <sub>CL</sub> | V <sub>CL</sub><br>+0.025 | V     | 1                      | 1               |

| Overdischarge detection voltage               | V <sub>DL</sub>    | 2.00 V to 3.00 V, Adjustable          |                                    | V <sub>DL</sub><br>-0.05  | V <sub>DL</sub> | V <sub>DL</sub><br>+0.05  | V     | 2                      | 2               |

|                                               | V <sub>DU</sub>    | 2.00 V to 3.40 V,<br>Adjustable       | $V_{\text{DU}} \neq V_{\text{DL}}$ | V <sub>DU</sub><br>-0.10  | V <sub>DU</sub> | V <sub>DU</sub><br>+0.10  | V     | 2                      | 2               |

| Overdischarge release voltage                 |                    |                                       | V <sub>DU</sub> = V <sub>DL</sub>  | V <sub>DU</sub><br>-0.05  | V <sub>DU</sub> | V <sub>DU</sub><br>+0.05  | V     | 2                      | 2               |

| INPUT VOLTAGE                                 |                    |                                       |                                    |                           |                 | _                         | _     |                        | _               |

| Operating voltage between VDD pin and VSS pin | V <sub>DSOP1</sub> | -                                     | -                                  | 1.5                       | -               | 8                         | V     | -                      | -               |

| INPUT CURRENT                                 |                    |                                       |                                    |                           |                 |                           |       | -                      | _               |

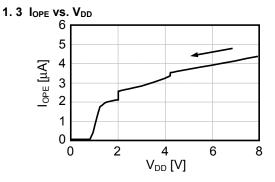

| Current consumption during operation          | I <sub>OPE</sub>   | $V_{DD}$ = 3.5 V, $V_{VM}$            | = 0 V                              | 1.0                       | 3.0             | 5.5                       | μA    | 3                      | 2               |

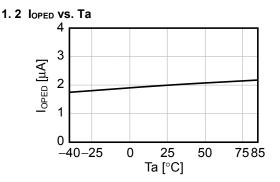

| Current consumption during overdischarge      | I <sub>OPED</sub>  | $V_{DD}$ = 1.5 V, $V_{VM}$            | = 0 V                              | 0.3                       | 2.0             | 3.5                       | μA    | 3                      | 2               |

| OUTPUT RESISTANCE                             |                    |                                       |                                    |                           |                 |                           |       |                        |                 |

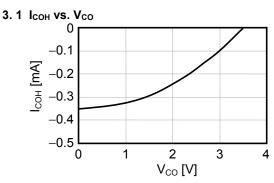

| CO pin resistance "H"                         | RCOH               | -                                     | _                                  | 2.5                       | 5               | 10                        | kΩ    | 4                      | 3               |

| CO pin resistance "L"                         | R <sub>COL</sub>   | CO pin output log                     |                                    | 2.5                       | 9               | 15                        | kΩ    | 4                      | 3               |

|                                               |                    | CO pin output log                     | ic active "L"                      | 2.5                       | 5               | 10                        | kΩ    | 4                      | 3               |

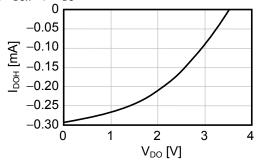

| DO pin resistance "H"                         | R <sub>DOH</sub>   | -                                     | -                                  | 2.5                       | 5               | 10                        | kΩ    | 5                      | 3               |

| DO pin resistance "L"                         | R <sub>DOL</sub>   | -                                     | _                                  | 2.5                       | 5               | 10                        | kΩ    | 5                      | 3               |

\*1. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

#### Rev.2.4\_02

## 2. Except Detection Delay Time (–40°C to +85°C $^{\star1}$ )

|                                               |                           |                                 | (Ta = –4                          | 0°C to +                  | -85°C *1        | unless                     | other | wise sp                | ecified)        |

|-----------------------------------------------|---------------------------|---------------------------------|-----------------------------------|---------------------------|-----------------|----------------------------|-------|------------------------|-----------------|

| Item                                          | Symbol                    | Condition                       |                                   | Min.                      | Тур.            | Max.                       | Unit  | Test<br>Condi-<br>tion | Test<br>Circuit |

| DETECTION VOLTAGE                             |                           |                                 |                                   |                           |                 |                            |       |                        |                 |

| Overcharge detection voltage                  | Vcu                       | 3.60 V to 4.50 V,               | 3.60 V to 4.50 V, Adjustable      |                           | Vcu             | V <sub>CU</sub><br>+ 0.040 | V     | 1                      | 1               |

|                                               |                           | 3.50 V to 4.40 V,               | $V_{CL} \neq V_{CU}$              | V <sub>CL</sub><br>- 0.08 | V <sub>CL</sub> | V <sub>CL</sub><br>+ 0.065 | V     | 1                      | 1               |

| Overcharge release voltage                    | Vercharge release voltage | Adjustable                      | V <sub>CL</sub> = V <sub>CU</sub> | V <sub>CL</sub><br>- 0.08 | V <sub>CL</sub> | V <sub>CL</sub><br>+ 0.04  | V     | 1                      | 1               |

| Overdischarge detection voltage               | Vdl                       | 2.00 V to 3.00 V, Adjustable    |                                   | V <sub>DL</sub><br>- 0.11 | $V_{\text{DL}}$ | V <sub>DL</sub><br>+ 0.13  | V     | 2                      | 2               |

| <b>•</b> • • • •                              | V <sub>DU</sub>           | 2.00 V to 3.40 V,<br>Adjustable | $V_{DU} \neq V_{DL}$              | V <sub>DU</sub><br>- 0.15 | V <sub>DU</sub> | V <sub>DU</sub><br>+ 0.19  | V     | 2                      | 2               |

| Overdischarge release voltage                 |                           |                                 | V <sub>DU</sub> = V <sub>DL</sub> | V <sub>DU</sub><br>- 0.11 | V <sub>DU</sub> | V <sub>DU</sub><br>+ 0.13  | V     | 2                      | 2               |

| INPUT VOLTAGE                                 |                           |                                 |                                   |                           |                 |                            |       |                        |                 |

| Operating voltage between VDD pin and VSS pin | V <sub>DSOP1</sub>        | -                               | -                                 | 1.5                       | -               | 8                          | V     | -                      | -               |

| INPUT CURRENT                                 |                           |                                 |                                   |                           |                 |                            |       |                        |                 |

| Current consumption during operation          | I <sub>OPE</sub>          | $V_{DD}$ = 3.5 V, $V_{VM}$      | = 0 V                             | 0.7                       | 3.0             | 6.0                        | μΑ    | 3                      | 2               |

| Current consumption during overdischarge      | I <sub>OPED</sub>         | $V_{DD}$ = 1.5 V, $V_{VM}$      | = 0 V                             | 0.2                       | 2.0             | 3.8                        | μΑ    | 3                      | 2               |

| OUTPUT RESISTANCE                             |                           | _                               |                                   |                           |                 |                            |       |                        |                 |

| CO pin resistance "H"                         | RCOH                      | -                               | _                                 | 1.2                       | 5               | 15                         | kΩ    | 4                      | 3               |

| CO pin resistance "L"                         | R <sub>COL</sub>          | CO pin output logic active "H"  |                                   | 1.2                       | 9               | 27                         | kΩ    | 4                      | 3               |

|                                               | NCOL                      | CO pin output log               | CO pin output logic active "L"    |                           | 5               | 15                         | kΩ    | 4                      | 3               |

| DO pin resistance "H"                         | RDOH                      | -                               | _                                 | 1.2                       | 5               | 15                         | kΩ    | 5                      | 3               |

| DO pin resistance "L"                         | R <sub>DOL</sub>          | -                               | -                                 | 1.2                       | 5               | 15                         | kΩ    | 5                      | 3               |

Table 9

\*1. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

#### 3. Detection Delay Time

#### 3. 1 S-8211EAC, S-8211EAH, S-8211EAI, S-8211EAJ, S-8211EAK, S-8211EAP

Table 10

| ltem                                           | Symbol          | Condition | Min. | Тур. | Max. | Unit | Test<br>Condi-<br>tion | Test<br>Circuit |

|------------------------------------------------|-----------------|-----------|------|------|------|------|------------------------|-----------------|

| DELAY TIME (Ta = +25°C)                        |                 |           |      |      |      |      |                        |                 |

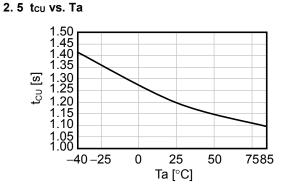

| Overcharge detection delay time                | t <sub>cu</sub> | -         | 0.96 | 1.2  | 1.4  | S    | 6                      | 4               |

| Overdischarge detection delay time             | t <sub>DL</sub> | -         | 120  | 150  | 180  | ms   | 6                      | 4               |

| DELAY TIME (Ta = -40°C to +85°C) <sup>*1</sup> |                 |           |      |      |      |      |                        |                 |

| Overcharge detection delay time                | t <sub>cu</sub> | -         | 0.7  | 1.2  | 2.0  | S    | 6                      | 4               |

| Overdischarge detection delay time             | t <sub>DL</sub> | _         | 83   | 150  | 255  | ms   | 6                      | 4               |

\*1. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

#### 3. 2 S-8211EAA, S-8211EAB, S-8211EAD, S-8211EAE, S-8211EAF, S-8211EAG

|                                     |                 | Table 11  |      |      |      |      |                        |                 |

|-------------------------------------|-----------------|-----------|------|------|------|------|------------------------|-----------------|

| ltem                                | Symbol          | Condition | Min. | Тур. | Max. | Unit | Test<br>Condi-<br>tion | Test<br>Circuit |

| DELAY TIME (Ta = +25°C)             |                 |           |      |      | _    |      |                        |                 |

| Overcharge detection delay time     | t <sub>CU</sub> | -         | 458  | 573  | 687  | ms   | 6                      | 4               |

| Overdischarge detection delay time  | t <sub>DL</sub> | -         | 240  | 300  | 360  | ms   | 6                      | 4               |

| DELAY TIME (Ta = -40°C to +85°C) *1 |                 |           |      |      |      |      |                        |                 |

| Overcharge detection delay time     | tcu             | -         | 334  | 573  | 955  | ms   | 6                      | 4               |

| Overdischarge detection delay time  | t <sub>DL</sub> | _         | 166  | 300  | 510  | ms   | 6                      | 4               |

\*1. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

#### Test Circuits

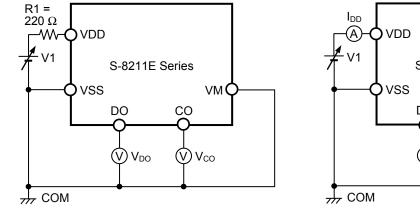

Caution Unless otherwise specified, the output voltage levels "H" and "L" at CO pin (V<sub>CO</sub>) are judged by  $V_{VM}$  + 1.0 V, and the output voltage levels "H" and "L" at DO pin (V<sub>DO</sub>) are judged by  $V_{SS}$  + 1.0 V. Judge the CO pin level with respect to  $V_{VM}$  and the DO pin level with respect to  $V_{SS}$ .

## 1. Overcharge Detection Voltage, Overcharge Release Voltage (Test Condition 1, Test Circuit 1)

#### 1. 1 CO pin output logic = Active "H"

Overcharge detection voltage (V<sub>CU</sub>) is defined as the voltage between the VDD pin and VSS pin at which V<sub>CO</sub> goes from "L" to "H" when the voltage V1 is gradually increased from the starting condition of V1 = 3.5 V. Overcharge release voltage (V<sub>CL</sub>) is defined as the voltage between the VDD pin and VSS pin at which V<sub>CO</sub> goes from "H" to "L" when the voltage V1 is then gradually decreased. Overcharge hysteresis voltage (V<sub>HC</sub>) is defined as the difference between overcharge detection voltage (V<sub>CU</sub>) and overcharge release voltage (V<sub>CL</sub>).

#### 1. 2 CO pin output logic = Active "L"

Overcharge detection voltage (V<sub>CU</sub>) is defined as the voltage between the VDD pin and VSS pin at which V<sub>CO</sub> goes from "H" to "L" when the voltage V1 is gradually increased from the starting condition of V1 = 3.5 V. Overcharge release voltage (V<sub>CL</sub>) is defined as the voltage between the VDD pin and VSS pin at which V<sub>CO</sub> goes from "L" to "H" when the voltage V1 is then gradually decreased. Overcharge hysteresis voltage (V<sub>HC</sub>) is defined as the difference between overcharge detection voltage (V<sub>CU</sub>) and overcharge release voltage (V<sub>CL</sub>).

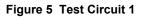

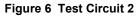

## 2. Overdischarge Detection Voltage, Overdischarge Release Voltage (Test Condition 2, Test Circuit 2)

Overdischarge detection voltage ( $V_{DL}$ ) is defined as the voltage between the VDD pin and VSS pin at which  $V_{DO}$  goes from "H" to "L" when the voltage V1 is gradually decreased from the starting condition of V1 = 3.5 V, V2 = 0 V. Overdischarge release voltage ( $V_{DU}$ ) is defined as the voltage between the VDD pin and VSS pin at which  $V_{DO}$  goes from "L" to "H" when the voltage V1 is then gradually increased. Overdischarge hysteresis voltage ( $V_{HD}$ ) is defined as the difference between overdischarge release voltage ( $V_{DU}$ ) and overdischarge detection voltage ( $V_{DL}$ ).

## 3. Current Consumption during Operation (Test Condition 3, Test Circuit 2)

The current consumption during operation ( $I_{OPE}$ ) is the current that flows through the VDD pin ( $I_{DD}$ ) under the set conditions of V1 = 3.5 V and V2 = 0 V (normal status).

## 4. Current Consumption during Overdischarge (Test Condition 3, Test Circuit 2)

The current consumption during overdischarge ( $I_{OPED}$ ) is the current that flows through the VDD pin ( $I_{DD}$ ) under the set conditions of V1 = 1.5 V, V2 = 0V (overdischarge status).

#### 5. CO Pin Resistance "H" (Test Condition 4, Test Circuit 3)

#### 5. 1 CO pin output logic = Active "H"

The CO pin resistance "H" ( $R_{COH}$ ) is the resistance at the CO pin under the set conditions of V1 = 4.5 V, V2 = 0 V, V3 = 4.0 V.

#### 5. 2 CO pin output logic = Active "L"

The CO pin resistance "H" ( $R_{COH}$ ) is the resistance at the CO pin under the set conditions of V1 = 3.5 V, V2 = 0 V, V3 = 3.0 V.

#### 6. CO Pin Resistance "L" (Test Condition 4, Test Circuit 3)

#### 6. 1 CO pin output logic = Active "H"

The CO pin resistance "L" ( $R_{COL}$ ) is the resistance at the CO pin under the set conditions of V1 = 3.5 V, V2 = 0 V, V3 = 0.5 V.

#### 6. 2 CO pin output logic = Active "L"

The CO pin resistance "L" ( $R_{COL}$ ) is the resistance at the CO pin under the set conditions of V1 = 4.5 V, V2 = 0 V, V3 = 0.5 V.

#### 7. DO Pin Resistance "H" (Test Condition 5, Test Circuit 3)

The DO pin "H" resistance ( $R_{DOH}$ ) is the resistance at the DO pin under the set conditions of V1 = 3.5 V, V2 = 0 V, V4 = 3.0 V.

#### 8. DO Pin Resistance "L" (Test Condition 5, Test Circuit 3)

The DO pin "L" resistance ( $R_{DOL}$ ) is the resistance at the DO pin under the set conditions of V1 = 1.8 V, V2 = 0 V, V4 = 0.5 V.

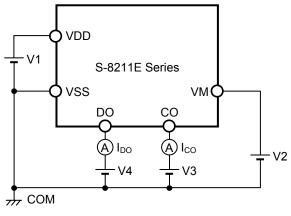

#### 9. Overcharge Detection Delay Time (Test Condition 6, Test Circuit 4)

#### 9. 1 CO pin output logic = Active "H"

The overcharge detection delay time (t<sub>CU</sub>) is the time needed for V<sub>CO</sub> to change from "L" to "H" just after the voltage V1 momentarily increases (within 10  $\mu$ s) from overcharge detection voltage (V<sub>CU</sub>) –0.2 V to overcharge detection voltage (V<sub>CU</sub>) +0.2 V under the set conditions of V2 = 0 V.

#### 9. 2 CO pin output logic = Active "L"

The overcharge detection delay time (t<sub>CU</sub>) is the time needed for V<sub>CO</sub> to change from "H" to "L" just after the voltage V1 momentarily increases (within 10  $\mu$ s) from overcharge detection voltage (V<sub>CU</sub>) –0.2 V to overcharge detection voltage (V<sub>CU</sub>) +0.2 V under the set conditions of V2 = 0 V.

#### 10. Overdischarge Detection Delay Time (Test Condition 6, Test Circuit 4)

The overdischarge detection delay time (t<sub>DL</sub>) is the time needed for V<sub>D0</sub> to change from "H" to "L" just after the voltage V1 momentarily decreases (within 10  $\mu$ s) from overdischarge detection voltage (V<sub>DL</sub>) +0.2 V to overdischarge detection voltage (V<sub>DL</sub>) -0.2 V under the set condition of V2 = 0 V.

VDD VDD VSS VM DO Oscilloscope VSS VM VM VZ VZ

#### Rev.2.4\_02

#### Operation

**Remark** Refer to the "

Battery Protection IC Connection Example".

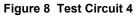

#### 1. Normal Status

The S-8211E Series monitors the voltage of the battery connected between the VDD and VSS pins. In case of overdischarge detection voltage ( $V_{DL}$ )  $\leq$  battery voltage  $\leq$  overcharge detection voltage ( $V_{CU}$ ), the output levels of CO and DO pins are as follows. This is the normal status.

| Table 12            |                 |                 |  |  |

|---------------------|-----------------|-----------------|--|--|

| CO Pin Output Logic | CO Pin          | DO Pin          |  |  |

| Active "H"          | Vvm             | V <sub>DD</sub> |  |  |

| Active "L"          | V <sub>DD</sub> | V <sub>DD</sub> |  |  |

#### 2. Overcharge Status

When the battery voltage in the normal status exceeds the overcharge detection voltage ( $V_{CU}$ ) during charge, and this status is held for the overcharge detection delay time ( $t_{CU}$ ) or more, the output levels of CO and DO pins are as follows. This is the overcharge status.

This overcharge status is released when the battery voltage decreases to the overcharge release voltage ( $V_{CL}$ ) or less.

| Table 13            |                 |                 |  |  |

|---------------------|-----------------|-----------------|--|--|

| CO Pin Output Logic | CO Pin          | DO Pin          |  |  |

| Active "H"          | V <sub>DD</sub> | V <sub>DD</sub> |  |  |

| Active "L"          | V <sub>VM</sub> | V <sub>DD</sub> |  |  |

#### 3. Overdischarge Status

When the battery voltage in the normal status decreases than the overcharge detection voltage ( $V_{DL}$ ) during discharge, and this status is held for the overdischarge detection delay time ( $t_{DL}$ ) or more, the output levels of CO and DO pins are as follows. This is the overdischarge status.

This overdischarge status is released when the battery voltage increases to the overdischarge release voltage ( $V_{DU}$ ) or more.

| Table 14                        |                 |        |  |

|---------------------------------|-----------------|--------|--|

| CO Pin Output Logic CO Pin DO F |                 | DO Pin |  |

| Active "H"                      | Vvm             | Vss    |  |

| Active "L"                      | V <sub>DD</sub> | Vss    |  |

#### 4. Delay Circuit

The detection delay times are determined by dividing a clock of approximately 3.5 kHz by the counter.

## Timing Chart

#### 1. Overcharge Detection, Overdischarge Detection

\*1. (1) : Normal status

(2) : Overcharge status

(3): Overdischarge status

Figure 9

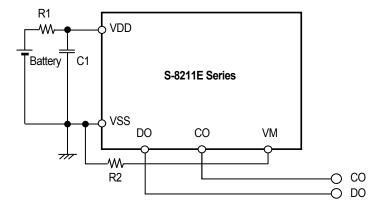

## Battery Protection IC Connection Example

Table 15 Constants for External Components

| Symbol | Part      | Purpose                                  | Min.     | Тур.   | Max.   | Remark                                                                                                                             |

|--------|-----------|------------------------------------------|----------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| R1     | Resistor  | ESD protection,<br>For power fluctuation | 100 Ω    | 220 Ω  | 330 Ω  | Resistance should be as small as possible to<br>avoid lowering the overcharge detection<br>accuracy due to current consumption. *1 |

| C1     | Capacitor | For power fluctuation                    | 0.022 μF | 0.1 μF | 1.0 μF | Connect a capacitor of 0.022 $\mu$ F or higher between VDD pin and VSS pin. *2                                                     |

| R2*3   | Resistor  | ESD protection                           | 300 Ω    | 1 kΩ   | 4 kΩ   | -                                                                                                                                  |

**\*1.** Insert a resistor of 100  $\Omega$  or higher as R1 for ESD protection.

\*2. If a capacitor of less than 0.022 μF is connected to C1, DO pin may oscillate. Be sure to connect a capacitor of 0.022 μF or higher to C1.

**\*3.** Be sure to using R2, connect the VM pin with the VSS pin.

#### Caution 1. The above constants may be changed without notice.

2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.

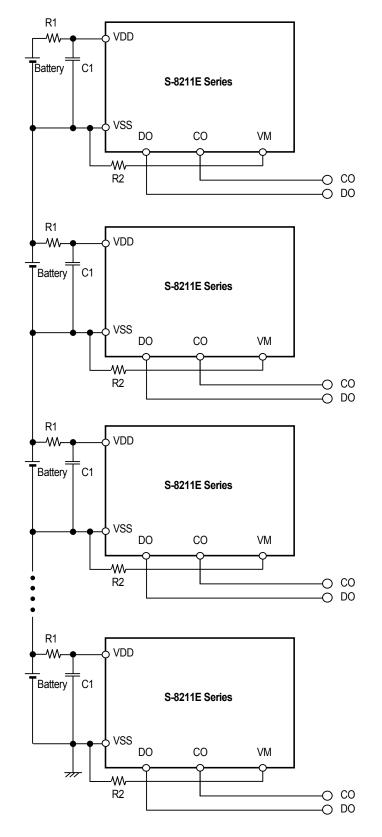

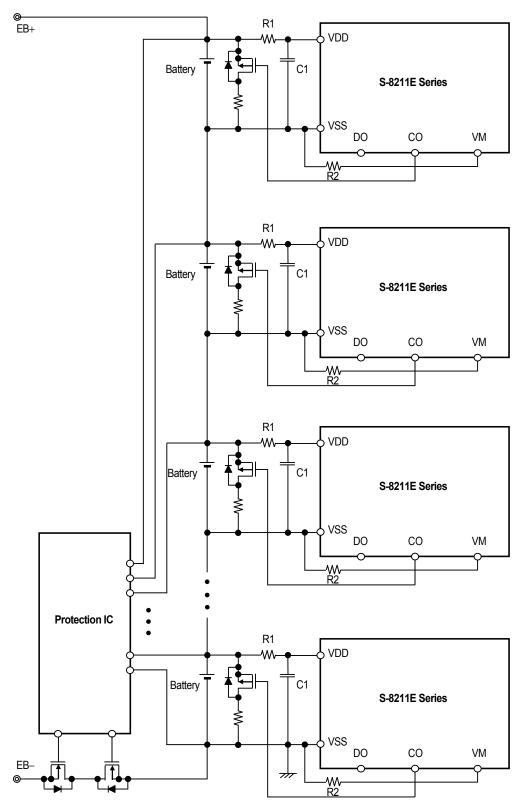

## Application Circuit Examples

1. Protection circuits series multi-cells

#### 2. Charge cell-balance detection circuit

Figure 12

#### Precautions

- The application conditions for the input voltage, output voltage, and load current should not exceed the package power dissipation.

- Be sure to using R2, connect the VM pin with the VSS pin.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- SII Semiconductor Corporation claims no responsibility for any and all disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

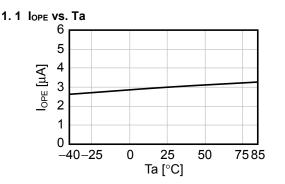

### Characteristics (Typical Data)

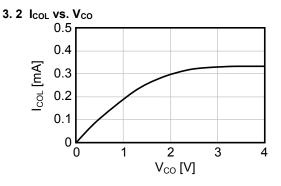

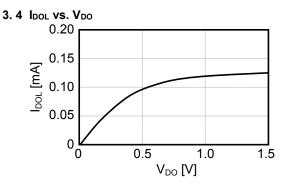

1. Current Consumption

2. Overcharge Detection / Release Voltage, Overdischarge Detection / Release Voltage, Overcurrent Detection Voltage, and Delay Time

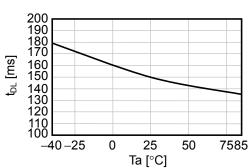

2.6 t<sub>DL</sub> vs. Ta

## Marking Specifications

#### 1. SOT-23-5

(1) to (3): (4) :

Product Code (refer to **Product Name vs. Product Code**) Lot number

#### Product Name vs. Product Code

| Product Name    | Product Code |     |     |

|-----------------|--------------|-----|-----|

| Floudet Name    | (1)          | (2) | (3) |

| S-8211EAC-M5T1U | R            | 3   | С   |

| S-8211EAF-M5T1U | R            | 3   | F   |

| S-8211EAG-M5T1U | R            | 3   | G   |

| S-8211EAJ-M5T1U | R            | 3   | J   |

| S-8211EAK-M5T1U | R            | 3   | K   |

#### 2. SNT-6A

(1) to (3): (4) to (6): Product Code (refer to **Product Name vs. Product Code**) Lot number

#### Product Name vs. Product Code

| Product Name    | Product Code |     |     |

|-----------------|--------------|-----|-----|

| FIGULE Name     | (1)          | (2) | (3) |

| S-8211EAA-I6T1U | R            | 3   | А   |

| S-8211EAB-I6T1U | R            | 3   | В   |

| S-8211EAD-I6T1U | R            | 3   | D   |

| S-8211EAE-I6T1U | R            | 3   | Е   |

| S-8211EAH-I6T1U | R            | 3   | Н   |

| S-8211EAI-I6T1U | R            | 3   | Ι   |

| S-8211EAP-I6T1U | R            | 3   | Р   |

## No. MP005-A-P-SD-1.2

| TITLE                         | SOT235-A-PKG Dimensions |  |

|-------------------------------|-------------------------|--|

| No.                           | MP005-A-P-SD-1.2        |  |

| SCALE                         |                         |  |

| UNIT                          | mm                      |  |

|                               |                         |  |

|                               |                         |  |

|                               |                         |  |

| SII Semiconductor Corporation |                         |  |

SII Semiconductor Corporation