# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# S-8250A Series

### BATTERY PROTECTION IC WITH DISCHARGE CONTROL FUNCTION FOR 1-CELL PACK

www.sii-ic.com

SII **O**

© SII Semiconductor Corporation, 2013-2016

The S-8250A Series is a protection IC for 1-cell lithium-ion / lithium polymer rechargeable batteries and includes high-accuracy voltage detection circuits and delay circuits.

The S-8250A Series is suitable for protecting 1-cell lithium-ion / lithium polymer rechargeable battery packs from overcharge, overdischarge, overcurrent, and controlling discharge by external signal. By adjusting power supply voltage dependency of discharge overcurrent detection voltage in accordance with ON resistance of the charge-discharge control FET, the S-8250A Series realizes high-accuracy discharge overcurrent detection.

### Features

- High-accuracy discharge overcurrent detection circuit

Discharge overcurrent detection voltage

0.050 V to 0.150 V (1 mV step)

Accuracy ±10 mV (Ta = +25°C)

(Power supply voltage dependency can be set in accordance with ON resistance of the charge-discharge control FET.)

- High-accuracy voltage detection circuit Overcharge detection voltage 4.100 V to 4.600 V (5 mV step) Accuracy  $\pm 20 \text{ mV}$  (Ta =  $+25^{\circ}$ C) Accuracy  $\pm 25 \text{ mV}$  (Ta =  $-10^{\circ}\text{C}$  to  $+60^{\circ}\text{C}$ ) 3.700 V to 4.600 V<sup>\*1</sup> Overcharge release voltage Accuracy ±30 mV 2.000 V to 2.800 V (10 mV step) Overdischarge detection voltage Accuracy ±50 mV 2.000 V to 3.000 V\*2 Overdischarge release voltage Accuracy ±100 mV Load short-circuiting detection voltage 0.250 V to 0.500 V (50 mV step) Accuracy ±50 mV -0.200 V to -0.025 V (25 mV step) Charge overcurrent detection voltage Accuracy ±15 mV Detection delay times are generated only by an internal circuit (External capacitors are unnecessary).

- Discharge control function

- CTL pin control logic is selectable:

- CTL pin internal resistance connection is selectable: CTL pin internal resistance value is selectable:

- Discharge inhibition status latch function is selectable:

- 0 V battery charge function is selectable:

- Power-down function is selectable:

- Release condition of discharge overcurrent status is selectable:

- High-withstand voltage:

- Wide operation temperature range:

- Low current consumption During operation: During power-down:

- Active "H", active "L" Pull-up, pull-down 1.0 M $\Omega$ , 2.0 M $\Omega$ , 3.0 M $\Omega$ , 4.0 M $\Omega$ , 5.0 M $\Omega$ Available, unavailable Available, unavailable Available, unavailable Load disconnection, charger connection VM pin and CO pin: Absolute maximum rating 28 V Ta = -40°C to +85°C

- 2.0 μA typ., 4.0 μA max. (Ta = +25°C) 50 nA max. (Ta = +25°C)

- Lead-free (Sn 100%), halogen-free

- \*1. Overcharge release voltage = Overcharge detection voltage Overcharge hysteresis voltage (Overcharge hysteresis voltage can be selected from a range of 0 V to 0.4 V in 50 mV step.)

- \*2. Overdischarge release voltage = Overdischarge detection voltage + Overdischarge hysteresis voltage (Overdischarge hysteresis voltage can be selected from a range of 0 V to 0.7 V in 100 mV step.)

### Applications

- Lithium-ion rechargeable battery pack

- Lithium polymer rechargeable battery pack

### Package

• SNT-6A

### Rev.1.3\_02

### BATTERY PROTECTION IC WITH DISCHARGE CONTROL FUNCTION FOR 1-CELL PACK S-8250A Series

Rev.1.3\_02

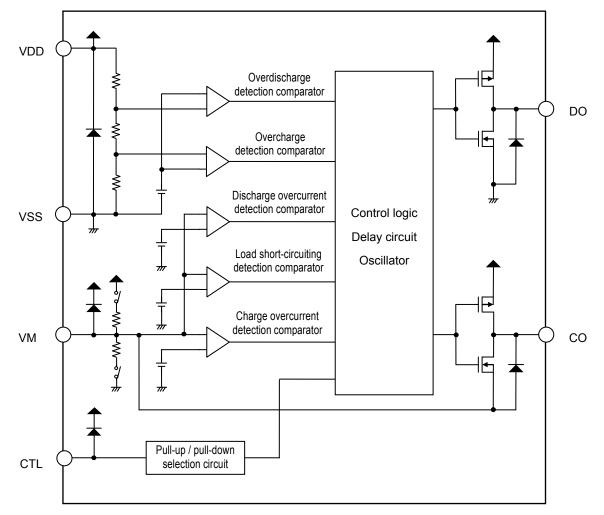

### Block Diagram

Remark All the diodes shown in the figure are parasitic diodes.

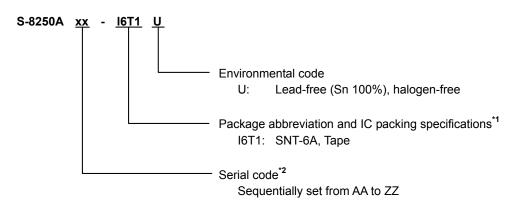

### Product Name Structure

1. Product name

- \*1. Refer to the tape drawing.

- \*2. Refer to "3. Product name list".

### 2. Package

Table 1 Package Drawing Codes

| Package Name | Dimension    | Таре         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| SNT-6A       | PG006-A-P-SD | PG006-A-C-SD | PG006-A-R-SD | PG006-A-L-SD |

### 3. Product name list

### 3.1 SNT-6A

### Table 2 (1 / 2)

| Product Name    | Overcharge<br>Detection<br>Voltage<br>[Vcu] | Overcharge<br>Release<br>Voltage<br>[V <sub>CL</sub> ] | Overdischarge<br>Detection<br>Voltage<br>[V <sub>DL</sub> ] | Overdischarge<br>Release<br>Voltage<br>[V <sub>DU</sub> ] | Delay Time<br>Combination <sup>*1</sup> | Function<br>Combination <sup>*2</sup> |

|-----------------|---------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------|---------------------------------------|

| S-8250AAB-I6T1U | 4.280 V                                     | 4.180 V                                                | 2.300 V                                                     | 2.300 V                                                   | (1)                                     | (1)                                   |

| S-8250AAE-I6T1U | 4.410 V                                     | 4.210 V                                                | 2.300 V                                                     | 2.300 V                                                   | (2)                                     | (2)                                   |

| S-8250AAG-I6T1U | 4.425 V                                     | 4.225 V                                                | 2.500 V                                                     | 2.500 V                                                   | (1)                                     | (3)                                   |

### Table 2 (2 / 2)

| Product Name    | Discharge C             | vercurrent Detec<br>[V <sub>DIOV</sub> ] | tion Voltage            | Load Short-circuiting<br>Detection Voltage | Charge Overcurrent<br>Detection Voltage |

|-----------------|-------------------------|------------------------------------------|-------------------------|--------------------------------------------|-----------------------------------------|

|                 | V <sub>DD</sub> = 3.0 V | V <sub>DD</sub> = 3.4 V                  | V <sub>DD</sub> = 4.0 V | [V <sub>SHORT</sub> ]                      | [V <sub>CIOV</sub> ]                    |

| S-8250AAB-I6T1U | 0.122 V                 | 0.113 V                                  | 0.104 V                 | 0.500 V                                    | –0.100 V                                |

| S-8250AAE-I6T1U | 0.037 V                 | 0.036 V                                  | 0.034 V                 | 0.500 V                                    | –0.075 V                                |

| S-8250AAG-I6T1U | 0.081 V                 | 0.076 V                                  | 0.071 V                 | 0.500 V                                    | –0.100 V                                |

\*1. Refer to Table 3 about the details of the delay time combinations.

\*2. Refer to Table 5 about the details of the function combinations.

Remark Please contact our sales office for the products with detection voltage value other than those specified above.

| Table 3                   |                                                             |                                                                |                                                                             |                                                                              |                                                                          |                                                              |  |  |  |  |

|---------------------------|-------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| Delay Time<br>Combination | Overcharge<br>Detection<br>Delay Time<br>[t <sub>cu</sub> ] | Overdischarge<br>Detection<br>Delay Time<br>[t <sub>DL</sub> ] | Discharge<br>Overcurrent<br>Detection<br>Delay Time<br>[t <sub>DIOV</sub> ] | Load<br>Short-circuiting<br>Detection<br>Delay Time<br>[t <sub>SHORT</sub> ] | Charge<br>Overcurrent<br>Detection<br>Delay Time<br>[t <sub>ClOV</sub> ] | Discharge<br>Inhibition<br>Delay Time<br>[t <sub>CTL</sub> ] |  |  |  |  |

| (1)                       | 1.0 s                                                       | 128 ms                                                         | 32 ms                                                                       | 280 μs                                                                       | 8 ms                                                                     | 256 ms                                                       |  |  |  |  |

| (2)                       | 1.0 s                                                       | 32 ms                                                          | 16 ms                                                                       | 280 μs                                                                       | 16 ms                                                                    | 256 ms                                                       |  |  |  |  |

Remark The delay times can be changed within the range listed in Table 4. For details, please contact our sales office.

#### Table 4

| Delay Time                                 | Symbol             | Selection Range      |                     | ge                   | Remark                        |

|--------------------------------------------|--------------------|----------------------|---------------------|----------------------|-------------------------------|

| Overcharge detection delay time            | tcu                | 256 ms               | 512 ms              | 1.0 s <sup>*1</sup>  | Select a value from the left. |

| Overdischarge detection delay time         | t <sub>DL</sub>    | 32 ms                | 64 ms               | 128 ms <sup>*1</sup> | Select a value from the left. |

| Discharge overcurrent detection delay time | t <sub>DIOV</sub>  | 8 ms                 | 16 ms <sup>*1</sup> | 32 ms                | Select a value from the left. |

| Load short-circuiting detection delay time | t <sub>SHORT</sub> | 280 μs <sup>*1</sup> | 530 μs              | _                    | Select a value from the left. |

| Charge overcurrent detection delay time    | t <sub>CIOV</sub>  | 8 ms                 | 16 ms <sup>*1</sup> | 32 ms                | Select a value from the left. |

| Discharge inhibition delay time            | t <sub>CTL</sub>   | 64 ms                | 128 ms              | 256 ms <sup>*1</sup> | Select a value from the left. |

\*1. This value is the delay time of the standard products.

### Table 5

| Function    | CTL Pin Discharge Inhibition   |                                                    |                                                                   |                          | 0 V Battery                      | Power-                         | Release<br>Condition                                |

|-------------|--------------------------------|----------------------------------------------------|-------------------------------------------------------------------|--------------------------|----------------------------------|--------------------------------|-----------------------------------------------------|

| Combination | Control<br>Logic <sup>*1</sup> | Internal<br>Resistance<br>Connection <sup>*2</sup> | Internal<br>Resistance Value <sup>*3</sup><br>[R <sub>CTL</sub> ] | Status Latch Function *4 | Charge<br>Function <sup>*5</sup> | down<br>Function <sup>*6</sup> | of Discharge<br>Overcurrent<br>Status <sup>*7</sup> |

| (1)         | Active "H"                     | Pull-down                                          | 5.0 MΩ                                                            | Unavailable              | Available                        | Available                      | Charger connection                                  |

| (2)         | Active "H"                     | Pull-down                                          | 5.0 MΩ                                                            | Unavailable              | Unavailable                      | Available                      | Load<br>disconnection                               |

| (3)         | Active "H"                     | Pull-down                                          | 5.0 MΩ                                                            | Unavailable              | Unavailable                      | Available                      | Charger connection                                  |

Caution The combination of CTL pin control logic active "H" and CTL pin internal resistance connection "pull-up" worsens the accuracy of overcharge detection voltage. Therefore, this combination can not be set up.

\*1. CTL pin control logic active "H" / active "L" is selectable.

**\*2.** CTL pin internal resistance connection "pull-up" / "pull-down" is selectable.

\*3. CTL pin internal resistance value 1.0 M $\Omega$  / 2.0 M $\Omega$  / 3.0 M $\Omega$  / 4.0 M $\Omega$  / 5.0 M $\Omega$  is selectable.

\*4. Discharge inhibition status latch function "available" / "unavailable" is selectable.

\*5. 0 V battery charge function "available" / "unavailable" is selectable.

**\*6.** Power-down function "available" / "unavailable" is selectable.

\*7. Release condition of discharge overcurrent status "load disconnection" / "charger connection" is selectable.

**Remark** Please contact our sales office for the products with function combinations other than those specified above.

### Pin Configuration

### 1. SNT-6A

Top view 1 3 1 6 5 4

| Table 6 |        |                                                                                        |  |  |  |  |  |  |  |

|---------|--------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin No. | Symbol | Description                                                                            |  |  |  |  |  |  |  |

| 1       | CTL    | Discharge control pin                                                                  |  |  |  |  |  |  |  |

| 2       | со     | Connection pin of charge control FET gate (CMOS output)                                |  |  |  |  |  |  |  |

| 3       | DO     | Connection pin of discharge control FET gate (CMOS output)                             |  |  |  |  |  |  |  |

| 4       | VSS    | Input pin for negative power supply                                                    |  |  |  |  |  |  |  |

| 5       | VDD    | Input pin for positive power supply                                                    |  |  |  |  |  |  |  |

| 6       | VM     | Voltage detection pin between VM pin and VSS pin (Overcurrent / charger detection pin) |  |  |  |  |  |  |  |

### Absolute Maximum Ratings

|                                           |                  |             | (Ta = +25°C unless otherwise                   | e specified) |

|-------------------------------------------|------------------|-------------|------------------------------------------------|--------------|

| Item                                      | Symbol           | Applied pin | Absolute Maximum Rating                        | Unit         |

| Input voltage between VDD pin and VSS pin | V <sub>DS</sub>  | VDD         | $V_{\rm SS}-0.3$ to $V_{\rm SS}+12$            | V            |

| VM pin input voltage                      | V <sub>VM</sub>  | VM          | $V_{DD} - 28$ to $V_{DD} + 0.3$                | V            |

| DO pin output voltage                     | V <sub>DO</sub>  | DO          | $V_{\text{SS}} - 0.3$ to $V_{\text{DD}} + 0.3$ | V            |

| CO pin output voltage                     | V <sub>co</sub>  | СО          | $V_{\text{VM}} - 0.3$ to $V_{\text{DD}} + 0.3$ | V            |

| CTL pin input voltage                     | V <sub>CTL</sub> | CTL         | $V_{\text{SS}} - 0.3$ to $V_{\text{DD}} + 0.3$ | V            |

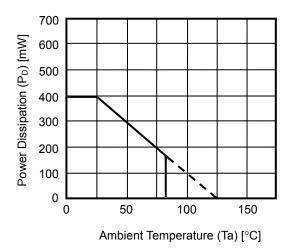

| Power dissipation                         | PD               | _           | 400 <sup>*1</sup>                              | mW           |

| Operation ambient temperature             | T <sub>opr</sub> | -           | -40 to +85                                     | °C           |

| Storage temperature                       | T <sub>stg</sub> | _           | -55 to +125                                    | °C           |

Table 7

\*1. When mounted on board

[Mounted board]

(1) Board size: 114.3 mm  $\times$  76.2 mm  $\times$  t1.6 mm

(2) Board name: JEDEC STANDARD51-7

# Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

Figure 3 Power Dissipation of Package (When Mounted on Board)

Table 8

### Electrical Characteristics

1. Ta = +25°C

Rev.1.3\_02

|                                               |                    | l able 8                                          | (Ta                          | a = +25°           | C unless otherwi             | ise sp    | ecified        |

|-----------------------------------------------|--------------------|---------------------------------------------------|------------------------------|--------------------|------------------------------|-----------|----------------|

| Item                                          | Symbol             | Condition                                         | Min.                         | Тур.               | Max.                         | Unit      | Test<br>Circui |

| Detection Voltage                             |                    |                                                   | ÷                            |                    |                              |           |                |

| Overcharge detection voltage                  | V                  | _                                                 | $V_{CU}-0.020$               | V <sub>CU</sub>    | $V_{CU} + 0.020$             | V         | 1              |

|                                               | V <sub>CU</sub>    | $Ta = -10^{\circ}C \text{ to } +60^{\circ}C^{*1}$ | $V_{\text{CU}}-0.025$        | V <sub>CU</sub>    | $V_{CU} + 0.025$             | V         | 1              |

| Overcharge release voltage                    | V <sub>CL</sub>    | $V_{CL} \neq V_{CU}$                              | $V_{\text{CL}}-0.030$        | V <sub>CL</sub>    | $V_{CL} + 0.030$             | V         | 1              |

|                                               |                    | $V_{CL} = V_{CU}$                                 | $V_{CL}-0.025$               | V <sub>CL</sub>    | $V_{CL} + 0.020$             | V         | 1              |

| Overdischarge detection voltage               | $V_{DL}$           | _                                                 | $V_{DL}-0.050$               | V <sub>DL</sub>    | $V_{DL} + 0.050$             | V         | 2              |

| Overdischarge release voltage                 | V <sub>DU</sub>    | V <sub>DL</sub> ≠ V <sub>DU</sub>                 | $V_{DU} - 0.100$             | V <sub>DU</sub>    | $V_{DU} + 0.100$             | V         | 2              |

|                                               | • 00               | $V_{DL} = V_{DU}$                                 | $V_{DU}-0.050$               | V <sub>DU</sub>    | $V_{DU} + 0.050$             | V         | 2              |

|                                               |                    | V <sub>DD</sub> = 3.0 V                           | $V_{\text{DIOV}}-0.010$      | VDIOV              | $V_{DIOV} + 0.010$           | V         | 2              |

| Discharge overcurrent detection voltage       | VDIOV              | V <sub>DD</sub> = 3.4 V                           | $V_{\text{DIOV}} - 0.010$    | VDIOV              | $V_{DIOV} + 0.010$           | V         | 2              |

|                                               |                    | V <sub>DD</sub> = 4.0 V                           | $V_{\text{DIOV}}-0.010$      | VDIOV              | $V_{DIOV} + 0.010$           | V         | 2              |

| Load short-circuiting detection voltage       | VSHORT             | _                                                 | V <sub>SHORT</sub> – 0.050   |                    | $V_{SHORT} + 0.050$          | V         | 2              |

| Charge overcurrent detection voltage          | VCIOV              | _                                                 | $V_{\text{CIOV}}-0.015$      | VCIOV              | $V_{\text{CIOV}} + 0.015$    | V         | 2              |

| 0 V Battery Charge Function                   | 1                  |                                                   | I                            | 1                  |                              | 1         | 1              |

| 0 V battery charge starting charger voltage   | V <sub>0CHA</sub>  | 0 V battery charge<br>function "available"        | 0.00                         | 0.70               | 1.00                         | V         | 2              |

| 0 V battery charge inhibition battery voltage | Voinh              | 0 V battery charge<br>function "unavailable"      | 0.90                         | 1.25               | 1.60                         | V         | 2              |

| Internal Resistance                           |                    |                                                   | •                            |                    |                              |           |                |

| Resistance between VM pin and VDD pin         | R <sub>VMD</sub>   | _                                                 | 500                          | 1000               | 2000                         | kΩ        | 3              |

| Resistance between VM pin and VSS pin         | R <sub>VMS</sub>   | _                                                 | 10                           | 20                 | 40                           | kΩ        | 3              |

| CTL pin internal resistance                   | R <sub>CTL</sub>   | -                                                 | $R_{CTL} 	imes 0.5$          | R <sub>CTL</sub>   | $R_{CTL} 	imes 2.0$          | $M\Omega$ | 3              |

| Input Voltage                                 | •                  | 1                                                 |                              |                    | 1                            |           |                |

| Operation voltage between VDD pin and VSS pin | V <sub>DSOP1</sub> | _                                                 | 1.5                          | -                  | 6.5                          | V         | -              |

| Operation voltage between VDD pin and VM pin  | V <sub>DSOP2</sub> | _                                                 | 1.5                          | -                  | 28                           | V         | -              |

| CTL pin voltage "H"                           | V <sub>CTLH</sub>  | _                                                 | _                            | _                  | $V_{DD} 	imes 0.9$           | V         | 2              |

| CTL pin voltage "L"                           | VCTLL              | _                                                 | $V_{DD} 	imes 0.1$           | _                  | _                            | V         | 2              |

| Input Current                                 |                    |                                                   |                              | •                  |                              |           |                |

| Current consumption during operation          | I <sub>OPE</sub>   | -                                                 | -                            | 2.0                | 4.0                          | μA        | 3              |

| Current consumption during power-down         | I <sub>PDN</sub>   | -                                                 | -                            | _                  | 50                           | nA        | 3              |

| Current consumption during overdischarge      | I <sub>OPED</sub>  | -                                                 | -                            | _                  | 1.0                          | μA        | 3              |

| Current consumption during discharge          |                    |                                                   |                              | 2.0                |                              |           | _              |

| inhibition                                    | I <sub>OPEC</sub>  | _                                                 | _                            | 2.0                | 4.0                          | μA        | 3              |

| Output Resistance                             |                    |                                                   |                              |                    |                              |           |                |

| CO pin resistance "H"                         | R <sub>COH</sub>   | _                                                 | 5                            | 10                 | 20                           | kΩ        | 4              |

| CO pin resistance "L"                         | R <sub>COL</sub>   | _                                                 | 5                            | 10                 | 20                           | kΩ        | 4              |

| DO pin resistance "H"                         | R <sub>DOH</sub>   | _                                                 | 5                            | 10                 | 20                           | kΩ        | 4              |

| DO pin resistance "L"                         | R <sub>DOL</sub>   | _                                                 | 5                            | 10                 | 20                           | kΩ        | 4              |

| Delay Time                                    |                    | 1                                                 |                              | -                  |                              |           | _              |

| Overcharge detection delay time               | t <sub>cu</sub>    | _                                                 | $t_{\text{CU}} \times 0.8$   | tcu                | $t_{CU} 	imes 1.2$           | -         | 5              |

| Overdischarge detection delay time            | t <sub>DL</sub>    | _                                                 | $t_{\text{DL}} 	imes 0.8$    | t <sub>DL</sub>    | $t_{DL} 	imes 1.2$           | -         | 5              |

| Discharge overcurrent detection delay time    | t <sub>DIOV</sub>  | _                                                 | $t_{\text{DIOV}} 	imes 0.8$  | t <sub>DIOV</sub>  | $t_{\text{DIOV}} 	imes 1.2$  | -         | 5              |

| Load short-circuiting detection delay time    | t <sub>SHORT</sub> | _                                                 | $t_{\text{SHORT}} 	imes 0.7$ | t <sub>SHORT</sub> | $t_{\text{SHORT}} 	imes 1.3$ | -         | 5              |

| Charge overcurrent detection delay time       | t <sub>CIOV</sub>  | _                                                 | $t_{CIOV} 	imes 0.8$         | t <sub>CIOV</sub>  | $t_{CIOV} 	imes 1.2$         | -         | 5              |

| Discharge inhibition delay time               | t <sub>CTL</sub>   | _                                                 | $t_{\text{CTL}} 	imes 0.8$   | t <sub>CTL</sub>   | $t_{\text{CTL}} 	imes 1.2$   |           | 5              |

\*1. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

# BATTERY PROTECTION IC WITH DISCHARGE CONTROL FUNCTION FOR 1-CELL PACK S-8250A Series

Rev.1.3\_02

### 2. Ta = $-40^{\circ}$ C to $+85^{\circ}$ C<sup>\*1</sup>

| 2. Ta = -40°C to +85°C '                         |                    | Table 9                                      | (Ta = –40°C t∉               | o +85°C           | <sup>*1</sup> unless otherw | ise sp    | ecified         |

|--------------------------------------------------|--------------------|----------------------------------------------|------------------------------|-------------------|-----------------------------|-----------|-----------------|

| Item                                             | Symbol             | Condition                                    | Min.                         | Тур.              | Max.                        | Unit      | Test<br>Circuit |

| Detection Voltage                                |                    |                                              |                              | 1                 |                             |           |                 |

| Overcharge detection voltage                     | Vcu                | _                                            | $V_{CU} - 0.045$             | V <sub>CU</sub>   | $V_{CU} + 0.030$            | V         | 1               |

|                                                  | V                  | $V_{CL} \neq V_{CU}$                         | $V_{CL} - 0.070$             | V <sub>CL</sub>   | $V_{CL} + 0.040$            | V         | 1               |

| Overcharge release voltage                       | V <sub>CL</sub>    | $V_{CL} = V_{CU}$                            | $V_{CL}-0.050$               | V <sub>CL</sub>   | $V_{CL} + 0.030$            | V         | 1               |

| Overdischarge detection voltage                  | V <sub>DL</sub>    | -                                            | $V_{\text{DL}}-0.090$        | V <sub>DL</sub>   | $V_{DL} + 0.060$            | V         | 2               |

| Overdischarge release veltage                    | V <sub>DU</sub>    | $V_{DL} \neq V_{DU}$                         | $V_{\text{DU}}-0.140$        | V <sub>DU</sub>   | $V_{DU} + 0.110$            | V         | 2               |

| Overdischarge release voltage                    | VDU                | $V_{DL} = V_{DU}$                            | $V_{\text{DU}}-0.090$        | V <sub>DU</sub>   | $V_{DU} + 0.060$            | V         | 2               |

|                                                  |                    | V <sub>DD</sub> = 3.0 V                      | _                            | VDIOV             | _                           | V         | 2               |

| Discharge overcurrent detection voltage*2        | VDIOV              | V <sub>DD</sub> = 3.4 V                      | -                            | VDIOV             | _                           | V         | 2               |

|                                                  |                    | V <sub>DD</sub> = 4.0 V                      | _                            | VDIOV             | _                           | V         | 2               |

| Load short-circuiting detection voltage          | VSHORT             | -                                            | $V_{\text{SHORT}} - 0.050$   | VSHORT            | $V_{\text{SHORT}} + 0.050$  | V         | 2               |

| Charge overcurrent detection voltage             | VCIOV              | -                                            | $V_{\text{CIOV}}-0.015$      | VCIOV             | $V_{\text{CIOV}} + 0.015$   | V         | 2               |

| 0 V Battery Charge Function                      | 1                  | 1                                            | •                            | 1                 | 1                           |           | I               |

| 0 V battery charge starting charger voltage      | V <sub>0CHA</sub>  | 0 V battery charge<br>function "available"   | 0.00                         | 0.70              | 1.50                        | V         | 2               |

| 0 V battery charge inhibition battery voltage    | Voinh              | 0 V battery charge<br>function "unavailable" | 0.70                         | 1.25              | 1.80                        | V         | 2               |

| Internal Resistance                              |                    |                                              | -                            |                   |                             |           |                 |

| Resistance between VM pin and VDD pin            | RVMD               | -                                            | 250                          | 1000              | 3000                        | kΩ        | 3               |

| Resistance between VM pin and VSS pin            | R <sub>VMS</sub>   | -                                            | 7.2                          | 20                | 44                          | kΩ        | 3               |

| CTL pin internal resistance                      | RCTL               | -                                            | $R_{CTL} 	imes 0.25$         | R <sub>CTL</sub>  | $R_{CTL} 	imes 3.0$         | $M\Omega$ | 3               |

| Input Voltage                                    |                    |                                              | 1                            |                   | I                           | 1         |                 |

| Operation voltage between VDD pin and<br>VSS pin | V <sub>DSOP1</sub> | _                                            | 1.5                          | _                 | 6.5                         | V         | _               |

| Operation voltage between VDD pin and<br>VM pin  | V <sub>DSOP2</sub> | _                                            | 1.5                          | -                 | 28                          | V         | _               |

| CTL pin voltage "H"                              | VCTLH              | —                                            | _                            | _                 | $V_{\text{DD}} \times 0.95$ | V         | 2               |

| CTL pin voltage "L"                              | V <sub>CTLL</sub>  | _                                            | $V_{\text{DD}} \times 0.05$  | _                 | _                           | V         | 2               |

| Input Current                                    |                    |                                              |                              |                   |                             |           |                 |

| Current consumption during operation             | I <sub>OPE</sub>   | -                                            | _                            | 2.0               | 4.5                         | μA        | 3               |

| Current consumption during power-down            | IPDN               | -                                            | -                            | -                 | 100                         | nA        | 3               |

| Current consumption during overdischarge         | IOPED              | -                                            | -                            | -                 | 2.0                         | μA        | 3               |

| Current consumption during discharge inhibition  | I <sub>OPEC</sub>  | -                                            | -                            | 2.0               | 4.5                         | μA        | 3               |

| Output Resistance                                |                    |                                              | -                            |                   |                             |           |                 |

| CO pin resistance "H"                            | RCOH               | -                                            | 2.5                          | 10                | 30                          | kΩ        | 4               |

| CO pin resistance "L"                            | R <sub>COL</sub>   | -                                            | 2.5                          | 10                | 30                          | kΩ        | 4               |

| DO pin resistance "H"                            | RDOH               | -                                            | 2.5                          | 10                | 30                          | kΩ        | 4               |

| DO pin resistance "L"                            | R <sub>DOL</sub>   | -                                            | 2.5                          | 10                | 30                          | kΩ        | 4               |

| Delay Time                                       | 1                  | I                                            | 1                            |                   | Γ                           | 1         |                 |

| Overcharge detection delay time                  | t <sub>CU</sub>    | _                                            | $t_{CU} 	imes 0.6$           | t <sub>cu</sub>   | $t_{CU} 	imes 1.6$          | _         | 5               |

| Overdischarge detection delay time               | t <sub>DL</sub>    | -                                            | $t_{\text{DL}} \times 0.6$   | t <sub>DL</sub>   | $t_{DL} 	imes 1.6$          | -         | 5               |

| Discharge overcurrent detection delay time       | t <sub>DIOV</sub>  | _                                            | $t_{\text{DIOV}} 	imes 0.6$  | t <sub>DIOV</sub> | $t_{\text{DIOV}} 	imes 1.6$ |           | 5               |

| Load short-circuiting detection delay time       | <b>t</b> SHORT     | _                                            | $t_{\text{SHORT}} 	imes 0.5$ | <b>t</b> SHORT    | $t_{SHORT} 	imes 1.7$       | _         | 5               |

| Charge overcurrent detection delay time          | t <sub>CIOV</sub>  | _                                            | $t_{CIOV} 	imes 0.6$         | t <sub>CIOV</sub> | $t_{CIOV} 	imes 1.6$        | _         | 5               |

| Discharge inhibition delay time                  | t <sub>CTL</sub>   | -                                            | $t_{\text{CTL}} 	imes 0.6$   | t <sub>CTL</sub>  | $t_{\text{CTL}} 	imes 1.6$  | -         | 5               |

\*1. Since products are not screened at high and low temperature, the specification for this temperature range is guaranteed by design, not tested in production.

\*2. The temperature characteristics of V<sub>DIOV</sub> is determined depending on the setting of V<sub>DIOV</sub>, and accords closely with the temperature characteristics of ON resistance of the charge-discharge control FET. Refer to "2. 5 V<sub>DIOV</sub> vs. Ta" in "■ Characteristics (Typical Data)" for details.

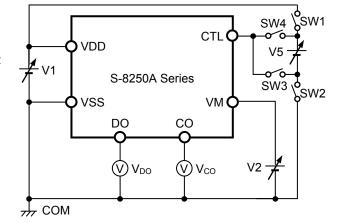

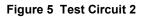

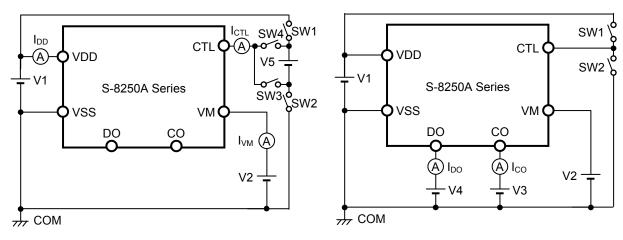

### Test Circuits

When CTL pin control logic is active "H", SW1 and SW3 are turned off, SW2 and SW4 are turned on. When CTL pin control logic is active "L", SW1 and SW3 are turned on, SW2 and SW4 are turned off.

Caution Unless otherwise specified, the output voltage levels "H" and "L" at CO pin ( $V_{CO}$ ) and DO pin ( $V_{DO}$ ) are judged by the threshold voltage (1.0 V) of the N-channel FET. Judge the CO pin level with respect to  $V_{VM}$  and the DO pin level with respect to  $V_{SS}$ .

# 1. Overcharge detection voltage, overcharge release voltage (Test circuit 1)

Overcharge detection voltage ( $V_{CU}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "H" to "L" when the voltage V1 is gradually increased from the starting conditions of V1 = 3.4 V. Overcharge release voltage ( $V_{CL}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "L" to "H" when the voltage V1 is then gradually decreased. Overcharge hysteresis voltage ( $V_{HC}$ ) is defined as the difference between  $V_{CU}$  and  $V_{CL}$ .

# 2. Overdischarge detection voltage, overdischarge release voltage (Test circuit 2)

Overdischarge detection voltage ( $V_{DL}$ ) is defined as the voltage V1 at which  $V_{DO}$  goes from "H" to "L" when the voltage V1 is gradually decreased from the starting conditions of V1 = 3.4 V, V2 = V5 = 0 V. Overdischarge release voltage ( $V_{DU}$ ) is defined as the voltage V1 at which  $V_{DO}$  goes from "L" to "H" when the voltage V1 is then gradually increased from the starting condition of V2 = 0.02 V. Overdischarge hysteresis voltage ( $V_{HD}$ ) is defined as the difference between  $V_{DU}$  and  $V_{DL}$ .

# 3. Discharge overcurrent detection voltage (Test circuit 2)

Discharge overcurrent detection voltage ( $V_{DIOV}$ ) is defined as the voltage V2 whose delay time for changing  $V_{DO}$  from "H" to "L" is discharge overcurrent detection delay time ( $t_{DIOV}$ ) when the voltage V2 is increased from the starting conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 4. Load short-circuiting detection voltage (Test circuit 2)

Load short-circuiting detection voltage ( $V_{SHORT}$ ) is defined as the voltage V2 whose delay time for changing  $V_{DO}$  from "H" to "L" is load short-circuiting detection delay time ( $t_{SHORT}$ ) when the voltage V2 is increased from the starting conditions of V1 = 3.4 V, V2 = V5 = 0 V.

### 5. Charge overcurrent detection voltage (Test circuit 2)

Charge overcurrent detection voltage ( $V_{CIOV}$ ) is defined as the voltage V2 whose delay time for changing  $V_{CO}$  from "H" to "L" is charge overcurrent detection delay time ( $t_{CIOV}$ ) when the voltage V2 is decreased from the starting conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 6. Current consumption during operation (Test circuit 3)

The current consumption during operation ( $I_{OPE}$ ) is the current that flows through the VDD pin ( $I_{DD}$ ) under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 7. Current consumption during power-down, current consumption during overdischarge (Test circuit 3)

### 7.1 With power-down function

The current consumption during power-down ( $I_{PDN}$ ) is  $I_{DD}$  under the set conditions of V1 = V2 = 1.5 V, V5 = 0 V.

### 7. 2 Without power-down function

The current consumption during overdischarge ( $I_{OPED}$ ) is  $I_{DD}$  under the set conditions of V1 = V2 = 1.5 V, V5 = 0 V.

# 8. Current consumption during discharge inhibition (Test circuit 3)

### 8.1 CTL pin control logic active "L" and CTL pin internal resistance connection "pull-up"

Current consumption during discharge inhibition ( $I_{OPEC}$ ) is the difference of absolute value between  $I_{DD}$  and  $I_{CTL}$  under the set condition of V1 = V2 = V5 = 3.4 V.

#### 8.2 Other function combinations

Current consumption during discharge inhibition ( $I_{OPEC}$ ) is  $I_{DD}$  under the set condition of V1 = V2 = V5 = 3.4 V.

# 9. Resistance between VM pin and VDD pin (Test circuit 3)

Resistance between VM pin and VDD pin is  $R_{VMD}$  under the set conditions of V1 = 1.8 V, V2 = V5 = 0 V.

### Resistance between VM pin and VSS pin (Release condition of discharge overcurrent status "load disconnection") (Test circuit 3)

Resistance between VM pin and VSS pin is  $R_{VMS}$  under the set conditions of V1 = 3.4 V, V2 = 1.0 V, V5 = 0 V.

### 11. CTL pin internal resistance (Test circuit 3)

11. 1 CTL pin control logic active "H" and CTL pin internal resistance connection "pull-down"

Resistance between CTL pin and VSS pin is  $R_{CTL}$  under the set conditions of V1 = V5 = 3.4 V, V2 = 0 V.

11. 2 CTL pin control logic active "L" and CTL pin internal resistance connection "pull-up"

Resistance between CTL pin and VDD pin is R<sub>CTL</sub> under the set conditions of V1 = V5 = 3.4 V, V2 = 0 V.

11.3 CTL pin control logic active "L" and CTL pin internal resistance connection "pull-down"

Resistance between CTL pin and VSS pin is  $R_{CTL}$  under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

#### 12. CO pin resistance "H" (Test circuit 4)

The CO pin resistance "H" ( $R_{COH}$ ) is the resistance between VDD pin and CO pin under the set conditions of V1 = 3.4 V, V2 = 0 V, V3 = 3.0 V.

#### 13. CO pin resistance "L" (Test circuit 4)

The CO pin resistance "L" ( $R_{COL}$ ) is the resistance between VM pin and CO pin under the set conditions of V1 = 4.6 V, V2 = 0 V, V3 = 0.4 V.

### 14. DO pin resistance "H" (Test circuit 4)

The DO pin resistance "H" ( $R_{DOH}$ ) is the resistance between VDD pin and DO pin under the set conditions of V1 = 3.4 V, V2 = 0 V, V4 = 3.0 V.

### 15. DO pin resistance "L" (Test circuit 4)

The DO pin resistance "L" ( $R_{DOL}$ ) is the resistance between VSS pin and DO pin under the set conditions of V1 = 1.8 V, V2 = 0 V, V4 = 0.4 V.

### 16. CTL pin voltage "H", CTL pin voltage "L" (Test circuit 2)

### 16. 1 CTL pin control logic active "H"

The CTL pin voltage "H" ( $V_{CTLH}$ ) is defined as the voltage V5 at which  $V_{DO}$  goes from "H" to "L" when the voltage V5 is gradually increased under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V. After that, the CTL pin voltage "L" ( $V_{CTLL}$ ) is defined as the voltage V5 at which  $V_{DO}$  goes from "L" to "H" after V5 is gradually decreased.

### 16. 2 CTL pin control logic active "L"

The CTL pin voltage "L" (V<sub>CTLL</sub>) is defined as the voltage difference between the voltage V5 and the voltage V1 (V1 – V5) at which V<sub>DO</sub> goes from "H" to "L" when the voltage V5 is gradually increased under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V. After that, the CTL pin voltage "H" (V<sub>CTLH</sub>) is defined as the voltage difference between V1 – V5 at which V<sub>DO</sub> goes from "L" to "H" after V5 is gradually decreased.

## 17. Overcharge detection delay time (Test circuit 5)

The overcharge detection delay time ( $t_{CU}$ ) is the time needed for  $V_{CO}$  to go to "L" after the voltage V1 increases and exceeds  $V_{CU}$  under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

### 18. Overdischarge detection delay time (Test circuit 5)

The overdischarge detection delay time ( $t_{DL}$ ) is the time needed for  $V_{DO}$  to go to "L" after the voltage V1 decreases and falls below  $V_{DL}$  under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 19. Discharge overcurrent detection delay time (Test circuit 5)

$t_{DIOV}$  is the time needed for V<sub>DO</sub> to go to "L" after the voltage V2 increases and exceeds V<sub>DIOV</sub> under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 20. Load short-circuiting detection delay time (Test circuit 5)

$t_{SHORT}$  is the time needed for V<sub>DO</sub> to go to "L" after the voltage V2 increases and exceeds V<sub>SHORT</sub> under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 21. Charge overcurrent detection delay time (Test circuit 5)

$t_{CIOV}$  is the time needed for V<sub>CO</sub> to go to "L" after the voltage V2 decreases and falls below V<sub>CIOV</sub> under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 22. Discharge inhibition delay time (Test circuit 5)

### 22.1 CTL pin control logic active "H"

Discharge inhibition delay time ( $t_{CTL}$ ) is the time needed for  $V_{DO}$  to go to "L" after the voltage V5 increases and exceeds  $V_{CTLH}$  under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

### 22. 2 CTL pin control logic active "L"

Discharge inhibition delay time ( $t_{CTL}$ ) is the time needed for  $V_{DO}$  to go to "L" after the voltage V5 increases and V1 – V5 falls below  $V_{CTLL}$  under the set conditions of V1 = 3.4 V, V2 = V5 = 0 V.

# 23. 0 V battery charge starting charger voltage (0 V battery charge function "available") (Test circuit 2)

The 0 V battery charge starting charger voltage ( $V_{0CHA}$ ) is defined as absolute value of the voltage V2 at which  $V_{CO}$  goes to "H" ( $V_{CO} = V_{DD}$ ) when the voltage V2 is gradually decreased under the set condition of V1 = V2 = V5 = 0 V.

# 24. 0 V battery charge inhibition battery voltage (0 V battery charge function "unavailable") (Test circuit 2)

The 0 V battery charge inhibition battery voltage ( $V_{0INH}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes to "H" ( $V_{CO}$  =  $V_{DD}$ ) when the voltage V1 is gradually increased under the set conditions of V1 = V5 = 0 V, V2 = -2.0 V.

$(V) V_{DO}$

Rev.1.3\_02

J COM

Figure 4 Test Circuit 1

$(V) V_{co}$

Figure 6 Test Circuit 3

Figure 8 Test Circuit 5

Figure 7 Test Circuit 4

### Operation

**Remark** Refer to "

Battery Protection IC Connection Example".

### 1. Normal status

The S-8250A Series monitors the voltage of the battery connected between the VDD pin and VSS pin, the voltage between the VM pin and VSS pin and the voltage between the CTL pin and VSS pin to control charging and discharging.

### 1.1 CTL pin control logic active "H"

When the battery voltage is in the range from the overdischarge detection voltage ( $V_{DL}$ ) to the overcharge detection voltage ( $V_{CU}$ ), and the VM pin voltage is in the range from the charge overcurrent detection voltage ( $V_{CIOV}$ ) to the discharge overcurrent detection voltage ( $V_{DIOV}$ ), the S-8250A Series turns both the charge and discharge control FETs on if the CTL pin voltage is equal to or lower than the CTL pin voltage "L" ( $V_{CTLL}$ ). This condition is called the normal status, and in this condition charging and discharging can be carried out freely. The resistance between the VM pin and VDD pin ( $R_{VMD}$ ) and the resistance between the VM pin and VSS pin ( $R_{VMS}$ ) are not connected in the normal status.

### 1. 2 CTL pin control logic active "L"

When the battery voltage is in the range from the overdischarge detection voltage ( $V_{DL}$ ) to the overcharge detection voltage ( $V_{CU}$ ), and the VM pin voltage is in the range from the charge overcurrent detection voltage ( $V_{CIOV}$ ) to the discharge overcurrent detection voltage ( $V_{DIOV}$ ), the S-8250A Series turns both the charge and discharge control FETs on if the CTL pin voltage is equal to or higher than the CTL pin voltage "H" ( $V_{CTLH}$ ). This condition is called the normal status, and in this condition charging and discharging can be carried out freely. The resistance between the VM pin and VDD pin ( $R_{VMD}$ ) and the resistance between the VM pin and VSS pin ( $R_{VMS}$ ) are not connected in the normal status.

Caution When the battery is connected for the first time, the S-8250A Series may not be in the normal status. In this case, short the VM pin and VSS pin, or set the VM pin voltage at the level of V<sub>CIOV</sub> or more and at the level of V<sub>DIOV</sub> or less by connecting the charger. The S-8250A Series then becomes the normal status.

### 2. Overcharge status

### 2.1 $V_{CL} \neq V_{CU}$ (Product in which overcharge release voltage differs from overcharge detection voltage)

When the battery voltage becomes higher than V<sub>CU</sub> during charging in the normal status and detection continues for the overcharge detection delay time (t<sub>CU</sub>) or longer, the S-8250A Series turns the charge control FET off to stop charging. This condition is called the overcharge status.

The overcharge status is released in the following two cases.

- (1) In the case that the VM pin voltage is lower than  $V_{DIOV}$ , the S-8250A Series releases the overcharge status when the battery voltage falls below overcharge release voltage ( $V_{CL}$ ).

- (2) In the case that the VM pin voltage is equal to or higher than  $V_{DIOV}$ , the S-8250A Series releases the overcharge status when the battery voltage falls below V<sub>CU</sub>.

When the discharge is started by connecting a load after the overcharge detection, the VM pin voltage rises by the V<sub>f</sub> voltage of the parasitic diode than the VSS pin voltage, because the discharge current flows through the parasitic diode in the charge control FET. If this VM pin voltage is equal to or higher than V<sub>DIOV</sub>, the S-8250A Series releases the overcharge status when the battery voltage is equal to or lower than  $V_{CU}$ .

Caution If the battery is charged to a voltage higher than  $V_{CU}$  and the battery voltage does not fall below  $V_{CU}$ even when a heavy load is connected, discharge overcurrent detection and load short-circuiting detection do not function until the battery voltage falls below  $V_{CU}$ . Since an actual battery has an internal impedance of tens of m $\Omega$ , the battery voltage drops immediately after a heavy load that causes overcurrent is connected, and discharge overcurrent detection and load short-circuiting detection function.

### 2. 2 $V_{CL}$ = $V_{CU}$ (Product in which overcharge release voltage is the same as overcharge detection voltage)

When the battery voltage becomes higher than V<sub>CU</sub> during charging in the normal status and detection continues for the overcharge detection delay time (t<sub>CU</sub>) or longer, the S-8250A Series turns the charge control FET off to stop charging. This condition is called the overcharge status.

In the case that the VM pin voltage is higher than 0 V typ., the S-8250A Series releases the overcharge status when the battery voltage falls below  $V_{CU}$ .

- Caution 1. If the battery is charged to a voltage higher than  $V_{CU}$  and the battery voltage does not fall below V<sub>CU</sub> even when a heavy load is connected, discharge overcurrent detection and load shortcircuiting detection do not function until the battery voltage falls below V<sub>cu</sub>. Since an actual battery has an internal impedance of tens of m $\Omega$ , the battery voltage drops immediately after a heavy load that causes overcurrent is connected, and discharge overcurrent detection and load short-circuiting detection function.

- 2. When a charger is connected after overcharge detection, the overcharge status is not released even if the battery voltage is below VcL. The overcharge status is released when the VM pin voltage goes over 0 V typ. by removing the charger.

### 3. Overdischarge status

When the battery voltage falls below  $V_{DL}$  during discharging in the normal status and the condition continues for the overdischarge detection delay time ( $t_{DL}$ ) or longer, the S-8250A Series turns the discharge control FET off to stop discharging. This condition is called the overdischarge status.

Under the overdischarge status, VDD pin and VM pin are shorted by  $R_{VMD}$  in the S-8250A Series. The VM pin voltage is pulled up by  $R_{VMD}$ .

R<sub>VMS</sub> is not connected in the overdischarge status.

#### 3.1 With power-down function

Under the overdischarge status, when voltage difference between VDD pin and VM pin is 0.8 V typ. or lower, the power-down function works and the current consumption is reduced to the current consumption during power-down ( $I_{PDN}$ ). By connecting a battery charger, the power-down function is released when the VM pin voltage is 0.7 V typ. or lower.

- When a battery is not connected to a charger and the VM pin voltage ≥0.7 V typ., the S-8250A Series maintains the overdischarge status even when the battery voltage reaches V<sub>DU</sub> or higher.

- When a battery is connected to a charger and 0.7 V typ. > the VM pin voltage > 0 V typ., the battery voltage reaches  $V_{DU}$  or higher and the S-8250A Series releases the overdischarge status.

- When a battery is connected to a charger and 0 V typ. ≥ the VM pin voltage, the battery voltage reaches V<sub>DL</sub> or higher and the S-8250A Series releases the overdischarge status.

### 3. 2 Without power-down function

The power-down function does not work even when voltage difference between VDD pin and VM pin is 0.8 V typ. or lower.

- When a battery is not connected to a charger and the VM pin voltage  $\ge 0.7$  V typ., the battery voltage reaches V<sub>DU</sub> or higher and the S-8250A Series releases the overdischarge status.

- When a battery is connected to a charger and 0.7 V typ. > the VM pin voltage > 0 V typ., the battery voltage reaches  $V_{DU}$  or higher and the S-8250A Series releases the overdischarge status.

- When a battery is connected to a charger and 0 V typ. ≥ the VM pin voltage, the battery voltage reaches V<sub>DL</sub> or higher and the S-8250A Series releases the overdischarge status.

### 4. Discharge overcurrent status (Discharge overcurrent, load short-circuiting)

When a battery in the normal status is in the status where the VM pin voltage is equal to or higher than  $V_{DIOV}$  because the discharge current is equal to or higher than the specified value and the status lasts for the discharge overcurrent detection delay time ( $t_{DIOV}$ ) or longer, the discharge control FET is turned off and discharging is stopped. This status is called the discharge overcurrent status.

### 4. 1 Release condition of discharge overcurrent status "load disconnection"

In the discharge overcurrent status, the VM pin and VSS pin are shorted by  $R_{VMS}$  in the S-8250A Series. However, the VM pin voltage is the VDD pin voltage due to the load as long as the load is connected. When the load is disconnected, the VM pin voltage returns to the VSS pin voltage. If the VM pin voltage returns to  $V_{DIOV}$  or lower, the S-8250A Series releases the discharge overcurrent status.

$R_{\text{VMD}}$  is not connected in the discharge overcurrent status.

### 4. 2 Release condition of discharge overcurrent status "charger connection"

In the discharge overcurrent status, the VM pin and VDD pin are shorted by R<sub>VMD</sub> in the S-8250A Series.

If the VM pin voltage returns to  $V_{DIOV}$  or lower by connecting a charger, the S-8250A Series releases the discharge overcurrent status.

R<sub>VMS</sub> is not connected in the discharge overcurrent status.

### 5. Charge overcurrent status

When a battery in the normal status is in the status where the VM pin voltage is equal to or lower than  $V_{CIOV}$  because the charge current is equal to or higher than the specified value and the status lasts for the charge overcurrent detection delay time ( $t_{CIOV}$ ) or longer, the charge control FET is turned off and charging is stopped. This status is called the charge overcurrent status.

The S-8250A Series releases the charge overcurrent status when the VM pin voltage returns to 0 V typ. or higher by removing the charger.

The charge overcurrent detection does not function in the overdischarge status and the discharge inhibition status.

### 6. Discharge inhibition status

#### 6. 1 CTL pin control logic active "H"

When a battery in the normal status is in the status where CTL pin voltage is equal to or higher than CTL pin voltage "H" ( $V_{CTLH}$ ) and the status lasts for discharge inhibition delay time ( $t_{CTL}$ ) or longer, the discharge control FET is turned off and discharging is stopped. This status is called the discharge inhibition status.

#### 6. 1. 1 Discharge inhibition status latch function "available"

If CTL pin voltage is equal to or lower than CTL pin voltage "L" ( $V_{CTLL}$ ), the S-8250A Series releases discharge inhibition status when the VM pin voltage becomes equal to or lower than  $V_{DIOV}$  by connecting a charger.

### 6. 1. 2 Discharge inhibition status latch function "unavailable"

The S-8250A Series releases discharge inhibition status when the CTL pin voltage becomes equal to or lower than  $V_{\text{CTLL}}.$

#### 6. 2 CTL pin control logic active "L"

When a battery in the normal status is in the status where CTL pin voltage is equal to or lower than CTL pin voltage "L" ( $V_{CTLL}$ ) and the status lasts for discharge inhibition delay time ( $t_{CTL}$ ) or longer, the discharge control FET is turned off and discharging is stopped. This status is called the discharge inhibition status.

#### 6. 2. 1 Discharge inhibition status latch function "available"

If CTL pin voltage is equal to or higher than CTL pin voltage "H" ( $V_{CTLH}$ ), the S-8250A Series releases discharge inhibition status when the VM pin voltage becomes equal to or lower than  $V_{DIOV}$  by connecting a charger.

#### 6. 2. 2 Discharge inhibition status latch function "unavailable"

The S-8250A Series releases discharge inhibition status when the CTL pin voltage becomes equal to or higher than  $V_{\text{CTLH}}$ .

In discharge inhibition status, if the battery voltage exceeds  $V_{CU}$  by connecting a charger, the S-8250A Series releases discharge inhibition status.

The CTL pin is shorted to the VDD pin or VSS pin by the CTL pin internal resistance ( $R_{CTL}$ ) in the S-8250A Series. When the voltage between the VDD pin and VM pin is 0.8 V typ. or lower in the overdischarge status,  $R_{CTL}$  is disconnected and the input and output current to the CTL pin is cut off.

The discharge control by the CTL pin does not function in the overcharge status and the charge overcurrent status. In the discharge inhibition status, the VM pin and VDD pin are shorted by  $R_{VMD}$  in the S-8250A Series.

### 7. 0 V battery charge function "available"

This function is used to recharge a connected battery whose voltage is 0 V due to self-discharge. When the 0 V battery charge starting charger voltage ( $V_{0CHA}$ ) or a higher voltage is applied between the EB+ pin and EB- pin by connecting a charger, the charge control FET gate is fixed to the VDD pin voltage. When the voltage between the gate and source of the charge control FET becomes equal to or higher than the threshold voltage due to the charger voltage, the charge control FET is turned on to start charging. At this time, the discharge control FET is off and the charge current flows through the internal parasitic diode in the discharge control FET. When the battery voltage becomes equal to or higher than  $V_{DU}$ , the S-8250A Series enters the normal status.

- Caution 1. Some battery providers do not recommend charging for a completely self-discharged battery. Please ask the battery provider to determine whether to enable or inhibit the 0 V battery charge function.

- 2. The 0 V battery charge function has higher priority than the charge overcurrent detection function. Consequently, a product in which use of the 0 V battery charge function is enabled charges a battery forcibly and the charge overcurrent cannot be detected when the battery voltage is lower than  $V_{DL}$ .

### 8. 0 V battery charge function "unavailable"

This function inhibits recharging when a battery that is internally short-circuited (0 V battery) is connected. When the battery voltage is the 0 V battery charge inhibition battery voltage ( $V_{0INH}$ ) or lower, the charge control FET gate is fixed to the EB- pin voltage to inhibit charging. When the battery voltage is  $V_{0INH}$  or higher, charging can be performed.

Caution Some battery providers do not recommend charging for a completely self-discharged battery. Please ask the battery provider to determine whether to enable or inhibit the 0 V battery charge function.

### 9. Delay circuit

The detection delay times are determined by dividing a clock of approximately 4 kHz by the counter.

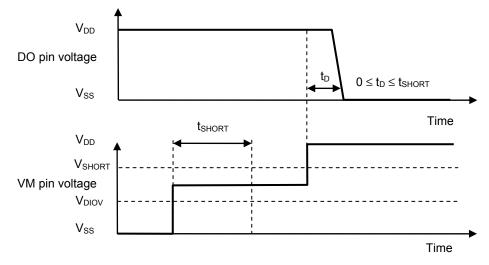

**Remark**  $t_{DIOV}$  and  $t_{SHORT}$  start when  $V_{DIOV}$  is detected. When  $V_{SHORT}$  is detected over  $t_{SHORT}$  after  $V_{DIOV}$ , the S-8250A Series turns the discharge control FET off within  $t_{SHORT}$  from the time of detecting  $V_{SHORT}$ .

Figure 9

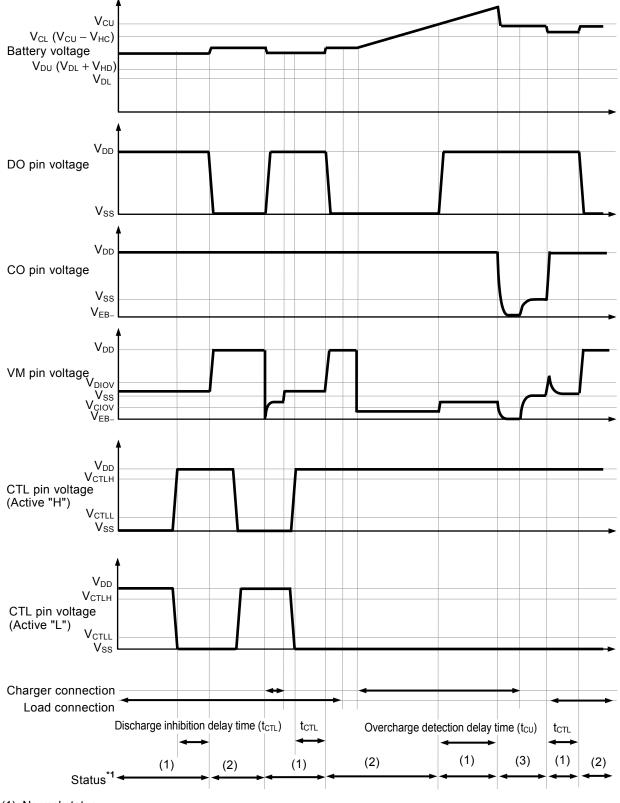

## ■ Timing Chart

Rev.1.3\_02

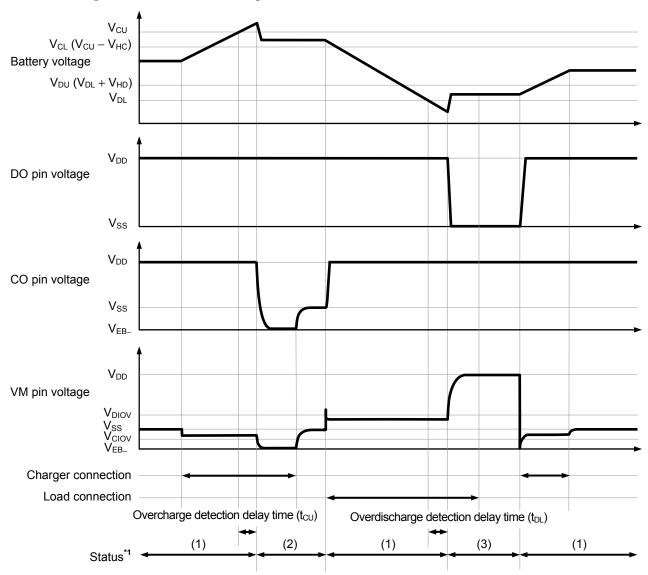

1. Overcharge detection, overdischarge detection

\*1. (1): Normal status

(2): Overcharge status

(3): Overdischarge status

Remark The charger is assumed to charge with a constant current.

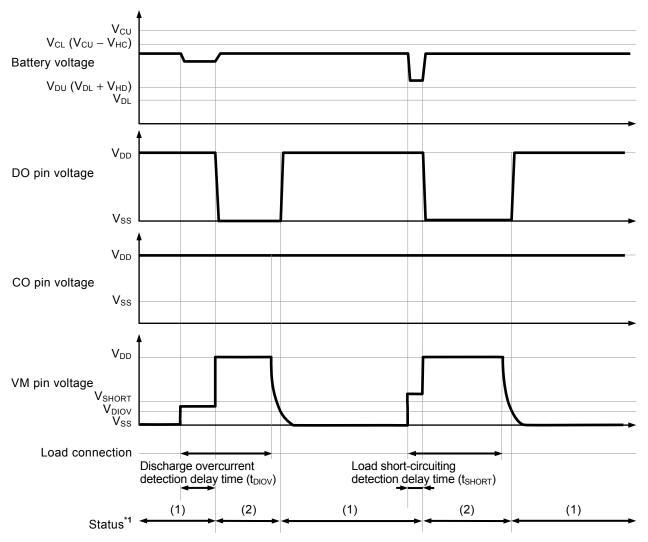

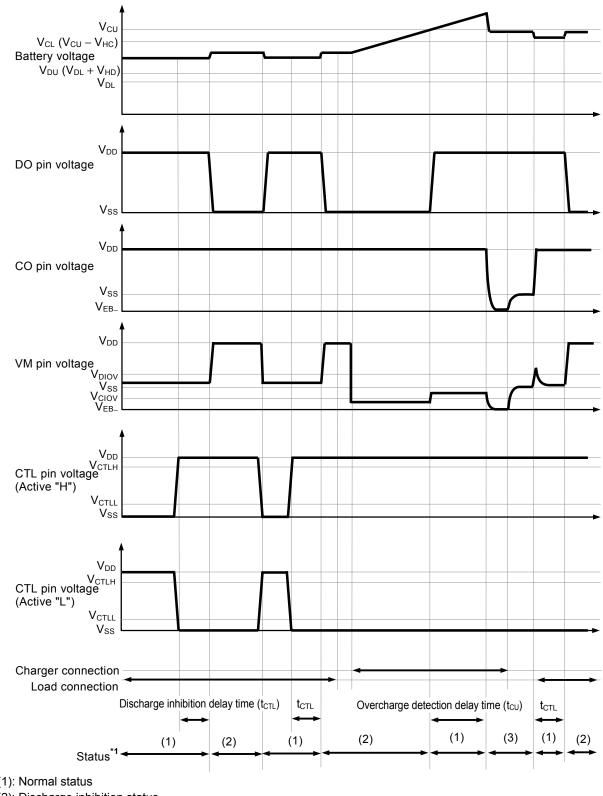

### 2. Discharge overcurrent detection

### 2. 1 Release condition of discharge overcurrent status "load disconnection"

\*1. (1): Normal status

(2): Discharge overcurrent status

**Remark** The charger is assumed to charge with a constant current.

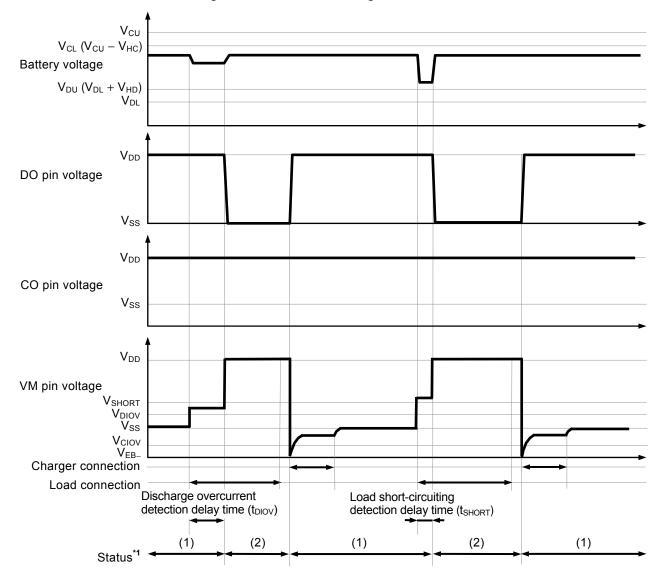

### 2. 2 Release condition of discharge overcurrent status "charger connection"

\*1. (1): Normal status

Rev.1.3\_02

(2): Discharge overcurrent status

Remark The charger is assumed to charge with a constant current.

### $V_{\text{CU}}$ $\begin{array}{c} V_{CL} \left( V_{CU} - V_{HC} \right) \\ Battery \ voltage \end{array}$ $V_{DU} (V_{DL} + V_{HD})$ $V_{\mathsf{DL}}$ V<sub>DD</sub> DO pin voltage $V_{\text{SS}}$ V<sub>DD</sub> CO pin voltage $V_{\text{SS}}$ $V_{EB_{-}}$ V<sub>DD</sub> VM pin voltage V<sub>SS</sub> V<sub>CIOV</sub> $V_{EB}$ Charger connection Load connection Overdischarge detection delay time $(\tilde{t}_{DL})$ Charge overcurrent detection Charge overcurrent detection delay time (t<sub>CIOV</sub>) delay time (t<sub>CIOV</sub>) (2) (1) (1) (1) (3) (2) Status<sup>\*1</sup>

### 3. Charge overcurrent detection

\*1. (1): Normal status

(2): Charge overcurrent status

(3): Overdischarge status

Remark The charger is assumed to charge with a constant current.

# 4. Discharge inhibition operation 4. 1 Discharge inhibition status latch function "available"

\*1. (1): Normal status

Rev.1.3\_02

(2): Discharge inhibition status

(3): Overcharge status

Remark The charger is assumed to charge with a constant current.

4. 2 Discharge inhibition status latch function "unavailable"

\*1. (1): Normal status

(2): Discharge inhibition status

(3): Overcharge status

Remark The charger is assumed to charge with a constant current.

Figure 15

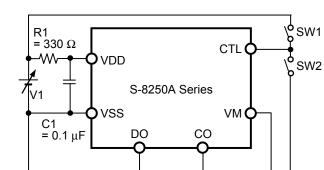

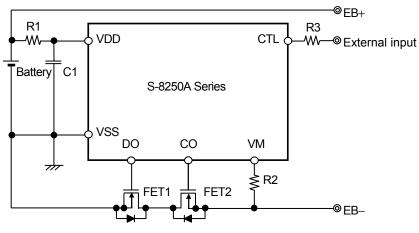

### Battery Protection IC Connection Example

### Figure 16

Table 10 Constants for External Components

| Symbol | Part                 | Purpose                                              | Min.     | Тур.   | Max.   | Remark                                                                                                                                          |

|--------|----------------------|------------------------------------------------------|----------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| FET1   | N-channel<br>MOS FET | Discharge control                                    | _        | _      | _      | Threshold voltage $\leq$ Overdischarge detection voltage <sup>*1</sup><br>Gate to source withstand voltage $\geq$ Charger voltage <sup>*2</sup> |

| FET2   | N-channel<br>MOS FET | Charge control                                       | _        | _      | _      | Threshold voltage $\leq$ Overdischarge detection voltage <sup>*1</sup><br>Gate to source withstand voltage $\geq$ Charger voltage <sup>*2</sup> |

| R1     | Resistor             | ESD protection,<br>For power fluctuation             | 150 Ω    | 330 Ω  | 510 Ω  | Resistance should be as small as possible to avoid worsening the overcharge detection accuracy due to current consumption. <sup>*3</sup>        |

| C1     | Capacitor            | For power fluctuation                                | 0.068 μF | 0.1 μF | 1.0 μF | Connect a capacitor of 0.068 $\mu$ F or higher between VDD pin and VSS pin. <sup>*4</sup>                                                       |

| R2     | Resistor             | Protection for reverse<br>connection of a<br>charger | 1 kΩ     | 2 kΩ   | 4 kΩ   | Select as large a resistance as possible to prevent current when a charger is connected in reverse. <sup>*5</sup>                               |

| R3     | Resistor             | ESD protection                                       | 1 kΩ     | _      | 10 kΩ  | Connect a resistor of 1 k $\Omega$ or more to R3 for ESD protection. <sup>*6</sup>                                                              |

\*1. If the threshold voltage of an FET is low, the FET may not cut the charge current. If an FET with a threshold voltage equal to or higher than the overdischarge detection voltage is used, discharging may be stopped before overdischarge is detected.

- \*2. If the withstand voltage between the gate and source is lower than the charger voltage, the FET may be destroyed.

- \*3. An accuracy of overcharge detection voltage is guaranteed by R1 = 330  $\Omega$ . Connecting resistors with other values worsen the accuracy. In case of connecting a larger resistor to R1, the voltage between the VDD pin and VSS pin may exceed the absolute maximum rating because the current flows to the S-8250A Series from the charger due to reverse connection of charger. Connect a resistor of 150  $\Omega$  or more to R1 for ESD protection.

- \*4. When connecting a resistor less than 150  $\Omega$  to R1 or a capacitor less than 0.068  $\mu$ F to C1, the S-8250A Series may malfunction when power dissipation is largely fluctuated.

- \*5. When a resistor more than 4 k $\Omega$  is connected to R2, the charge current may not be cut.

- \*6. If the resistance of R3 is too large, the conditions of  $V_{CTL} \ge V_{CTLH}$ ,  $V_{CTL} \le V_{CTLL}$  may not be met.

Caution 1. The above constants may be changed without notice.

2. It has not been confirmed whether the operation is normal or not in circuits other than the above example of connection. In addition, the example of connection shown above and the constant do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constant.