# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### S26KL512S/S26KS512S S26KL256S/S26KS256S S26KL128S/S26KS128S

# 512 Mbit (64 Mbyte)/256 Mbit (32 Mbyte)/ 128 Mbit (16 Mbyte), 1.8V/3.0V HyperFlash™ Family

# Features

- 3.0V I/O, 11 bus signals

Single ended clock

- 1.8V I/O, 12 bus signals

Differential clock (CK, CK#)

- Chip Select (CS#)

- 8-bit data bus (DQ[7:0])

- Read-Write Data Strobe (RWDS)

- HyperFlash™ memories use RWDS only as a Read Data Strobe

- Up to 333 MB/s sustained read throughput

- Double-Data Rate (DDR) two data transfers per clock

- 166-MHz clock rate (333 MB/s) at 1.8V V<sub>CC</sub>

- 100-MHz clock rate (200 MB/s) at 3.0V V<sub>CC</sub>

- 96-ns initial random read access time

- Initial random access read latency: 5 to 16 clock cycles

- Sequential burst transactions

- Configurable Burst Characteristics

- Wrapped burst lengths:

- 16 bytes (8 clocks)

- 32 bytes (16 clocks)

- 64 bytes (32 clocks)

- Linear burst

- Hybrid option one wrapped burst followed by linear burst

- Wrapped or linear burst type selected in each transaction

- Configurable output drive strength

- Low Power Modes

- Active Clock Stop During Read: 12 mA, no wake-up required

- Standby: 25 µA (typical), no wake-up required

- Deep Power-Down: 8  $\mu$ A (typical)

- 300 μs wake-up required

- INT# output to generate external interrupt

- Busy to Ready Transition

- ECC detection

- RSTO# output to generate system level power-on reset

User configurable RSTO# Low period

- 512-byte Program Buffer

- Sector Erase

- Uniform 256-kB sectors

- Optional Eight 4-kB Parameter Sectors (32 kB total)

- Advanced Sector Protection

- Volatile and non-volatile protection methods for each sector

- Separate 1024-byte one-time program array

- Operating Temperature

- Industrial (–40°C to +85°C)

- Industrial Plus (-40°C to +105°C)

- Extended (-40°C to +125°C)

- Automotive, AEC-Q100 Grade 3 (-40°C to +85°C)

- Automotive, AEC-Q100 Grade 2 (-40°C to +105°C)

- Automotive, AEC-Q100 Grade 1 (-40°C to +125°C)

- ISO/TS16949 and AEC Q100 Certified

- Endurance

- 100,000 program/erase cycles

- Retention

- 20 year data retention

- Erase and Program Current - Max Peak ≤ 100 mA

- Packaging Options

24-Ball FBGA

- Additional Features

- ECC 1-bit correction, 2-bit detection

- CRC (Check-value Calculation)

# **Performance Summary**

| Read Acce                                                     | ss Timings |

|---------------------------------------------------------------|------------|

| Maximum Clock Rate at 1.8V V <sub>CC</sub> /V <sub>CC</sub> Q | 166 MHz    |

| Maximum Clock Rate at 3.0V V <sub>CC</sub> /V <sub>CC</sub> Q | 100 MHz    |

| Maximum Access Time, (t <sub>ACC</sub> )                      | 96 ns      |

| Maximum CS# Access Time to First Word @ 166 MHz               | 118 ns     |

| Typical Program / Erase Times           |                    |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|--------------------|--|--|--|--|--|--|--|--|--|

| Single Word Programming (2B = 16b)      | 500 μs (~4 kB/s)   |  |  |  |  |  |  |  |  |  |

| Write Buffer Programming (512B = 4096b) | 475 μs (~1 MB/s)   |  |  |  |  |  |  |  |  |  |

| Sector Erase Time (256 kB = 2 Mb)       | 930 ms (~282 kB/s) |  |  |  |  |  |  |  |  |  |

| Typical Current Consumption             |                            |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|----------------------------|--|--|--|--|--|--|--|--|--|

| Burst Read (Continuous Read at 166 MHz) | 80 mA                      |  |  |  |  |  |  |  |  |  |

| Power-On Reset                          | 80 mA                      |  |  |  |  |  |  |  |  |  |

| Sector Erase Current                    | 60 mA                      |  |  |  |  |  |  |  |  |  |

| Write Buffer Programming Current        | 60 mA                      |  |  |  |  |  |  |  |  |  |

| Standby (CS# = High)                    | 25 μΑ                      |  |  |  |  |  |  |  |  |  |

| Deep Dewer Dewe (CC# _ Lligh 95%C)      | 30 µA (512 Mb)             |  |  |  |  |  |  |  |  |  |

| Deep Power-Down (CS# = High, 85°C)      | 4 μA (all other densities) |  |  |  |  |  |  |  |  |  |

# S26KL512S/S26KS512S S26KL256S/S26KS256S S26KL128S/S26KS128S

# Contents

| <b>1.</b><br>1.1                      | General Description                                                                                                                | . 4      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2                                   | Functionality (DCARS)<br>Error Detection and Correction Functionality                                                              |          |

| <b>2.</b><br>2.1                      | Connection Diagram<br>FBGA 24-Ball 5 x 5 Array Footprint                                                                           |          |

| 3.                                    | Signal Description                                                                                                                 | 10       |

| <b>4.</b><br>4.1<br>4.2<br>4.3<br>4.4 | HyperBus Protocol<br>Command / Address Bit Assignments<br>Read Operations<br>HyperFlash Read with DCARS Timing<br>Write Operations | 12<br>12 |

| <b>5.</b><br>5.1<br>5.2               | Address Space Maps<br>Flash Memory Array<br>Device ID and CFI (ID-CFI) ASO                                                         | 20       |

| <b>6.</b><br>6.1<br>6.2<br>6.3        | Embedded Operations<br>Embedded Algorithm Controller (EAC)<br>Program and Erase Summary<br>Data Protection                         | 24<br>25 |

| <b>7.</b><br>7.1                      | Device ID and Common Flash<br>Interface (ID-CFI) ASO Map<br>Device ID and Common Flash Interface<br>(ID-CFI) ASO Map — Standard    |          |

| 7.2                                   | Device ID and Common Flash Interface<br>(ID-CFI) ASO Map — Automotive Grade /<br>AEC-Q100                                          |          |

| <b>8.</b><br>8.1                      | Software Interface Reference<br>Command Summary                                                                                    |          |

| 9.                                    | Data Integrity                                                                                                                     | 70       |

| 9.1<br>9.2                                                         | Endurance<br>Data Retention                                                                                                                                                                                                                     | -                                                    |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Hard                                                               | Iware Interface                                                                                                                                                                                                                                 |                                                      |

| <b>10.</b><br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7 | Electrical Specifications.<br>Absolute Maximum Ratings<br>Latchup Characteristics<br>Operating Ranges<br>DC Characteristics (CMOS Compatible)<br>Power-Up and Power-Down<br>Power-Off with Hardware Data Protection<br>Power Conservation Modes | . 71<br>. 72<br>. 72<br>. 73<br>. 73<br>. 75<br>. 79 |

| <b>11.</b><br>11.1<br>11.2                                         | Timing Specifications<br>AC Test Conditions<br>AC Characteristics                                                                                                                                                                               | . 81                                                 |

| 12.                                                                | Embedded Algorithm Performance                                                                                                                                                                                                                  | . 88                                                 |

| <b>13.</b><br>13.1<br>13.2<br>13.3                                 | Ordering Information<br>Ordering Part Numbers<br>Valid Combinations — Standard<br>Valid Combinations — Automotive Grade /<br>AEC-Q100                                                                                                           | . 89<br>. 90                                         |

| 14.                                                                | Physical Interface                                                                                                                                                                                                                              |                                                      |

| 14.1                                                               | Physical Diagram                                                                                                                                                                                                                                |                                                      |

| 15.                                                                | Document History Page                                                                                                                                                                                                                           |                                                      |

|                                                                    | s, Solutions, and Legal Information                                                                                                                                                                                                             |                                                      |

| F<br>F<br>C                                                        | Norldwide Sales and Design Support<br>Products<br>PSoC® Solutions<br>Cypress Developer Community                                                                                                                                                | . 99<br>. 99<br>. 99                                 |

| ٦                                                                  | Technical Support                                                                                                                                                                                                                               | . 99                                                 |

# 1. General Description

The Cypress HyperFlash family of products are high-speed CMOS, MirrorBit<sup>®</sup> NOR flash devices with the HyperBus low signal count DDR (Double Data Rate) interface, that achieves high speed read throughput. The DDR protocol transfers two data bytes per clock cycle on the data (DQ) signals. A read or write access for the HyperFlash consists of a series of 16-bit wide, one clock cycle data transfers at the internal HyperFlash core and two corresponding 8-bit wide, one-half-clock-cycle data transfers on the DQ signals.

Both data and command/address information are transferred in DDR fashion over the 8-bit data bus. The clock input signals are used for signal capture by the HyperFlash device when receiving command/address/data information on the DQ signals. The Read Data Strobe (RWDS) is an output from the HyperFlash device that indicates when data is being transferred from the memory to the host. RWDS is referenced to the rising and falling edges of CK during the data transfer portion of read operations. Command/address/write-data values are center aligned with the clock edges and read-data values are edge aligned with the transitions of RWDS.

Read and write operations to the HyperFlash device are burst oriented. Read transactions can be specified to use either a wrapped or linear burst. During wrapped operation, accesses start at a selected location and continue for a configured number of locations in a group wrap sequence. During linear operation accesses start at a selected location and continue in a sequential manner until the read operation is terminated, when CS# returns High. Write transactions transfer one or more16-bit values.

The HyperFlash family consists of multiple densities, 1.8V/3.0V core and I/O, non-volatile, synchronous flash memory devices. These devices have an 8-bit (1-byte) wide DDR data bus and use only word-wide (16-bit data) address boundaries. Read operations provide 16 bits of data during each clock cycle (8 bits on each clock edge). Write operations take 16 bits of data from each clock cycle (8 bits on each clock edge).

Each random read accesses a 32-byte length and aligned set of data called a page. Each page consists of a pair of 16-byte aligned groups of array data called half-pages. Half-pages are aligned on 16-byte address boundaries. A read access requires two clock cycles to define the target half-page address and the burst type, then an additional initial latency. During the initial latency period the third clock cycle will specify the starting address within the target half-page. After the initial data value has been output, additional data can be read from the Page on subsequent clock cycles in either a wrapped or linear manner. When configured in linear burst mode, while a page is being burst out, the device will automatically fetch the next sequential page from the MirrorBit flash memory array. This simultaneous burst output while fetching from the array allows for a linear sequential burst operation that can provide a sustained output of 333 MB/s data rate (1-byte (8-bit data bus) \* 2 (Data on both clock edges) \* 166 MHz = 333 MB/s).

#### Table 1. S26KS Address Map

| Туре                                                        | Count                                       | Addresses  | Notes     |

|-------------------------------------------------------------|---------------------------------------------|------------|-----------|

| Word Address within a half-page (16 byte)                   | 8 (word addresses)                          | A2 – A0    | 16 bytes  |

| Word Address within Write Buffer Line (512 byte)            | 256 (word addresses)                        | A7 – A0    | 512 bytes |

| Half-pages (16 bytes) within Erase Sector (256 kB)          | 8192 (half-pages)                           | A16 – A3   |           |

| Write Buffer Lines (512 bytes) within Erase Sector (256 kB) | 512 (lines)                                 | A16 – A8   |           |

| Total Number of Erase Sectors (256 kB)                      | 256 (512 Mb)<br>128 (256 Mb)<br>64 (128 Mb) | Amax – A17 |           |

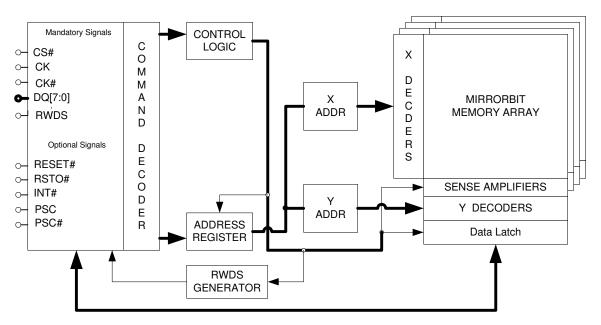

The device control logic is subdivided into two parallel operating sections: the Host Interface Controller (HIC) and the Embedded Algorithm Controller (EAC). The HIC monitors signal levels on the device inputs and drives outputs as needed to complete read and write data transfers with the host system (HyperFlash master). The HIC delivers data from the currently entered address map on read transfers; places write transfer address and data information into the EAC command memory; notifies the EAC of power transition, and write transfers. The EAC looks in the command memory, after a write transfer, for legal command sequences and performs the related Embedded Algorithms.

Changing the non-volatile data in the memory array requires a complex sequence of operations that are called Embedded Algorithms (EA). The algorithms are managed entirely by the internal EAC. The main algorithms perform programming and erase of the main flash array data. The host system writes command codes to the flash device address space. The EAC receives the command, performs all the necessary steps to complete the command, and provides status information during the progress of an EA.

The erased state of each memory bit is a logic 1. Programming changes a logic 1 (High) to a logic 0 (Low). Only an erase operation is able to change a 0 to a 1. An erase operation must be performed on an entire 256-kbyte (or 4-kbyte for parameter sectors) aligned group of data called a Sector. When shipped from Cypress all Sectors are erased.

Programming is done via a 512-byte Write Buffer. It is possible to write from one to 256 words, anywhere within the Write Buffer before starting a programming operation. Within the flash memory array, each 512-byte aligned group of data is called a Line. A programming operation transfers data from the volatile Write Buffer to a non-volatile memory array Line. The operation is called Write Buffer Programming.

The Write Buffer is filled with 1s after reset or the completion of any operation using the Write Buffer. Any locations not written to a 0 by a Write to Buffer command are by default still filled with 1s. Any 1s in the Write Buffer do not affect data in the memory array during a programming operation.

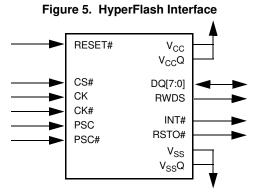

In addition to the mandatory signals (CS#, CK, CK#, DQ [7:0], RWDS) dedicated to the HyperBus, the device also includes optional signals (RESET#, INT#, RSTO#, and Phase Shifted clocks PSC/PSC#).

When RESET# transitions from Low to High the device returns to the default state that occurs after an internal Power-On Reset (POR).

The INT# output can provide an interrupt to the HyperFlash master to indicate when the HyperFlash transitions from busy to ready at the end of a program or erase operation.

The RSTO# is an open-drain output used to indicate when a POR is occurring within the device and can be used as a system level reset signal. Upon completion of the internal POR the RSTO# signal will transition from Low to high impedance after a user defined timeout period has expired. Upon transition to the high impedance state the external pull-up resistance will pull RSTO# High and the device immediately is placed into the Standby state.

PSC/PSC# are differential Phase Shifted Clock inputs used as a reference for RWDS edges instead of CK/CK#. Refer to Section 1.1, DDR Center Aligned Read Strobe Functionality (DCARS) on page 6 for more details.

# 1.1 DDR Center Aligned Read Strobe Functionality (DCARS)

The HyperFlash memories offer a configurable feature that enables independent skewing (phase shifting) of the RWDS signal with respect to the read data outputs.

When the DDR Center Aligned Read Strobe (DCARS) feature is enabled, a second differential Phase Shifted Clock input PSC/PSC# is used as the reference for RWDS edges instead of CK/CK#. The second clock is generally a copy of CK/CK# that is phase shifted 90 degrees to place the RWDS edges centered within the DQ signals valid data window. However, other degrees of phase shift between CK/CK# and PSC/PSC# may be used to optimize the position of RWDS edges within the DQ signals valid data window so that RWDS provides the desired amount of data setup and hold time in relation to RWDS edges.

PSC/PSC# is not used during a write transaction. PSC and PSC# may be driven Low and High respectively or, both may be driven Low during write transactions.

# **1.2 Error Detection and Correction Functionality**

### 1.2.1 Error Correction Code

HyperFlash memories provide embedded Hamming Error Correction Code (ECC) generation during Flash memory array programming, with error detection and correction during read.

As each 16-byte aligned half-page of data, loaded into the Write Buffer, is transferred to the 512-byte flash memory array Line, an Error Correction Code (ECC) for each Half-page ECC unit is also programmed in to a portion of the memory array not visible to the host system software.

The ECC information is checked during each Half-page Flash array read operation. Any one bit error within the Half-page will be corrected by the ECC logic during the access of each Half-page.

The ECC information for each Half-page can be written once after each erase of the sector containing each Half-page. Programming within the same Half-page more than once will disable error detection and correction within that Half-page.

Word Programming and Write Buffer Programming, more than once within a Half-page, is supported for legacy software compatibility. However, for the best data integrity, it is recommended to not use Word Programming or Write Buffer Programming to program within a Half-page, more than once. Multiple writes to the same half page without an erase will disable the ECC functionality since the ECC syndrome becomes invalid. For applications requiring multiple programming operations within the same Half-page, it is recommended to add system software Error Detection and Correction, to enhance the data integrity of Half-pages that are programmed more than once.

There is a mode that may be enabled for two bit error detection. When this mode is enabled, any one bit error in a Half-page is corrected and any two bit error is detected and reported. In this mode, the ability to write to the same half-page more than once, after an erase, is disabled. In this mode, attempting to program more than once in the same Half-page will result in programming operation failure status.

ECC errors may be detected by reading an ECC status register, enabling an interrupt, or enabling the RWDS to stop when an uncorrectable error is encountered - to create a bus error before data is transferred to the HyperBus master.

A register is provided to capture the address location of the ECC error.

A counter is provided to count ECC corrections or uncorrectable errors.

### 1.2.2 Cyclic Redundancy Check

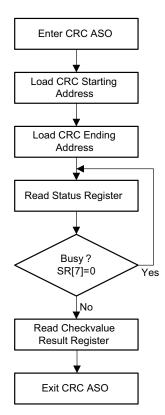

A group of commands are provided to perform a hardware accelerated Cyclic Redundancy Check (CRC) calculation over a user defined address range. The calculation is another type of embedded operation similar to programming or erase, in which the device is busy while the calculation is in progress. The CRC operation uses a 32-bit polynomial able to detect up to a 32-bit long group of error bits.

A command is used to enter the CRC Address Space Overlay (ASO) where the desired address range is loaded to start the CRC calculation. While entered in the CRC ASO the status of the CRC operation may be checked, suspended to read from the memory array, resumed, and the resulting check-value read. See Address Space Maps on page 19.

### 1.2.2.1 CRC Check-Value Calculation

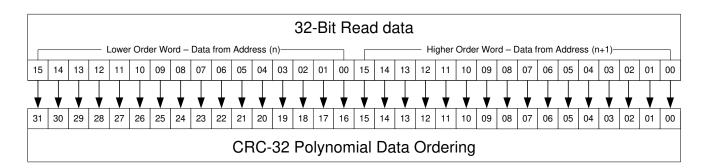

The Check-value Calculation command sequence causes the device to perform a Cyclic Redundancy Check (CRC) calculation over a user defined address range. The CRC calculation is achieved with the polynomial described in Figure 2.

The Check-value generation sequence is started by entering the CRC ASO. The next step is to load the beginning address into the CRC Start Address Register identifying the beginning of the address range that will be covered by the CRC calculation. Next the ending address is loaded into the CRC End Address Register, this step starts the CRC calculation. The CRC process calculates the Check-value on the data contained at the starting address through the ending address.

During the calculation period the device goes into the Busy state (SR[7] = 0). Once the Check-value Calculation has completed the device returns to the Ready state (SR[7] = 1) and the calculated Check-value is available in the Check-value Low Result Register and the Check-value High Result Register. The Check-value Low Result Register contains Check-value bits 0-15 and can be read from address 0 while the device is in the CRC ASO. The Check-value High Result Register contains bits 16-31 and can be read from address 1 while the device is in the CRC ASO. The Check-value Low Result Register and the Check-value High Result Register are loaded with 0s once the CRC calculation process is initiated.

The Check-value Calculation can only be initiated when the device is in Standby State and once started can be suspended with the CRC Suspend sequence to read data from the array. During the Suspended state the CRC Suspend Status Bit (CRCSSB) in the Status Register will be set (SR[8] = 1). Once suspended, the host can read the Status Register, read data from the array and can resume the CRC calculation by using the CRC Resume command sequence. Once initiated the CRC ASO can be terminated with the ASO Exit Command or a Hardware Reset to return the device to Read Array Mode. The Check-value Calculation can not be performed while another ASO is active. A Hardware Reset will clear the value in the CRC Start Address Register, CRC End Address Register, Check-value High Result Register and the Check-value Low Result Register.

The Ending Address (EA) should be at least two addresses higher than the Starting Address (SA). If EA < SA + 2 the Check-value Calculation will abort and the device will return to the Ready state (SR[7] = 1). SR[3] will be set (1) to indicate the aborted condition. If EA < SA + 2 the Check-value High Result Register and the Check-value Low Result Register will hold indeterminate data.

#### Figure 2. CRC-32 Polynomial

CRC-32C Polynomial =  $X^{32} + X^{28} + X^{27} + X^{26} + X^{25} + X^{23} + X^{22} + X^{20} + X^{19} + X^{18} + X^{14} + X^{13} + X^{11} + X^{10} + X^{9} + X^{8} + X^{6} + 1$

#### Figure 3. Check-Value Calculation Sequence

The read data ordering used in calculating the check-value from the CRC-32 polynomial is shown as follows:

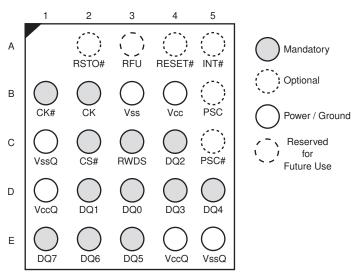

# 2. Connection Diagram

# 2.1 FBGA 24-Ball 5 x 5 Array Footprint

HyperFlash devices are provided in Fortified Ball Grid Array (FBGA), 1 mm pitch, 24-ball, 5 x 5 ball array footprint, with 6mm x 8mm body. The package height is device dependent and may be either 1 mm or 1.2 mm. See Ordering Information on page 89. Consult the device data sheet Ordering Part Number valid combinations section for the package in use.

#### Figure 4. 24-Ball FBGA, 6 x 8 mm, 5x5 Ball Footprint, Top View

#### Notes:

1. B1 (CK#) is RFU on the 3.0V device (model 02).

- 2. B5 (PSC) and C5 (PSC#) are RFU on standard 3.0V and 1.8V devices (model 02). C5 (PSC#) is RFU on 3V DCARS device (model 03).

- 3. RFU Reserved for Future Use. Not currently connected internally but the pin/ball location should be left unconnected and unused by PCB routing channel for future compatibility. The pin/ball may be used by a signal in the future.

# 3. Signal Description

### Table 2. Signal Descriptions

| Symbol            | Туре                   | M / O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS#               | Input                  | М     | <b>Chip Select.</b> HyperFlash bus transactions are initiated with a High to Low transition. HyperFlash bus transactions are terminated with a Low to High transition.                                                                                                                                                                                                                                                                                                       |

| CK, CK#           | Input                  | М     | <b>Differential Clock.</b> Command / Address / Data information is input or output with respect to the crossing of the CK and CK# signals. CK# is only used on the 1.8V devices and may be left open or connected to CK on 3V devices.                                                                                                                                                                                                                                       |

| RWDS              | Output                 | М     | Read Write Data Strobe. Output data during read transactions are edge aligned with RWDS.                                                                                                                                                                                                                                                                                                                                                                                     |

| DQ[70]            | Input / Output         | М     | <b>Data Input / Output.</b> Command / Address / Data information is transferred on these DQs during read and write transactions.                                                                                                                                                                                                                                                                                                                                             |

| PSC,<br>PSC#      | Input                  | 0     | <b>Phase Shifted Clock.</b> PSC/PSC# allows independent skewing of the RWDS signal with respect to the CK/CK# inputs. PSC# is only used on the 1.8V device. PSC and PSC# may be driven High and Low respectively or both may be driven Low during write transactions.                                                                                                                                                                                                        |

| INT#              | Output<br>(open drain) | 0     | <b>INT Output.</b> When Low, the device is indicating that an internal event has occurred. This signal is intended to be used as a system level interrupt for the device to indicate that an on-chip event has occurred. INT# is an open-drain output.                                                                                                                                                                                                                       |

| RESET#            | Input                  | 0     | <b>Hardware Reset.</b> When Low, the device will self initialize and return to the array read state.<br>RWDS and DQ[7:0] are placed into the High-Z state when RESET# is Low. RESET# includes<br>a weak pull-up, if RESET# is left unconnected it will be pulled up to the High state.                                                                                                                                                                                       |

| RSTO#             | Output<br>(open drain) | 0     | <b>RSTO# Output.</b> RSTO# is an open-drain output used to indicate when a POR is occurring within the device and can be used as a system level reset signal. Upon completion of the internal POR the RSTO# signal will transition from Low to high impedance after a user defined timeout period has elapsed. Upon transition to the high impedance state the external pull-up resistance will pull RSTO# High and the device immediately is placed into the Standby state. |

| V <sub>CC</sub>   | Power Supply           | P/G   | Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>CC</sub> Q | Power Supply           | P/G   | Input / Output Power.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{SS}$          | Power Supply           | P/G   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $V_{SS}Q$         | Power Supply           | P/G   | Input / Output Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Note:

1. *M* = Mandatory; *O* = Optional; *P*/*G* = Power / Ground

# 4. HyperBus Protocol

All bus transactions can be classified as either read or write. A bus transaction is started with CS# going Low with CK = Low and CK# = High. The transaction to be performed is presented to the HyperFlash device during the first three clock cycles in a DDR manner using all six clock edges. These first three clocks transfer three words of Command / Address (CA0, CA1, CA2) information to define the transaction characteristics:

- Read or write transaction.

- Whether the transaction will be to the memory array or to register space.

- Although the HyperBus protocol provides for slave devices that have both memory and register address spaces, HyperFlash memories described in this specification do not differentiate between memory and registers as separate address spaces. There is a single address space selected by any transaction, independent of whether the transaction indicates the target location is in memory space or register space. Write transactions always place the transaction address and data into a a command register set (buffer). Read transactions return data from the memory array or from a register address space window that has been temporarily overlaid within the single address space by the execution of commands. The single address space with register space overlays methodology is backward compatible with legacy parallel NOR Flash memory program and erase software drivers.

- Whether a transaction will use a linear or wrapped burst sequence.

- HyperFlash write transactions do not support burst sequence and ignore the burst type indication. Write command transactions transfer a single word per write. Only the Word Program command write data transfer may be done with a linear burst at up to 50 MHz.

- The target half-page address (row and upper order column address).

- The target Word (within half-page) address (lower order column address).

Once the transaction has been defined, a number of idle clock cycles are used to satisfy any read latency requirements before data is transferred. Once the target data has been transferred the HyperBus master host completes the transaction by driving CS# High with CK = Low and CK# = High. Data is transferred as 16-bit values with the first eight bits (15-8) transferred on a High going CK (write data or CA bits) or RWDS edge (read data) and the second eight bits (7-0) being transferred on the Low going CK or RWDS edge. Data transfers during read or write operations can be ended at any time by bringing CS# High when CK = Low and CK# = High. Read data is edge aligned with RWDS transitions and Write data is center aligned with clock edges.

# 4.1 Command / Address Bit Assignments

#### Table 3. Command / Address Bit Assignments

| CA Bit#                        | Bit Name                        | Bit Function                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|--------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 47                             | R/W#                            | Identifies the transaction as a Read or Write.<br>1 = Read operation<br>0 = Write operation<br>Target space is defined in CA46.                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| 46                             | Target                          | Indicates whether the Read or Write operation accesses the memory or register spaces.<br>0 = memory space<br>1 = register space<br>The register space is intended to be used by volatile memory and peripheral devices. The<br>HyperFlash devices will not take advantage of this feature and this bit should be set to 0<br>during Read or Write transactions. |  |  |  |  |  |  |  |  |

| 45                             | Burst Type                      | Indicates whether the burst will be linear or wrapped.<br>0 = Wrapped Burst<br>1 = Linear Burst                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| 44-39 (1 Gb)<br>44-38 (512 Mb) | Reserved                        | Reserved for future address expansion.<br>Reserved bits should be set to 0 by the host controller.                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 38-16 (1 Gb)<br>37-16 (512 Mb) | Row and Upper<br>Column Address | Half page component of target address.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 15-3                           | Reserved                        | Reserved for future column address expansion.<br>Reserved bits should be set to 0 by the host controller.                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| 2-0                            | Lower Column<br>Address         | Lower Column component of the target address: System word address bits A2-0 selecting the starting word within a half-page.                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

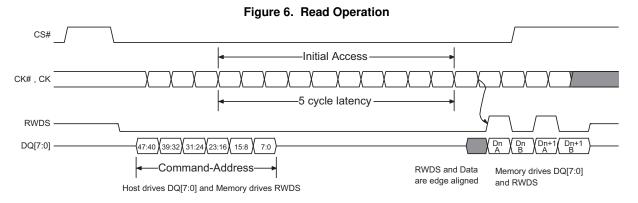

# 4.2 Read Operations

CA0 indicates that a read operation is to be performed and also indicates the burst type (wrapped or linear). Read operations begin the internal array access as soon as the half-page address has been presented in CA0 and CA1. CA2 identifies the target word address within the chosen half-page. The host then continues clocking for a number of cycles defined by the latency count setting in the Configuration Register. Once these latency clocks have been completed the memory starts to simultaneously transition the Read Write Data Strobe (RWDS) and begins outputting the target data. New data is output in an edge aligned fashion upon every transition of RWDS. Data will continue to be output as long as the host continues to transition the clock (CK and CK#). Wrapped bursts will continue to wrap within the burst length and linear burst will output data in a sequential manner across page boundaries. A Hybrid Burst provides one initial wrapped burst followed by linear burst, as described in Section 6.3.11, Hybrid Burst on page 56. Wrapped reads can be performed from the main array, the CFI Tables and the Secure Silicon Region. Read transfers can be ended at any time by bringing CS# High when CK = Low and CK# = High.

When a linear burst reaches the last address in the array, if the burst continues, the address counter will wrap around and roll back to address 000000h, allowing the read sequence to be continued indefinitely. The entire memory can therefore be read out with one single read instruction.

The 16-byte and 32-byte wrapped bursts do not cross page boundaries and do not incur inter-page boundary crossing latencies. For a 64-byte wrapped burst read, a latency may occur during the target address to next page boundary crossing, depending on the starting address (See 64-byte Wrapped Burst Address Sequence (Latency Code = 16) on page 40.)

#### Notes:

1. Transactions must be initiated with CK = Low and CK# = High. CS# must return High before a new transaction is initiated.

2. Read access from the flash array starts once CA[23:16] is captured.

3. The read latency is defined by the Read Latency value in the Volatile Configuration Register (or the Non-Volatile Configuration Register).

4. In this example of a read operation the Latency Count was set to five clocks.

#### Table 4. Maximum Operating Frequency for Latency Code Options

| Latency Code | Latency Clocks | Maximum Operating Frequency<br>(MHz) |

|--------------|----------------|--------------------------------------|

| 0000         | 5              | 52                                   |

| 0001         | 6              | 62                                   |

| 0010         | 7              | 72                                   |

| 0011         | 8              | 83                                   |

| 0100         | 9              | 93                                   |

| 0101         | 10             | 104                                  |

| 0110         | 11             | 114                                  |

| 0111         | 12             | 125                                  |

| 1000         | 13             | 135                                  |

| 1001         | 14             | 145                                  |

| 1010         | 15             | 156                                  |

| 1011         | 16             | 166                                  |

| 1100         | Reserved       | NA                                   |

| 1101         | Reserved       | NA                                   |

| 1110         | Reserved       | NA                                   |

| 1111         | Reserved       | NA                                   |

#### Notes:

1. Default NVCR latency setting when the device is shipped from the factory is 16 clocks.

2. The Latency Code is the value loaded into (Non) Volatile Configuration Register bits xVCR[7:4].

3. Maximum Operating Frequency assumed to be using a device with  $t_{ACC}$  = 96 ns.

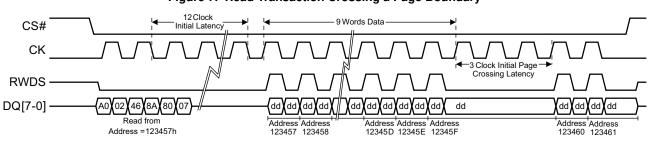

#### Figure 7. Read Transaction Crossing a Page Boundary

#### Notes:

- 1. Read operation starting at device address 123457h.

- 2. Latency code loaded into the Configuration Register is 0111b which results in 12 latency clocks.

- 3. Page boundary crossing requires three clocks in this case. 12 clock initial latency minus 9 clocks (words) of initial data.

- 4. CK# is not shown but is the complement of the CK signal.

- 5. CA45 = 1 for a linear Read burst.

| Target  |     |     |     |        |                 |                 |                 |     |     |     |     | Clock | Cycle  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|---------|-----|-----|-----|--------|-----------------|-----------------|-----------------|-----|-----|-----|-----|-------|--------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Address | 0   | 1   | 2   | 3      |                 | 12              | 13              | 14  | 15  | 16  | 17  | 18    | 19     | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  |     |     |     |     |     |

| 0       |     |     |     |        |                 |                 | D0              | D1  | D2  | D3  | D4  | D5    | D6     | D7  | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 |     |     |     |     |     |

| 1       |     |     |     |        |                 |                 | D1              | D2  | D3  | D4  | D5  | D6    | D7     | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 |     |     |     |     |     |

| 2       |     |     |     |        |                 |                 | D2              | D3  | D4  | D5  | D6  | D7    | D8     | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 |     |     |     |     |     |

| 3       |     |     |     |        |                 |                 | D3              | D4  | D5  | D6  | D7  | D8    | D9     | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 |     |     |     |     |     |

| 4       |     |     |     |        |                 |                 | D4              | D6  | D6  | D7  | D8  | D9    | D10    | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 |     |     |     |     |     |

| 5       |     |     |     |        |                 |                 | D5              | D6  | D7  | D8  | D9  | D10   | D11    | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |     |

| 6       |     |     |     |        |                 |                 |                 |     | D6  | D7  | D8  | D9    | D10    | D11 | D12 | D13 | D14 | D15 | Х   | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |

| 7       |     |     |     | Bus 1  | Bus Turnaround  | us Turnaround   | ound            | D7  | D8  | D9  | D10 | D11   | D12    | D13 | D14 | D15 | Х   | Х   | D16 | D17 | D18 | D19 | D20 | D21 | D22 |     |     |     |     |

| 8       | CA0 | CA1 | CA2 | +      |                 |                 |                 | •   | •   |     |     | D8    | D9     | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 |

| 9       |     |     |     | Initia | Initial Latency | Initial Latency | Initial Latency | D9  | D10 | D11 | D12 | D13   | D14    | D15 | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 |     |     |     |     |

| 10      |     |     |     |        |                 |                 | D10             | D11 | D12 | D13 | D14 | D15   | D16    | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 |     |     |     |     |     |

| 11      |     |     |     |        |                 | D11             | D12             | D13 | D14 | D15 | D16 | D17   | D18    | D19 | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 |     |     |     |     |     |     |

| 12      |     |     |     | 1      |                 | D12             | D13             | D14 | D15 | D16 | D17 | D18   | D19    | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 |     |     |     |     |     |     |

| 13      |     |     |     |        |                 |                 | D13             | D14 | D15 | D16 | D17 | D18   | D19    | D20 | D21 | D22 | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |     |     |     |     |

| 14      |     |     |     |        |                 |                 | D14             | D15 | D16 | D17 | D18 | D19   | D20    | D21 | D22 | D23 | Х   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |     |     |     |     |

| 15      |     |     |     |        |                 |                 | D15             | D16 | D17 | D18 | D19 | D20   | D21    | D22 | D23 | Х   | Х   | D24 | D25 | D26 | D27 | D28 | D29 | D30 |     |     |     |     |     |

| 16      |     |     |     |        |                 |                 | D16             | D17 | D18 | D19 | D20 | D21   | D22    | D23 | D24 | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 |     |     |     |     |     |

|         | —   | —   | 1   | 2      |                 | 11              | _               | —   | —   | _   | _   | -     | _      | _   | _   | _   |     | _   | —   | —   | _   | _   | —   | —   |     |     |     |     |     |

|         |     |     |     |        |                 |                 |                 |     |     |     | L   | atenc | y Coui | nt  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

#### Table 5. First Page Boundary Crossing During Linear Read (Latency Count = 11 Clocks)

| Table 6. | First Page Boundary | Crossing During Linear | r Read (Latency Count = 16 Clocks) |

|----------|---------------------|------------------------|------------------------------------|

|----------|---------------------|------------------------|------------------------------------|

| Target  |     |     |     |   |                                     |     |     |     |     | Cloc | k Cyc | le Afte | r CS#  | Goes | Low |     |     |     |     |     |     |     |     |     |     |

|---------|-----|-----|-----|---|-------------------------------------|-----|-----|-----|-----|------|-------|---------|--------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Address | 0   | 1   | 2   | 3 |                                     | 17  | 18  | 19  | 20  | 21   | 22    | 23      | 24     | 25   | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  |     |

| 0       |     |     |     |   |                                     |     | D0  | D1  | D2  | D3   | D4    | D5      | D6     | D7   | D8  | D9  | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 |     |

| 1       |     |     |     |   |                                     |     | D1  | D2  | D3  | D4   | D5    | D6      | D7     | D8   | D9  | D10 | D11 | D12 | D13 | D14 | D15 | Х   | D16 | D17 |     |

| 2       |     |     |     |   |                                     |     | D2  | D3  | D4  | D5   | D6    | D7      | D8     | D9   | D10 | D11 | D12 | D13 | D14 | D15 | Х   | Х   | D16 | D17 |     |

| 3       |     |     |     |   |                                     |     | D3  | D4  | D5  | D6   | D7    | D8      | D9     | D10  | D11 | D12 | D13 | D14 | D15 | Х   | Х   | х   | D16 | D17 |     |

| 4       |     |     |     |   |                                     |     | D4  | D6  | D6  | D7   | D8    | D9      | D10    | D11  | D12 | D13 | D14 | D15 | Х   | Х   | Х   | х   | D16 | D17 |     |

| 5       |     |     |     |   |                                     |     | D5  | D6  | D7  | D8   | D9    | D10     | D11    | D12  | D13 | D14 | D15 | Х   | Х   | Х   | Х   | Х   | D16 | D17 |     |

| 6       |     |     |     |   | Bus Turnaround<br>+ Initial Latency |     | D6  | D7  | D8  | D9   | D10   | D11     | D12    | D13  | D14 | D15 | Х   | х   | Х   | Х   | Х   | х   | D16 | D17 |     |

| 7       |     |     |     | _ |                                     |     |     | D7  | D8  | D9   | D10   | D11     | D12    | D13  | D14 | D15 | х   | Х   | х   | Х   | Х   | Х   | х   | D16 | D17 |

| 8       | CA0 | CA1 | CA2 |   |                                     |     | D8  | D9  | D10 | D11  | D12   | D13     | D14    | D15  | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | D24 | D25 |     |

| 9       |     |     |     |   |                                     |     |     | D9  | D10 | D11  | D12   | D13     | D14    | D15  | D16 | D17 | D18 | D19 | D20 | D21 | D22 | D23 | х   | D24 | D25 |

| 10      |     |     |     |   |                                     | D10 | D11 | D12 | D13 | D14  | D15   | D16     | D17    | D18  | D19 | D20 | D21 | D22 | D23 | Х   | х   | D24 | D25 |     |     |

| 11      |     |     |     |   |                                     |     | D11 | D12 | D13 | D14  | D15   | D16     | D17    | D18  | D19 | D20 | D21 | D22 | D23 | Х   | Х   | Х   | D24 | D25 |     |

| 12      |     |     |     |   |                                     |     | D12 | D13 | D14 | D15  | D16   | D17     | D18    | D19  | D20 | D21 | D22 | D23 | Х   | Х   | Х   | Х   | D24 | D25 |     |

| 13      |     |     |     |   |                                     |     | D13 | D14 | D15 | D16  | D17   | D18     | D19    | D20  | D21 | D22 | D23 | Х   | Х   | Х   | Х   | Х   | D24 | D25 |     |

| 14      |     |     |     |   |                                     |     | D14 | D15 | D16 | D17  | D18   | D19     | D20    | D21  | D22 | D23 | Х   | Х   | Х   | Х   | Х   | Х   | D24 | D25 |     |

| 15      |     |     |     |   |                                     |     | D15 | D16 | D17 | D18  | D19   | D20     | D21    | D22  | D23 | Х   | Х   | Х   | Х   | Х   | Х   | Х   | D24 | D25 |     |

| 16      |     |     |     |   |                                     | D16 | D17 | D18 | D19 | D20  | D21   | D22     | D23    | D24  | D25 | D26 | D27 | D28 | D29 | D30 | D31 | D32 | D33 |     |     |

|         | —   | —   | 1   | 2 |                                     | 16  | —   | —   | —   | _    | —     | _       | —      | —    | —   | —   | —   | _   | —   | —   | —   | —   | _   | -   |     |

|         |     |     |     |   |                                     |     |     |     |     |      | L     | atency  | / Cour | nt   |     |     |     |     |     |     |     |     |     |     |     |

To calculate latency when crossing a page boundary, use the following formula:

```

if ((PS - LTCY) < ADDR & (SP -1))

{

((ADDR & (SP -1)) - PS + LTCY)

}

else

{0}</pre>

```

where:

PS = page size = 16 words

SP = sub-page size = 8 words

LTCY = latency

ADDR = target address

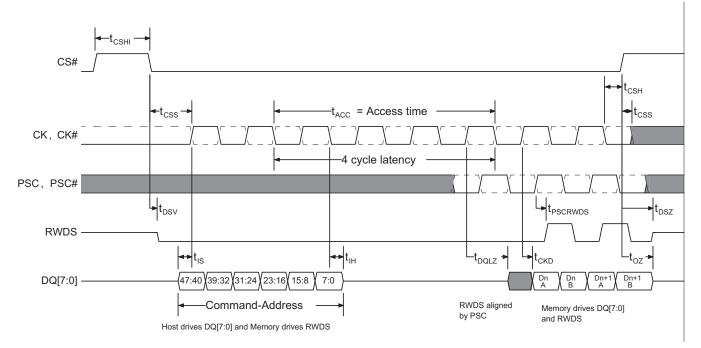

# 4.3 HyperFlash Read with DCARS Timing

The illustrations and parameters in this section are only those needed to define the DCARS feature and show the relationship between the Phase Shifted Clock, RWDS, and data.

#### Figure 8. HyperFlash Read DCARS Timing Diagram

#### Notes:

- 1. Transactions must be initiated with CK = Low and CK# = High. CS# must return High before a new transaction is initiated.

- 2. CK# and PSC# are optional and shown as dashed line waveforms.

- 3. The memory drives RWDS during read transactions.

- 4. This example demonstrates a latency code setting of four clocks and no additional initial latency required.

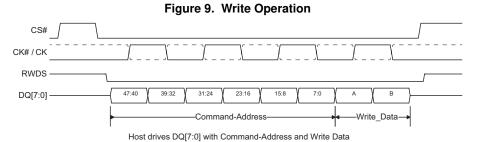

# 4.4 Write Operations

A write operation starts with the first three clock cycles providing the CAx (Command / Address) information indicating the transaction characteristics. The Burst Type bit CA[45) is 'don't care' because the HyperFlash device only supports a single write transaction of 16b or a continuous linear write burst that is only supported when loading data during a Word Program command. Immediately following the CA information the host is able to transfer the write data on the DQ bus. The first byte (A) of data is presented on the rising edge of CK and the second byte (B) is presented on the falling edge of CK. Write data is center aligned with the CK/CK# inputs. Write transfers can be ended at any time by bringing CS# High when CK = Low and CK# = High.

Notes:

- 1. Transactions must be initiated with CK = Low and CK# = High. CS# must return High before a new transaction is initiated.

- 2. RWDS will be driven Low as long as CS# is Low.

3. Write operations are limited to a transaction of a single word (16b) or a linear write burst supported only when loading data during a Word Program command.

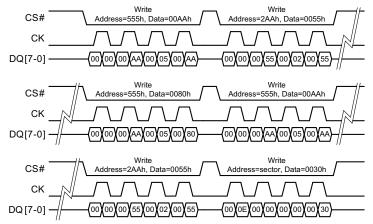

#### Figure 10. Write Transaction Usage Example: Erase Operation Command Sequence

Notes:

- 1. See Figure 16, Sector Erase Operation on page 33 for the Erase Operation Command Sequence flowchart.

- 2. Erase operation to the sector starting at 0700000h.

- 3. CK# is not shown but is the complement of the CK signal.

- 4. RWDS is not shown and is not used during Write transactions.

### S26KL512S/S26KS512S S26KL256S/S26KS256S S26KL128S/S26KS128S

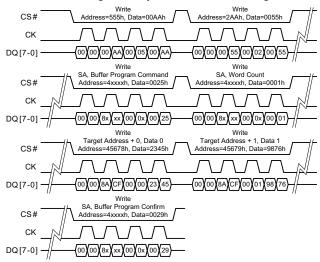

#### Figure 11. Write Transaction Usage Example: Write Buffer Program Command Sequence

#### Notes:

- 1. See Figure 14, Write Buffer Programming Operation with Status Register on page 29 for the Write Buffer Program Operation Command Sequence flowchart.

- 2. Program 2345h into address 45678h, and 9876h into address 45679h.

- 3. CK# is not shown but is the complement of the CK signal.

- 4. RWDS is not shown and is not used during Write transactions.

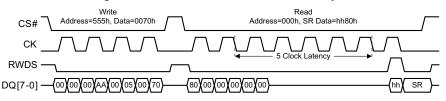

#### Figure 12. Status Read Transaction Example

#### Note:

<sup>1.</sup> CK# is not shown but is the complement of the CK signal.

# 5. Address Space Maps

Although the HyperBus protocol provides for slave devices that have both memory and register address spaces, HyperFlash memories described in this specification do not differentiate between memory and registers as separate address spaces. There is a single address space selected by any transaction, independent of whether the HyperBus transaction indicates the target location is in memory space or register space of the selected device.

Write transactions always place the transaction address and data into a a command register set (buffer).

Read transactions return data from the memory array or from a register address space window that has been temporarily overlaid within the single address space by the execution of commands. The single address range with register space overlays methodology is backward compatible with legacy parallel NOR Flash memory program and erase software drivers.

There are several separate address spaces that may appear within the address range of the flash memory device. One address space is visible (entered) at any given time.

- Flash Memory Array: the main non-volatile memory array used for storage of data that may be randomly accessed by read operations.

- ID/CFI: a flash memory array used for Cypress factory programmed device characteristics information. This area contains the Device Identification (ID) and Common Flash Interface (CFI) information tables.

- Secure Silicon Region (SSR): a 1024-byte one-time programmable non-volatile memory array used for Cypress factory programmed permanent data, and customer programmable permanent data.

- Persistent Protection Bits (PPB): a non-volatile memory array with one bit for each Sector. When programmed, each bit protects the related Sector from erasure and programming.

- PPB Lock Bit: a volatile register bit used to enable or disable programming and erase of the PPB bits.

- Password: an OTP non-volatile array used to store a 64-bit password used to enable changing the state of the PPB Lock Bit when using Password Mode Sector Protection.

- Dynamic Protection Bits (DYB): a volatile array with one bit for each Sector. When set, each bit protects the related Sector from erasure and programming.

- ECC Status: read the address of ECC corrected data and total ECC error count.

- CRC: read the CRC Check-value.

- Status or Peripheral Registers: register access used to display Embedded Algorithm status and read or write other registers.

The Flash Memory Array is the primary and default address space but, it may be overlaid by one other address space, at any one time. Each alternate address space is called an Address Space Overlay (ASO).

Each ASO replaces (overlays) either the sector selected by the command that enters the ASO or the entire flash device address range, depending on the ASO entry command. If only one sector is overlaid by an ASO the remaining sectors of the memory array remain readable. Any address range not defined by a particular ASO address map, is reserved for future use. Unless otherwise stated all read accesses outside of an ASO address map returns non-valid (undefined) data. The locations will display actively driven data but their meaning is not defined.

There are multiple address map modes that determine what appears in the flash device address space at any given time:

- Read Mode

- Status Register (SR) Mode

- Address Space Overlay (ASO) Mode

- Peripheral Register Mode

In Read Mode the entire Flash Memory Array may be directly read by the host system memory controller. The memory device Embedded Algorithm Controller (EAC), puts the device in Read Mode during Power-On, after a Hardware Reset, after a Command Reset, or after an Embedded Algorithm (EA) is suspended. Read accesses and commands are accepted in Read Mode. A subset of commands is accepted in Read Mode when an EA is suspended.

While in any mode, the Status Register read command may be issued to cause the Status Register ASO to appear at every word address in the device address space. In this Status Register ASO Mode, the device interface waits for a read access and, any write access is ignored. The next read access to the device accesses the content of the Status Register, exits the Status Register ASO, and returns to the previous (calling) mode in which the Status Register read command was received.

Similarly, commands that read and write other registers use Peripheral Register Mode, in which the register appears in a temporary ASO that is automatically exited after the read or write of the command selected register. The read or write occurs in the last cycle of the register access command sequence.

In EA Mode the EAC is performing an Embedded Algorithm, such as programming or erasing a non-volatile memory array. While in EA Mode, none of the Flash Memory Array is readable. While in EA Mode, only the Program / Erase Suspend command or the Status Register Read command will be accepted. All other commands are ignored. Thus, no other ASO may be entered from the EA Mode.

In ASO Mode, one of the remaining overlay address spaces is entered (overlaid on the Flash Memory Array address map). Only one ASO may be entered at any one time. Commands to the device affect the currently entered ASO. Only certain commands are valid for each ASO. These are listed in each ASO related section of Table 39, Command Definitions on page 65.

The following ASOs have non-volatile data that may be programmed to change 1s to 0s:

- Secure Silicon Region

- ASP Configuration Register (ASPR)

- Persistent Protection Bits (PPB)

- Password

- Only the PPB ASO has non-volatile data that may be erased to change 0s to 1s.

When a program or erase command is issued while one of the non-volatile ASOs is entered, the EA operates on the ASO. The ASO is not readable while the EA is active. When the EA is completed the ASO remains entered and is again readable. Suspend and Resume commands are ignored during an EA operating on any of these ASOs.

The Peripheral Register Mode is used to manage the Power-On Reset Timer, Interrupt Configuration Register, Interrupt Status Register, Volatile Configuration Register, and the Non-Volatile Configuration Register.

### 5.1 Flash Memory Array

The S26KL/S26KS family has a uniform sector architecture with a sector size of 256 kB. The following tables show the sector architecture of the devices.

A user configuration option is available to overlay either the first sector (SA00) or last sector (SAmax) with eight 4-kB Parameter-Sectors. The Parameter-Sector address map showing how the lowest or highest sector is partitioned is shown in the following memory address map tables. The Parameter-Sectors can be erased and programmed in the normal manner using the standard erase and program command sequences targeting the appropriate Parameter-Sector addresses. Note that the smaller Parameter-Sectors need to include A[16:11] as part of the address identifying the target Parameter-Sector during erase and program command sequences. Configuring the first or last uniform sector to include the parameter sectors is accomplished with the Non-Volatile Configuration Register.

**Note:** The following tables have been condensed to show sector related information for an entire device on a single page. Sectors and their address ranges that are not explicitly listed (such as SA001 – SA510) have sector starting and ending addresses that form the same pattern as all other sectors of that size. For example, all 256-kB sectors have the pattern XX00000h – XX1FFFFh.

| Table 7. | S26KL512S and | S26KS512S Sec | ctor and Memory | Address Map |

|----------|---------------|---------------|-----------------|-------------|

|----------|---------------|---------------|-----------------|-------------|

| Sector Size (kbyte) | Sector Count | Sector Range | Address Range (16-bit) | Notes                   |

|---------------------|--------------|--------------|------------------------|-------------------------|

|                     |              | SA00         | 0000000h – 001FFFFh    | Sector Starting Address |

| 256                 | 256          | :            | :                      | _                       |

|                     |              | SA255        | 1FE0000h – 1FFFFFFh    | Sector Ending Address   |

#### Table 8. S26KL256S and S26KS256S Sector and Memory Address Map

| Sector Size (kbyte) | Sector Count | Sector Range | Address Range (16-bit) | Notes                   |

|---------------------|--------------|--------------|------------------------|-------------------------|

|                     |              | SA00         | 0000000h – 001FFFFh    | Sector Starting Address |

| 256                 | 128          | :            | :                      | -                       |

|                     |              | SA127        | 0FE0000h – 0FFFFFh     | Sector Ending Address   |

#### Table 9. S26KL128S and S26KS128S Sector and Memory Address Map

| Sector Size (kbyte) | Sector Count | Sector Range | Address Range (16-bit) | Notes                   |

|---------------------|--------------|--------------|------------------------|-------------------------|

|                     |              | SA00         | 0000000h - 001FFFFh    | Sector Starting Address |

| 256                 | 64           | :            | :                      | -                       |

|                     |              | SA63         | 07E0000h – 07FFFFFh    | Sector Ending Address   |

#### Table 10. Main Array Sector 0 Overlaid with Eight 4-kB Parameter-Sectors

| Main Array<br>Sector Size | Parameter-Sector Number                   | Address Size | Address Range (16-bit) | Notes                                               |

|---------------------------|-------------------------------------------|--------------|------------------------|-----------------------------------------------------|

|                           | 0                                         | 4 kB         | 0000000h – 00007FFh    | Start of Parameter-Sector 0                         |

|                           | 1                                         | 4 kB         | 0000800h – 0000FFFh    | Parameter-Sector 1                                  |

|                           | 2                                         | 4 kB         | 0001000h – 00017FFh    | Parameter-Sector 2                                  |

|                           | 3                                         | 4 kB         | 0001800h – 0001FFFh    | Parameter-Sector 3                                  |

| 256 kB                    | 4                                         | 4 kB         | 0002000h – 00027FFh    | Parameter-Sector 4                                  |

|                           | 5                                         | 4 kB         | 0002800h – 0002FFFh    | Parameter-Sector 5                                  |

|                           | 6                                         | 4 kB         | 0003000h – 00037FFh    | Parameter-Sector 6                                  |

|                           | 7                                         | 4 kB         | 0003800h – 0003FFFh    | End of Parameter-Sector 7                           |

|                           | Exposed Portion of Main<br>Array Sector 0 | 224 kB       | 0004000h – 001FFFFh    | Mapped to exposed portion<br>of Main Array Sector 0 |

#### Table 11. Last Sector Overlaid with Eight 4-kB Parameter-Sectors

| Main Array<br>Sector Size | Parameter-Sector Number                      | Address Size | Address Range (16-bit) | Notes                                                    |

|---------------------------|----------------------------------------------|--------------|------------------------|----------------------------------------------------------|

|                           | Exposed portion of last sector in main array | 224 kB       | xx00000h – xx1BFFFh    | Mapped to exposed portion of<br>Main Array Sector (last) |

|                           | 0                                            | 4 kB         | xx1C000h – xx1C7FFh    | Start of Parameter-Sector 0                              |

|                           | 1                                            | 4 kB         | xx1C800h – xx1CFFFh    | Parameter-Sector 1                                       |

|                           | 2                                            | 4 kB         | xx1D000h – xx1D7FFh    | Parameter-Sector 2                                       |

| 256 kB                    | 3                                            | 4 kB         | xx1D800h – xx1DFFFh    | Parameter-Sector 3                                       |

|                           | 4                                            | 4 kB         | xx1E000h – xx1E7FFh    | Parameter-Sector 4                                       |

|                           | 5                                            | 4 kB         | xx1E800h – xx1EFFFh    | Parameter-Sector 5                                       |

|                           | 6                                            | 4 kB         | xx1F000h – xx1F7FFh    | Parameter-Sector 6                                       |

|                           | 7                                            | 4 kB         | xx1F800h – xx1FFFFh    | End of Parameter-Sector 7                                |

# 5.2 Device ID and CFI (ID-CFI) ASO

There are two traditional methods for systems to identify the type of flash memory installed in the system. One is Device Identification (ID). The other method is called Common Flash Interface (CFI).

For ID, a command is used to enable an address space overlay where up to 16 word locations can be read to get JEDEC manufacturer identification (ID), device ID, and some configuration and protection status information from the flash memory. The system can use the manufacturer and device IDs to select the appropriate driver software to use with the flash device.

CFI also uses a command to enable an Address Space Overlay where an extendable table of standard information about how the flash memory is organized and operates can be read. With this method the driver software does not have to be written with the specifics of each possible memory device in mind. Instead the driver software is written in a more general way to handle many different devices but adjusts the driver behavior based on the information in the CFI table.

Traditionally these two address spaces have used separate commands and were separate overlays. However, the mapping of these two address spaces are non-overlapping and so can be combined in to a single address space and appear together in a single overlay. Either of the traditional commands used to access (enter) the Autoselect (ID) or CFI overlay will cause the now combined ID-CFI address map to appear.

The ID-CFI address map appears within, and overlays the Flash Memory Array data of the sector selected by the address used in the ID-CFI enter command. While the ID-CFI ASO is entered the content of all other sectors is undefined.

The ID-CFI address map starts at location zero of the selected sector. Locations above the maximum defined address of the ID-CFI ASO to the maximum address of the selected sector have undefined data. The ID-CFI enter commands use the same address and data values used on previous generation memories to access the JEDEC Manufacturer ID (Autoselect) and Common Flash Interface (CFI) information, respectively.

| Table 12. | ID-CFI | Address | Мар | Overview |

|-----------|--------|---------|-----|----------|

|-----------|--------|---------|-----|----------|

| Word Address          | Description                                  | Read / Write |

|-----------------------|----------------------------------------------|--------------|

| (SA) + 0000h to 000Fh | Device ID<br>(traditional Autoselect values) | Read Only    |

| (SA) + 0010h to 0079h | CFI data structure                           | Read Only    |

| (SA) + 007Ah to 00FFh | Undefined                                    | Read Only    |

For the complete address map see Table 33, ID (Autoselect) Address Map on page 59.

### 5.2.1 Device ID

The Joint Electron Device Engineering Council (JEDEC) standard JEP106T defines the manufacturer ID for a compliant memory. Common industry usage defined a method and format for reading the manufacturer ID and a device specific ID from a memory device. The manufacturer and device ID information is primarily intended for programming equipment to automatically match a device with the corresponding programming algorithm. Cypress has added additional fields within this 32-byte address space.

The original industry format was structured to work with any memory data bus width e.g. x8, x16, x32. The ID code values are traditionally byte wide but are located at bus width address boundaries such that incrementing the device address inputs will read successive byte, word, or double word locations with the ID codes always located in the least significant byte location of the data bus. Because the device data bus is word wide, each code byte is located in the lower half of each word location. The original industry format made the high order byte always zero. Cypress has modified the format to use both bytes in some words of the address space. For the detail description of the Device ID address map see Table 33, ID (Autoselect) Address Map on page 59.

### 5.2.2 Common Flash Memory Interface