Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 32/16 Mbit, 2.6/3.3 V, Dual Boot, Simultaneous Read/Write, Burst Flash

### **General Description**

The Spansion S29CD-J and S29CL-J devices are Floating Gate products fabricated in 110-nm process technology. These burst-mode Flash devices are capable of performing simultaneous read and write operations with zero latency on two separate banks, using separate data and address pins. These products can operate up to 75 MHz (32 Mb) or 66 MHz (16 Mb), and use a single V<sub>CC</sub> of 2.5V to 2.75V (S29CD-J) or 3.0V to 3.6V (S29CL-J) that make them ideal for today's demanding automotive applications.

### **Distinctive Characteristics**

- Single 2.6V (S29CD-J) or 3.3V (S29CL-J) for read/program/erase

- 110 nm Floating Gate Technology

- Simultaneous Read/Write operation with zero latency

- x32 Data Bus

- Dual Boot Sector Configuration (top and bottom)

- Flexible Sector Architecture

- CD016J and CL016J: Eight 2k Double word, Thirty 16k Double word, and Eight 2k Double Word sectors

- CD032J and CL032J: Eight 2k Double word, Sixty-two 16k Double Word, and Eight 2k Double Word sectors

- VersatileI/O<sup>™</sup> control (1.65V to 3.6V)

- Programmable Burst Interface

- Linear for 2, 4, and 8 double word burst with wrap around

- Secured Silicon Sector that can be either factory or customer locked

- 20 year data retention (typical)

- Cycling Endurance: 1 million write cycles per sector (typical)

- Command set compatible with JEDEC (JC42.4) standard

- Supports Common Flash Interface (CFI)

- Extended Temperature range

- Persistent and Password methods of Advanced Sector Protection

- Unlock Bypass program command to reduce programming time

- ACC input pin to reduce factory programming time

- Data Polling bits indicate program and erase operation completion

- Hardware (WP#) protection of two outermost sectors in the large bank

- Ready/Busy (RY/BY#) output indicates data available to system

- Suspend and Resume commands for Program and Erase Operation

- Offered Packages

- 80-pin PQFP

- 80-ball Fortified BGA (13 x 11 mm and 11 x 9mm versions)

- Pb-free package option available

- Known Good Die

### **Performance Characteristics**

| Read Access Times                                |                    |    |    |    |  |  |  |  |

|--------------------------------------------------|--------------------|----|----|----|--|--|--|--|

| Speed Option (MHz)                               | 75<br>(32 Mb only) | 66 | 56 | 40 |  |  |  |  |

| Max Asynch. Access Time, ns (t <sub>ACC</sub> )  | 54                 | 54 | 54 | 54 |  |  |  |  |

| Max Synch. Burst Access, ns (t <sub>BACC</sub> ) | 8                  | 8  | 8  | 8  |  |  |  |  |

| Min Initial Clock Delay (clock cycles)           | 5                  | 5  | 5  | 4  |  |  |  |  |

| Max CE# Access Time, ns (t <sub>CE</sub> )       | 54                 | 54 | 54 | 54 |  |  |  |  |

| Max OE# Access time, ns (t <sub>OE</sub> )       | 20                 | 20 | 20 | 20 |  |  |  |  |

| Current Consumption (Max values) |       |  |  |  |  |

|----------------------------------|-------|--|--|--|--|

| Continuous Burst Read @ 75 MHz   | 90 mA |  |  |  |  |

| Program                          | 50 mA |  |  |  |  |

| Erase                            | 50 mA |  |  |  |  |

| Standby Mode                     | 60 μΑ |  |  |  |  |

| Typical Program and Erase Times |       |  |  |  |  |

|---------------------------------|-------|--|--|--|--|

| Double Word Programming         | 18 μs |  |  |  |  |

| Sector Erase                    | 1.0 s |  |  |  |  |

### Notice for the 32Mb S29CD-J and S29CL-J devices only:

Please refer to the application note "Recommended Mode of Operation for Spansion® 110 nm S29CD032J/S29CL032J Flash Memory" publication number S29CD-CL032J Recommend AN for programming best practices.

Cypress Semiconductor Corporation

Document Number: 002-00948 Rev. \*A

### **Contents**

| <b>1.</b><br>1.1                       | Ordering Information                                                                                                                                               |                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.                                     | Input/Output Descriptions and Logic Symbols                                                                                                                        | . 5                        |

| 3.                                     | Block Diagram                                                                                                                                                      | . 6                        |

| 4.                                     | Block Diagram of Simultaneous Read/Write Circuit.                                                                                                                  | . 7                        |

| <b>5.</b><br>5.1<br>5.2                | Physical Dimensions/Connection Diagrams                                                                                                                            | . E                        |

| 5.3<br>5.4<br>5.5                      | 80-Ball Fortified BGA Connection Diagrams<br>Special Package Handling Instructions<br>LAA080–80-ball Fortified Ball Grid Array (13 x 11 mm)<br>Physical Dimensions | 10                         |

| 5.6                                    | LAD080–80-ball Fortified Ball Grid Array (11 x 9 mm) Physical Dimensions                                                                                           | 12                         |

| 6.<br>6.1<br>6.2<br>6.3<br>6.4         | Additional Resources  Application Notes  Specification Bulletins  Hardware and Software Support  Contacting Spansion                                               | 13<br>13<br>13<br>13       |

| <b>7.</b><br>7.1                       | Product Overview                                                                                                                                                   | 14<br>14                   |

| 8.<br>8.1<br>8.2<br>8.3<br>8.4         | Device Operations                                                                                                                                                  | 19<br>19<br>20<br>20       |

| 8.5<br>8.6<br>8.7<br>8.8<br>8.9        | Register                                                                                                                                                           | 26<br>26<br>31             |

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6 | Dynamic Protection Bits Password Protection Method                                                                                                                 | 39<br>39<br>41<br>41       |

|                                        | , 3                                                                                                                                                                | 44<br>45<br>45             |

| 11.                                    | Electronic Marking                                                                                                                                                 | 45                         |

| 12.2<br>12.3                           | Power Conservation Modes  Standby Mode  Automatic Sleep Mode  Hardware RESET# Input Operation                                                                      | 45<br>45<br>46<br>46<br>46 |

|      | Electrical Specifications                         |    |

|------|---------------------------------------------------|----|

| 13.1 | Absolute Maximum Ratings                          |    |

| 14.  | Operating Ranges                                  | 48 |

| 15.  | DC Characteristics                                |    |

| 15.1 | Zero Power Flash                                  | 49 |

| 16.  | Test Conditions                                   | 50 |

| 17.  | Test Specifications                               | 50 |

| 17.1 | Switching Waveforms                               | 50 |

| 18.  | AC Characteristics                                | 51 |

|      | V <sub>CC</sub> and V <sub>IO</sub> Power-up      |    |

|      | Asynchronous Operations                           |    |

|      | Synchronous Operations                            |    |

|      | Hardware Reset (RESET#)                           |    |

| 18.5 | Write Protect (WP#)                               | 57 |

| 18.6 | Erase/Program Operations                          | 57 |

|      | Alternate CE# Controlled Erase/Program Operations |    |

|      | Erase and Programming Performance                 |    |

| 18.9 | PQFP and Fortified BGA Pin Capacitance            | טט |

| 19.  | Appendix 1                                        | 67 |

| 19.1 | Common Flash Memory Interface (CFI)               | 67 |

| 20.  | Appendix 2                                        | 71 |

| 20.1 | Command Definitions                               | 71 |

| 21.  | Revision History                                  | 73 |

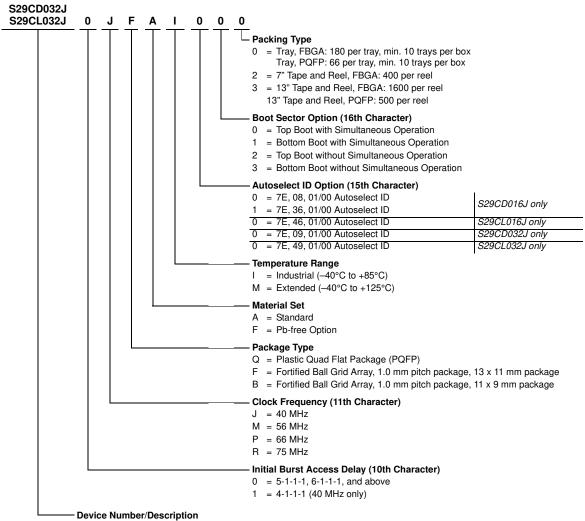

### 1. Ordering Information

The order number (Valid Combination) is formed by the following:

S29CD032J/S29CD016J (2.5 volt-only), S29CL032J/S29CL016J (3.3 volt-only)

32 or 16 Megabit (1M or  $512k \times 32$ -Bit) CMOS Burst Mode, Dual Boot, Simultaneous Read/Write Flash Memory Manufactured on 110 nm floating gate technology

### 1.1 Valid Combinations

Valid Combinations lists configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

|                  |                               |                    | S29CD-J/C       | L-J Valid C     | ombinations          |                         |                       |                 |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|------------------|-------------------------------|--------------------|-----------------|-----------------|----------------------|-------------------------|-----------------------|-----------------|-----|-----|-----|-----|--------|---|---|---|------|------|------|--|--|------------|---------|

| Device<br>Number | Initial Burst<br>Access Delay | Clock<br>Frequency | Package<br>Type | Material<br>Set | Temperature<br>Range | Autoselect ID<br>Option | Boot Sector<br>Option | Packing<br>Type |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | 0, 1                          | J                  | Q               |                 |                      |                         |                       | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| S29CD016J        | 0, 1                          | J                  | B, F            |                 |                      | 0, 1                    |                       | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| 323000100        | 0                             | M, P               | Q               |                 |                      | 0, 1                    |                       | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | U                             | IVI, F             | B, F            |                 |                      |                         |                       | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | 0, 1                          | J                  | Q               |                 |                      |                         |                       | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| S29CL016J        | 0, 1                          | J                  | B, F            |                 |                      |                         | 0, 1, 2, 3            | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| 329CL010J        | 0                             | M, P               | Q               |                 |                      |                         | 0, 1, 2, 3            | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | U                             | IVI, F             | B, F            |                 |                      |                         |                       | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | 0, 1                          | 0.1                | 0.1             | 0.1             | 0.1                  | 0.1                     | 0.1                   | 0.1             | 0.1 | 0.1 | 0.1 | 0.1 | 0, 1 J | Q |   |   |      |      | 0, 3 |  |  |            |         |

|                  |                               | J                  | B, F            | A, F            |                      |                         |                       | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | 0                             | M, P               | Q               |                 |                      |                         |                       | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| S29CD032J        |                               |                    | B, F            |                 | I, M                 | 0                       |                       | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| 329000320        |                               |                    | Q<br>B, F       |                 |                      |                         | 0, 1 (2)              | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  |                               | R                  |                 |                 |                      |                         | 2, 3                  |                 |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  |                               |                    |                 |                 |                      |                         | 0, 1 (2)              |                 |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  |                               |                    | Б, Г            |                 |                      |                         | 2, 3                  | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | 0.1                           | J                  | Q               |                 |                      |                         |                       | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | 0, 1                          | J                  | J               | J               | J                    | J                       | J                     | J               | J   | J   | J   | J   | J      | J | J | J | B, F | B, F |      |  |  | 0, 1, 2, 3 | 0, 2, 3 |

|                  |                               | M, P               | Q               |                 |                      |                         | 0, 1, 2, 3            | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| S29CL032J        |                               | IVI, F             | B, F            |                 |                      |                         |                       | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

| 329CL032J        | 0                             |                    | Q               |                 |                      |                         | 0, 1 (2)              | 0, 3            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  | U                             | R                  | ų ų             |                 |                      |                         | 2, 3                  |                 |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  |                               | , R                | D E             |                 |                      |                         | 0, 1 (2)              | 0.00            |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

|                  |                               |                    | B, F            |                 |                      |                         | 2, 3                  | 0, 2, 3         |     |     |     |     |        |   |   |   |      |      |      |  |  |            |         |

### Notes:

<sup>1.</sup> The ordering part number that appears on BGA packages omits the leading "S29".

<sup>2.</sup> Contact factory for availability.

# 2. Input/Output Descriptions and Logic Symbols

Table identifies the input and output package connections provided on the device.

| Symbol          | Туре       | Description                                                                                                                                                                                                                                                                                           |

|-----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A19-A0          | Input      | Address lines for S29CD-J and S29CL-J (A18-A0 for 16 Mb and A19-A0 for 32 Mb). A9 supports 12V autoselect input.                                                                                                                                                                                      |

| DQ31-DQ0        | I/O        | Data input/output                                                                                                                                                                                                                                                                                     |

| CE#             | Input      | Chip Enable. This signal is asynchronous relative to CLK for the burst mode.                                                                                                                                                                                                                          |

| OE#             | Input      | Output Enable. This signal is asynchronous relative to CLK for the burst mode.                                                                                                                                                                                                                        |

| WE#             | Input      | Write Enable                                                                                                                                                                                                                                                                                          |

| V <sub>CC</sub> | Supply     | Device Power Supply. This signal is asynchronous relative to CLK for the burst mode.                                                                                                                                                                                                                  |

| V <sub>IO</sub> | Supply     | VersatileI/O <sup>™</sup> Input.                                                                                                                                                                                                                                                                      |

| V <sub>SS</sub> | Supply     | Ground                                                                                                                                                                                                                                                                                                |

| NC              | No Connect | Not connected internally                                                                                                                                                                                                                                                                              |

| RY/BY#          | Output     | Ready/Busy output and open drain which require a external pull up resistor. When RY/BY# = $V_{OH}$ , the device is ready to accept read operations and commands. When RY/BY# = $V_{OL}$ , the device is either executing an embedded algorithm or the device is executing a hardware reset operation. |

| CLK             | Input      | Clock Input that can be tied to the system or microprocessor clock and provides the fundamental timing and internal operating frequency.                                                                                                                                                              |

| ADV#            | Input      | Load Burst Address input. Indicates that the valid address is present on the address inputs.                                                                                                                                                                                                          |

| IND#            | Output     | End of burst indicator for finite bursts only. IND is low when the last word in the burst sequence is at the data outputs.                                                                                                                                                                            |

| WAIT#           | Output     | Provides data valid feedback only when the burst length is set to continuous.                                                                                                                                                                                                                         |

| WP#             | Input      | Write Protect Input. At $V_{\text{IL}}$ , disables program and erase functions in two outermost sectors of the large bank.                                                                                                                                                                            |

| ACC             | Input      | Acceleration input. At $V_{HH}$ , accelerates erasing and programming. When not used for acceleration, ACC = $V_{SS}$ or $V_{CC}$ .                                                                                                                                                                   |

| RESET#          | Input      | Hardware Reset.                                                                                                                                                                                                                                                                                       |

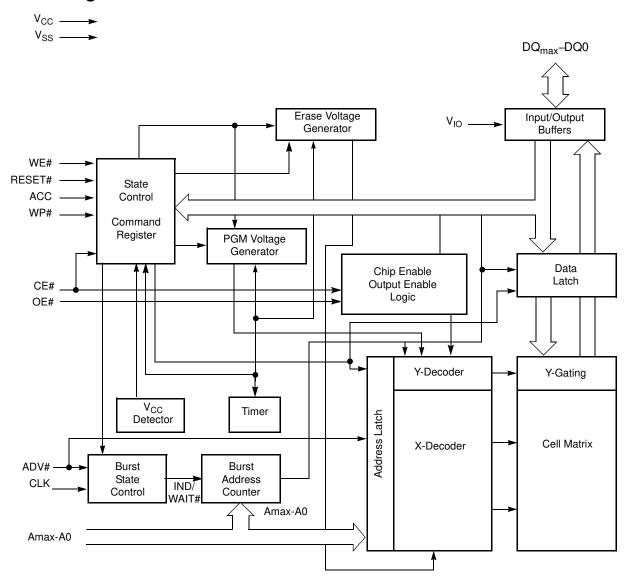

# 3. Block Diagram

**Note**Address bus is A19–A0 for 32 Mb device, A18–A0 for 16 Mb device. Data bus is D31–DQ0.

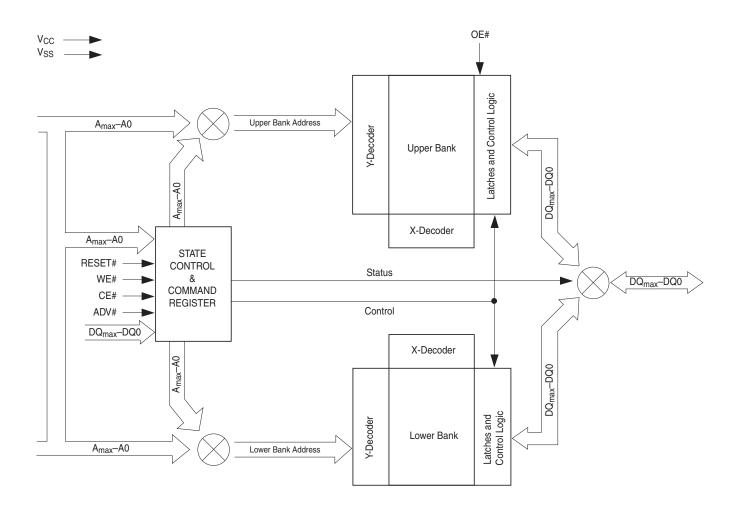

## 4. Block Diagram of Simultaneous Read/Write Circuit

### 5. Physical Dimensions/Connection Diagrams

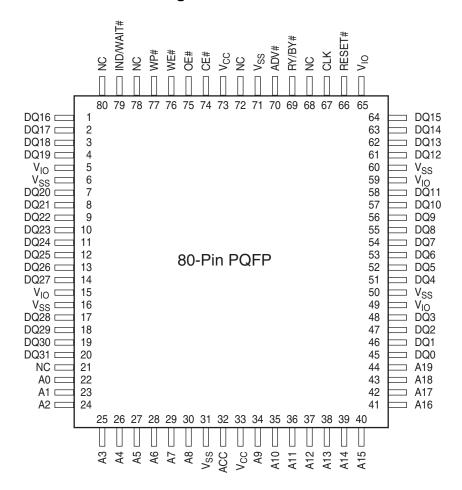

### 5.1 80-Pin PQFP Connection Diagram

#### Notes

- 1. On 16 Mb device, pin 44 (A19) is NC.

- 2. Pin 69 (RY/BY#) is Open Drain and requires an external pull-up resistor.

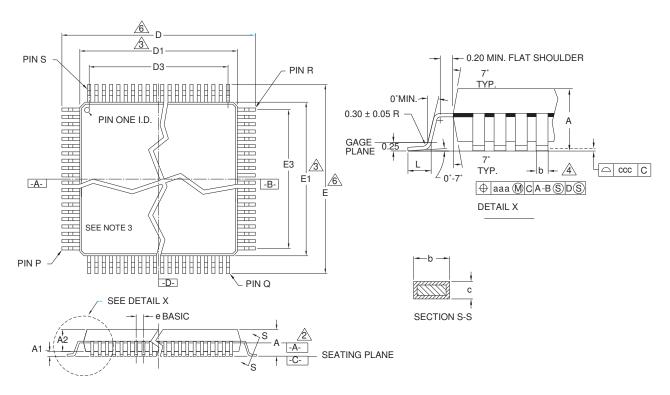

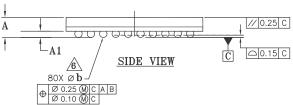

#### 5.2 PQR080-80-Lead Plastic Quad Flat Package Physical Dimensions

| PACKAGE |       | PQR 080     |       |                   |

|---------|-------|-------------|-------|-------------------|

| JEDEC   | N     | IO-108(B)CB | -1    | NOTES             |

| SYMBOL  | MIN   | NOM         | MAX   |                   |

| Α       |       |             | 3.35  |                   |

| A1      | 0.25  |             |       |                   |

| A2      | 2.70  | 2.80        | 2.90  |                   |

| b       | 0.30  |             | 0.45  | SEE NOTE 4        |

| С       | 0.15  |             | 0.23  |                   |

| D       | 17.00 | 17.20       | 17.40 |                   |

| D1      | 13.90 | 14.00       | 14.10 | SEE NOTE 3        |

| D3      |       | 12.0        | RE    | REFERENCE         |

| е       |       | 0.80        |       | BASIC, SEE NOTE 7 |

| Е       | 23.00 | 23.20       | 23.40 |                   |

| E1      | 19.90 | 20.00       | 20.10 | SEE NOTE 3        |

| E3      |       | 18.40       |       | REFERENCE         |

| aaa     |       | 0.20        |       |                   |

| ccc     |       | 0.10        |       |                   |

| L       | 0.73  | 0.88        | 1.03  |                   |

| Р       |       | 24          |       |                   |

| Q       |       | 40          |       |                   |

| R       |       | 64          |       |                   |

| S       |       | 80          |       |                   |

#### NOTES:

ALL DIMENSIONS AND TOLERANCES CONFORM TO ANSI Y14.5M-1982.

DATUM PLANE  $\fbox{-A-}$  IS LOCATED AT THE MOLD PARTING LINE AND IS COINCIDENT WITH THE BOTTOM OF THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY.

3. DIMENSIONS "D1" AND "E1" DO NOT INCLUD MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. DIMENSIONS "D1" AND "E1" INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -A-

4. DIMENSION "B" DOES NOT INCLUDE DAMBAR PROTRUSION.

5. CONTROLLING DIMENSIONS: MILLIMETER.

6. DIMENSIONS "D" AND "E" ARE MEASURED FROM BOTH INNERMOST AND OUTERMOST POINTS.

- DEVIATION FROM LEAD-TIP TRUE POSITION SHALL BE WITHIN  $\pm 0.0076$  mm FOR PITCH > 0.5 mm AND WITHIN  $\pm 0.04$  FOR PITCH ≤ 0.5 mm.

- 8. LEAD COPLANARITY SHALL BE WITHIN: (REFER TO 06-500) 1 - 0.10 mm FOR DEVICES WITH LEAD PITCH OF 0.65 - 0.80 mm 2 -  $0.076\ mm$  FOR DEVICES WITH LEAD PITCH OF  $0.50\ mm$  . COPLANARITY IS MEASURED PER SPECIFICATION 06-500.

- HALF SPAN (CENTER OF PACKAGE TO LEAD TIP) SHALL BE WITHIN ±0.0085".

3213\38.4C

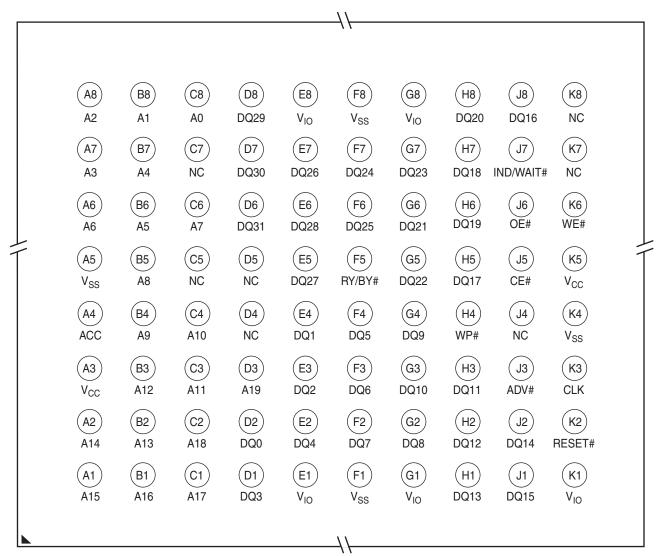

### 5.3 80-Ball Fortified BGA Connection Diagrams

#### Notes

### 5.4 Special Package Handling Instructions

Special handling is required for Flash Memory products in molded packages (BGA). The package and/or data integrity may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

<sup>1.</sup> On 16 Mb device, ball D3 (A19) is NC.

<sup>2.</sup> Ball F5 (RY/BY#) is Open Drain and requires an external pull-up resistor.

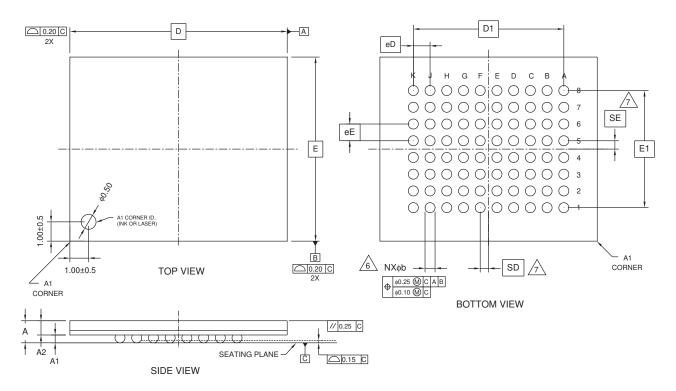

### 5.5 LAA080-80-ball Fortified Ball Grid Array (13 x 11 mm) Physical Dimensions

| PACKAGE | LAA 080   |                           |      |                          |  |  |

|---------|-----------|---------------------------|------|--------------------------|--|--|

| JEDEC   |           | N/A                       |      |                          |  |  |

|         | 13        | 0.00 x 11.00 n<br>PACKAGE | nm   | NOTE                     |  |  |

| SYMBOL  | MIN       | NOM                       | MAX  |                          |  |  |

| Α       |           |                           | 1.40 | PROFILE HEIGHT           |  |  |

| A1      | 0.40      |                           |      | STANDOFF                 |  |  |

| A2      | 0.60      |                           |      | BODY THICKNESS           |  |  |

| D       |           | 13.00 BSC.                |      | BODY SIZE                |  |  |

| E       |           | 11.00 BSC.                |      | BODY SIZE                |  |  |

| D1      |           | 9.00 BSC.                 |      | MATRIX FOOTPRINT         |  |  |

| E1      |           | 7.00 BSC.                 |      | MATRIX FOOTPRINT         |  |  |

| MD      |           | 10                        |      | MATRIX SIZE D DIRECTION  |  |  |

| ME      |           | 8                         |      | MATRIX SIZE E DIRECTION  |  |  |

| N       |           | 80                        |      | BALL COUNT               |  |  |

| фЬ      | 0.50      | 0.60                      | 0.70 | BALL DIAMETER            |  |  |

| eD      | 1.00 BSC. |                           |      | BALL PITCH - D DIRECTION |  |  |

| еE      | 1.00 BSC. |                           |      | BALL PITCH - E DIRECTION |  |  |

| SD/SE   |           | 0.50 BSC                  |      | SOLDER BALL PLACEMENT    |  |  |

### NOTES:

- DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JESD 95-1, SPP-010 (EXCEPT AS NOTED).

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL ROW MATRIX SIZE IN THE "D" DIRECTION. SYMBOL "ME" IS THE BALL COLUMN MATRIX SIZE IN THE "E" DIRECTION. N IS THE TOTAL NUMBER OF SOLDER BALLS.

- DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

- SD AND SE ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW. WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW PARALLEL TO THE D OR E DIMENSION, RESPECTIVELY, SD OR SE = 0.000. WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, SD OR SE = |0/2|

- 8. N/A

- 9. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

3214\38.12C

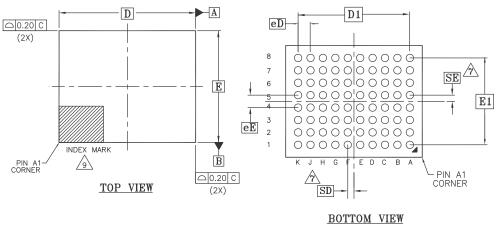

#### 5.6 LAD080-80-ball Fortified Ball Grid Array (11 x 9 mm) Physical Dimensions

| PACKAGE |               | LAD 080                 |            |                          |   |  |

|---------|---------------|-------------------------|------------|--------------------------|---|--|

| JEDEC   |               | N/A                     |            |                          |   |  |

| DXE     | 11.0          | 00 mm x 9.00<br>PACKAGE | mm         |                          |   |  |

| SYMBOL  | MIN           | NOM                     | MAX        | NOTE                     | 1 |  |

| A       |               |                         | 1.40       | PROFILE                  | 1 |  |

| A1      | 0.35          | 0.45                    | 0.55       | BALL HEIGHT              | 1 |  |

| D       |               | 11.00 BSC               |            | BODY SIZE                | 1 |  |

| E       |               | 9.00 BSC                |            | BODY SIZE                | 1 |  |

| D1      |               | 9.00 BSC                |            | MATRIX FOOTPRINT         |   |  |

| E1      |               | 7.00 BSC                |            | MATRIX FOOTPRINT         | 1 |  |

| MD      |               | 10                      |            | MATRIX SIZE D DIRECTION  | 1 |  |

| ME      |               | 8                       |            | MATRIX SIZE E DIRECTION  | ] |  |

| N       | 80 BALL COUNT |                         | BALL COUNT | ]                        |   |  |

| Øb      | 0.55          | 0.65                    | 0.75       | BALL DIAMETER            | 1 |  |

| еE      | 1.00 BSC      |                         |            | BALL PITCH               |   |  |

| eD      | 1.00 BSC      |                         |            | BALL PITCH               |   |  |

| SD/SE   |               | 0.50 BSC                |            | SOLDER BALL PLACEMENT    |   |  |

|         |               | N/A                     |            | DEPOPULATED SOLDER BALLS | 1 |  |

|         |               |                         |            |                          |   |  |

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING METHODS PER ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JEP95, SECTION 4.3, SPP-010.

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH.

- 5. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

- SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

- N IS THE NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- © DIMENSION "5" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

DIAMETER IN A PLANE PARALLEL TO DATUM C.

DIAMETER IN A PLANE PARALLEL TO DATUM C.

AND BE AND SEE ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

- WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW  $\fbox{SD}$  OR  $\fbox{SE}$  = 0.000.

- WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, SD OR SE = e/2

- "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS. 41 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

### 6. Additional Resources

Visit www.spansion.com to obtain the following related documents:

### 6.1 Application Notes

The following is a list of application notes related to this product. All Spansion application notes are available at http://www.spansion.com/Support/TechnicalDocuments/Pages/ApplicationNotes.aspx

- Using the Operation Status Bits in AMD Devices

- Understanding Page Mode Flash Memory Devices

- Common Flash Interface Version 1.4 Vendor Specific Extensions

### 6.2 Specification Bulletins

Contact your local sales office for details.

### 6.3 Hardware and Software Support

Downloads and related information on Flash device support is available at http://www.spansion.com/SUPPORT/Pages/Support.aspx

- Spansion low-level drivers

- Enhanced Flash drivers

- Flash file system

Downloads and related information on simulation modeling and CAD modeling support is available at http://www.spansion.com/Support/Pages/SimulationModels.aspx

VHDL and Verilog

- IBIS

- ORCAD

### 6.4 Contacting Spansion

Obtain the latest list of company locations and contact information on our web site at http://www.spansion.com/About/Pages/Locations.aspx

### 7. Product Overview

The S29CD-J and S29CL-J families consist of 32 Mb and 16 Mb, 2.6 volt-only (CD-J) or 3.3 volt-only (CL-J), simultaneous read/write, dual boot burst mode Flash devices optimized for today's automotive designs.

These devices are organized in 1,048,576 double words (32 Mb) or 524,288 double words (16 Mb) and are capable of linear burst read (2, 4, or 8 double words) with wraparound. (Note that 1 double word = 32 bits.) These products also offer single word programming with program/erase suspend and resume functionality. Additional features include:

- Advanced Sector Protection methods for protecting sectors as required.

- 256 bytes of Secured Silicon area for storing customer or factory secured information. The Secured Silicon Sector is One-Time Programmable.

- Electronic marking.

### 7.1 Memory Map

The S29CD-J and S29CL-J devices consist of two banks organized as shown in Table , Table , Table and Table .

Document Number: 002-00948 Rev. \*A

### S29CD016J/CL016J (Top Boot) Sector and Memory Address Map

|              | Sector          | Sector<br>Group | x32 Address<br>Range (A18:A0) | Sector Size<br>(KDwords) |                 | Sector           | Sector<br>Group | x32 Address Range<br>(A18:A0) | Sector Size<br>(KDwords) |

|--------------|-----------------|-----------------|-------------------------------|--------------------------|-----------------|------------------|-----------------|-------------------------------|--------------------------|

|              | SA0<br>(Note 1) | SG0             | 00000h-007FFh                 | 2                        |                 | SA15             |                 | 20000h-23FFFh                 | 16                       |

|              | SA1             | SG1             | 00800h-00FFFh                 | 2                        |                 | SA16             | SG10            | 24000h-27FFFh                 | 16                       |

|              | SA2             | SG2             | 01000h-017FFh                 | 2                        |                 | SA17             |                 | 28000h–2BFFFh                 | 16                       |

|              | SA3             | SG3             | 01800h-01FFFh                 | 2                        |                 | SA18             |                 | 2C000h-2FFFFh                 | 16                       |

|              | SA4             | SG4             | 02000h-027FFh                 | 2                        |                 | SA19             |                 | 30000h-33FFFh                 | 16                       |

| e 2)         | SA5             | SG5             | 02800h-02FFFh                 | 2                        |                 | SA20             | 0011            | 34000h-37FFFh                 | 16                       |

| Not          | SA6             | SG6             | 03000h-037FFh                 | 2                        |                 | SA21             | - SG11          | 38000h-3BFFFh                 | 16                       |

| Bank 0 (Note | SA7             | SG7             | 03800h-03FFFh                 | 2                        |                 | SA22             |                 | 3C000h-3FFFFh                 | 16                       |

| ank          | SA8             |                 | 04000h-07FFFh                 | 16                       |                 | SA23             |                 | 40000h-43FFFh                 | 16                       |

| "            | SA9             | SG8             | 08000h-0BFFFh                 | 16                       |                 | SA24             | 0010            | 44000h-47FFFh                 | 16                       |

|              | SA10            |                 | 0C000h-0FFFFh                 | 16                       |                 | SA25             | SG12            | 48000h–4BFFFh                 | 16                       |

|              | SA11            |                 | 10000h-13FFFh                 | 16                       |                 | SA26             |                 | 4C000h-4FFFFh                 | 16                       |

|              | SA12            | 000             | 14000h-17FFFh                 | 16                       |                 | SA27             |                 | 50000h-53FFFh                 | 16                       |

|              | SA13            | SG9             | 18000h-1BFFFh                 | 16                       |                 | SA28             | 0040            | 54000h-57FFFh                 | 16                       |

|              | SA14            |                 | 1C000h-1FFFFh                 | 16                       | te 2            | SA29             | SG13            | 58000h-5BFFFh                 | 16                       |

|              |                 |                 |                               | •                        | N <sub>O</sub>  | SA30             |                 | 5C000h-5FFFFh                 | 16                       |

|              |                 |                 |                               |                          | Bank 1 (Note 2) | SA31             |                 | 60000h-63FFFh                 | 16                       |

|              |                 |                 |                               |                          | Bar             | SA32             | SG14            | 64000h-67FFFh                 | 16                       |

|              |                 |                 |                               |                          |                 | SA33             | 3014            | 68000h-6BFFFh                 | 16                       |

|              |                 |                 |                               |                          |                 | SA34             |                 | 6C000h-6FFFFh                 | 16                       |

|              |                 |                 |                               |                          |                 | SA35             |                 | 70000h-73FFFh                 | 16                       |

|              |                 |                 |                               |                          |                 | SA36             | SG15            | 74000h-77FFFh                 | 16                       |

|              |                 |                 |                               |                          |                 |                  |                 | 78000h–7BFFFh                 | 16                       |

|              |                 |                 |                               |                          |                 | SA38             | SG16            | 7C000h-7C7FFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA39             | SG17            | 7C800h-7CFFFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA40             | SG18            | 7D000h-7D7FFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA41             | SG19            | 7D800h-7DFFFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA42             | SG20            | 7E000h-7E7FFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA43             | SG21            | 7E800h-7EFFFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA44<br>(Note 3) | SG22            | 7F000h-7F7FFh                 | 2                        |

|              |                 |                 |                               |                          |                 | SA45<br>(Note 3) | SG23            | 7F800h–7FFFFh                 | 2                        |

#### Notes

- 1. Secured Silicon Sector overlays this sector when enabled.

- 2. The bank address is determined by A18 and A17. BA = 00 for Bank 0 and BA = 01, 10, or 11 for Bank 1.

- 3. This sector has the additional WP# pin sector protection feature.

### S29CD016J/CL016J (Bottom Boot) Sector and Memory Address Map

|   | Sector       | Sector<br>Group | x32 Address<br>Range (A18:A0) | Sector Size<br>(KDwords) |           | Sector           | Sector<br>Group | x32<br>Address Range<br>(A18:A0) | Sector Size<br>(KDwords) |

|---|--------------|-----------------|-------------------------------|--------------------------|-----------|------------------|-----------------|----------------------------------|--------------------------|

|   | SA0 (Note 1) | SG0             | 00000h-007FFh                 | 2                        |           | SA31             |                 | 60000h-63FFFh                    | 16                       |

|   | SA1 (Note 1) | SG1             | 00800h-00FFFh                 | 2                        | 1         | SA32             | - SG14          | 64000h-67FFFh                    | 16                       |

|   | SA2          | SG2             | 01000h-017FFh                 | 2                        |           | SA33             | 3014            | 68000h-6BFFFh                    | 16                       |

|   | SA3          | SG3             | 01800h-01FFFh                 | 2                        |           | SA34             |                 | 6C000h-6FFFFh                    | 16                       |

|   | SA4          | SG4             | 02000h-027FFh                 | 2                        | 1         | SA35             |                 | 70000h-73FFFh                    | 16                       |

|   | SA5          | SG5             | 02800h-02FFFh                 | 2                        |           | SA36             | SG15            | 74000h-77FFFh                    | 16                       |

|   | SA6          | SG6             | 03000h-037FFh                 | 2                        | te 2)     | SA37             |                 | 78000h–7BFFFh                    | 16                       |

|   | SA7          | SG7             | 03800h-03FFFh                 | 2                        | (Note     | SA38             | SG16            | 7C000h-7C7FFh                    | 2                        |

|   | SA8          | SG8             | 04000h-07FFFh                 | 16                       | <u>لا</u> | SA39             | SG17            | 7C800h-7CFFFh                    | 2                        |

|   | SA9          |                 | 08000h-0BFFFh                 | 16                       | Bank 1    | SA40             | SG18            | 7D000h-7D7FFh                    | 2                        |

| ľ | SA10         |                 | 0C000h-0FFFFh                 | 16                       |           | SA41             | SG19            | 7D800h-7DFFFh                    | 2                        |

|   | SA11         |                 | 10000h-13FFFh                 | 16                       | 1         | SA42             | SG20            | 7E000h-7E7FFh                    | 2                        |

|   | SA12         |                 | 14000h-17FFFh                 | 16                       |           | SA43             | SG21            | 7E800h-7EFFFh                    | 2                        |

|   | SA13         | SG9             | 18000h-1BFFFh                 | 16                       |           | SA44             | SG22            | 7F000h-7F7FFh                    | 2                        |

|   | SA14         |                 | 1C000h-1FFFFh                 | 16                       |           | SA45<br>(Note 3) | SG23            | 7F800h–7FFFFh                    | 2                        |

| ) | SA15         |                 | 20000h-23FFFh                 | 16                       |           |                  | •               |                                  |                          |

|   | SA16         | 0040            | 24000h-27FFFh                 | 16                       | 1         |                  |                 |                                  |                          |

| 1 | SA17         | SG10            | 28000h-2BFFFh                 | 16                       | 1         |                  |                 |                                  |                          |

|   | SA18         |                 | 2C000h-2FFFFh                 | 16                       |           |                  |                 |                                  |                          |

|   | SA19         |                 | 30000h-33FFFh                 | 16                       | 1         |                  |                 |                                  |                          |

|   | SA20         | 0011            | 34000h-37FFFh                 | 16                       |           |                  |                 |                                  |                          |

|   | SA21         | SG11            | 38000h-3BFFFh                 | 16                       | 1         |                  |                 |                                  |                          |

|   | SA22         | ]               | 3C000h-3FFFFh                 | 16                       | 1         |                  |                 |                                  |                          |

|   | SA23         |                 | 40000h-43FFFh                 | 16                       |           |                  |                 |                                  |                          |

|   | 0.10.1       | 1               | 440001 47555                  | 40                       | 1         |                  |                 |                                  |                          |

16

16

16

16

16

16

16

### Notes

SA24

SA25

SA26

**SA27**

SA28

**SA29**

SA30

1. This sector has the additional WP# pin sector protection feature.

SG13

SG12

2. The bank address is determined by A18 and A17. BA = 00, 01, or 10 for Bank 0 and BA = 11 for Bank 1.

44000h-47FFh

48000h-4BFFFh

4C000h-4FFFFh

50000h-53FFFh

54000h-57FFFh

58000h-5BFFFh

5C000h-5FFFFh

3. Secured Silicon Sector overlays this sector when enabled.

### S29CD032J/CL032J (Top Boot) Sector and Memory Address Map

| Sector       | Sector<br>Group | x32 Address Range<br>(A19:A0) | Sector Size<br>(KDwords) | Sector        | Sector<br>Group | x32 Address Range<br>(A19:A0) | Sector Size<br>(KDwords) |

|--------------|-----------------|-------------------------------|--------------------------|---------------|-----------------|-------------------------------|--------------------------|

|              | В               | ank 0 (Note 2)                |                          |               | Bank 1          | continued (Note 2)            |                          |

| SA0 (Note 1) | SG0             | 00000h-007FFh                 | 2                        | SA39          |                 | 80000h-83FFFh                 | 16                       |

| SA1          | SG1             | 00800h-00FFFh                 | 2                        | SA40          | 0010            | 84000h-87FFFh                 | 16                       |

| SA2          | SG2             | 01000h-017FFh                 | 2                        | SA41          | SG16            | 88000h-8BFFFh                 | 16                       |

| SA3          | SG3             | 01800h-01FFFh                 | 2                        | SA42          |                 | 8C000h-8FFFFh                 | 16                       |

| SA4          | SG4             | 02000h-027FFh                 | 2                        | SA43          |                 | 90000h-93FFFh                 | 16                       |

| SA5          | SG5             | 02800h-02FFFh                 | 2                        | SA44          | 0017            | 94000h-97FFFh                 | 16                       |

| SA6          | SG6             | 03000h-037FFh                 | 2                        | SA45          | SG17            | 98000h-9BFFFh                 | 16                       |

| SA7          | SG7             | 03800h-03FFFh                 | 2                        | SA46          |                 | 9C000h-9FFFFh                 | 16                       |

| SA8          |                 | 04000h-07FFFh                 | 16                       | SA47          |                 | A0000h-A3FFFh                 | 16                       |

| SA9          | SG8             | 08000h-0BFFFh                 | 16                       | SA48          | 0040            | A4000h-A7FFFh                 | 16                       |

| SA10         |                 | 0C000h-0FFFFh                 | 16                       | SA49          | SG18            | A8000h-ABFFFh                 | 16                       |

| SA11         |                 | 10000h-13FFFh                 | 16                       | SA50          |                 | AC000h-AFFFFh                 | 16                       |

| SA12         | 000             | 14000h-17FFFh                 | 16                       | SA51          |                 | B0000h-B3FFFh                 | 16                       |

| SA13         | SG9             | 18000h-1BFFFh                 | 16                       | SA52          | 9010            | B4000h-B7FFFh                 | 16                       |

| SA14         |                 | 1C000h-1FFFFh                 | 16                       | SA53          | SG19            | B8000h-BBFFFh                 | 16                       |

| SA15         |                 | 20000h-23FFFh                 | 16                       | SA54          |                 | BC000h-BFFFFh                 | 16                       |

| SA16         | SG10            | 24000h-27FFFh                 | 16                       | SA55          |                 | C0000h-C3FFFh                 | 16                       |

| SA17         |                 | 28000h-2BFFFh                 | 16                       | SA56          | 0000            | C4000h-C7FFFh                 | 16                       |

| SA18         |                 | 2C000h-2FFFFh                 | 16                       | SA57          | - SG20          | C8000h-CBFFFh                 | 16                       |

| SA19         |                 | 30000h-33FFFh                 | 16                       | SA58          |                 | CC000h-CFFFFh                 | 16                       |

| SA20         |                 | 34000h-37FFFh                 | 16                       | SA59          |                 | D0000h-D3FFFh                 | 16                       |

| SA21         | - SG11          | 38000h-3BFFFh                 | 16                       | SA60          |                 | D4000h-D7FFFh                 | 16                       |

| SA22         |                 | 3C000h-3FFFFh                 | 16                       | SA61          | SG21            | D8000h-DBFFFh                 | 16                       |

|              | В               | ank 1 (Note 2)                | •                        | SA62          |                 | DC000h-DFFFFh                 | 16                       |

| SA23         |                 | 40000h-43FFFh                 | 16                       | SA63          |                 | E0000h-E3FFFh                 | 16                       |

| SA24         | 0010            | 44000h-47FFFh                 | 16                       | SA64          | 0000            | E4000h-E7FFFh                 | 16                       |

| SA25         | - SG12          | 48000h-4BFFFh                 | 16                       | SA65          | SG22            | E8000h-EBFFFh                 | 16                       |

| SA26         |                 | 4C000h-4FFFFh                 | 16                       | SA66          |                 | EC000h-EFFFFh                 | 16                       |

| SA27         |                 | 50000h-53FFFh                 | 16                       | SA67          |                 | F0000h-F3FFFh                 | 16                       |

| SA28         | 0010            | 54000h-57FFFh                 | 16                       | SA68          | SG23            | F4000h-F7FFFh                 | 16                       |

| SA29         | - SG13          | 58000h-5BFFFh                 | 16                       | SA69          |                 | F8000h-FBFFFh                 | 16                       |

| SA30         |                 | 5C000h-5FFFFh                 | 16                       | SA70          | SG24            | FC000h-FC7FFh                 | 2                        |

| SA31         |                 | 60000h-63FFFh                 | 16                       | SA71          | SG25            | FC800h-FCFFFh                 | 2                        |

| SA32         | 0014            | 64000h-67FFFh                 | 16                       | SA72          | SG26            | FD000h-FD7FFh                 | 2                        |

| SA33         | - SG14          | 68000h-6BFFFh                 | 16                       | SA73          | SG27            | FD800h-FDFFFh                 | 2                        |

| SA34         |                 | 6C000h-6FFFFh                 | 16                       | SA74          | SG28            | FE000h-FE7FFh                 | 2                        |

| SA35         |                 | 70000h-73FFFh                 | 16                       | SA75          | SG29            | FE800h-FEFFFh                 | 2                        |

| SA36         | 0015            | 74000h-77FFFh                 | 16                       | SA76 (Note 3) | SG30            | FF000h-FF7FFh                 | 2                        |

| SA37         | - SG15          | 78000h-7BFFFh                 | 16                       | SA77 (Note 3) | SG31            | FF800h-FFFFFh                 | 2                        |

| SA38         | 1               | 7C000h–7FFFFh                 | 16                       |               |                 |                               |                          |

### Notes

- 1. Secured Silicon Sector overlays this sector when enabled.

- 2. The bank address is determined by A19 and A18. BA = 00 for Bank 0 and BA = 01, 10, or 11 for Bank 1.

- 3. This sector has the additional WP# pin sector protection feature.

### S29CD032J/CL032J (Bottom Boot) Sector and Memory Address Map

| Sector       | Sector<br>Group | x32 Address Range<br>(A19:A0) | Sector Size<br>(KDwords) | Sector        | Sector<br>Group | x32 Address Range<br>(A19:A0) | Sector Size<br>(KDwords) |

|--------------|-----------------|-------------------------------|--------------------------|---------------|-----------------|-------------------------------|--------------------------|

|              | Ba              | nk 0 (Note 2)                 |                          |               | Bank 0          | continued (Note 2)            | I.                       |

| SA0 (Note 3) | SG0             | 00000h-007FFh                 | 2                        | SA39          |                 | 80000h-83FFFh                 | 16                       |

| SA1 (Note 3) | SG1             | 00800h-00FFFh                 | 2                        | SA40          | 0040            | 84000h-87FFFh                 | 16                       |

| SA2          | SG2             | 01000h-017FFh                 | 2                        | SA41          | SG16            | 88000h-8BFFFh                 | 16                       |

| SA3          | SG3             | 01800h-01FFFh                 | 2                        | SA42          |                 | 8C000h-8FFFFh                 | 16                       |

| SA4          | SG4             | 02000h-027FFh                 | 2                        | SA43          |                 | 90000h-93FFFh                 | 16                       |

| SA5          | SG5             | 02800h-02FFFh                 | 2                        | SA44          | 0017            | 94000h-97FFFh                 | 16                       |

| SA6          | SG6             | 03000h-037FFh                 | 2                        | SA45          | SG17            | 98000h-9BFFFh                 | 16                       |

| SA7          | SG7             | 03800h-03FFFh                 | 2                        | SA46          |                 | 9C000h-9FFFFh                 | 16                       |

| SA8          |                 | 04000h-07FFFh                 | 16                       | SA47          |                 | A0000h-A3FFFh                 | 16                       |

| SA9          | SG8             | 08000h-0BFFFh                 | 16                       | SA48          | 0010            | A4000h–A7FFFh                 | 16                       |

| SA10         |                 | 0C000h-0FFFFh                 | 16                       | SA49          | SG18            | A8000h-ABFFFh                 | 16                       |

| SA11         |                 | 10000h-13FFFh                 | 16                       | SA50          |                 | AC000h-AFFFFh                 | 16                       |

| SA12         | 000             | 14000h-17FFFh                 | 16                       | SA51          |                 | B0000h-B3FFFh                 | 16                       |

| SA13         | SG9             | 18000h-1BFFFh                 | 16                       | SA52          | 0010            | B4000h-B7FFFh                 | 16                       |

| SA14         |                 | 1C000h-1FFFFh                 | 16                       | SA53          | SG19            | B8000h-BBFFFh                 | 16                       |

| SA15         |                 | 20000h-23FFFh                 | 16                       | SA54          |                 | BC000h-BFFFFh                 | 16                       |

| SA16         | SG10            | 24000h-27FFFh                 | 16                       |               | Ва              | nk 1 (Note 2)                 |                          |

| SA17         | 5610            | 28000h-2BFFFh                 | 16                       | SA55          | - SG20          | C0000h-C3FFFh                 | 16                       |

| SA18         |                 | 2C000h-2FFFFh                 | 16                       | SA56          |                 | C4000h-C7FFFh                 | 16                       |

| SA19         |                 | 30000h-33FFFh                 | 16                       | SA57          |                 | C8000h-CBFFFh                 | 16                       |

| SA20         | 0011            | 34000h-37FFFh                 | 16                       | SA58          |                 | CC000h-CFFFFh                 | 16                       |

| SA21         | SG11            | 38000h-3BFFFh                 | 16                       | SA59          |                 | D0000h-D3FFFh                 | 16                       |

| SA22         |                 | 3C000h-3FFFFh                 | 16                       | SA60          | SG21            | D4000h-D7FFFh                 | 16                       |

| SA23         |                 | 40000h-43FFFh                 | 16                       | SA61          | SG21            | D8000h-DBFFFh                 | 16                       |

| SA24         | SG12            | 44000h-47FFFh                 | 16                       | SA62          |                 | DC000h-DFFFFh                 | 16                       |

| SA25         | 3012            | 48000h-4BFFFh                 | 16                       | SA63          |                 | E0000h-E3FFFh                 | 16                       |

| SA26         |                 | 4C000h-4FFFFh                 | 16                       | SA64          | SG22            | E4000h-E7FFFh                 | 16                       |

| SA27         |                 | 50000h-53FFFh                 | 16                       | SA65          | 3022            | E8000h-EBFFFh                 | 16                       |

| SA28         | SG13            | 54000h-57FFFh                 | 16                       | SA66          |                 | EC000h-EFFFFh                 | 16                       |

| SA29         | 5013            | 58000h-5BFFFh                 | 16                       | SA67          |                 | F0000h-F3FFFh                 | 16                       |

| SA30         |                 | 5C000h-5FFFFh                 | 16                       | SA68          | SG23            | F4000h-F7FFFh                 | 16                       |

| SA31         |                 | 60000h-63FFFh                 | 16                       | SA69          |                 | F8000h-FBFFFh                 | 16                       |

| SA32         | SG14            | 64000h-67FFFh                 | 16                       | SA70          | SG24            | FC000h-FC7FFh                 | 2                        |

| SA33         | 3014            | 68000h-6BFFFh                 | 16                       | SA71          | SG25            | FC800h-FCFFFh                 | 2                        |

| SA34         |                 | 6C000h-6FFFFh                 | 16                       | SA72          | SG26            | FD000h-FD7FFh                 | 2                        |

| SA35         |                 | 70000h-73FFFh                 | 16                       | SA73          | SG27            | FD800h-FDFFFh                 | 2                        |

| SA36         | SG15            | 74000h-77FFFh                 | 16                       | SA74          | SG28            | FE000h-FE7FFh                 | 2                        |

| SA37         | 3013            | 78000h-7BFFFh                 | 16                       | SA75          | SG29            | FE800h-FEFFFh                 | 2                        |

| SA38         |                 | 7C000h-7FFFFh                 | 16                       | SA76          | SG30            | FF000h-FF7FFh                 | 2                        |

| •            |                 | -                             |                          | SA77 (Note 1) | SG31            | FF800h-FFFFFh                 | 2                        |

#### Notes

- 1. This sector has the additional WP# pin sector protection feature.

- 2. The bank address is determined by A19 and A18. BA = 00, 01, or 10 for Bank 0 and BA = 11 for Bank 1.

- 3. The Secured Silicon Sector overlays this sector when enabled.

### 8. Device Operations

This section describes the read, program, erase, simultaneous read/write operations, and reset features of the Flash devices.

Operations are initiated by writing specific commands or a sequence with specific address and data patterns into the command register (see Table ). The command register itself does not occupy any addressable memory location; rather, it is composed of latches that store the commands, along with the address and data information needed to execute the command. The contents of the register serve as input to the internal state machine; the state machine outputs dictate the function of the device. Writing incorrect address and data values or writing them in an improper sequence may place the device in an unknown state, in which case the system must write the reset command in order to return the device to the reading array data mode.

### 8.1 Device Operation Table

The device must be set up appropriately for each operation. Table describes the required state of each control pin for any particular operation.

### **Device Bus Operation**

| Operation                                                                     | CE# | OE# | WE# | RESET# | CLK      | ADV# | Addresses                                           | Data<br>(DQ0-DQ31)               |

|-------------------------------------------------------------------------------|-----|-----|-----|--------|----------|------|-----------------------------------------------------|----------------------------------|

| Read                                                                          | L   | L   | Н   | Н      | Х        | Х    | A <sub>IN</sub>                                     | D <sub>OUT</sub>                 |

| Asynchronous Write                                                            | L   | Н   | L   | Н      | Х        | Х    | A <sub>IN</sub>                                     | D <sub>IN</sub>                  |

| Synchronous Write                                                             | L   | Н   | L   | Н      |          |      | A <sub>IN</sub>                                     | D <sub>IN</sub>                  |

| Standby (CE#)                                                                 | Н   | Х   | Х   | Н      | Н        | Х    | Х                                                   | High-Z                           |

| Output Disable                                                                | L   | Н   | Н   | Н      | Х        | Х    | High-Z                                              | High-Z                           |

| Reset                                                                         | Х   | Х   | Х   | L      | Х        | Х    | Х                                                   | High-Z                           |

| DDD Dystastics Chatre (Nets 0)                                                |     |     |     | Н      | х        | х    | Sector Address,<br>$A9 = V_{ID}$ ,<br>A7 - A0 = 02h | 00000001h, (protected)<br>A6 = H |

| PPB Protection Status (Note 2)                                                | L   | L   | Н   |        |          |      |                                                     | 00000000h (unprotect)<br>A6 = L  |

| Burst Read Operations                                                         | •   |     |     | •      |          |      |                                                     |                                  |

| Load Starting Burst Address                                                   | L   | Х   | Н   | Н      |          |      | A <sub>IN</sub>                                     | х                                |

| Advance Burst to next address with appropriate Data presented on the Data bus | L   | L   | Н   | Н      |          | Н    | Х                                                   | Burst Data Out                   |

| Terminate Current Burst Read Cycle                                            | Н   | Х   | Н   | Н      | <b>-</b> | Х    | x                                                   | High-Z                           |

| Terminate Current Burst<br>Read Cycle with RESET#                             | Х   | Х   | Н   | L      | Х        | Х    | Х                                                   | High-Z                           |

| Terminate Current Burst Read Cycle;<br>Start New Burst Read Cycle             | L   | Н   | Н   | Н      |          |      | A <sub>IN</sub>                                     | ×                                |

#### Legend

$L = Logic Low = V_{IL}$ ,  $H = Logic High = V_{IH}$ , X = Don't care.

#### Notes

- 1. WP# controls the two outermost sectors of the top boot block or the two outermost sectors of the bottom boot block.

- 2. DQ0 reflects the sector PPB (or sector group PPB) and DQ1 reflects the DYB.

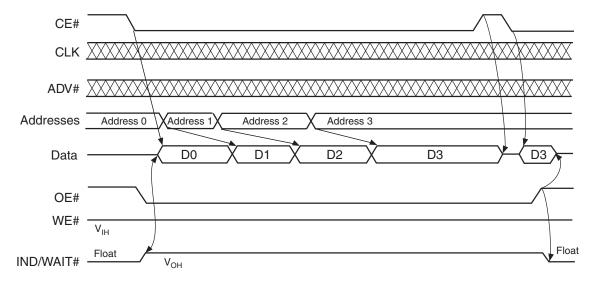

### 8.2 Asynchronous Read

All memories require access time to output array data. In an asynchronous read operation, data is read from one memory location at a time. Addresses are presented to the device in random order, and the propagation delay through the device causes the data on its outputs to arrive asynchronously with the address on its inputs.

The internal state machine is set for asynchronously reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory content occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid addresses on the device address inputs produce valid data on the device data outputs. The device remains enabled for read access until the command register contents are altered.

The device has two control functions which must be satisfied in order to obtain data at the outputs. CE# is the power control and should be used for device selection (CE# must be set to  $V_{IL}$  to read data). OE# is the output control and should be used to gate data to the output pins if the device is selected (OE# must be set to  $V_{IL}$  in order to read data). WE# should remain at  $V_{IH}$  (when reading data).

Address access time ( $t_{ACC}$ ) is equal to the delay from stable addresses to valid output data. The chip enable access time ( $t_{CE}$ ) is the delay from the stable addresses and stable CE# to valid data at the output pins. The output enable access time ( $t_{CE}$ ) is the delay from the falling edge of OE# to valid data at the output pins (assuming the addresses have been stable for at least a period of  $t_{ACC}$ - $t_{CE}$  and CE# has been asserted for at least  $t_{CE}$ - $t_{CE}$  time). Figure 8.1 shows the timing diagram of an asynchronous read operation.

Figure 8.1 Asynchronous Read Operation

Note

Operation is shown for the 32-bit data bus. For the 16-bit data bus, A-1 is required.

Refer to Asynchronous Operations on page 52 for timing specifications and to Figure 18.2, Conventional Read Operations Timings on page 52 for another timing diagram. I<sub>CC1</sub> in the DC Characteristics table represents the active current specification for reading array data.

### 8.3 Hardware Reset (RESET#)

The RESET# pin is an active low signal that is used to reset the device under any circumstances. A logic "0" on this input forces the device out of any mode that is currently executing back to the reset state. RESET# may be tied to the system reset circuitry. A system reset would thus also reset the device. To avoid a potential bus contention during a system reset, the device is isolated from the DQ data bus by tristating the data outputs for the duration of the RESET pulse. All data outputs are "don't care" during the reset operation.

If RESET# is asserted during a program or erase operation, the RY/BY# output remains low until the reset operation is internally complete. The RY/BY# pin can be used to determine when the reset operation is complete. Since the device offers simultaneous read/write operation, the host system may read a bank after a period of t<sub>READY2</sub>, if the bank was in the read/reset mode at the time

RESET# was asserted. If one of the banks was in the middle of either a program or erase operation when RESET# was asserted, the user must wait a period of t<sub>READY</sub> before accessing that bank.

Asserting RESET# during a program or erase operation leaves erroneous data stored in the address locations being operated on at the time of device reset. These locations need updating after the reset operation is complete. See *Hardware Reset (RESET#)* on page 56 for timing specifications.

Asserting RESET# active during  $V_{CC}$  and  $V_{IO}$  power-up is required to guarantee proper device initialization until  $V_{CC}$  and  $V_{IO}$  have reached their steady state voltages. See  $V_{CC}$  and  $V_{IO}$  Power-up on page 51.

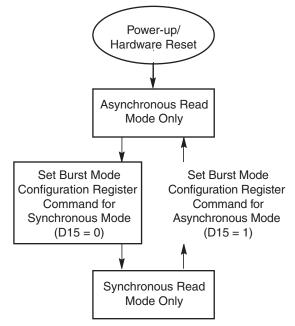

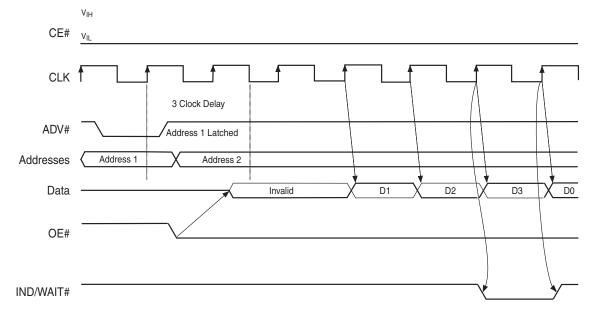

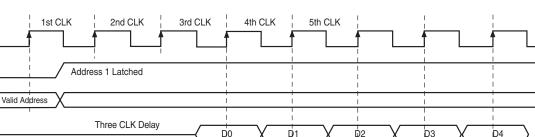

### 8.4 Synchronous (Burst) Read Mode and Configuration Register

When a series of adjacent addresses need to be read from the device, the synchronous (or burst read) mode can be used to significantly reduce the overall time needed for the device to output array data. After an initial access time required for the data from the first address location, subsequent data is output synchronized to a clock input provided by the system.