## mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### S29PL-J

# 128-/128-/64-/32-Mbit (8/8/4/2M $\times$ 16-Bit), 3 V, Flash with Enhanced VersatileIO<sup>TM</sup>

## **Distinctive Characteristics**

#### Architectural Advantages

- 128-/128-/64-/32-Mbit Page Mode devices

- Page size of 8 words: Fast page read access from random locations within the page

- Single power supply operation

- Full Voltage range: 2.7 to 3.6 V read, erase, and program operations for battery-powered applications

- Dual Chip Enable inputs (only in PL129J)

- Two CE# inputs control selection of each half of the memory space

- Simultaneous Read/Write Operation

- Data can be continuously read from one bank while executing erase/program functions in another bank

- Zero latency switching from write to read operations

FlexBank Architecture (PL127J/PL064J/PL032J)

- 4 separate banks, with up to two simultaneous operations per device

- Bank A:

- PL127J -16 Mbit (4 Kw × 8 and 32 Kw × 31)

- PL064J 8 Mbit (4 Kw × 8 and 32 Kw × 15)

- PL032J 4 Mbit (4 Kw  $\times$  8 and 32 Kw  $\times$  7)

- Bank B:

- PL127J 48 Mbit (32 Kw × 96)

- PL064J 24 Mbit (32 Kw × 48)

- PL032J 12 Mbit (32 Kw × 24)

- Bank C:

- PL127J 48 Mbit (32 Kw × 96)

- PL064J 24 Mbit (32 Kw × 48)

- PL032J 12 Mbit (32 Kw × 24)

- Bank D:

- PL127J -16 Mbit (4 Kw  $\times$  8 and 32 Kw  $\times$  31)

- PL064J 8 Mbit (4 Kw × 8 and 32 Kw × 15)

- PL032J 4 Mbit (4 Kw  $\times$  8 and 32 Kw  $\times$  7)

- FlexBank Architecture (PL129J)

- 4 separate banks, with up to two simultaneous operations per device

- CE#1 controlled banks: Bank 1A: PL129J - 16-Mbit (4Kw × 8 and 32Kw × 31) Bank 1B: PL129J - 48-Mbit (32Kw × 96)

- CE#2 controlled banks: Bank 2A: PL129J - 48-Mbit (32 Kw × 96) Bank 2B: PL129J - 16-Mbit (4 Kw × 8 and 32 Kw × 31)

- Enhanced VersatileI/O (VIO) Control

- Output voltage generated and input voltages tolerated on all control inputs and I/Os is determined by the voltage on the  $\rm V_{IO}$  pin

- $V_{IO}$  options at 1.8 V and 3 V I/O for PL127J and PL129J devices

- 3V V<sub>IO</sub> for PL064J and PL032J devices

- Secured Silicon Sector region

- Up to 128 words accessible through a command sequence

- Up to 64 factory-locked words

- Up to 64 customer-lockable words

- Both top and bottom boot blocks in one device

- Manufactured on 110-nm process technology

- Data Retention: 20 years typical

- Cycling Endurance: 1 million cycles per sector typical

#### Performance Characteristics

- High Performance

- Page access times as fast as 20 ns

Random access times as fast as 55 ns

- Power consumption (typical values at 10 MHz)

45 mA active read current

- 17 mA program/erase current

- -0.2 µA typical standby mode current

#### Software Features

- Software command-set compatible with JEDEC 42.4 standard

- Backward compatible with Am29F, Am29LV, Am29DL, and AM29PDL families and MBM29QM/RM, MBM29LV, MBM29DL, MBM29PDL families

- CFI (Common Flash Interface) compliant

- Provides device-specific information to the system, allowing host software to easily reconfigure for different Flash devices

- Erase Suspend / Erase Resume

Suspends an erase operation to allow read or program operations in other sectors of same bank

- Program Suspend / Program Resume

Suspends a program operation to allow read operation from sectors other than the one being programmed

- Unlock Bypass Program command

- Reduces overall programming time when issuing multiple program command sequences

Cypress Semiconductor Corporation Document Number: 002-00615 Rev. \*C

198 Champion Court

#### **Hardware Features**

- Ready/Busy# pin (RY/BY#)

- Provides a hardware method of detecting program or erase cycle completion

- Hardware reset pin (RESET#)

- Hardware method to reset the device to reading array data

- WP#/ ACC (Write Protect/Acceleration) input

- At  $V_{\text{IL}},$  hardware level protection for the first and last two 4K word sectors.

- At VIH, allows removal of sector protection

- At  $V_{HH}, \, \text{provides}$  accelerated programming in a factory setting

- Persistent Sector Protection

- A command sector protection method to lock combinations of individual sectors and sector groups to prevent program or erase operations within that sector

- Sectors can be locked and unlocked in-system at  $V_{CC}$  level

- Password Sector Protection

- A sophisticated sector protection method to lock combinations of individual sectors and sector groups to prevent program or erase operations within that sector using a user-defined 64-bit password

- Package options

- Standard discrete pinouts

- 11  $\times$  8 mm, 80-ball Fine-pitch BGA (PL127J) (VBG080) 8.15  $\times$  6.15 mm, 48-ball Fine pitch BGA (PL064J/PL032J) (VBK048)

- MCP-compatible pinout

- $8\times11.6$  mm, 64-ball Fine-pitch BGA (PL127J)  $7\times9$  mm, 56-ball Fine-pitch BGA (PL064J and PL032J) Compatible with MCP pinout, allowing easy integration of RAM into existing designs

- 20 × 14 mm, 56-pin TSOP (PL127J) (TS056)

## S29PL-J

### Contents

| Disti                                                | nctive Characteristics                                                                                                                                                                        | . 1                                    |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1.                                                   | General Description                                                                                                                                                                           | . 4                                    |

| 2.                                                   | Simultaneous Read/Write Operation with Zero Latency                                                                                                                                           | . 4                                    |

| 2.1<br>2.2                                           | Page Mode Features<br>Standard Flash Memory Features                                                                                                                                          |                                        |

| 3.                                                   | Ordering Information                                                                                                                                                                          | . 6                                    |

| 4.                                                   | Product Selector Guide                                                                                                                                                                        | . 8                                    |

| 5.                                                   | Block Diagram                                                                                                                                                                                 | . 8                                    |

| 6.                                                   | Simultaneous Read/Write Block Diagram                                                                                                                                                         | . 9                                    |

| 7.                                                   | Simultaneous Read/Write Block Diagram (PL129J)                                                                                                                                                | 10                                     |

| 8.<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6         | Connection Diagrams                                                                                                                                                                           | 11<br>11<br>12<br>13<br>14             |

| 9.                                                   | Pin Description                                                                                                                                                                               | 16                                     |

| 10.                                                  | Logic Symbol                                                                                                                                                                                  | 17                                     |

| 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8 | Device Bus Operations                                                                                                                                                                         | 18<br>19<br>20<br>20<br>20<br>21<br>43 |

| 12.1<br>12.2<br>12.3                                 | Sector Protection<br>Persistent Sector Protection<br>Password Sector Protection<br>WP# Hardware Protection<br>Selecting a Sector Protection Mode                                              | 49<br>49<br>49                         |

| 13.1<br>13.2<br>13.3                                 | Persistent Sector Protection<br>Persistent Protection Bit (PPB)<br>Persistent Protection Bit Lock (PPB Lock)<br>Dynamic Protection Bit (DYB)<br>Persistent Sector Protection Mode Locking Bit | 50<br>50<br>50                         |

| 14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6         | Password Protection Mode<br>Password and Password Mode Locking Bit                                                                                                                            | 52<br>52<br>53<br>53<br>55<br>55       |

| 15.                                                                                                                                            | Common Flash Memory Interface (CFI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .58                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 16.                                                                                                                                            | Command Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .61                                                                                                                             |

|                                                                                                                                                | Reading Array Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|                                                                                                                                                | Reset Command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |

|                                                                                                                                                | Autoselect Command Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .62                                                                                                                             |

| 16.4                                                                                                                                           | Enter/Exit Secured Silicon Sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u></u>                                                                                                                         |

| 165                                                                                                                                            | Command Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                 |

|                                                                                                                                                | Chip Erase Command Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

|                                                                                                                                                | Sector Erase Command Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |

|                                                                                                                                                | Erase Suspend/Erase Resume Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                 |

| 16.9                                                                                                                                           | Program Suspend/Program Resume Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .67                                                                                                                             |

| 16.10                                                                                                                                          | Command Definitions Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .67                                                                                                                             |

| 17.                                                                                                                                            | Write Operation Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .71                                                                                                                             |

|                                                                                                                                                | DQ7: Data# Polling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|                                                                                                                                                | RY/BY#: Ready/Busy#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                 |

|                                                                                                                                                | DQ6: Toggle Bit I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                 |

|                                                                                                                                                | DQ2: Toggle Bit II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

|                                                                                                                                                | Reading Toggle Bits DQ6/DQ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

|                                                                                                                                                | DQ5: Exceeded Timing Limits<br>DQ3: Sector Erase Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                 |

| 18.                                                                                                                                            | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                 |

| 19.                                                                                                                                            | Operating Ranges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                 |

| -                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |

| 20.                                                                                                                                            | DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                 |

| 21.                                                                                                                                            | AC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70                                                                                                                              |

|                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |

| 21.1                                                                                                                                           | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .79                                                                                                                             |

| 21.1<br>21.2                                                                                                                                   | Test Conditions<br>Switching Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .79<br>.80                                                                                                                      |

| 21.1<br>21.2<br>21.3                                                                                                                           | Test Conditions<br>Switching Waveforms<br>Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .79<br>.80<br>.80                                                                                                               |

| 21.1<br>21.2<br>21.3<br>21.4                                                                                                                   | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .79<br>.80<br>.80<br>.82                                                                                                        |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5                                                                                                           | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset<br>Erase/Program Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .79<br>.80<br>.80<br>.82<br>.83                                                                                                 |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6                                                                                                   | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset<br>Erase/Program Operations<br>Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .79<br>.80<br>.80<br>.82<br>.83<br>.83                                                                                          |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b>                                                                                     | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset<br>Erase/Program Operations<br>Timing Diagrams<br>Protect/Unprotect                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .79<br>.80<br>.80<br>.82<br>.83<br>.83<br>.84                                                                                   |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1                                                                             | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset<br>Erase/Program Operations<br>Timing Diagrams<br>Protect/Unprotect<br>Controlled Erase Operations                                                                                                                                                                                                                                                                                                                                                                                                                                        | .79<br>.80<br>.80<br>.82<br>.83<br>.84<br>.84<br>.88                                                                            |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b>                                                               | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Erase/Program Operations<br>Timing Diagrams<br>Protect/Unprotect<br>Controlled Erase Operations<br>Pin Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                              | .79<br>.80<br>.82<br>.83<br>.83<br>.84<br>.88<br>.90                                                                            |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1                                                       | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .79<br>.80<br>.82<br>.83<br>.84<br>.88<br>.90<br>.93<br>.93                                                                     |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2                                               | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset<br>Erase/Program Operations<br>Timing Diagrams<br>Protect/Unprotect<br>Controlled Erase Operations<br>Pin Capacitance<br>BGA Pin Capacitance<br>TSOP Pin Capacitance                                                                                                                                                                                                                                                                                                                                                                      | .79<br>.80<br>.82<br>.83<br>.84<br>.88<br>.90<br>.93<br>.93                                                                     |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b>                                 | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .79<br>.80<br>.82<br>.83<br>.83<br>.84<br>.90<br>.93<br>.93<br>.93<br>.94                                                       |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b>                                 | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .79<br>.80<br>.82<br>.83<br>.83<br>.84<br>.90<br>.93<br>.93<br>.93<br>.93                                                       |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1                         | Test Conditions<br>Switching Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .79<br>.80<br>.82<br>.83<br>.84<br>.90<br>.93<br>.93<br>.93<br>.93<br>.94<br>1<br>.94                                           |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1                         | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Erase/Program Operations<br>Timing Diagrams<br><b>Protect/Unprotect</b><br>Controlled Erase Operations<br><b>Pin Capacitance</b><br>BGA Pin Capacitance<br>TSOP Pin Capacitance<br><b>Physical Dimensions</b><br>VBG080—80-Ball Fine-pitch Ball Grid Array 8 × 11 mm<br>Package (PL127J)<br>VBH064—64-Ball Fine-pitch Ball Grid Array 8 × 11.6 m                                                                                                                                                                                                | .79<br>.80<br>.82<br>.83<br>.83<br>.84<br>.90<br>.93<br>.93<br>.93<br>.93<br>.94<br>1<br>.94                                    |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1<br>24.2                 | Test Conditions<br>Switching Waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .79<br>.80<br>.82<br>.83<br>.83<br>.84<br>.90<br>.93<br>.93<br>.93<br>.93<br>.94<br>1<br>.94<br>1.95                            |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1<br>24.2                 | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Erase/Program Operations<br>Timing Diagrams<br><b>Protect/Unprotect</b><br>Controlled Erase Operations<br><b>Pin Capacitance</b><br>BGA Pin Capacitance<br>TSOP Pin Capacitance<br><b>Physical Dimensions</b><br>VBG080—80-Ball Fine-pitch Ball Grid Array 8 × 11 mn<br>Package (PL127J)<br>VBH064—64-Ball Fine-pitch Ball Grid Array 8 × 11.6 m<br>package (PL127J)<br>VBK048—48-Ball Fine-pitch Ball Grid Array 8.15 × 6.15 m<br>package                                                                                                      | .79<br>.80<br>.82<br>.83<br>.83<br>.83<br>.83<br>.93<br>.93<br>.93<br>.93<br>.93<br>.94<br>1.95<br>m                            |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1<br>24.2<br>24.3         | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Erase/Program Operations<br>Timing Diagrams<br><b>Protect/Unprotect</b><br>Controlled Erase Operations<br><b>Pin Capacitance</b><br>BGA Pin Capacitance<br>TSOP Pin Capacitance<br><b>Physical Dimensions</b><br>VBG080—80-Ball Fine-pitch Ball Grid Array 8 × 11 mn<br>Package (PL127J)<br>VBH064—64-Ball Fine-pitch Ball Grid Array 8 × 11.6 m<br>package (PL127J)<br>VBK048—48-Ball Fine-pitch Ball Grid Array 8.15 × 6.15 m<br>package (PL032J and PL064J)                                                                                  | .79<br>.80<br>.82<br>.83<br>.83<br>.83<br>.83<br>.93<br>.93<br>.93<br>.93<br>.93<br>.94<br>1.95<br>m                            |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1<br>24.2<br>24.3         | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Erase/Program Operations<br>Timing Diagrams<br><b>Protect/Unprotect</b><br>Controlled Erase Operations<br><b>Pin Capacitance</b><br>BGA Pin Capacitance<br>TSOP Pin Capacitance<br><b>Physical Dimensions</b><br>VBG080—80-Ball Fine-pitch Ball Grid Array 8 × 11 mm<br>Package (PL127J)<br>VBH064—64-Ball Fine-pitch Ball Grid Array 8 × 11.6 m<br>package (PL127J)<br>VBK048—48-Ball Fine-pitch Ball Grid Array 8.15 × 6.15 m<br>package (PL032J and PL064J)<br>VBU056—56-Ball Fine-pitch BGA 7 × 9mm package                                 | .79<br>.80<br>.82<br>.83<br>.83<br>.84<br>.93<br>.93<br>.93<br>.93<br>.93<br>.94<br>1.95<br>m<br>.95                            |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1<br>24.2<br>24.3<br>24.3 | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Reset<br>Erase/Program Operations<br>Timing Diagrams<br><b>Protect/Unprotect</b><br>Controlled Erase Operations<br><b>Pin Capacitance</b><br>BGA Pin Capacitance<br>TSOP Pin Capacitance<br><b>Physical Dimensions</b><br>VBG080—80-Ball Fine-pitch Ball Grid Array 8 × 11 mm<br>Package (PL127J)<br>VBH064—64-Ball Fine-pitch Ball Grid Array 8 × 11.6 m<br>package (PL127J)<br>VBK048—48-Ball Fine-pitch Ball Grid Array 8.15 × 6.15 m<br>package (PL032J and PL064J)<br>VBU056—56-Ball Fine-pitch BGA 7 × 9mm package<br>(PL064J and PL032J) | .79<br>.80<br>.82<br>.83<br>.83<br>.83<br>.84<br>.93<br>.93<br>.93<br>.93<br>.93<br>.93<br>.94<br>.94<br>.95<br>m<br>.96<br>.97 |

| 21.1<br>21.2<br>21.3<br>21.4<br>21.5<br>21.6<br><b>22.</b><br>22.1<br><b>23.</b><br>23.1<br>23.2<br><b>24.</b><br>24.1<br>24.2<br>24.3<br>24.3 | Test Conditions<br>Switching Waveforms<br>Read Operations<br>Erase/Program Operations<br>Timing Diagrams<br><b>Protect/Unprotect</b><br>Controlled Erase Operations<br><b>Pin Capacitance</b><br>BGA Pin Capacitance<br>TSOP Pin Capacitance<br><b>Physical Dimensions</b><br>VBG080—80-Ball Fine-pitch Ball Grid Array 8 × 11 mm<br>Package (PL127J)<br>VBH064—64-Ball Fine-pitch Ball Grid Array 8 × 11.6 m<br>package (PL127J)<br>VBK048—48-Ball Fine-pitch Ball Grid Array 8.15 × 6.15 m<br>package (PL032J and PL064J)<br>VBU056—56-Ball Fine-pitch BGA 7 × 9mm package                                 | .79<br>.80<br>.82<br>.83<br>.84<br>.83<br>.90<br>.93<br>.93<br>.93<br>.93<br>.93<br>.94<br>n.94<br>n.95<br>m.96<br>.97<br>.98   |

D

## 1. General Description

The PL127J/PL129J/PL064J/PL032J is a 128/128/64/32 Mbit, 3.0 volt-only Page Mode and Simultaneous Read/Write Flash memory device organized as 8/8/4/2 Mwords. The devices are offered in the following packages:

- 11 mm × 8 mm, 80-ball Fine-pitch BGA standalone (PL127J)

- 8 mm × 11.6 mm, 64-ball Fine-pitch BGA multi-chip compatible (PL127J)

- 8.15 mm × 6.15 mm, 48-ball Fine-pitch BGA standalone (PL064J/PL032J)

- 7 mm × 9 mm, 56-ball Fine-pitch BGA multi-chip compatible (PL064J and PL032J)

- 20 mm × 14 mm, 56-pin TSOP (PL127J)

16 Mbit (4 Kw x 8 and 32 Kw  $\times$  31)

The word-wide data (x16) appears on DQ15-DQ0. This device can be programmed in-system or in standard EPROM programmers. A 12.0 V  $V_{PP}$  is not required for write or erase operations.

## 2. Simultaneous Read/Write Operation with Zero Latency

The Simultaneous Read/Write architecture provides **simultaneous operation** by dividing the memory space into 4 banks, which can be considered to be four separate memory arrays as far as certain operations are concerned. The device can improve overall system performance by allowing a host system to program or erase in one bank, then immediately and simultaneously read from another bank with zero latency (with two simultaneous operations operating at any one time). This releases the system from waiting for the completion of a program or erase operation, greatly improving system performance.

| Bank | PL127J Sectors                                  | PL064J Sectors                                 | PL032J Sectors                                |

|------|-------------------------------------------------|------------------------------------------------|-----------------------------------------------|

| Α    | 16 Mbit (4 Kw $\times$ 8 and 32 Kw $\times$ 31) | 8 Mbit (4 Kw $\times$ 8 and 32 Kw $\times$ 15) | 4 Mbit (4 Kw $\times$ 8 and 32 Kw $\times$ 7) |

| В    | 48 Mbit (32 Kw $	imes$ 96)                      | 24 Mbit (32 Kw × 48)                           | 12 Mbit (32 Kw × 24)                          |

| С    | 48 Mbit (32 Kw $	imes$ 96)                      | 24 Mbit (32 Kw × 48)                           | 12 Mbit (32 Kw × 24)                          |

The device can be organized in both top and bottom sector configurations. The banks are organized as follows:

| Bank | PL129J Sectors                                  | CE# Control |

|------|-------------------------------------------------|-------------|

| 1A   | 16 Mbit (4 Kw $\times$ 8 and 32 Kw $\times$ 31) | CE1#        |

| 1B   | 48 Mbit (32 Kw × 96)                            | CE1#        |

| 2A   | 48 Mbit (32 Kw × 96)                            | CE2#        |

| 2B   | 16 Mbit (4 Kw $\times$ 8 and 32 Kw $\times$ 31) | CE2#        |

8 Mbit (4 Kw  $\times$  8 and 32 Kw  $\times$  15)

4 Mbit (4 Kw  $\times$  8 and 32 Kw  $\times$  7)

#### 2.1 Page Mode Features

The page size is 8 words. After initial page access is accomplished, the page mode operation provides fast read access speed of random locations within that page.

#### 2.2 Standard Flash Memory Features

The device requires a **single 3.0 volt power supply** (2.7 V to 3.6 V) for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations.

The device is entirely command set compatible with the **JEDEC 42.4 single-power-supply Flash standard**. Commands are written to the command register using standard microprocessor write timing. Register contents serve as inputs to an internal state-machine that controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the device is similar to reading from other Flash or EPROM devices.

Device programming occurs by executing the program command sequence. The Unlock Bypass mode facilitates faster programming times by requiring only two write cycles to program data instead of four. Device erasure occurs by executing the erase command sequence.

The host system can detect whether a program or erase operation is complete by reading the DQ7 (Data# Polling) and DQ6 (toggle) **status bits**. After a program or erase cycle has been completed, the device is ready to read array data or accept another command.

The sector erase architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is fully erased when shipped from the factory.

**Hardware data protection** measures include a low V<sub>CC</sub> detector that automatically inhibits write operations during power transitions. The hardware sector protection feature disables both program and erase operations in any combination of sectors of memory. This can be achieved in-system or via programming equipment.

The Erase Suspend/Erase Resume feature enables the user to put erase on hold for any period of time to read data from, or program data to, any sector that is not selected for erasure. True background erase can thus be achieved. If a read is needed from the Secured Silicon Sector area (One Time Program area) after an erase suspend, then the user must use the proper command sequence to enter and exit this region.

The **Program Suspend/Program Resume** feature enables the user to hold the program operation to read data from any sector that is not selected for programming. If a read is needed from the Secured Silicon Sector area, Persistent Protection area, Dynamic Protection area, or the CFI area, after a program suspend, then the user must use the proper command sequence to enter and exit this region.

The device offers two power-saving features. When addresses have been stable for a specified amount of time, the device enters the **automatic sleep mode**. The system can also place the device into the standby mode. Power consumption is greatly reduced in both these modes. The device electrically erases all bits within a sector simultaneously via Fowler-Nordheim tunneling. The data is programmed using hot electron injection.

## 3. Ordering Information

The order number (Valid Combination) is formed by a valid combinations of the following:

| S29PL-J | <u> </u> | xx | × | xx       | X<br>Packing Type: X = 0 or 1 or 2 or 3<br>0 = Tray<br>1 = Tube<br>2 = 7-inch Tape and Reel<br>3 = 13-inch Tape and Reel                                                                                |

|---------|----------|----|---|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |          |    |   |          |                                                                                                                                                                                                         |

|         |          |    |   |          | Temperature Range: X = W or I W = Wireless (-25°C to +85°C) I = Industrial (-40°C to +85°C)                                                                                                             |

|         |          |    |   |          | <ul> <li>Package Type: XX = BF or TF</li> <li>BF = Fine-Pitch Grid Array (FBGA)<br/>Lead (Pb)-free</li> <li>TF = Thin Small Outline Package (TSOP) Standard Pinout<br/>Lead (Pb)-free</li> </ul>        |

|         |          |    |   |          | <ul> <li>Clock Speed: XX = 55 or 60 or 65 or 70 or 80</li> <li>55 = 55 ns (Contact factory for availability)</li> <li>60 = 60 ns</li> <li>65 = 65 ns</li> <li>70 = 70 ns</li> <li>80 = 80 ns</li> </ul> |

|         |          |    |   | umber/De |                                                                                                                                                                                                         |

128 Mbit (8M x 16-Bit), 64 Megabit (4M x 16-Bit), 32 Megabit (2M x 16-Bit) CMOS Flash Memory, Simultaneous-Read/Write, Page-Mode Flash Memory, 3.0 V-only Read, Program, and Erase

#### Valid Combinations to be Supported for this Device

| 128 Mb Products Based on 110 nm Floating Gate Technology                                                                                            |            |        |      |        |            |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|------|--------|------------|--|--|

| Device Number/<br>Description         Package<br>Speed (ns)         Temperature<br>Type         Additional<br>Range         CE#<br>Ordering Options |            |        |      |        |            |  |  |

| S29PL127J                                                                                                                                           | 60, 65, 70 | BF, TF | W, I | 00, 13 | Single CE# |  |  |

| S29PL127J                                                                                                                                           | 80         | BF     | W, I | 01     | Single CE# |  |  |

| S29PL127J                                                                                                                                           | 80         | TF     | W, I | 14     | Single CE# |  |  |

| 64 Mb Products Based on 110 nm Floating Gate Technology                                                  |            |    |      |        |  |  |

|----------------------------------------------------------------------------------------------------------|------------|----|------|--------|--|--|

| Device Number/<br>DescriptionSpeed (ns)Package<br>TypeTemperature<br>RangeAdditional<br>Ordering Options |            |    |      |        |  |  |

| S29PL064J                                                                                                | 55, 60, 70 | BF | W, I | 12, 15 |  |  |

| 32 Mb Products Based on 110 nm Floating Gate Technology                                           |            |    |      |        |  |  |  |

|---------------------------------------------------------------------------------------------------|------------|----|------|--------|--|--|--|

| Device Number/<br>DescriptionSpeed (ns)Package TypeTemperature RangeAdditional Orderin<br>Options |            |    |      |        |  |  |  |

| S29PL032J                                                                                         | 55, 60, 70 | BF | W, I | 12, 15 |  |  |  |

| Valid Combinations for BGA Packages |                    |                       |  |  |  |  |

|-------------------------------------|--------------------|-----------------------|--|--|--|--|

| Order Number (Note 1)               | Speed (ns)         | V <sub>IO</sub> Range |  |  |  |  |

| PL129J, PL127J,PL064J, PL032J       | 55, 60, 65, 70 (3) | 2.7–3.6               |  |  |  |  |

| PL129J, PL127J                      | 80                 | 1.65–1.95             |  |  |  |  |

Notes

1. Please contact the factory for PL129J availability.

2. BGA package marking omits leading S29 and packing type designator from ordering part number.

3. 55 ns speed only supported for PL032J and PL127J.

| Valid Combinations for TSOP Packages          |        |         |  |  |

|-----------------------------------------------|--------|---------|--|--|

| Order Number Speed (ns) V <sub>IO</sub> Range |        |         |  |  |

| S29PL127J                                     | 60, 70 | 2.7–3.6 |  |  |

Note

TSOP package markings omit packing type designator from ordering part number.

## 4. Product Selector Guide

|                                          | Part Number $\rightarrow$                                                           | S29PL032J/S29PL064J/S29PL0127J/S29PL129J |    |    |    |    |  |

|------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------|----|----|----|----|--|

|                                          | $V_{CC}, V_{IO} = 2.7 V - 3.6 V$                                                    | 55 (See Note)                            | 60 | 65 | —  | 70 |  |

| Speed Option                             | $V_{CC} = 2.7 V - 3.6 V,$<br>$V_{IO} = 1.65 V - 1.95 V$<br>(PL127J and PL129J only) | -                                        | _  | _  | 80 | _  |  |

| Max Access Time                          | , ns (t <sub>ACC</sub> )                                                            | 55 (See Note) 60 65 80                   |    | 70 |    |    |  |

| Max CE# Access,                          | ns (t <sub>CE</sub> )                                                               | 55 (See Note) 60 65 80                   |    | 80 | 70 |    |  |

| Max Page Access, ns (t <sub>PACC</sub> ) |                                                                                     | 20 (See Note)                            | 25 |    | 30 | 30 |  |

| Max OE# Access,                          | ns (t <sub>OE</sub> )                                                               | 20 (See Note)                            | 20 |    | 30 | 30 |  |

| Note                                     |                                                                                     | +                                        |    |    | •  | •  |  |

55 ns speed bin only supported for PL032J and PL064J.

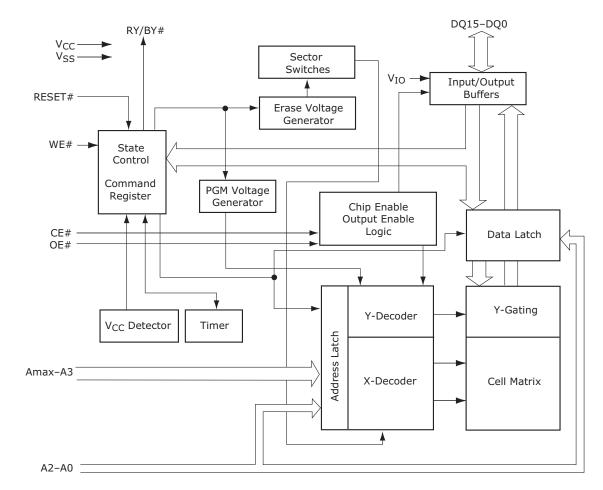

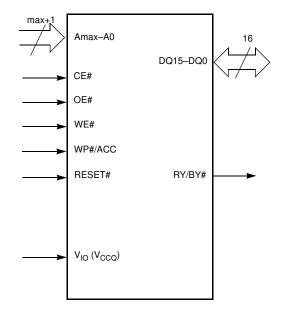

## 5. Block Diagram

#### Notes

1. RY/BY# is an open drain output.

2. Amax = A22 (PL127J), A21 (PL129J and PL064J), A20 (PL032J)

3. For PL129J, there are two CE# (CE1# and CE2#).

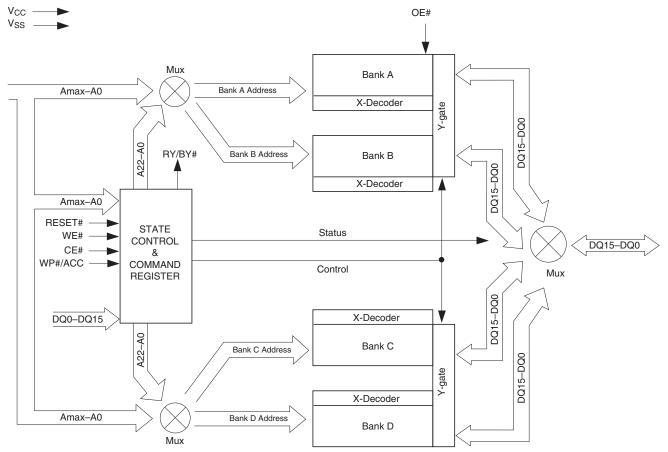

## 6. Simultaneous Read/Write Block Diagram

#### Note

Amax = A22 (PL127J), A21 (PL064J), A20 (PL032J)

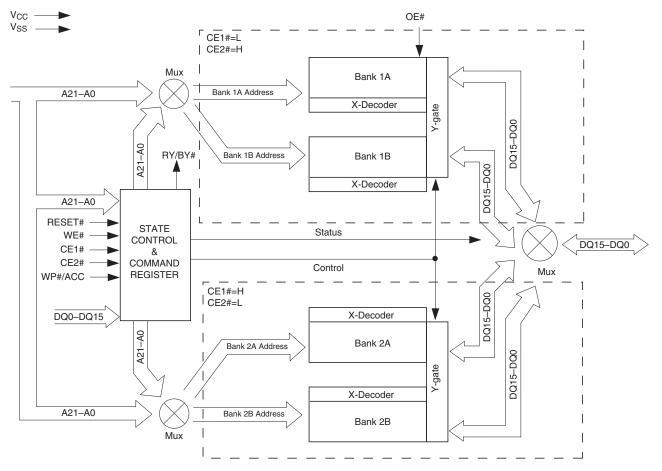

## 7. Simultaneous Read/Write Block Diagram (PL129J)

Note Amax = A21 (PL129J)

#### 8. Connection Diagrams

#### 8.1 Special Package Handling Instructions

#### 8.1.1 TSOP, BGA, PDIP, SSOP, and PLCC Packages

Special handling is required for Flash Memory products in molded packages.

The package and/or data integrity may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

#### 8.1.2 FBGA Packages

Special handling is required for Flash Memory products in FBGA packages.

Flash memory devices in FBGA packages may be damaged if exposed to ultrasonic cleaning methods. The package and/or data integrity may be compromised if the package body is exposed to temperatures above 150°C for prolonged periods of time.

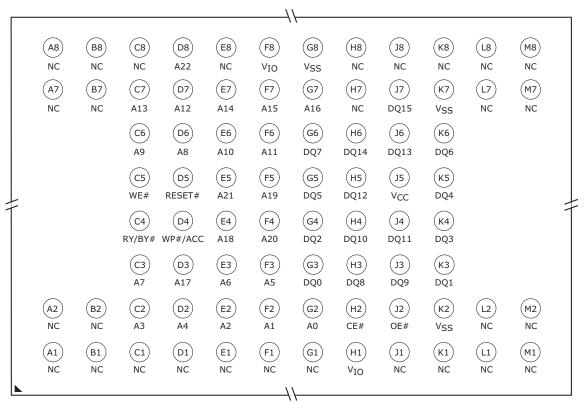

#### 8.2 80-Ball Fine-Pitch BGA—PL127J

Figure 8.1 80-Ball Fine-Pitch BGA, Top View, Balls Facing Down-PL127J

#### 8.3 64-Ball Fine-Pitch BGA—MCP Compatible—PL127J

Figure 8.2 64-Ball Fine-Pitch BGA, MCP Compatible, Top View, Balls Facing Down—PL127J

| (A1)<br>NC |       |      |      |                  |      |           |           | (A10)<br>NC |

|------------|-------|------|------|------------------|------|-----------|-----------|-------------|

|            |       |      |      | B5 B6<br>RFU RFU |      |           |           |             |

|            |       | C3   | (C4) | C5 C6            | C7   | (C8)      |           |             |

|            | _     | A7   | RFU  | WP#/ACC WE#      | A8   | A11       | _         |             |

|            | D2    | D3   | D4   | D5 D6            | D7   | D8        | D9        |             |

|            | A3    | A6   | RFU  | RESET# RFU       | A19  | A12       | A15       |             |

|            | E2    | E3   | E4   | E5 E6            | (E7) | (E8)      | (E9)      |             |

|            | A2    | A5   | A18  | RY/BY # A20      | A9   | A13       | A21       |             |

|            | F2    | F3   | F4   |                  | (F7) | F8        | (F9)      |             |

| ŧ          | A1    | A4   | A17  |                  | A10  | A14       | A22       | 1           |

|            | G2    | G3   | G4)  |                  | G7)  | <b>G8</b> | <b>G9</b> |             |

|            | A0    | VSS  | DQ1  |                  | DQ6  | RFU       | A16       |             |

|            | (H2)  | НЗ   | H4   | (H5) (H6)        | (H7) | (H8)      | (Н9)      |             |

|            | CE#f1 | OE#  | DQ9  | DQ3 DQ4          | DQ13 | DQ15      | VCCf      |             |

|            | (J2)  | (J3) | (J4) | J5 J6            | (J7) | (8L)      | (9L)      |             |

|            | RFU   | DQ0  | DQ10 | VCCf RFU         | DQ12 | DQ7       | VSS       |             |

|            |       | (кз) | (К4) | (к5) (к6)        | (к7) | (кв)      |           |             |

|            |       | DQ8  | DQ2  | DQ11 RFU         | DQ5  | DQ14      |           |             |

|            |       |      |      | L5 L6            |      |           |           |             |

|            |       |      |      | RFU RFU          |      |           |           |             |

| M1<br>NC   |       |      |      |                  |      |           |           | M10         |

| NC         |       |      |      |                  |      |           |           | NC          |

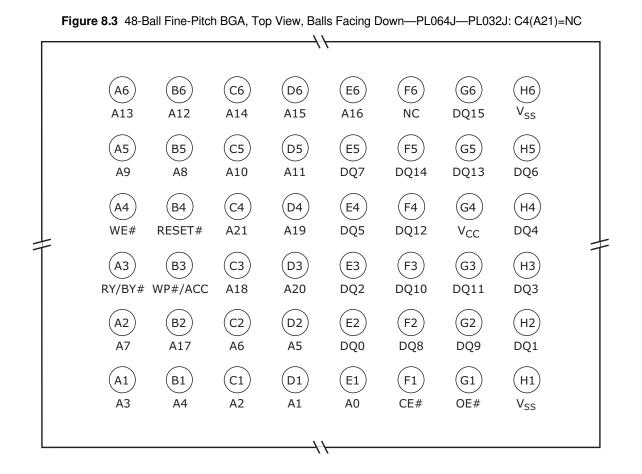

#### 8.4 48-Ball Fine-Pitch BGA, PL064J and PL032J

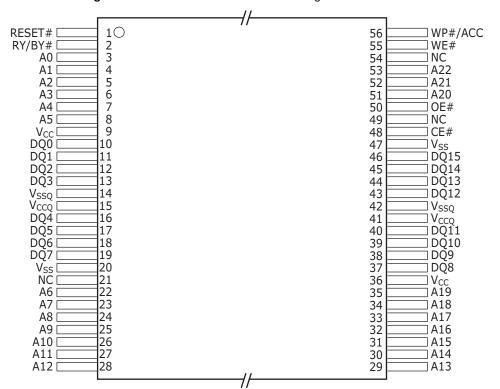

#### 8.5 56-Pin TSOP 20 x 14 mm

Figure 8.4 56-Pin TSOP 20 x 14 mm Configuration—PL127J

For this family of products, a single multi-chip compatible package (TSOP) is offered for each density to allow both standalone and multi-chip qualification using a single, adaptable package. This new methodology allows package standardization resulting in faster development. The multi-chip compatible package includes all the pins required for standalone device operation and verification. In addition, extra pins are included for insertion of common data storage or logic devices to be used for multi-chip products. If a standalone device is required, the extra multi-chip specific pins are not connected and the standalone device operates normally. The multi-chip compatible package sizes were chosen to serve the largest number of combinations possible. There are only a few cases where a larger package size would be required to accommodate the multi-chip combination. This multi-chip compatible package set does not allow for direct package migration from the Am29BDS128H, Am29BDS128G, Am29BDS640G products, which use legacy standalone packages.

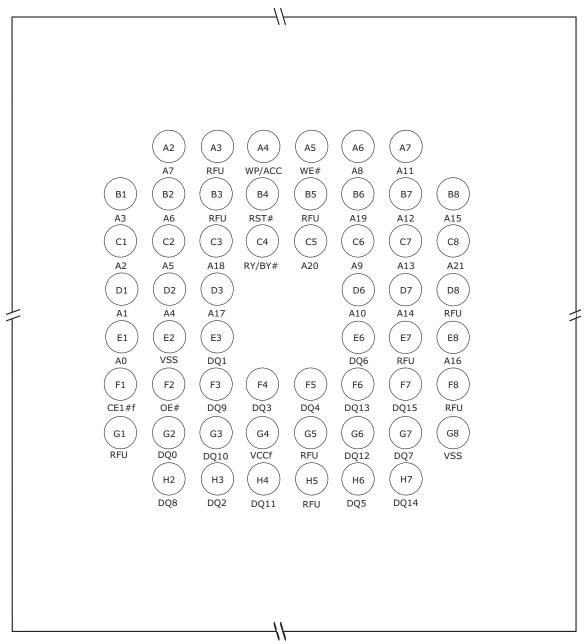

#### 8.6 56-Ball Fine-Pitch Ball Grid Array, PL064J and PL032J

Figure 8.5 56-ball Fine-Pitch BGA, Top View, Balls Facing Down,—PL064J and PL032J,

## 9. Pin Description

#### Table 9.1 Pin Description

| Amax–A0         | Address bus                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ15–DQ0        | 16-bit data inputs/outputs/float                                                                                                                                                                                                                                                                                                                                                 |

| CE#             | Chip Enable Inputs                                                                                                                                                                                                                                                                                                                                                               |

| OE#             | Output Enable Input                                                                                                                                                                                                                                                                                                                                                              |

| WE#             | Write Enable                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>SS</sub> | Device Ground                                                                                                                                                                                                                                                                                                                                                                    |

| NC              | Not Connected. No device internal signal is connected to the package connector nor is there any future plan to use the connector for a signal. The connection may safely be used for routing space for a signal on a Printed Circuit Board (PCB).                                                                                                                                |

| RFU             | Reserved for Future Use. Not currently connected internally but the pin/ball location should be left unconnected and unused by PCB routing channel for future compatibility. The pin/ball may be used by signal in the future.                                                                                                                                                   |

| RY/BY#          | Ready/Busy output and open drain.<br>When RY/BY#= $V_{IH}$ , the device is ready to accept read operations and commands. When RY/BY#= $V_O$ the device is either executing an embedded algorithm or the device is executing a hardware reset operation.                                                                                                                          |

| WP#/ACC         | Write Protect/Acceleration Input.           When WP#/ACC= V <sub>IL</sub> , the highest and lowest two 4K-word sectors are write protected regardless of other sector protection configurations. When WP#/ACC= V <sub>IH</sub> , these sector are unprotected unless the DYB or PPB is programmed. When WP#/ACC= V <sub>IH</sub> , program and erase operations are accelerated. |

| V <sub>IO</sub> | Input/Output Buffer Power Supply<br>(1.65 V to 1.95 V (for PL127J and PL129J) or 2.7 V to 3.6 V (for all PLxxxJ devices))                                                                                                                                                                                                                                                        |

| V <sub>CC</sub> | Chip Power Supply<br>(2.7 V to 3.6 V or 2.7 to 3.3 V)                                                                                                                                                                                                                                                                                                                            |

| RESET#          | Hardware Reset Pin                                                                                                                                                                                                                                                                                                                                                               |

| CE1#, CE2#      | Chip Enable Inputs.<br>CE1# controls the 64Mb in Banks 1A and 1B.<br>CE2# controls the 64 Mb in Banks 2A and 2B. (Only for PL129J)                                                                                                                                                                                                                                               |

Note

Amax = A22 (PL127J), A21 (PL129J and PL064J), A20 (PL032J)

## 10. Logic Symbol

## **11. Device Bus Operations**

This section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register itself does not occupy any addressable memory location. The register is a latch used to store the commands, along with the address and data information needed to execute the command. The contents of the register serve as inputs to the internal state machine. The state machine outputs dictate the function of the device. Table 11.1 lists the device bus operations, the inputs and control levels they require, and the resulting output. The following subsections describe each of these operations in further detail.

| Operation                                 | CE#                    | OE# | WE# | RESET#                 | WP#/<br>ACC   | Addresses<br>(Amax–A0) | DQ15–DQ0         |

|-------------------------------------------|------------------------|-----|-----|------------------------|---------------|------------------------|------------------|

| Read                                      | L                      | L   | Н   | Н                      | Х             | A <sub>IN</sub>        | D <sub>OUT</sub> |

| Write                                     | L                      | Н   | L   | Н                      | X<br>(Note 2) | A <sub>IN</sub>        | D <sub>IN</sub>  |

| Standby                                   | V <sub>IO</sub> ±0.3 V | Х   | х   | V <sub>IO</sub> ±0.3 V | X<br>(Note 2) | Х                      | High-Z           |

| Output Disable                            | L                      | Н   | Н   | Н                      | Х             | Х                      | High-Z           |