Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

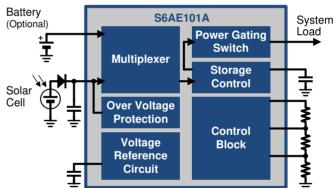

# Energy Harvesting PMIC for Wireless Sensor Node

The S6AE101A is a power management IC (PMIC) for energy harvesting that is built into circuits of solar cells connected in series, output power control circuits, output capacitor storage circuits, and power switching circuits of primary batteries. Super-low-power operation is possible using a consumption current of only 250 nA and startup power of only 1.2 µW. As a result, even slight amounts of power generation can be obtained from compact solar cells under low-brightness environments of approximately 100 lx. The S6AE101A stores power generated by solar cells to an output capacitor using built-in switch control, and it turns on the power switching circuit while the capacitor voltage is within a preset maximum and minimum range for supplying energy to a load. If the power generated from solar cells is not enough, energy can also be supplied in the same way as solar cells from connected primary batteries for auxiliary power. Also, an over voltage protection (OVP) function is built into the input pins of the solar cells, and the open voltage of solar cells is used by this IC to prevent an overvoltage state. The S6AE101A is provided as a battery-free wireless sensor node solution that is operable by super-compact solar cells.

#### **Features**

- Input power selection control: Solar cell or primary battery

- ■Operated by solar cells without the need for primary batteries

- ■Storage of energy from power supply to storage capacitors

- ■Output power gating control, output voltage regulation

■Operation input voltage range

□ Solar cell power : 2.0V to 5.5V □ Primary battery power : 2.0V to 5.5V

■Adjustable output voltage range : 1.1V to 5.2V

■Low-consumption current : 250 nA

■Minimum input power at startup : 1.2 µW

■Input overv oltage protection : 5.4V

■Compact SON-10 package : 3 mm×3 mm

## Block Diagram

#### **Applications**

- ■Energy harvesting power system with a very small solar cell

- ■Bluetooth® Smart sensor

- ■Wireless HVAC sensor

- ■Wireless lighting control

- ■Security system

- ■Smart home / Building / Industrial wireless sensor

## **Contents**

| Features                                      | 1  |

|-----------------------------------------------|----|

| Applications                                  | 1  |

| Block DiagramBlock Diagram                    | 1  |

| 1. Pin Assignment                             | 3  |

| 2. Pin Descriptions                           | 3  |

| 3. Architecture Block Diagram                 | 4  |

| 4. Absolute Maximum Ratings                   | 5  |

| 5. Recommended Operating Conditions           | 5  |

| 6. Electrical Characteristics                 | 6  |

| 7. Functional Description                     | 7  |

| 7.1 Power Supply Control                      | 7  |

| 7.2 Power Gating                              | 14 |

| 7.3 Discharge                                 | 14 |

| 7.4 Over Voltage Protection (OVP Block)       | 14 |

| 8. Application Circuit Example and Parts list | 15 |

| 9. Application Note                           | 16 |

| 9.1 Setting the Operation Conditions          | 16 |

| 9.2 PCB Layout                                | 17 |

| 10. Development Support                       | 17 |

| 11. Reference Data                            |    |

| 12. Usage Precaution                          |    |

| 13. RoHS Compliance Information               | 20 |

| 14. Ordering Information                      | 20 |

| 15. Package Dimensions                        |    |

| 16. Major Changes                             | 22 |

| Document History                              |    |

| Sales, Solutions, and Legal Information       | 23 |

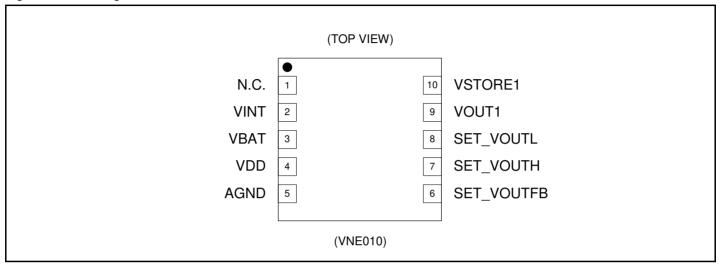

## 1. Pin Assignment

Figure 1-1 Pin Assignment

## 2. Pin Descriptions

**Table 2-1 Pin Descriptions**

| Pin No. | Pin Name   | I/O | Description                                                           |

|---------|------------|-----|-----------------------------------------------------------------------|

| 1       | N.C        | -   | Non connection pin (Leave this pin open)                              |

| 2       | VINT       | 0   | Internal circuit storage output pin                                   |

| 3       | VBAT       | I   | Primary battery input pin (when being not used, leave this pin open ) |

| 4       | VDD        | I   | Solar cell input pin (when being not used, leave this pin open )      |

| 5       | AGND       | -   | Ground pin.                                                           |

| 6       | SET_VOUTFB | 0   | Reference voltage output pin (for connecting resistor)                |

| 7       | SET_VOUTH  | I   | VOUT1 output voltage setting pin (for connecting resistor)            |

| 8       | SET_VOUTL  | I   | VOUT1 output voltage setting pin (for connecting resistor)            |

| 9       | VOUT1      | 0   | Output voltage pin                                                    |

| 10      | VSTORE1    | 0   | Storage output pin                                                    |

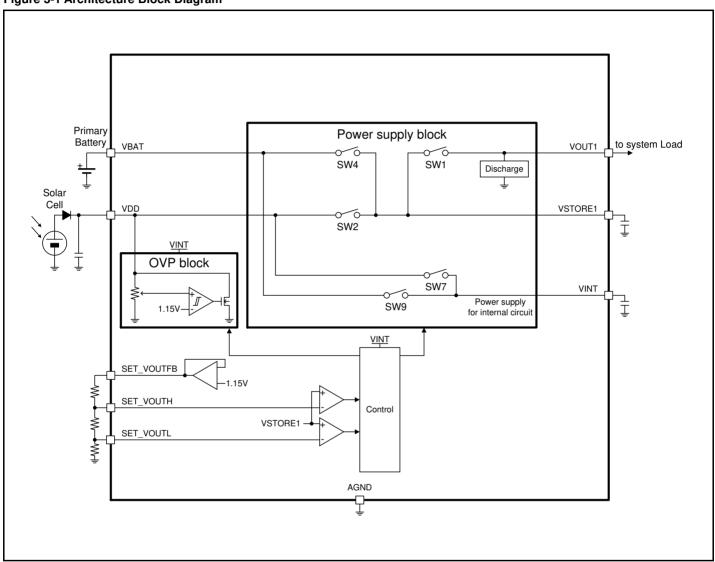

Figure 2-1 I/O Pin Equivalent Circuit Diagram

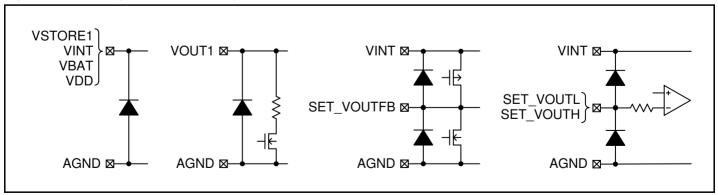

## 3. Architecture Block Diagram

Figure 3-1 Architecture Block Diagram

## 4. Absolute Maximum Ratings

| Parameter                 | Symbol                | Condition                | Rat  | Unit      |       |

|---------------------------|-----------------------|--------------------------|------|-----------|-------|

| Farameter                 | Syllibol              | Condition                | Min  | Max       | Ollit |

| Power supply voltage (*1) | $V_{MAX}$             | VDD, VBAT pin            | -0.3 | +6.9      | V     |

| Signal input voltage(*1)  | V <sub>INPUTMAX</sub> | SET_VOUTH, SET_VOUTL pin | -0.3 | $V_{VDD}$ | V     |

| VDD slew rate             | V <sub>SLOPE</sub>    | VDD pin                  | -    | 0.1       | mV/μs |

| Power dissipation (*1)    | P <sub>D</sub>        | Ta ≤+ 25°C               | -    | 1200 (*2) | mW    |

| Storage temperature       | T <sub>STG</sub>      | -                        | -55  | +125      | °C    |

<sup>\*1:</sup> When GND=0V

#### Warning:

1. Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

### 5. Recommended Operating Conditions

| Parameter                     | Cumphal            | 0-                                                |                          |     | Value |                        | Unit |

|-------------------------------|--------------------|---------------------------------------------------|--------------------------|-----|-------|------------------------|------|

| Parameter                     | Symbol             | Co                                                | Condition                |     | Тур   | Max                    | Unit |

| Power supply voltage 1 (*1)   | $V_{VDD}$          | VDD pin                                           |                          | 2.0 | 3.3   | 5.5                    | V    |

| Power supply voltage 2 (*1)   | $V_{VBAT}$         | VBAT pin                                          |                          | 2.0 | 3.0   | 5.5                    | V    |

| Signal input voltage (*1)     | V <sub>INPUT</sub> | SET_VOUTH, SET_VOUTL pin                          |                          | -   | -     | VINT pin<br>voltage    | ٧    |

| VOUT1 setting resistance      | R <sub>VOUT</sub>  | Sum of R1, R2, R3                                 |                          | 10  | -     | 50                     | ΜΩ   |

| VDD capacitance               | C1                 | VDD pin                                           |                          | 10  | _     | -                      | μF   |

| VINT capacitance              | C2                 | VINT pin                                          |                          | 1   | -     | -                      | μF   |

| VSTORE1 capacitance           | C3                 | VSTORE1 pin                                       |                          | 100 | -     | -                      | μF   |

| VOUT maximum setting voltage  | V <sub>SYSH</sub>  | VSTORE1 pin                                       |                          | 1.3 | -     | 5.2                    | ٧    |

| VOUT minimum setting          | V                  | VCTODE1 nin                                       | V <sub>SYSH</sub> ≥ 1.7V | 1.1 | _     | $V_{SYSH} \times 0.90$ | V    |

| voltage                       | $V_{SYSL}$         | VSTORE1 pin $\frac{VSYSH \ge 1.7V}{VSYSH < 1.7V}$ |                          | 1.1 | -     | $V_{SYSH} \times 0.85$ | V    |

| Operating ambient temperature | Ta                 |                                                   | -                        | -40 | _     | +85                    | °C   |

<sup>\*1:</sup> When GND = 0V

#### Warning:

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

<sup>\*2:</sup> θja (wind speed 0m/s): +58°C/W

#### 6. Electrical Characteristics

The electrical characteristics excluding the effect of external resistors and external capacitors are shown in below.

Table 6-1 Electrical Characteristics (System Overall)

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Davamatav                               | Cumahal             | O a m dit                                                                                                             | !a=                    |                                | Value                        |                                | I I m i A |

|-----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|------------------------------|--------------------------------|-----------|

| Parameter                               | Symbol              | Condition                                                                                                             |                        | Min                            | Тур                          | Max                            | Unit      |

| Minimum Input power in start-up         | W <sub>START</sub>  | VDD pin, Ta = +25°C, No. 10 states 3V × 95% after VDD reaches 3V.                                                     | -                      | -                              | 1.2                          | μW                             |           |

| Consumption current 1                   | I <sub>QIN1</sub>   | VDD pin input current, VDD=3V, Open VBAT pin, SW2 = OFF, Ta = +25°C, SET_VOUTFB resistance = 50 MΩ, VOUT1 Load = 0 mA |                        | -                              | 250                          | 390                            | nA        |

| Power detection voltage                 | $V_{DETH}$          | VDD, VBAT ,VINT pin                                                                                                   |                        | 1.0                            | 1.4                          | 2.0                            | V         |

| Power undetection voltage               | $V_{DETL}$          | VDD, VBAT ,VINT pin                                                                                                   |                        | 0.9                            | 1.3                          | 1.9                            | V         |

| Power detection hysteresis              | $V_{DETHYS}$        | VDD, VBAT ,VINT pin                                                                                                   |                        | -                              | 0.1                          | -                              | ٧         |

| VOUT maximum voltage                    |                     | VSTORE1 pin,<br>VOUT1 Load=0 mA                                                                                       | V <sub>SYSH</sub> ≥ 2V | $V_{SYSH} \times 0.950$        | $V_{SYSH}$                   | V <sub>SYSH</sub> ×1.050       | V         |

| VOOT maximum voitage                    | V VOUTH             |                                                                                                                       | V <sub>SYSH</sub> < 2V | $V_{SYSH} \times 0.935$        | $V_{SYSH}$                   | V <sub>SYSH</sub> ×1.065       | V         |

| Input power reconnect                   | V                   | VSTORE1 pin,                                                                                                          | V <sub>SYSH</sub> ≥2V  | V <sub>VOUTH</sub><br>×0.90250 | V <sub>VOUTH</sub><br>× 0.95 | V <sub>VOUTH</sub> × 0.99750   | ٧         |

| voltage                                 | $V_{VOUTM}$         | VOUT1 Load=0 mA                                                                                                       | V <sub>SYSH</sub> < 2V | V <sub>VOUTH</sub><br>×0.88825 | V <sub>VOUTH</sub><br>× 0.95 | V <sub>VOUTH</sub><br>×1.01175 | ٧         |

| VOLIT minimum voltage                   | V                   | VSTORE1 pin,                                                                                                          | V <sub>SYSL</sub> ≥ 2V | V <sub>SYSL</sub> ×0.950       | $V_{SYSL}$                   | V <sub>SYSL</sub> ×1.050       | ٧         |

| VOUT minimum voltage V <sub>VOUTL</sub> |                     | VOUT1 Load=0 mA                                                                                                       | V <sub>SYSL</sub> < 2V | V <sub>SYSL</sub> ×0.935       | $V_{SYSL}$                   | V <sub>SYSL</sub> ×1.065       | ٧         |

| OVP detection voltage                   | $V_{OVPH}$          | VDD pin                                                                                                               |                        | 5.2                            | 5.4                          | 5.5                            | ٧         |

| OVP release voltage                     | $V_{OVPL}$          | VDD pin                                                                                                               |                        | 5.1                            | 5.3                          | 5.4                            | ٧         |

| OVP detection hysteresis                | V <sub>OVPHYS</sub> | VDD pin                                                                                                               |                        | _                              | 0.1                          | _                              | V         |

| OVP protection current                  | $I_{OVP}$           | VDD pin input current                                                                                                 |                        | 6                              | -                            | _                              | mA        |

#### **Table 6-2 Electrical Characteristics (Switch)**

$\mathsf{VDD} \geq \mathsf{3V},\, \mathsf{VBAT} \geq \mathsf{3V},\, \mathsf{VINT} \geq \mathsf{3V},\, \mathsf{V}_{\mathsf{VOUTL}} \geq \mathsf{3V},\, \mathsf{VSTORE1} \geq \mathsf{V}_{\mathsf{VOUTL}}$

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

| Parameter            | Symbol           | Condition                                       | Value |     |     |      |

|----------------------|------------------|-------------------------------------------------|-------|-----|-----|------|

| Farameter            | Syllibol         | Condition                                       | Min   | Тур | Max | Unit |

| On resistance 1      | R <sub>ON1</sub> | SW1, In connection of VSTORE1 pin and VOUT1 pin | ı     | 1.5 | 2.5 | Ω    |

| On resistance 2      | R <sub>ON2</sub> | SW2, In connection of VDD pin and VSTORE1 pin   | -     | 5   | 10  | kΩ   |

| On resistance 4      | R <sub>ON4</sub> | SW4, In connection of VDD pin and VSTORE1 pin   | -     | 5   | 10  | kΩ   |

| Discharge resistance | R <sub>DIS</sub> | VOUT1 pin                                       | ı     | 1   | 2   | kΩ   |

Document Number: 002-08493 Rev. \*B Page 6 of 23

## 7. Functional Description

#### 7.1 Power Supply Control

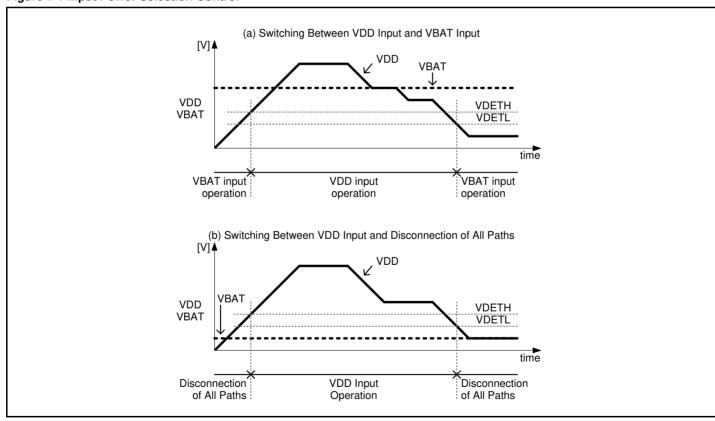

This IC can operate by two input power supplies, namely, the solar cell voltage VDD and the primary battery voltage VBAT. The voltages at the VDD pin and VBAT pin are monitored, and selection control of the input power supply is performed based on this voltage state (Figure 7-1).

The input power (solar cell or primary battery) is temporarily stored to a capacitor connected to the VSTORE1 pin. When the voltage of the VSTORE1 pin reaches a certain threshold value or higher, the power switching switch (SW1) connects VSTORE1 and VOUT1.

**Table 7-1 Input Power Supply Selection Control**

| VDD Voltage (Solar Cell)          | VBAT Voltage (Primary Battery)      | Operation                            |

|-----------------------------------|-------------------------------------|--------------------------------------|

| $V_{DETH}$ (1.55V) or higher      | V <sub>DETH</sub> (1.55V) or higher | VDD input power supply is performed  |

|                                   | V <sub>DETL</sub> (1.45V) or less   | VDD input power supply is performed  |

| \/ (1.45\/) or loss               | V <sub>DETH</sub> (1.55V) or higher | VBAT input power supply is performed |

| V <sub>DETL</sub> (1.45V) or less | V <sub>DETL</sub> (1.45V) or less   | All paths are disconnected           |

Figure 7-1 Input Power Selection Control

#### 1. VDD input voltage operation

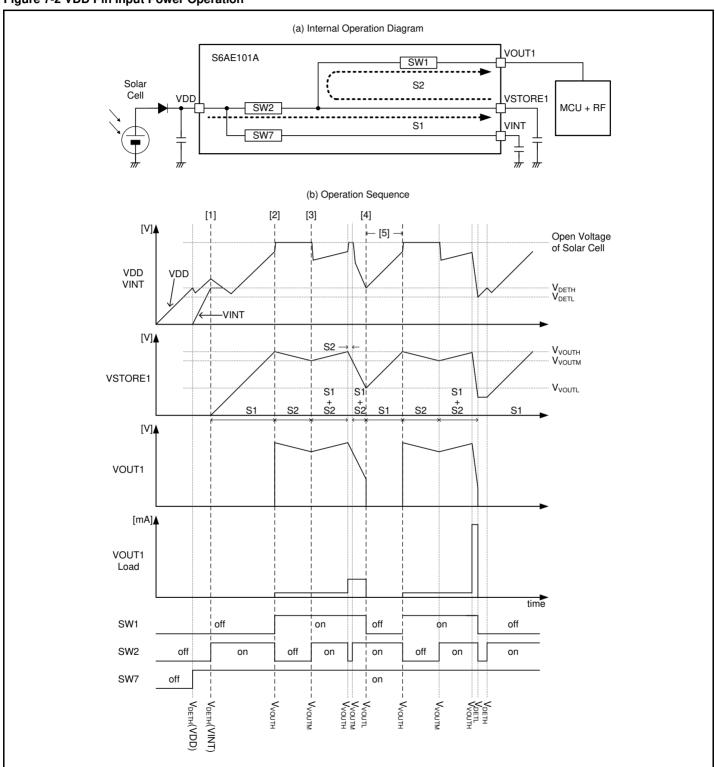

This section describes operation when the VDD pin is set as the input power (Figure 7-2).

- [1] When the voltage of the VDD pin reaches the power detection voltage ( $V_{DETH} = 1.55V$ ) or higher, the switch (SW2) connects VDD and VSTORE1 (path S1). Also, when the voltage of the VDD pin falls to the power undetection voltage ( $V_{DETL} = 1.45V$ ) or less, SW2 disconnects the path S1.

- [2] When the voltage of the VSTORE1 pin reaches the threshold value ( $V_{VOUTH}$ ) or higher that was set by the SET\_VOUTH pin, SW2 disconnects the path S1. Also, the VOUT switch (SW1) connects VSTORE1 and VOUT1 (path S2).

- [3] When the voltage of the VSTORE1 pin falls to the input power reconnect voltage (V<sub>VOUTM</sub>) or less, SW2 connects the path S1 (path S1+S2).

- [4] In addition, when the voltage falls to the threshold value (V<sub>VOUTL</sub>) or less that was set by the SET\_VOUTL pin, SW1 disconnects the path S2.

- [5] When SW1 disconnects the path S2, the discharge function is activated.

Figure 7-2 VDD Pin Input Power Operation

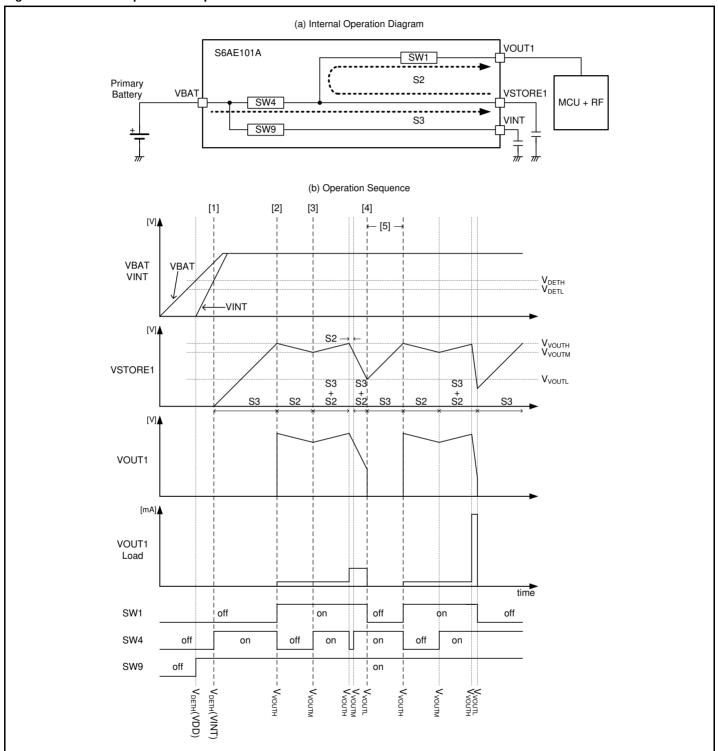

#### 2. VBAT input voltage operation

This section describes operation when the VBAT pin is set as the input power (Figure 10-3).

- [1] When the voltage of the VBAT pin reaches the power detection voltage (VDETH = 1.55V) or higher, the switch (SW2) connects VBAT and VSTORE1 (path S3). Also, when the voltage of the VDD pin falls to the power undetection voltage (VDETL = 1.45V) or less, SW4 disconnects the path S3.

- [2] When the voltage of the VSTORE1 pin reaches the threshold value (VVOUTH) or higher that was set by the SET\_VOUTH pin, SW4 disconnects the path S3. Also, the VOUT switch (SW1) connects VSTORE1 and VOUT1 (path S2).

- [3] When the voltage of the VSTORE1 pin falls to the input power reconnect voltage (VVOUTM) or less, SW4 connects the path S3 (path S3+S2).

- [4] In addition, when the voltage falls to the threshold value (VVOUTL) or less that was set by the SET\_VOUTL pin, SW1 disconnects the path S2.

- [5] When SW1 disconnects the path S2, the discharge function is activated.

**Figure 7-3 VBAT Pin Input Power Operation**

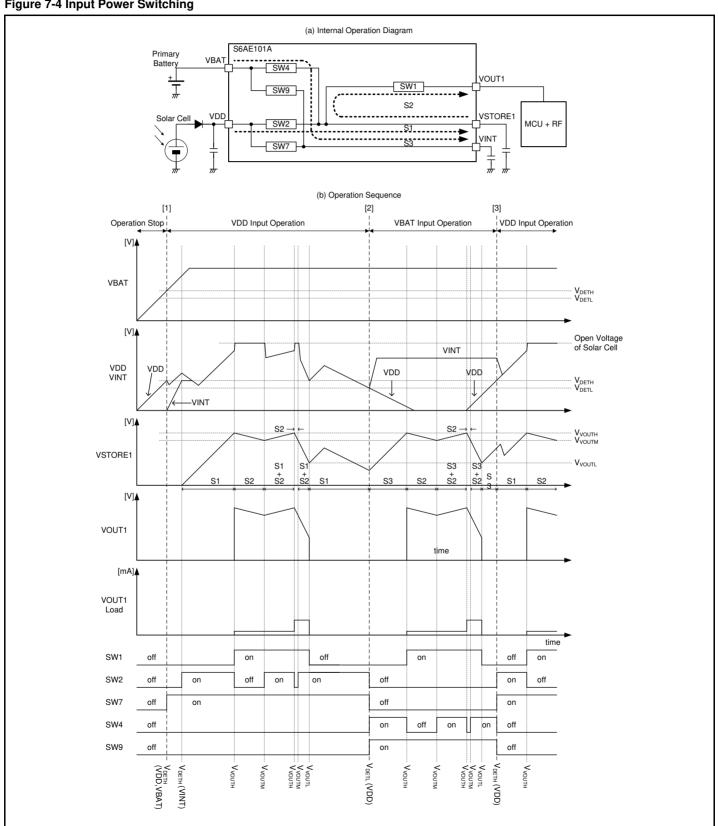

#### 3. Input power supply switching

This section describes the input power switching operation (Figure 7-4).

- [1] If the voltages of the VDD pin and VBAT pin increase from a state where both are less than the power detection voltage (V<sub>DETH</sub> = 1.55V) so that the voltage of the VDD pin reaches the power detection voltage (V<sub>DETH</sub> = 1.55V) or higher, and operation switches to VDD input power operation back from the stage of disconnecting all paths.

- [2] When the voltage of the VBAT pin increases to the power detection voltage (V<sub>DETH</sub> = 1.55V) or higher, if the power from the solar cell is reduced, and when the voltage of the VDD pin falls to the power undetection voltage (V<sub>DETL</sub> = 1.45V) or less, operation switches from VDD input power operation to VBAT input power operation.

- [3] When the amount of power supplied from the solar cell increases, and the voltage of the VDD pin reaches the power detection voltage (V<sub>DETH</sub> = 1.55V) or higher, operation switches back to VDD input power operation. After switching, operation is performed based on VDD input power operation.

Figure 7-4 Input Power Switching

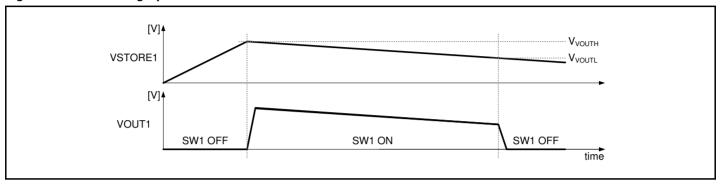

#### 7.2 Power Gating

This IC has a power gating function for the external system. Once it is detected that the voltage of the VSTORE1 pin has reached the VOUT maximum voltage (VVOUTH), the VSTORE1 pin and VOUT pin are connected by an internal switch until the VOUT minimum voltage (VVOUTL) is reached.

Figure 7-5 Power Gating Operation

#### 7.3 Discharge

This IC includes a VOUT1 pin discharge function.

When SW1 disconnects the VSTORE1 and VOUT1 path, the discharge circuit is activated between the VOUT1 pin and GND. The power of the VOUT1 pin is discharged to the GND level.

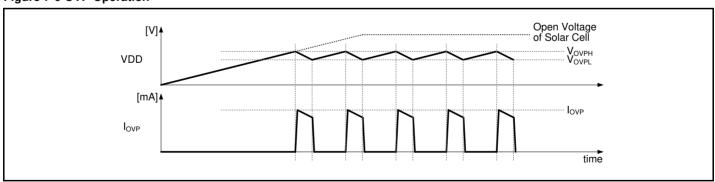

#### 7.4 Over Voltage Protection (OVP Block)

This IC includes an input overvoltage protection (OVP) function for the VDD pin voltage.

When the VDD pin voltage reaches the OVP detection voltage ( $V_{OVPH}=5.4V$ ) or higher, the OVP current (IOVP) from the VDD pin is drawn in for limiting the increase in the VDD pin voltage for preventing damage to the IC. Also, when the OVP release voltage ( $V_{OVPL}=5.3V$ ) or less is reached, drawing-in of the OVP current is stopped.

Figure 7-6 OVP Operation

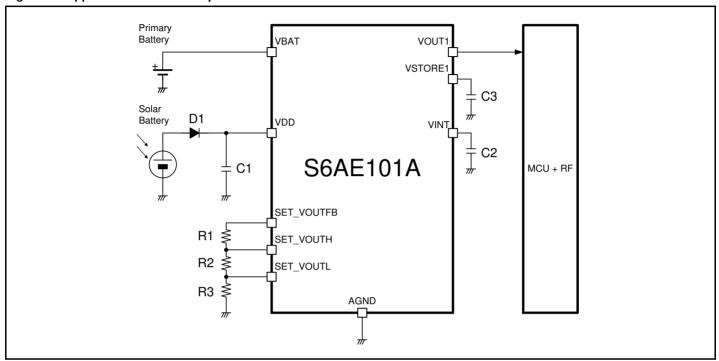

## 8. Application Circuit Example and Parts list

Figure 8-1 Application Circuit Example

**Table 8-1 Parts List**

| Symbol | Item              | Value       | Remarks |

|--------|-------------------|-------------|---------|

| C1     | Ceramic capacitor | 10 μF       | -       |

| C2     | Ceramic capacitor | 1 µF        | -       |

| C3     | Ceramic capacitor | 100 μF      | -       |

| R1     | Resistor          | 6.8 MΩ (*1) | -       |

| R2     | Resistor          | 2.7 MΩ (*1) | -       |

| R3     | Resistor          | 9.1 ΜΩ (*1) | -       |

| D1     | Diode             | -           | -       |

<sup>\*1:</sup> Setting of VOUT maximum voltage:  $V_{VOUTH} \approx 3.3 V$ , VOUT minimum voltage:  $V_{VOUTL} \approx 2.6 V$ .

#### 9. Application Note

#### 9.1 Setting the Operation Conditions

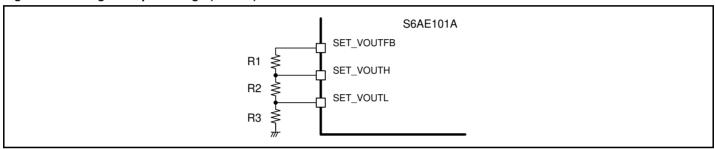

#### Setting of output voltage (VOUT1)

The resistor connecting the SET\_VOUTH pin and SET\_VOUTL pin can be changed to set the VOUT1 output voltage of this IC. This is because the VOUT maximum voltage (V<sub>VOUTH</sub>) and VOUT minimum voltage (V<sub>VOUTL</sub>) are set based on the connected resistance. The SET\_VOUTFB pin outputs a reference voltage for setting the VOUT maximum voltage and VOUT minimum voltage. Resistor voltage division can be performed on this reference voltage outside the IC for creating a voltage applied to the SET\_VOUTH pin and SET\_VOUTL pin.

Figure 9-1 Setting of output voltage (VOUT1)

The VOUT maximum voltage (V<sub>VOUTH</sub>) and VOUT minimum voltage (V<sub>VOUTL</sub>) can be calculated using the formulas below.

VOUT maximum voltage

$$V_{\text{VOUTH}}[V] = \frac{57.5 \times (R2 + R3)}{11.1 \times (R1 + R2 + R3)}$$

VOUT minimum voltage

$$V_{VOUTL}[V] = \frac{57.5 \times R3}{11.1 \times (R1 + R2 + R3)}$$

The characteristics when the total value for R1, R2, and R3 is from 10 M $\Omega$  to 50 M $\Omega$  are shown in "6. Electrical Characteristics".

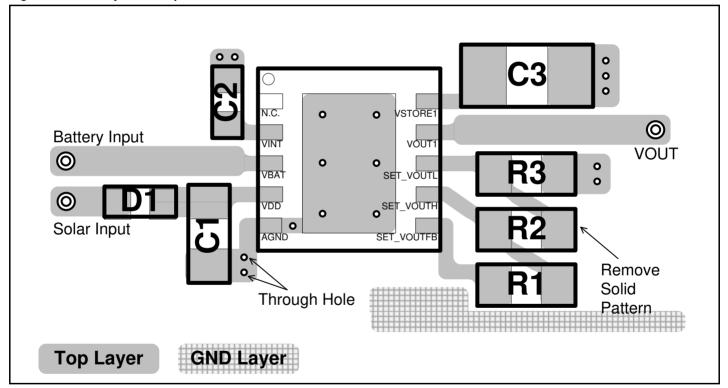

#### 9.2 PCB Layout

#### Take into account the following points when designing the layout.

- □ Try to route the wiring for the diode (D1) and input capacitor (C1) for connecting the solar cell on the top layer as m uch as possible, and avoid implementing a connection using a through hole.

- □ For the AGND pin of S6AE101A, provide a through hole nearby, and connect it to the GND plane.

- □ Locate the capacitor (C2) for the internal power as near as possible to the VINT pin.

- □ Locate the resistors (R1, R2, R3) for setting the output voltage in a grid-type configuration with small loops, and locat e them as near as possible to each pin (SET\_VOUTFB, SET\_VOUTH, SET\_VOUTL). Also, removing the GND plane under the parts can be effective in preventing malfunctions due to the leakage current.

- □ To prevent a leakage current, locate and route the storage capacitor (C3) as far as possible from patterns that are different from the electrical potential of VSTORE1 (such as the GND line). Generally, the insulation resistor of printed circuit boards is extremely high, and normally, the passing of leakage current through the board does not pose a proble m. However, in certain rare cases, the surface of the board may have a low insulation resistance, and when using these boards, a leakage current that cannot be ignored may occur.

Figure 9-2 PCB Layout Example

#### 10. Development Support

This IC has a set of documentation, such as application notes, development tools, and online resources to assist you during your development process. Visit <a href="https://www.cypress.com/energy-harvesting">www.cypress.com/energy-harvesting</a> to find out more.

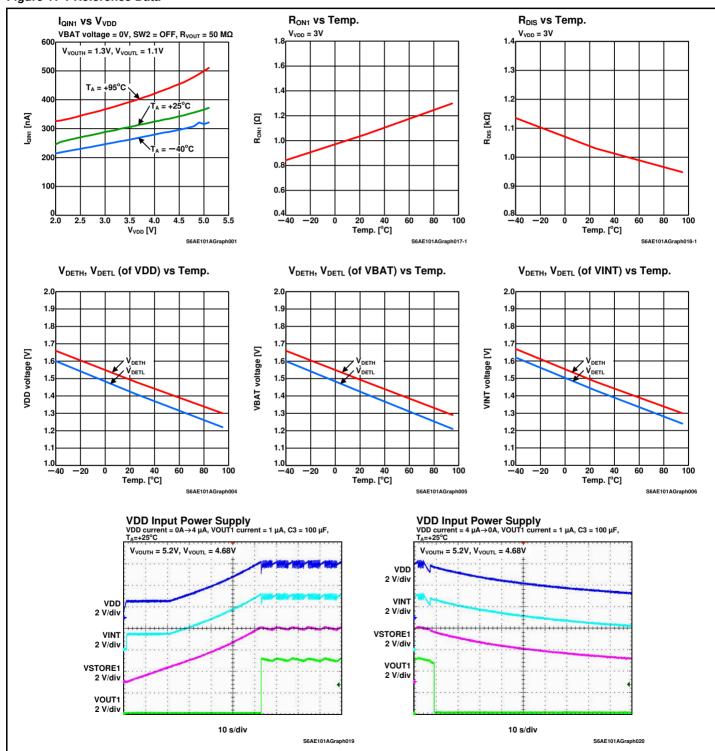

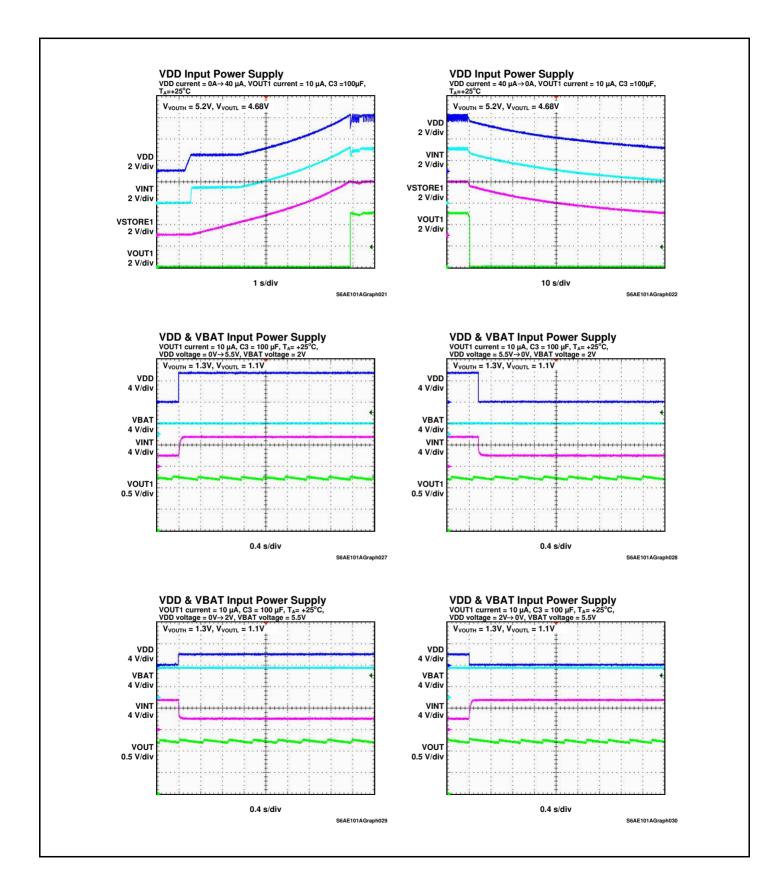

#### 11. Reference Data

For the circuit diagram of the reference data, Refer to "Figure 8-1 Application Circuit Example".

Figure 11-1 Reference Data

#### 12. Usage Precaution

Printed circuit board ground lines should be set up with consideration for common impedance.

#### Take appropriate measures against static electricity.

- □ Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- □ After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- □ Work platforms, tools, and instruments should be properly grounded.

- $\square$  Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  in serial body and ground.

#### Do not apply negative voltages.

The use of negative voltages below -0.3 V may make the parasitic transistor activated to the LSI, and can cause malfunctions.

#### 13. RoHS Compliance Information

This product has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

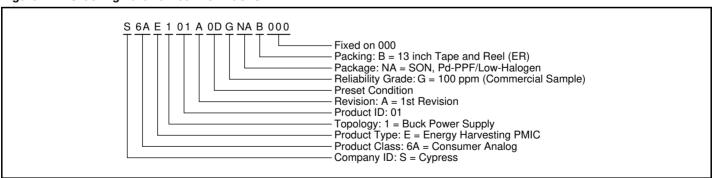

#### 14. Ordering Information

#### **Table 14-1 Ordering Part Number**

| Part number (MPN) | Package                                   |

|-------------------|-------------------------------------------|

| S6AE101A0DGNAB000 | 10-pin plastic SON (0.5mm pitch) (VNE010) |

MPN: Marketing Part Number

#### Figure 14-1 Ordering Part Number Definitions

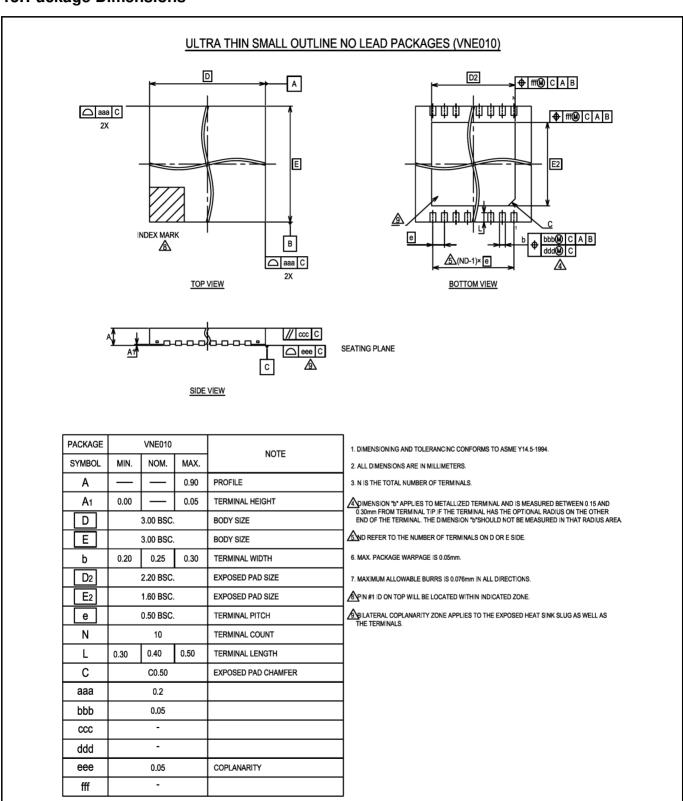

## 15. Package Dimensions

## 16. Major Changes

Spansion Publication Number: S6AE101A\_DS405-00026

| Page       | Section         | Change Results  |  |  |  |  |  |

|------------|-----------------|-----------------|--|--|--|--|--|

| Preliminar | Preliminary 0.1 |                 |  |  |  |  |  |

| _          | -               | Initial release |  |  |  |  |  |

NOTE: Please see "Document History" about later revised information.

## **Document History**

Document Title: S6AE101A Energy Harvesting PMIC for Wireless Sensor Node

Document Number: 002-08493

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                            |

|----------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | -       | TAOA               | 04/27/2015         | New Spec.                                                                                                                                                                                                                                                        |

| *A       | 5054369 | TAOA               | 12/17/2015         | Added Block Diagram  Updated 5. Recommended Operating Conditions  Updated 6. Electrical Characteristics  Updated Table 8-1 Parts List  Updated 9.1 Setting the Operation Conditions: Changed the formulas for the VOUT maximum voltage and VOUT minimum voltage. |

| *B       | 5103619 | HIXT               | 01/25/2016         | Added Figure 2-1 I/O Pin Equivalent Circuit Diagram  Updated Figure 3-1 Architecture Block Diagram  Added 10. Development Support  Added 11. Reference Data                                                                                                      |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Wireless/RF

Automotive cypress.com/go/automotive

Clocks & Buffers cypress.com/go/clocks

Interface cypress.com/go/interface

Lighting & Power Control cypress.com/go/powerpsoc

Memory cypress.com/go/memory

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/USB

cypress.com/go/wireless

Spansion Products cypress.com/spansionproducts

#### **PSoC® Solutions**

psoc.cypress.com/solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

#### **Technical Support**

cypress.com/go/support

Cypress, the Cypress logo, Spansion®, the Spansion logo, MirrorBit®, MirrorBit®, Eclipse<sup>TM</sup>, ORNAND<sup>TM</sup>, Easy DesignSim<sup>TM</sup>, Traveo<sup>TM</sup> and combinations thereof, are trademarks and registered trademarks of Cypress Semiconductor Corp. ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

© Cypress Semiconductor Corporation, 2015-2016. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 002-08493 Rev. \*B January 25, 2016 Page 23 of 23