Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

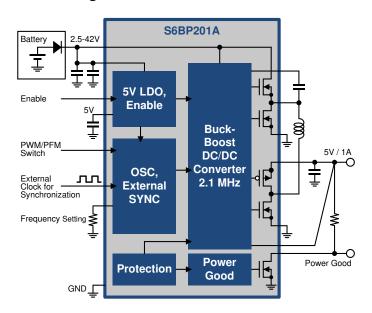

# ASSP, 42V, 1A, Synchronous Buck-boost DC/DC Converter IC

S6BP201A is a 1ch Buck-boost DC/DC converter IC with four built-in switching FETs. This IC is able to supply up to 1.0A of load current within the very wide range from 2.5V to 42V in the input voltage. This IC has an operation mode that is automatically changed to PFM operation during low load, which can achieve super-high efficiency with a very low quiescent current 20 μA. It is possible to provide stable output voltage from an automotive cold cranking and load dump, up to 42V, conditions within 1 ms transition time. As a result, this IC is suitable for power supply solutions of automotive and Industrial applications. This IC has the SYNC function, which is capable of selecting the SYNC\_IN that is able to inputs an external clock signal. When an external clock signal in the range from 200 kHz to 400 kHz is inputted, the FETs perform the switching operation with synchronizing signal from an external clock. When an external clock signal is not inputted, the FETs perform the switching operation from an internal clock. The internal clock signal in the range from 200 kHz to 2.1 MHz can be set by an external resistor. Since external voltage setting resistors and phase compensation capacitors are not required with this IC, it can reduce the number of parts and a part mounting area. This IC has five protection (output OVP), output over voltage lockout (input UVLO), output under voltage protection (output UVP), output over voltage protection (output OVP), output over current protection (output OCP), and thermal shutdown (TSD). Moreover, this IC has the power good (PG) function that indicates the state of the output voltage (VOUT pin). When the output voltage reaches the PG voltage, the PG signal is outputted. The VOUT output voltage of this product is selectable from the product lineup (refer to the "1. Product Lineup").

#### **Features**

- ■Wide input voltage range: 2.5V to 42V

- Selectable output voltage (factory settable): 5.000V/5.050V/5.075V/5.100V/5.125V/5.150V/5.200V

- ■Wide operating frequency range: 200 kHz to 2.1 MHz

- ■External synchronized clock range: 200 kHz to 400 kHz

- ■SYNC function

- □ SYNC\_IN: External clock input (Unless inputting clock, this IC operates by internal clock)

- ■Super-high efficiency by PFM operation (When setting MODE pin to a low level)

- Automatic PWM/PFM switching operation and fixed PWM operation are selectable by MODE pin

- ■Built-in switching FET

- Synchronous current mode architecture

- Shutdown current: Lower than 1 µA

- ■Quiescent current: 20 µA

- Power Good Monitor

- □ Output voltage monitoring by window comparator

- □ Power-on reset time: 14 ms

- Soft start time without load dependence : 0.9 ms (When switching frequency = 2.1 MHz)

- Enhanced protection functions

- □ Input under voltage lockout

- □ Output under voltage protection: 95.5%

- □ Output over voltage protection: 104.5%

- □ Output over current protection

- □ Thermal shutdown

- ■Small TSSOP16 package (exposed PAD): 5 mm × 6.4 mm

- ■AEC-Q100 compliant (Grade-1)

# **Applications**

- ■Body Control Module (BCM)

- ■Gateway module

- Automotive applications

- ■Industrial applications

# **Block Diagram**

# **Contents**

| Feat | ures                                       | 1  |

|------|--------------------------------------------|----|

| App  | lications                                  | 1  |

| Bloc | k Diagram                                  | 1  |

| 1.   | Product Lineup                             | 3  |

| 2.   | Pin Assignment                             | 4  |

| 3.   | Pin Descriptions                           | 4  |

| 4.   | Architecture Block Diagram                 | 6  |

| 5.   | Absolute Maximum Ratings                   | 7  |

| 6.   | Recommended Operating Conditions           | 7  |

| 7.   | Electrical Characteristics                 | 8  |

| 8.   | Functional Description                     | 9  |

| 8.1  | Protection Function                        | 9  |

| 8.2  | Protection Function Table                  | 10 |

| 9.   | Application Circuit Example and Parts list | 11 |

| 10.  | Application Note                           | 12 |

| 10.1 | Setting the Operation Conditions           | 12 |

| 11.  | Development Support                        | 13 |

| 12.  | Reference Data                             | 14 |

| 13.  | Usage Precaution                           | 16 |

| 14.  | RoHS Compliance Information                | 16 |

| 15.  | Ordering Information                       | 16 |

| 16.  | Package Dimensions                         | 17 |

| 17.  | Major Changes                              | 18 |

| Doc  | ument History                              | 18 |

| Sale | s, Solutions, and Legal Information        | 19 |

# 1. Product Lineup

The VOUT output voltage of this product is set at the factory shipment. To order a product, select an item from the product lineup blow.

|                   | Order V |                            | SYNC    | <b>VOUT UVP T</b> | hreshold [%] | <b>VOUT OVP T</b> |               |                  |

|-------------------|---------|----------------------------|---------|-------------------|--------------|-------------------|---------------|------------------|

| Part Number (MPN) | Code    | VOUT Output<br>Voltage [V] |         | Falling (Typ)     | Rising (Typ) | Rising (Typ)      | Falling (Typ) | Reset<br>Time[s] |

| S6BP201A1AST2B000 | 1A      | 5.000                      |         |                   |              |                   |               |                  |

| S6BP201A2AST2B000 | 2A      | 5.050                      |         |                   |              |                   |               |                  |

| S6BP201A3AST2B000 | 3A      | 5.075                      |         |                   |              |                   |               |                  |

| S6BP201A4AST2B000 | 4A      | 5.100                      | SYNC_IN | 95.5              | 96.5         | 104.5             | 103.5         | 14.0m            |

| S6BP201A5AST2B000 | 5A      | 5.125                      |         |                   |              |                   |               |                  |

| S6BP201A6AST2B000 | 6A      | 5.150                      |         |                   |              |                   |               |                  |

| S6BP201A7AST2B000 | 7A      | 5.200                      |         |                   |              |                   |               |                  |

MPN: Marketing Part Number

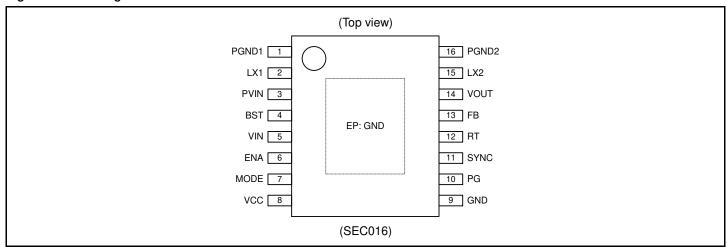

# 2. Pin Assignment

Figure 2-1 Pin Assignment

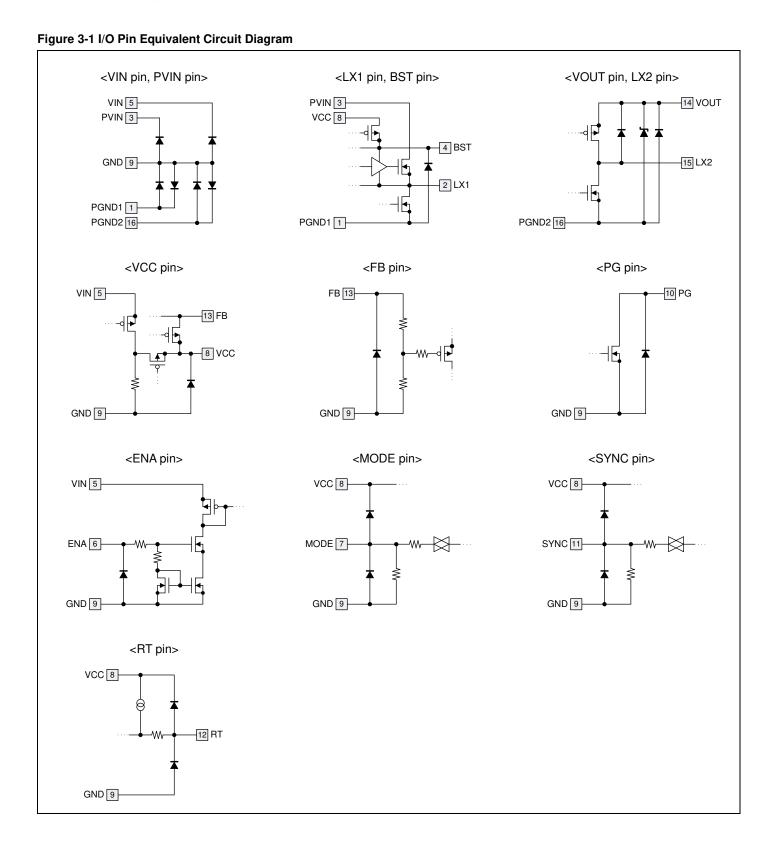

# 3. Pin Descriptions

**Table 3-1 Pin Descriptions**

| Pin No. | Pin Name | I/O | Description                                                                                                                                  |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PGND1    | -   | GND pin for built-in switching FET                                                                                                           |

| 2       | LX1      | 0   | Inductor connection pin                                                                                                                      |

| 3       | PVIN     | I   | Power supply pin for PWM controller and switching FETs                                                                                       |

| 4       | BST      | I   | BST(Boost) capacitor connection pin                                                                                                          |

| 5       | VIN      | I   | Power supply pin                                                                                                                             |

| 6       | ENA      | I   | DC/DC converter enable pin                                                                                                                   |

| 7       | MODE     | I   | PWM/PFM operation control pin For the MODE pin setting, refer to "10.1 Setting the Operation Conditions"                                     |

| 8       | VCC      | 0   | LDO output pin of Internal reference voltage VCC capacitor connection pin                                                                    |

| 9       | GND      | -   | GND pin                                                                                                                                      |

| 10      | PG       | 0   | Open drain output pin for power good. When being used, connect PG pin to VCC pin or VOUT pin. When not being used, leave PG pin open.        |

| 11      | SYNC     | l   | External clock input pin. For the SYNC pin setting, refer to "10.1 Setting the Operation Conditions"                                         |

| 12      | RT       | 0   | Timing resistor connection pin for internal clock (switching frequency) For the resistance, refer to "10.1 Setting the Operation Conditions" |

| 13      | FB       | l   | Output voltage feedback pin                                                                                                                  |

| 14      | VOUT     | 0   | DC/DC converter output pin                                                                                                                   |

| 15      | LX2      | 0   | Inductor connection output pin.                                                                                                              |

| 16      | PGND2    | -   | GND pin for built-in switching FET                                                                                                           |

| EP      | GND      | -   | GND pin                                                                                                                                      |

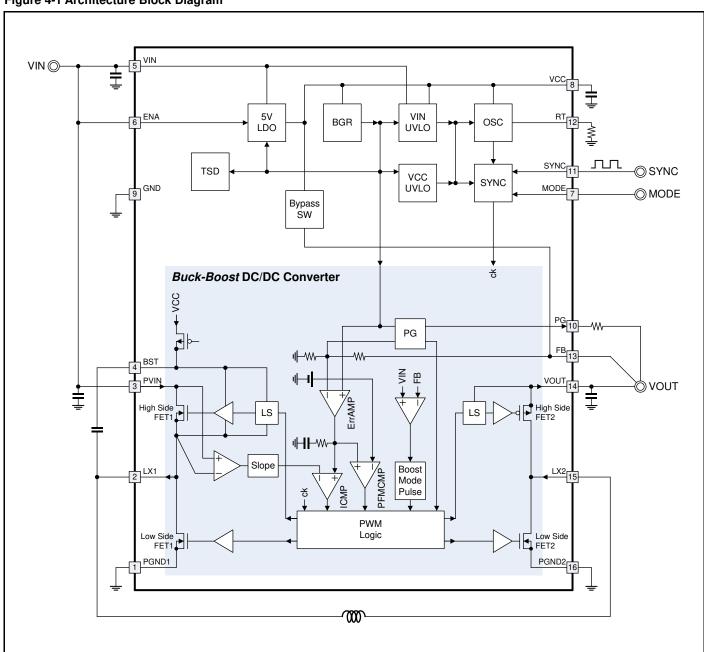

# 4. Architecture Block Diagram

Figure 4-1 Architecture Block Diagram

# 5. Absolute Maximum Ratings

| Parameter                 | Symbol           | Condition                                      | Ra          | ting      | Unit  |

|---------------------------|------------------|------------------------------------------------|-------------|-----------|-------|

| Parameter                 | Syllibol         | Condition                                      | Min         | Max       | Ullit |

|                           | $V_{VIN}$        | VIN pin                                        | -0.3        | +48.0     | V     |

| Power supply voltage (*1) | $V_{PVIN}$       | PVIN pin                                       | -0.3        | +48.0     | V     |

|                           | $V_{VCC}$        | VCC pin                                        | -0.3        | +6.9      | V     |

|                           | $V_{BST}$        | BST pin                                        | -0.3        | +48.0     | V     |

|                           | $V_{LX1}$        | LX1 pin                                        | -2.0        | +48.0     | V     |

|                           | $V_{LX2}$        | LX2 pin                                        | -2.0        | +6.9      | V     |

|                           | $V_{FB}$         | FB pin                                         | -0.3        | $V_{VCC}$ | V     |

| Terminal voltage (*1)     | $V_{RT}$         | RT pin                                         | -0.3        | $V_{VCC}$ | V     |

|                           | $V_{MODE}$       | MODE pin                                       | -0.3        | $V_{VCC}$ | V     |

|                           | $V_{SYNC}$       | SYNC pin                                       | -0.3        | $V_{VCC}$ | V     |

|                           | $V_{ENA}$        | ENA pin                                        | -0.3        | +48.0     | V     |

|                           | $V_{PG}$         | PG pin                                         | -0.3        | +6.9      | V     |

| Difference voltage (*1)   | $V_{BST-LX}$     | Between BST-LX1 pins                           | -0.3        | +6.9      | V     |

| Difference voltage (*1)   | $V_{GND}$        | Between GND-PGND1 pins, Between GND-PGND2 pins | -0.3        | +0.3      | V     |

| PG output current         | I <sub>PG</sub>  | PG pin                                         | -3          | 0         | mA    |

| Power dissipation (*1)    | $P_D$            | Ta ≤ ±25°C                                     | 0           | 3324 (*2) | mW    |

| Storage temperature       | T <sub>STG</sub> | -                                              | <b>-</b> 55 | +150      | °C    |

<sup>\*1:</sup> When PGND1 = PGND2 = GND = 0V

#### Warning:

# 6. Recommended Operating Conditions

| Doromotor                     | Cymbol           | Condition                                           |                             |       | Value<br>Min   Tvp   Max |       |      |  |  |

|-------------------------------|------------------|-----------------------------------------------------|-----------------------------|-------|--------------------------|-------|------|--|--|

| Parameter                     | Parameter Symbol |                                                     | Condition                   |       |                          | Max   | Unit |  |  |

| Dower supply voltage (*1)     | \/               | VINI nin                                            | At start-up                 | 5.0   | 12.0                     | 42.0  | V    |  |  |

| Power supply voltage (*1)     | $V_{VIN}$        | VIN pin                                             | After start-up              | 2.5   | 12.0                     | 42.0  | V    |  |  |

|                               | $V_{BST}$        | BST pin                                             |                             | 0.0   | -                        | 47.5  | V    |  |  |

|                               | $V_{LX1}$        | LX1 pin                                             |                             | -1.0  | +12.0                    | +42.0 | V    |  |  |

|                               | $V_{LX2}$        | LX2 pin                                             |                             | -1.0  | -                        | +5.5  | V    |  |  |

| Terminal voltage (*1)         | $V_{FB}$         | FB pin                                              |                             | 0.0   | -                        | 5.5   | V    |  |  |

| Terminal voltage ( 1)         | $V_{MODE}$       | MODE pin                                            |                             |       | -                        | 5.5   | V    |  |  |

|                               | $V_{SYNC}$       | SYNC pin                                            | 0.0                         | -     | 5.5                      | V     |      |  |  |

|                               | $V_{ENA}$        | ENA pin                                             | ENA pin                     |       |                          | 42.0  | V    |  |  |

|                               | $V_{PG}$         | PG pin                                              | 0.0                         | -     | 5.5                      | V     |      |  |  |

|                               | $V_{BST-LX1}$    | Between BST-                                        | -LX1 pins                   | 0.0   | -                        | 5.5   | V    |  |  |

| Difference voltage (*1)       | $V_{GND}$        |                                                     | PPGND1 pins,<br>PPGND2 pins | -0.05 | 0.00                     | +0.05 | ٧    |  |  |

| PG output current             | $I_{PG}$         | PG pin (sink c                                      | PG pin (sink current) 0 - 1 |       |                          |       | mΑ   |  |  |

| BST capacitance               | C <sub>BST</sub> | Between BST-LX1 pins 0.068 0.100 0                  |                             |       |                          | 0.470 | μF   |  |  |

| VCC capacitance               | C <sub>VCC</sub> |                                                     |                             |       |                          | 10.0  | μF   |  |  |

| Timing resistance             | R <sub>RT</sub>  | Between RT-GND pins. When using internal clock 22 - |                             |       | 270                      | kΩ    |      |  |  |

| Operating ambient Temperature | Ta               |                                                     | 40 +25 +125                 |       |                          |       | °C   |  |  |

<sup>\*1:</sup> When PGND1 = PGND2 = GND = 0V

#### Warning:

- 1. The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated under these conditions.

- 2. Any use of semiconductor devices will be under their recommended operating condition.

- 3. Operation under any conditions other than these conditions may adversely affect reliability of device and could result in device failure.

- 4. No warranty is made with respect to any use, operating conditions or combinations not represented on this data sheet. If you are considering application under any conditions other than listed herein, please contact sales representatives beforehand.

Document Number: 002-08537 Rev. \*B

<sup>\*2:</sup> When the product is mounted on 76.2 mm × 114.3 mm, four-layer FR-4 board

<sup>1.</sup> Semiconductor devices may be permanently damaged by application of stress (including, without limitation, voltage, current or temperature) in excess of absolute maximum ratings. Do not exceed any of these ratings.

# 7. Electrical Characteristics

VIN=PVIN=12V, ENA=5V

(Unless specified otherwise, these are the electrical characteristics under the recommended operating environment.)

|                 | Parameter                           | Symbol                 | Condition                                              |          | Value  |            | Unit |

|-----------------|-------------------------------------|------------------------|--------------------------------------------------------|----------|--------|------------|------|

| raiailletei     |                                     | Зунион                 |                                                        | Min      | Тур    | Max        |      |

|                 |                                     |                        | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.000$ (*1)         | 4.925    | 5.000  | 5.075      | V    |

|                 |                                     |                        | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.050$ (*1)         | 4.975    | 5.050  | 5.125      | V    |

|                 |                                     |                        | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.075$ (*1)         | 4.999    | 5.075  | 5.151      | V    |

|                 | VOUT output voltage                 | $V_{VOUT}$             | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.100$ (*1)         | 5.024    | 5.100  | 5.176      | V    |

|                 |                                     |                        | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.125$ (*1)         | 5.048    | 5.125  | 5.201      | V    |

|                 |                                     |                        | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.150$ (*1)         | 5.073    | 5.150  | 5.227      | V    |

|                 |                                     |                        | $I_{VOUT} = 0A$ , When $V_{VOUT} = 5.200$ (*1)         | 5.122    | 5.200  | 5.278      | V    |

| Buck-boost      | FB input resistance                 | $R_FB$                 | EN = 0V, $Ta = +25$ °C                                 | 3.84     | 4.80   | 5.76       | МΩ   |

| DC/DC           |                                     | R <sub>HSIDEFET1</sub> | LX1 = −30 mA (Between PVIN-LX1)                        | -        | 150    | -          | mΩ   |

| converter       | Switching FET                       | R <sub>LSIDEFET1</sub> | LX1 = 30 mA (Between LX1-PGND1)                        | -        | 150    | -          | mΩ   |

| Block           | on-resistance                       | R <sub>HSIDEFET2</sub> | LX2 = −30 mA (Between VOUT-LX2)                        | -        | 150    | -          | mΩ   |

|                 |                                     | R <sub>LSIDEFET2</sub> | LX2 = 30 mA (Between LX2-PGND2)                        | -        | 150    | -          | mΩ   |

|                 | Switching FET leakage current       | I <sub>LEAK</sub>      | -                                                      | -        | -      | 5          | μΑ   |

|                 | Soft-start time                     | T <sub>SS</sub>        | $R_{RT} = 22 k\Omega$                                  | 0.855    | 0.9    | 0.945      | ms   |

|                 | Maximum output ourront              |                        | PVIN ≥ 7.5V, Ta = 25°C                                 | 1.0 (*2) | -      | _          | Α    |

|                 | Maximum output current              | $I_{VOUT}$             | PVIN = 4.5V, Ta = 25°C                                 | 1.0 (*2) | -      | -          | Α    |

|                 | Current limit                       | I <sub>LIMT</sub>      | PVIN = 12V, L = 2.2μH                                  | 1.0 (*2) | -      | -          | Α    |

| 5V LDO<br>block | VCC output voltage                  | $V_{VCC}$              | VIN = 12V                                              | 4.9      | 5.0    | 5.1        | ٧    |

| VIN UVLO        | VIN UVLO falling threshold          | $V_{UVLOVINHL}$        | VIN input voltage when falling                         | 2.30     | 2.40   | 2.50       | V    |

| block           | VIN UVLO rising threshold           | $V_{UVLOVINLH}$        | VIN input voltage when rising                          | 4.55     | 4.75   | 4.95       | V    |

| VCC UVLO        | VCC UVLO falling threshold          | V <sub>UVLOVCCHL</sub> | VCC input voltage when falling                         | 2.30     | 2.40   | 2.50       | V    |

| block           | VCC UVLO rising threshold           | V <sub>UVLOVCCLH</sub> | VCC input voltage when rising                          | 4.55     | 4.75   | 4.95       | V    |

|                 | Enable condition                    | $V_{ENA}$              | Enable voltage range                                   | 1.10     | -      | $V_{VIN}$  | V    |

| ENA pin         | Enable condition                    | $V_{DSB}$              | Disable voltage range                                  | 0.0      | -      | 0.2        | V    |

|                 | ENA input current                   | I <sub>ENA</sub>       | $V_{ENA} = 12V$                                        | -        | 1      | 3          | μΑ   |

|                 |                                     | $V_{MODE\_L}$          | Automatic PWM/PFM switching                            | 0.0      | -      | 0.4        | V    |

| MODE pin        | MODE input voltage                  |                        | operation                                              |          |        |            | •    |

| MODE pin        |                                     | $V_{MODE\_H}$          | Fixed PWM operation                                    | 2.0      | -      | $V_{VOUT}$ | V    |

|                 | MODE Input current                  | I <sub>MODE</sub>      | MODE = 5.0V                                            | _        | 5      | 10         | μΑ   |

| OSC block       | Switching frequency                 | Fosc                   | $R_{RT} = 22 \text{ k}\Omega$                          | 2.0      | 2.1    | 2.2        | MHz  |

| OCC BIOOK       | ownorming mequency                  |                        | $R_{RT} = 270 \text{ k}\Omega$                         | 180      | 200    | 220        | kHz  |

|                 | SYNC input threshold                | V <sub>SYNC L</sub>    | -                                                      | 0.0      | -      | 0.4        | V    |

| SYNC block      |                                     | $V_{SYNC\;H}$          | -                                                      | 2.0      | -      | $V_{VOUT}$ | V    |

| (SYNC IN)       | SYNC input frequency                | V <sub>SYNC L</sub>    | -                                                      | 200      | _      | 400        | kHz  |

| (3:::3_::1)     | SYNC input duty ratio               | $V_{SYNC\;H}$          | -                                                      | +20      | +50    | +80        | %    |

|                 | SYNC leakage current                | I <sub>LKSYNC</sub>    | $V_{SYNC} = 5.0V$                                      | -        | 5      | 10         | μΑ   |

|                 | VOUT UVP falling threshold          | $P_{GUVPHL}$           | Falling threshold for VOUT output voltage setting (*1) | 94.0     | 95.5   | 97.0       | %    |

|                 | VOUT UVP rising threshold           | $P_{GUVPLH}$           | Rising threshold for VOUT output voltage setting (*1)  | 95.0     | 96.5   | 98.0       | %    |

| PG block        | VOUT OVP rising threshold           | $P_{GOVPLH}$           | Rising threshold for VOUT output voltage setting (*1)  | 103.0    | 104.5  | 106.0      | %    |

| (UVP, OVP)      | VOUT OVP falling threshold          | P <sub>GOVPHL</sub>    | Falling threshold for VOUT output voltage setting (*1) | 102.0    | 103.5  | 105.0      | %    |

|                 | Leak current                        | I <sub>LKPG</sub>      | $V_{PWRGD} = 5.0V, V_{ENA} = 0V$                       | 0        | -      | 1          | μΑ   |

|                 | Low level output voltage            | V <sub>OLPG</sub>      | I <sub>PGSINK</sub> = 1 mA                             | 0.025    | 0.05   | 0.15       | V    |

|                 | Delay time<br>at abnormal detection | T <sub>PPG</sub>       | At power shutdown                                      | -        | 7 (*2) | 12 (*2)    | μs   |

|                 |                                     | T <sub>RPG</sub>       |                                                        | 9.1      |        |            |      |

|                         | Parameter            | Symbol              | Condition                                                                                         |     | Value    |     | Unit  |

|-------------------------|----------------------|---------------------|---------------------------------------------------------------------------------------------------|-----|----------|-----|-------|

|                         | Parameter            | Symbol              |                                                                                                   | Min | Тур      | Max | Ullit |

| Thermal                 |                      | T <sub>TSDH</sub> – |                                                                                                   | ı   | 165 (*2) | -   | °C    |

| shutdown<br>block (TSD) | Shutdown temperature | T <sub>TSDL</sub>   | Hysteresis                                                                                        | ı   | 10 (*2)  | -   | °C    |

|                         | Shutdown current     | I <sub>VINSDN</sub> | VIN input current, V <sub>ENA</sub> = 0V                                                          | -   | 1        | 5   | μΑ    |

| Supply<br>current       | Quiescent current    | I <sub>VINQ</sub>   | VIN input current, V <sub>ENA</sub> = 12V,<br>I <sub>VOUT</sub> = 0A,<br>MODE/SYNC/PG Pins = OPEN | ı   | 20       | 40  | μΑ    |

<sup>\*1:</sup> Refer to "1. Product Lineup"

# 8. Functional Description

#### 8.1 Protection Function

#### Input Under Voltage Lockout (Input UVLO)

The input UVLO is the function that prevents a malfunction of this IC from the following status, and protects poststage devices.

- ☐ Transitional state at start-up

- ☐ Momentary drop of power supply voltage

To prevent such a malfunction, this protection monitors the VIN input voltage and VCC voltage. When either VIN or VCC voltage falls to the UVLO falling threshold, 2.4V (Typ), or lower, the IC stops the VOUT voltage output and becomes UVLO status. When both VIN and VCC voltages reach the UVLO rising threshold, 4.75V (Typ), or higher, the IC is released from the UVLO state and returns to the normal operation.

#### Output Under Voltage Protection (Output UVP)

The output UVP is the function that monitors the voltage drop of the VOUT pin and notifies by the PG pin.

When the output voltage falls to the UVP falling threshold ( $P_{GUVPHL}$ ) for the output voltage setting or lower, the PG voltage is fixed to the low level. The IC becomes the UVP status, but the switching operation is maintained under the UVP status.

When the output voltage once again reaches the UVP rising threshold (P<sub>GUVPLH</sub>) for the output voltage setting or higher, the IC is released from the UVP state and the PG voltage is fixed to the high level.

#### **Output Over Voltage Protection (Output OVP)**

The output OVP is the function that monitors the voltage rise of the VOUT pin and stops the switching operations, which protects poststate devices from overvoltage. Also, the VOUT state is notified by the PG pin.

When the output voltage rises to the OVP falling threshold ( $P_{GOVPLH}$ ) for the output voltage setting or higher, the PG voltage is fixed to the low level. The IC becomes the OVP status, and the switching operations of the high-side FETs are stopped. When the output voltage once again falls to the OVP falling threshold ( $P_{GOVPHL}$ ) for the output voltage setting or lower, the IC is released from the OVP state and resumes the switching operations. The PG voltage is fixed to the high level again.

#### **Output Over Current Protection (Output OCP)**

The output OCP is the function that limits the excessive current load and protects poststage devices.

#### Thermal Shutdown (TSD)

The TSD is the function that protects the IC from heat-destruction. When the junction temperature reaches +165°C (Typ), the high-side and low-side switching FET are turned off and the IC becomes the TSD status. When the junction temperature once again falls to +155°C (Typ) or lower, the IC is released from the TSD state and restarts the power supply.

<sup>\*2:</sup> The electrical characteristic is ensured by statistical characterization and indirect tests.

## 8.2 Protection Function Table

The following table shows the state of each pin when each protection function operates.

**Table 8-1 Protection Function Table**

| Function                                     | ENA Pin<br>Setting | PG Pin<br>Output | DC/DC<br>Converter<br>Operation | Remarks                                                                                                                                                                                             |

|----------------------------------------------|--------------------|------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shutdown operation                           | L                  | Hi-Z (*1)        | Shutdown                        | It is recommended to connect PG pin to VCC pin or VOUT pin via a pull-up resistor. When setting ENA pin to a low level, both VCC pin and VOUT pin voltage drop to 0V. Therefore, PG pin outputs 0V. |

| Nominal operation                            | Н                  | Hi-Z (*1)        | Switching                       | -                                                                                                                                                                                                   |

| Input under voltage protection (Input UVLO)  | Н                  | L                | Shutdown                        | After releasing UVLO state, this IC is automatically reset with soft start.                                                                                                                         |

| Output under voltage protection (Output UVP) | Н                  | L                | Switching                       | -                                                                                                                                                                                                   |

| Output over voltage protection (Output OVP)  | Н                  | L                | Shutdown                        | -                                                                                                                                                                                                   |

| Output over current protection (Output OCP)  | Н                  | L                | Switching                       | OCP operates to drop the output voltage.                                                                                                                                                            |

| Thermal shutdown (TSD)                       | Н                  | L                | Shutdown                        | After releasing TSD state, this IC is automatically reset with soft start.                                                                                                                          |

<sup>\*1:</sup> PG pin is formed as an open drain structure. The internal MOSFET is in the OFF state.

# 9. Application Circuit Example and Parts list

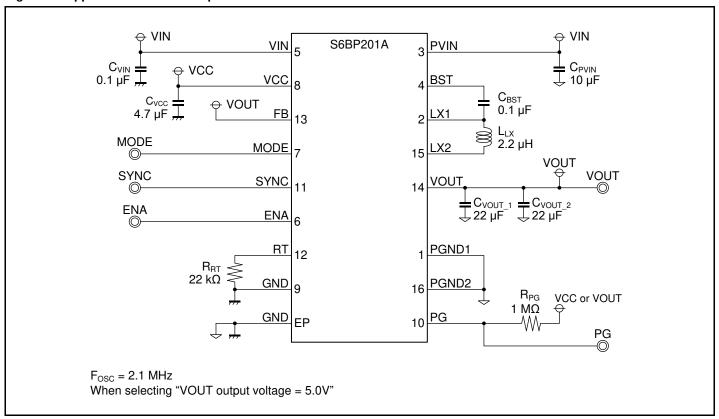

# Figure 9-1 Application Circuit Example

**Table 9-1 Parts List**

| Symbol                                       | Item              | Value  | Part Number          | Vendor | Package Size<br>(W×L×H[mm]) | Remarks                                  |

|----------------------------------------------|-------------------|--------|----------------------|--------|-----------------------------|------------------------------------------|

| C <sub>VIN</sub> ,<br>C <sub>BST</sub>       | Ceramic capacitor | 0.1 μF | CGA2B3X7R1H104K050BB | TDK    | 1.0×0.5×0.5                 | X7R, Rated Voltage: 50 Vdc               |

| C <sub>PVIN</sub>                            | Ceramic capacitor | 10 μF  | CGA9N3X7R1H106K230KB | TDK    | 5.7×5.0×2.3                 | X7R, Rated Voltage: 50 Vdc               |

| C <sub>VCC</sub>                             | Ceramic capacitor | 4.7 µF | CGA4J3X7R1C475K125AB | TDK    | 2.0×1.25×1.25               | X7R, Rated Voltage: 16 Vdc               |

| C <sub>VOUT_1</sub> ,<br>C <sub>VOUT_2</sub> | Ceramic capacitor | 22 µF  | CGA6P1X7R1C226M250AC | TDK    | 3.2×2.5×2.5                 | X7R, Rated Voltage: 16 Vdc               |

| L <sub>LX</sub>                              | Inductor          | 2.2 µH | CLF7045T-2R2N-D      | TDK    | 7.2×6.9×4.5                 | DCR: 14.6 mΩ, I <sub>DC_MAX</sub> : 5.5A |

| R <sub>RT</sub>                              | Resistor          | 22 kΩ  | RK73H1JTTD2202F      | KOA    | 0.8×1.6×0.45                | -                                        |

| R <sub>PG</sub>                              | Resistor          | 1 ΜΩ   | RK73H1JTTD1004F      | KOA    | 0.8×1.6×0.45                | -                                        |

TDK: TDK Corporation KOA: KOA Corporation

# 10. Application Note

#### 10.1 Setting the Operation Conditions

## Operation State of DC/DC Convertor

The operation stage of DC/CD converter is set by both MODE pin and SYNC pin.

Table 10-1 Operation State of DC/DC Convertor

| <b>MODE Pin</b>                                                                                            | SYNC Pin (Signal Input)                                      | Operation State of DC/DC Convertor                                        |  |  |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

|                                                                                                            | Automatic PWM/PFM switching operation from an internal clock |                                                                           |  |  |

| L (*3) External clock input (*5) Fixed PWM operation with synchronizing signal from an external clock (*2) |                                                              |                                                                           |  |  |

|                                                                                                            | H (*4)                                                       | Prohibition of use (*1)                                                   |  |  |

|                                                                                                            | L (*3)                                                       | Fixed PWM operation from an internal clock                                |  |  |

| H (*4)                                                                                                     | External clock input (*5)                                    | Fixed PWM operation with synchronizing signal from an external clock (*2) |  |  |

|                                                                                                            | H (*4)                                                       | Prohibition of use (*1)                                                   |  |  |

<sup>\*1:</sup> When setting SYNC pin to a high level, the quiescent current (IVINQ) is increased.

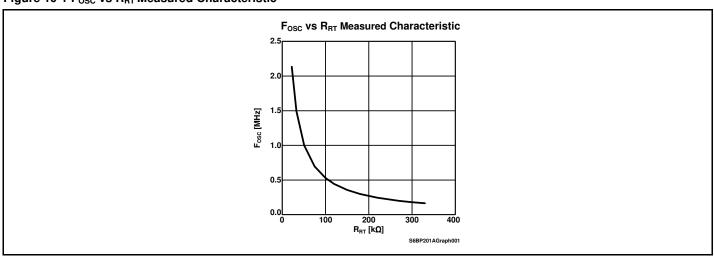

## **Setting of Switching Frequency (Internal Clock)**

The switching frequency (internal clock) can be set by RT resistor, which value is the timing resistance ( $R_{RT}$ ), connected to RT pin. Set the timing resistance in a range within the following graph.

Figure 10-1 F<sub>OSC</sub> vs R<sub>RT</sub> Measured Characteristic

The reference value can be calculated by the following formula.

$$F_{OSC} \left[ Hz \right] \approx \frac{1}{R_{RT} \times 21.7 \times 10^{-12}} \label{eq:Fosc}$$

$F_{OSC}$  : Switching frequency [Hz]  $R_{RT}$  : Timing resistance [ $\Omega$ ]

<sup>\*2:</sup> Set the timing resistance ( $R_{RT}$ ) to 330 k $\Omega$ .

<sup>\*3:</sup> Apply the GND1 or GND2 voltage.

<sup>\*4:</sup> Apply the VOUT voltage.

<sup>\*5:</sup> Apply the VOUT voltage at a high level. Apply the GND1 or GND2 voltage at a low level

#### **Setting of Soft-start Time**

The Soft-start time is determined by the timing resistance (RRT), the value of the resistor connected to RT pin.

$$T_{SS}[s] = \frac{1}{F_{OSC}} \times 2 \times 1024$$

T<sub>SS</sub> : Soft-start time [s]

Fosc : Switching frequency [Hz]

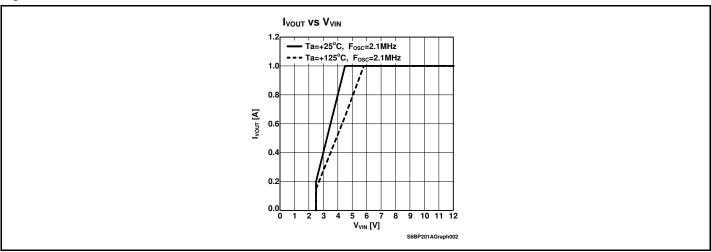

# **Consideration of VOUT Maximum Output Current**

Make sure the VOUT maximum output current in a range within the following graph.

#### Figure 10-2 $I_{VOUT}$ vs $V_{VIN}$

# 11. Development Support

The IC has a set of documentation, such as application notes, development tools, and online resources to assist you during your development process. Visit <a href="https://www.cypress.com/automotive-pmic">www.cypress.com/automotive-pmic</a> to find out more.

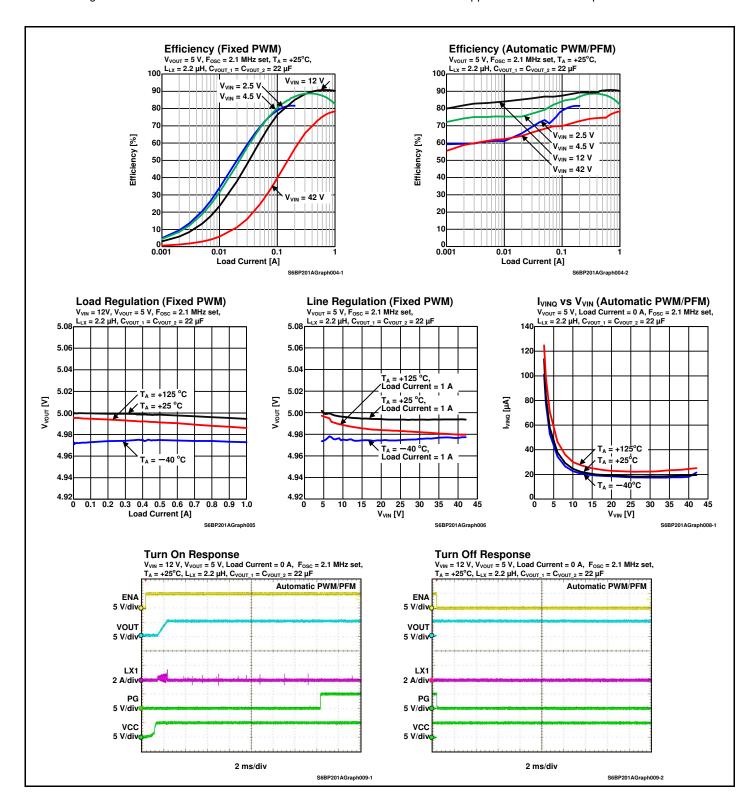

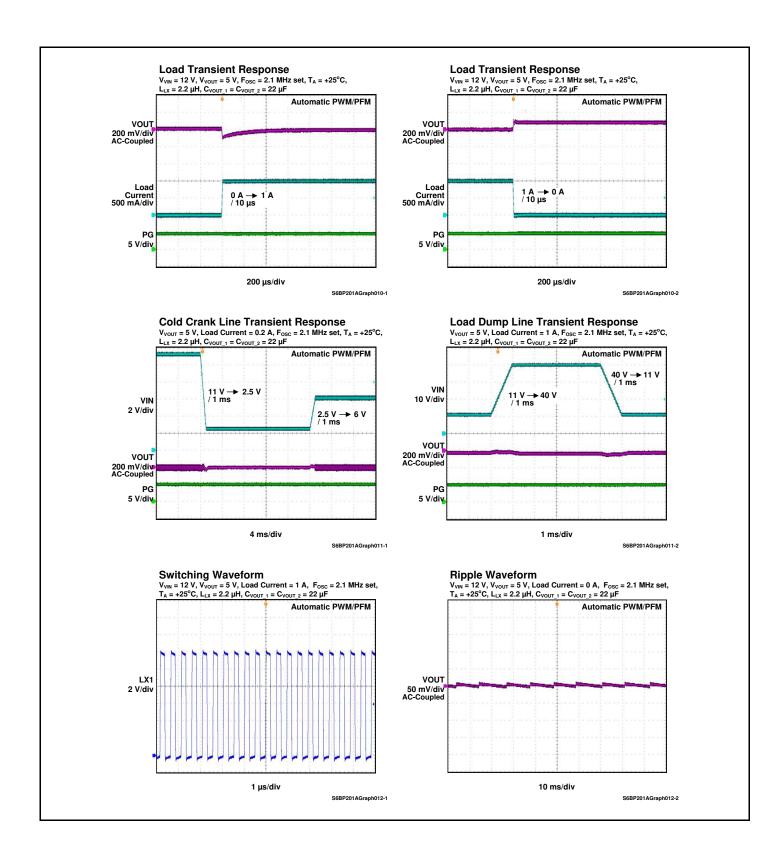

#### 12. Reference Data

The followings are the reference data measured under the conditions shown in "9. Application Circuit Example and Parts list".

# 13. Usage Precaution

Printed circuit board ground lines should be set up with consideration for common impedance.

#### Take appropriate measures against static electricity.

- □ Containers for semiconductor materials should have anti-static protection or be made of conductive material.

- □ After mounting, printed circuit boards should be stored and shipped in conductive bags or containers.

- □ Work platforms, tools, and instruments should be properly grounded.

- $\square$  Working personnel should be grounded with resistance of 250 k $\Omega$  to 1 M $\Omega$  in serial body and ground.

#### Do not apply negative voltages.

The use of negative voltages below -0.3V may make the parasitic transistor activated to the LSI, and can cause malfunctions.

## 14. RoHS Compliance Information

This product has observed the standard of lead, cadmium, mercury, Hexavalent chromium, polybrominated biphenyls (PBB), and polybrominated diphenyl ethers (PBDE).

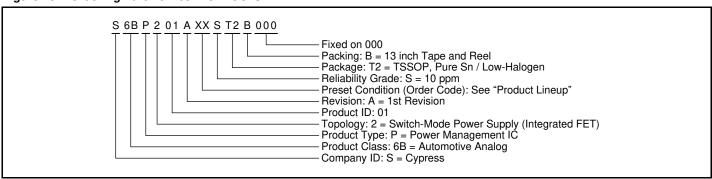

## 15. Ordering Information

**Table 15-1 Ordering Information**

| Order Code | Part Number (MPN) (*1) | Package                                             |  |  |  |  |

|------------|------------------------|-----------------------------------------------------|--|--|--|--|

| 1A         | S6BP201A1AST2B000      | Digetic TCCOD16 (0.65 mm nitch), 16 nin             |  |  |  |  |

| 4A         | S6BP201A4AST2B000      | Plastic TSSOP16 (0.65 mm pitch), 16-pin<br>(SEC016) |  |  |  |  |

| 7A         | S6BP201A7AST2B000      | (SLO010)                                            |  |  |  |  |

MPN: Marketing Part Number

Figure 15-1 Ordering Part Number Definitions

<sup>\*1:</sup> Please contact our sales division for the part numbers (refer to "1. Product Lineup") not mentioned in this table.

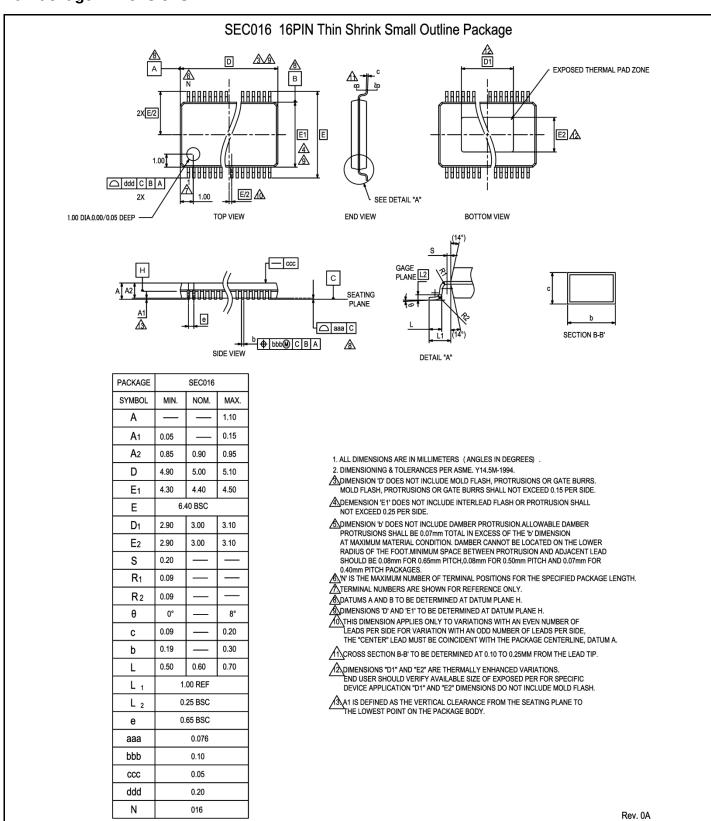

# 16. Package Dimensions

# 17. Major Changes

Spansion Publication Number: S6BP201A DS405-00032

| Page        | Section                           | Change Results                                                       |  |  |  |  |  |

|-------------|-----------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Preliminary | 0.1                               |                                                                      |  |  |  |  |  |

| -           | -                                 | Initial release                                                      |  |  |  |  |  |

| Preliminary | Preliminary 0.2                   |                                                                      |  |  |  |  |  |

| 12          | 10. Electrical<br>Characteristics | "(TSD)" was added in the table of "10. Electrical Characteristics ". |  |  |  |  |  |

NOTE: Please see "Document History" about later revised information.

# **Document History**

Document Title: S6BP201A, ASSP, 42V, 1A, Synchronous Buck-boost DC/DC Converter IC

Document Number: 002-08537

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | -       | HIXT               | 09/04/2015         | New Spec.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *A       | 5056149 | HIXT               | 12/18/2015         | Added Block Diagram Added Figure 15-1 Updated 16. Package Dimensions                                                                                                                                                                                                                                                                                                                                                                              |

| *B       | 5164343 | HIXT               | 03/08/2016         | Added "AEC-Q100 compliant (Grade-1)" in Features Added Figure 3-1 I/O Pin Equivalent Circuit Diagram The followings in 7. Electrical Characteristics were updated. The parameter name of I <sub>VOUT</sub> was changed from "VOUT output voltage" to "Maximum output current" The max values of I <sub>VOUT</sub> were moved to the min column. Added 11. Development Support Added 12. Reference Data Deleted the ES part number from Table 15-1 |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Lighting & Power Control cypress.com/powerpsoc

Memory cypress.com/memory

PSoC cypress.com/psoc

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless/RF cypress.com/wireless

#### **PSoC® Solutions**

cypress.com/psoc

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

#### **Technical Support**

cypress.com/support

ARM and Cortex are the registered trademarks of ARM Limited in the EU and other countries

© Cypress Semiconductor Corporation 2015-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-08537 Rev. \*B March 8, 2016 Page 19 of 19