# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Freescale Semiconductor**

Data Sheet: Technical Data

#### Document Number: MC9S08MP16 Rev. 2, 08/2011

# MC9S08MP16 Series Data Sheet

Features

- 8-Bit HCS08 Central Processor Unit (CPU)

- Up to 51.34 MHz CPU at 2.7V to 5.5V across temperature range of -40°C to 105°C

- Up to 40 MHz CPU at 2.7V to 5.5V across temperature range of -40°C to 125°C

- HC08 instruction set with added BGND instruction and additional addressing modes for LDHX and STHX

Support for up to 48 interrupt/reset sources

- On-Chip Memory

- Up to 16 KB flash memory; read/program/erase over full operating voltage and temperature

- Up to 1 KB random-access memory (RAM)

- Security circuitry to prevent unauthorized access to RAM and flash memory contents

- Power-Saving Modes

- Two low power stop modes; reduced power wait mode

- Peripheral clock gating can disable clocks to unused modulesClock Source Options

- Oscillator (XOSC) Loop-control Pierce oscillator; Crystal or ceramic resonator range of 31.25–38.4 kHz or 1–16 MHz

- Internal Clock Source (ICS) Containing a frequency-locked-loop (FLL) controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolutions and 2% deviation over temperature and voltage; supports CPU frequencies up to 51.34 MHz

- System Protection

- Watchdog computer operating properly (COP) reset running from dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- Illegal opcode and illegal address detection with reset

- Flash memory block protection

- Development Support

- Single-wire background debug interface

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus three more breakpoints in on-chip debug module)

- On-chip in-circuit emulator (ICE) debug module containing three comparators and nine trigger modes. Eight deep FIFO for storing change-of-flow addresses and event-only data. Debug module supports both tag and force breakpoints

- Peripherals

- IPC Interrupt Priority Controller with 4 programmable interrupt priority levels

- ADC 13-channel, 12-bit resolution; 2.5 µs conversion time; automatic compare function; 1.7 mV/°C temperature sensor; internal bandgap reference channel; operation in stop3

48-LQFP Case 932-03 28-SOIC

32-LQFP Case 873A-03

PGA — Differential programmable gain amplifier with programmable gain (x1, x2, x4, x8, x16, or x32)

Case 751F-05

- HSCMP Three fast analog comparators with positive and negative inputs; separately selectable interrupt on rising and falling comparator output; filtering; windowing; HSCMP1 and HSCMP2 outputs can be optionally routed to FTM1 module; runs in stop3

- DAC Three 5-bit digital to analog convertor used as a 32-tap voltage reference for each comparator

- PDB Two programmable delay blocks: PDB1 synchronizes PWM with samples of ADC; PDB2 synchronizes PWM with comparing window of analog comparators

- SCI Full duplex non-return to zero (NRZ); LIN master extended break generation; LIN slave extended break detection; wake up on active edge

- SPI Full-duplex or single-wire bidirectional; Double-buffered transmit and receive; Master or Slave mode; MSB-first or LSB-first shifting

- IIC/SMBus Up to 400 kbps; Multi-master operation; Programmable slave address; Interrupt driven byte-by-byte data transfer; supports broadcast mode and 10-bit addressing; SMBus compatible

- FTM Two Flextimers with total of 8 channels; One

2-channel (FTM1) and one 6-channel (FTM2); supports

operation up to 2x bus clock; selectable input capture, output

compare, edge- or center-aligned PWM; dead time insertion;

fault inputs

- MTIM 8-bit modulo counter with 8-bit prescaler

- RTC (Real-time counter) 8-bit modulus counter with binary or decimal based prescaler; External clock source for precise time base, time-of-day, calendar or task scheduling; Free running on-chip low power oscillator (1 kHz) for cyclic wake-up without external components, runs in all MCU modes

- CRC Cyclic redundancy check generator

- KBI Three 8 channel keyboard interrupt module with software selectable polarity on edge or edge/level modes

- Input/Output

- 40 GPIOs, 2 output-only pins.

- Hysteresis and configurable pull up device on input pins; Configurable slew rate and drive strength on output pins; Sink/Source current up to 20mA

- Package Options

- 48-LQFP, 32-LQFP, 28-SOIC

- 48-LQFP qualified for automotive usage

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

© Freescale Semiconductor, Inc., 2009-2011. All rights reserved.

## **Table of Contents**

| Pin A | ssignments4                                                                          |

|-------|--------------------------------------------------------------------------------------|

| Elect | rical Characteristics                                                                |

| 2.1   | Introduction                                                                         |

| 2.2   | Parameter Classification                                                             |

| 2.3   | Absolute Maximum Ratings                                                             |

| 2.4   | Thermal Characteristics10                                                            |

| 2.5   | ESD Protection and Latch-Up Immunity11                                               |

| 2.6   | DC Characteristics11                                                                 |

| 2.7   | Supply Current Characteristics                                                       |

| 2.8   | External Oscillator (XOSC) Characteristics                                           |

| 2.9   | Internal Clock Source (ICS) Characteristics                                          |

| 2.10  | ADC Characteristics                                                                  |

| 2.11  | Digital to Analog (DAC) Characteristics                                              |

| 2.12  | High Speed Comparator (HSCMP) Characteristics26                                      |

|       | Elect<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11 |

|   | 2.13 Programmable Gain Amplifier (PGA) Characteristics . 26 |

|---|-------------------------------------------------------------|

|   | 2.14 AC Characteristics                                     |

|   | 2.14.1 Control Timing 27                                    |

|   | 2.14.2 FTM Module Timing                                    |

|   | 2.14.3 MTIM Module Timing 29                                |

|   | 2.14.4 SPI                                                  |

|   | 2.15 Flash Memory Specifications                            |

|   | 2.16 EMC Performance                                        |

|   | 2.16.1 Radiated Emissions                                   |

| 3 | Ordering Information                                        |

|   | 3.1 Device Numbering Scheme 35                              |

| 4 | Package Information                                         |

| 5 | Related Documentation                                       |

| 6 | Revision History 35                                         |

Notes: When PTF1 is configured as RESET, pin becomes bi-directional with output being open-drain drive containing an internal pull-up device. When PTF0 is configured as BKGD, pin becomes bi-directional.

V<sub>DD2</sub> pad is tied internally on 32-pin and 28-pin packages,

V<sub>SS2</sub> pad is tied internally on 28-pin packages

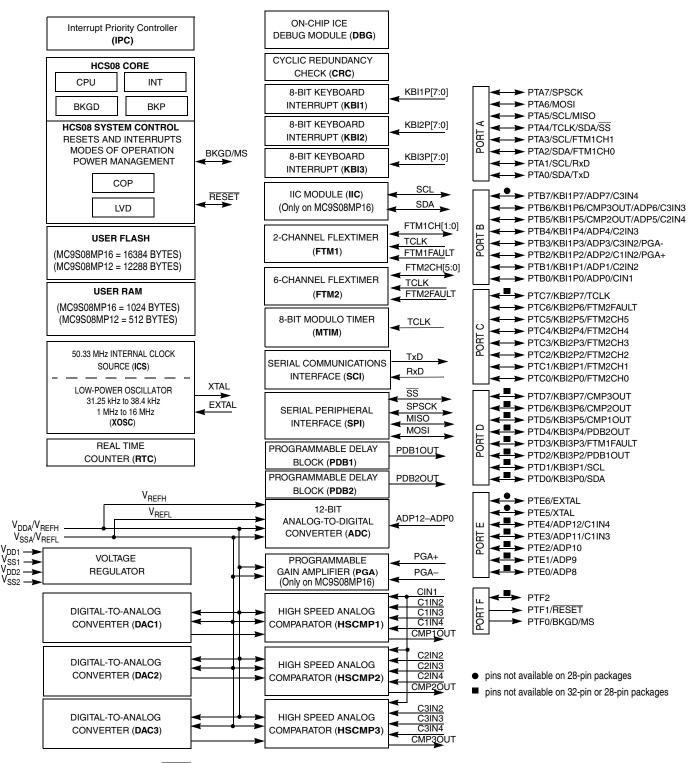

Figure 1. MC9S08MP16 Series Block Diagram

**Pin Assignments**

## 1 Pin Assignments

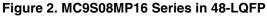

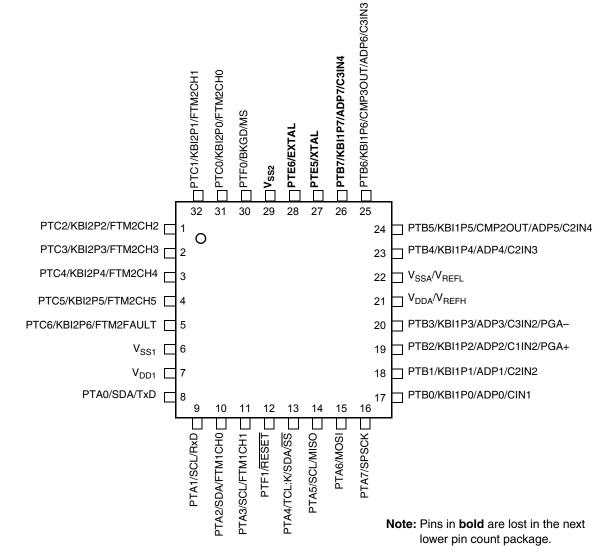

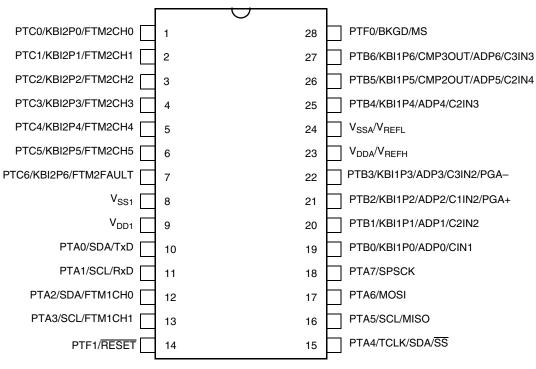

This section shows the pin assignments for the MC9S08MP16 Series devices.

#### **Pin Assignments**

Figure 3. MC9S08MP16 Series in 32-Pin LQFP Package

#### **Pin Assignments**

Figure 4. MC9S08MP16 Series in 28-Pin SOIC Package

**Pin Assignments**

|    | Pin Numbe  | er |          | < Lowes            | t <b>Priority</b>    | > Highest          |                                     |

|----|------------|----|----------|--------------------|----------------------|--------------------|-------------------------------------|

| 48 | 32<br>LQFP | 28 | Port Pin | Alt 1              | Alt 2                | Alt3               | Alt4                                |

| 1  | 3          | 5  | PTC4     | KBI2P4             | FTM2CH4              |                    |                                     |

| 2  | 4          | 6  | PTC5     | KBI2P5             | FTM2CH5              |                    |                                     |

| 3  | 5          | 7  | PTC6     | KBI2P6             | FTM2FAULT            |                    |                                     |

| 4  | —          | _  | PTC7     | KBI2P7             | TCLK <sup>1</sup>    |                    |                                     |

| 5  | —          | _  | PTD0     | KBI3P0             | SDA <sup>5</sup>     |                    |                                     |

| 6  |            | _  | PTD1     | KBI3P1             | SCL <sup>5</sup>     |                    |                                     |

| 7  | _          | _  | PTD2     | KBI3P2             | PDB1OUT              |                    |                                     |

| 8  | _          |    | PTD3     | KBI3P3             | FTM1FAULT            |                    |                                     |

| 9  | 6          | 8  |          |                    |                      |                    | V <sub>SS1</sub>                    |

| 10 | 7          | 9  |          |                    |                      |                    | V <sub>DD1</sub>                    |

| 11 | 8          | 10 | PTA0     | SDA <sup>5</sup>   | TxD                  |                    |                                     |

| 12 | 9          | 11 | PTA1     | SCL <sup>5</sup>   | RxD                  |                    |                                     |

| 13 | 10         | 12 | PTA2     | SDA <sup>5</sup>   | FTM1CH0              |                    |                                     |

| 14 | 11         | 13 | PTA3     | SCL <sup>5</sup>   | FTM1CH1              |                    |                                     |

| 15 |            | _  | PTD4     | KBI3P4             | PDB2OUT              |                    |                                     |

| 16 | _          |    | PTD5     | KBI3P5             | CMP1OUT              |                    |                                     |

| 17 | _          |    | PTD6     | KBI3P6             | CMP2OUT <sup>2</sup> |                    |                                     |

| 18 |            | _  | PTD7     | KBI3P7             | CMP3OUT <sup>3</sup> |                    |                                     |

| 19 | 12         | 14 | PTF1     | RESET <sup>4</sup> |                      |                    |                                     |

| 20 | _          |    | PTF2     |                    |                      |                    |                                     |

| 21 | 13         | 15 | PTA4     | TCLK <sup>1</sup>  | SDA <sup>5</sup>     | SS                 |                                     |

| 22 | 14         | 16 | PTA5     |                    | SCL <sup>5</sup>     | MISO               |                                     |

| 23 | 15         | 17 | PTA6     |                    |                      | MOSI               |                                     |

| 24 | 16         | 18 | PTA7     |                    |                      | SPSCK              |                                     |

| 25 | _          |    | PTE0     |                    | ADP8                 |                    |                                     |

| 26 |            |    | PTE1     |                    | ADP9                 |                    |                                     |

| 27 |            |    | PTE2     |                    | ADP10                |                    |                                     |

| 28 | 17         | 19 | PTB0     | KBI1P0             | ADP0 <sup>6</sup>    | CIN1 <sup>6</sup>  |                                     |

| 29 | 18         | 20 | PTB1     | KBI1P1             | ADP1 <sup>6</sup>    | C2IN2 <sup>6</sup> |                                     |

| 30 | 19         | 20 | PTB2     | KBI1P2             | ADP2 <sup>6</sup>    | C1IN2 <sup>6</sup> | PGA+ <sup>6</sup>                   |

| 31 | 20         | 22 | PTB3     | KBI1P3             | ADP3 <sup>6</sup>    | C3IN2 <sup>6</sup> | PGA- <sup>6</sup>                   |

| 32 | 21         | 23 |          |                    |                      |                    | V <sub>DDA</sub> /V <sub>REFF</sub> |

| 33 | 22         | 24 |          |                    |                      |                    | V <sub>SSA</sub> /V <sub>REFL</sub> |

| 34 |            |    | PTE3     |                    | ADP11 <sup>6</sup>   | C1IN3 <sup>6</sup> | · 33A · NEFL                        |

| I  | Pin Numbe  | r  |          | < Lowes | st <b>Priority</b>   | > Highest          | :                  |

|----|------------|----|----------|---------|----------------------|--------------------|--------------------|

| 48 | 32<br>LQFP | 28 | Port Pin | Alt 1   | Alt 2                | Alt3               | Alt4               |

| 35 | _          | _  | PTE4     |         | ADP12 <sup>6</sup>   | C1IN4 <sup>6</sup> |                    |

| 36 | 23         | 25 | PTB4     | KBI1P4  |                      | ADP4 <sup>6</sup>  | C2IN3 <sup>6</sup> |

| 37 | 24         | 26 | PTB5     | KBI1P5  | CMP2OUT <sup>2</sup> | ADP5 <sup>6</sup>  | C2IN4 <sup>6</sup> |

| 38 | 25         | 27 | PTB6     | KBI1P6  | CMP3OUT <sup>3</sup> | ADP6 <sup>6</sup>  | C3IN3 <sup>6</sup> |

| 39 | 26         | _  | PTB7     | KBI1P7  |                      | ADP7 <sup>6</sup>  | C3IN4 <sup>6</sup> |

| 40 | 27         | _  | PTE5     | XTAL    |                      |                    |                    |

| 41 | 28         | _  | PTE6     | EXTAL   |                      |                    |                    |

| 42 | 29         |    |          |         |                      |                    | V <sub>SS2</sub>   |

| 43 | —          |    |          |         |                      |                    | V <sub>DD2</sub>   |

| 44 | 30         | 28 | PTF0     | BKGD    | MS                   |                    |                    |

| 45 | 31         | 1  | PTC0     | KBI2P0  | FTM2CH0              |                    |                    |

| 46 | 32         | 2  | PTC1     | KBI2P1  | FTM2CH1              | 1                  |                    |

| 47 | 1          | 3  | PTC2     | KBI2P2  | FTM2CH2              |                    |                    |

| 48 | 2          | 4  | PTC3     | KBI2P3  | FTM2CH3              |                    |                    |

Table 1. Pin Availability by Package Pin-Count (continued)

<sup>1</sup> TCLK pin can be repositioned using TCLKPS in SOPT2. Default reset location is PTC7.

<sup>2</sup> HSCMP2 output CMP2OUT can be repositioned using the CMP2OPS in the SOPT2 register. Default reset location is PTD6.

<sup>3</sup> HSCMP3 output CMP3OUT can be repositioned using the CMP3OPS in the SOPT2 register. Default reset location is PTD7.

<sup>4</sup> Pin is open drain with an internal pullup that is always enabled. Pin does not contain a clamp diode to  $V_{DD}$  and should not be driven above  $V_{DD}$ . The voltage measured on the internally pulled up RESET will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ .

- <sup>5</sup> IIC pins SDA and SCL can be repositioned using IICPS in SOPT2. Default reset locations are PTD0 and PTD1.

- <sup>6</sup> If ADC, HSCMP, or PGA is enabling a shared analog input pin, each has access to the pin.

## 2 Electrical Characteristics

### 2.1 Introduction

This section contains electrical and timing specifications for the MC9S08MP16 Series of microcontrollers available at the time of publication.

## 2.2 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

| Table 2. | Parameter | Classifications |

|----------|-----------|-----------------|

|----------|-----------|-----------------|

| Р | Those parameters that are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| С | Those parameters that are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters that are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters that are derived mainly from simulations.                                                                                                                                                                  |

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

## 2.3 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 3 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

| Rating                                                                                          | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +5.8                  | V    |

| Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                           | V <sub>In</sub>  | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | Ι <sub>D</sub>   | ± 25                          | mA   |

| Storage temperature range                                                                       | T <sub>stg</sub> | –55 to 150                    | °C   |

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

<sup>2</sup> All functional non-supply pins, except for PTF1/RESET are internally clamped to V<sub>SS</sub> and V<sub>DD</sub>.

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

## 2.4 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and voltage regulator circuits, and it is user-determined rather than being controlled by the MCU design. To take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| Num | С | Rating                                                | Symbol         | Consumer &<br>Industrial | Automotive | Unit |

|-----|---|-------------------------------------------------------|----------------|--------------------------|------------|------|

| 1   | _ | Operating temperature range (packaged)                | Τ <sub>Α</sub> | -40 to 105               | -40 to 125 | °C   |

| 2   | D | Maximum junction temperature                          | Т <sub>Ј</sub> | 115                      | 135        | °C   |

| 3   | D | Thermal resistance <sup>1,2</sup> single-layer board  |                |                          |            |      |

|     |   | 48-pin LQFP                                           |                | 80                       | 80         |      |

|     |   | 32-pin LQFP                                           | $\theta_{JA}$  | 85                       | _          | °C/W |

|     |   | 28-pin SOIC                                           |                | 71                       | _          |      |

| 4   | D | Thermal resistance <sup>1,2</sup><br>four-layer board |                |                          |            |      |

|     |   | 48-pin LQFP                                           |                | 56                       | 56         |      |

|     |   | 32-pin LQFP                                           | $\theta_{JA}$  | 57                       | _          | °C/W |

|     |   | 28-pin SOIC                                           |                | 48                       |            |      |

| Table 4. Thermal | Characteristics |

|------------------|-----------------|

|------------------|-----------------|

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Junction-to-ambient natural convection

The average chip-junction temperature  $(T_I)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A$  = Ambient temperature, °C  $\theta_{JA}$  = Package thermal resistance, junction-to-ambient, °C/W  $P_D = P_{int} + P_{I/O}$   $P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power  $P_{I/O}$  = Power dissipation on input and output pins — user determined

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$\mathbf{K} = \mathbf{P}_{\mathbf{D}} \times (\mathbf{T}_{\mathbf{A}} + 273^{\circ}\mathbf{C}) + \theta_{\mathbf{J}\mathbf{A}} \times (\mathbf{P}_{\mathbf{D}})^{2} \qquad \qquad Eqn. 3$$

where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

## 2.5 ESD Protection and Latch-Up Immunity

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, normal handling precautions should be taken to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits. During the device qualification, ESD stresses were performed for the human body model (HBM) and the charge device model (CDM).

A device is defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless instructed otherwise in the device specification.

| Model    | Description                 | Symbol | Value | Unit |

|----------|-----------------------------|--------|-------|------|

| Human    | Series resistance           | R1     | 1500  | Ω    |

| Body     | Storage capacitance         | С      | 100   | pF   |

|          | Number of pulses per pin    | —      | 3     |      |

| Latch-up | Minimum input voltage limit |        | - 2.5 | V    |

|          | Maximum input voltage limit |        | 7.5   | V    |

Table 5. ESD and Latch-up Test Conditions

#### Table 6. ESD and Latch-Up Protection Characteristics

| No. | Rating <sup>1</sup>                      | Symbol           | Min       | Max | Unit |

|-----|------------------------------------------|------------------|-----------|-----|------|

| 1   | Human body model (HBM)                   | V <sub>HBM</sub> | $\pm2000$ | —   | V    |

| 2   | Charge device model (CDM)                | V <sub>CDM</sub> | $\pm500$  | _   | ۷    |

| 3   | Latch-up current at $T_A = 125^{\circ}C$ | I <sub>LAT</sub> | ± 100     |     | mA   |

Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

## 2.6 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

#### Table 7. DC Characteristics

| Num | С | Characteristic                                                   | Symbol           | Condition | Min | Typ <sup>1</sup> | Max  | Unit |

|-----|---|------------------------------------------------------------------|------------------|-----------|-----|------------------|------|------|

| 1   | — | Operating Voltage                                                | V <sub>DD</sub>  |           | 2.7 | —                | 5.5  | V    |

| 2   | — | Analog Supply voltage delta to $V_{DD} (V_{DD} - V_{DDA})^{(2)}$ | $\Delta V_{DDA}$ |           | _   | 0                | ±100 | mV   |

| 3   | — | Analog Ground voltage delta to $V_{SS} (V_{SS} - V_{SSA})^{(2)}$ | $\Delta V_{SSA}$ |           |     | 0                | ±100 | mV   |

| Num | С | Charao                                   | cteristic                               | Symbol           | Condition                            | Min                   | Typ <sup>1</sup> | Max                  | Unit |

|-----|---|------------------------------------------|-----------------------------------------|------------------|--------------------------------------|-----------------------|------------------|----------------------|------|

|     | С | Ali I/O                                  | pins (except PTF1/RESET)                |                  | 5 V, I <sub>Load</sub> = -4 mA       | V <sub>DD</sub> – 1.5 | —                | —                    |      |

|     | Ρ |                                          | low-drive strength                      |                  | 5 V, $I_{Load} = -2 \text{ mA}$      | V <sub>DD</sub> – 0.8 | —                | —                    |      |

| 4   | С | Output high                              |                                         | V <sub>OH</sub>  | 3 V, $I_{Load} = -1 \text{ mA}$      | V <sub>DD</sub> – 0.8 | _                | —                    | V    |

| 4   | С | voltage                                  |                                         |                  | 5 V, I <sub>Load</sub> = -20 mA      | V <sub>DD</sub> – 1.5 | —                | —                    |      |

|     | Ρ |                                          | high-drive strength                     |                  | 5 V, $I_{Load} = -10 \text{ mA}$     | V <sub>DD</sub> – 0.8 | —                | —                    |      |

|     | С |                                          |                                         |                  | 3 V, I <sub>Load</sub> = -5 mA       | V <sub>DD</sub> – 0.8 | —                | —                    |      |

| 5   | D | Output high current                      | Max total I <sub>OH</sub> for all ports | I <sub>OHT</sub> | $V_{OUT} < V_{DD}$                   | 0                     |                  | -100                 | mA   |

|     | С |                                          | All I/O pins                            |                  | 5 V, I <sub>Load</sub> = 4 mA        | _                     | _                | 1.5                  |      |

|     | Ρ |                                          | (except PTF1/RESET)                     |                  | 5 V, I <sub>Load</sub> = 2 mA        | —                     | —                | 0.8                  |      |

| 6   | С |                                          | low-drive strength                      | V <sub>OL</sub>  | 3 V, I <sub>Load</sub> = 1 mA        | —                     | —                | 0.8                  | V    |

| 6   | С | -                                        | All I/O pins                            |                  | 5 V, I <sub>Load</sub> = 20 mA       | —                     | —                | 1.5                  |      |

|     | Ρ | Output low                               | (Except PTF1/RESET)                     |                  | 5 V, I <sub>Load</sub> = 10 mA       | —                     | —                | 0.8                  |      |

|     | С | voltage                                  | high-drive strength                     |                  | 3 V, I <sub>Load</sub> = 5 mA        | —                     | —                | 0.8                  |      |

| 7   | С | -                                        | PTF1/RESET                              |                  | 5 V, I <sub>Load</sub> = 3.2 mA      | —                     | _                | 1.5                  |      |

| 8   | Ρ |                                          |                                         |                  | 5 V, I <sub>Load</sub> = 1.6 mA      | —                     | _                | 0.8                  |      |

| 9   | С |                                          |                                         |                  | 3 V, I <sub>Load</sub> = 0.8 mA      | —                     | _                | 0.8                  |      |

| 10  | D | Output low current                       | Max total I <sub>OL</sub> for all ports | I <sub>OLT</sub> | $V_{OUT} > V_{SS}$                   | 0                     | _                | 100                  | mA   |

| 11  | Ρ | Input high voltage; all digit            | al inputs                               | V <sub>IH</sub>  | 5V                                   | $0.65 \times V_{DD}$  | _                | —                    | V    |

| 11  | С |                                          |                                         |                  | 3V                                   | 0.7 x V <sub>DD</sub> | —                | —                    |      |

| 12  | Ρ | Input low voltage; all digita            | al inputs                               | V <sub>IL</sub>  | 5V                                   | —                     | —                | $0.35 \times V_{DD}$ | V    |

| 12  | С |                                          |                                         |                  | 3V                                   | —                     | —                | $0.35 \times V_{DD}$ |      |

| 13  | С | Input hysteresis                         |                                         | V <sub>hys</sub> |                                      | $0.06 \times V_{DD}$  |                  |                      | V    |

| 14  | Ρ | Input leakage current (per               | pin)                                    | I <sub>In</sub>  | $V_{In} = V_{DD} \text{ or } V_{SS}$ | —                     | _                | 1                    | μA   |

|     | Ρ | Hi-Z (off-st                             | ate) leakage current (per pin)          |                  |                                      |                       |                  |                      |      |

| 15  |   |                                          | input/output port pins                  | I <sub>oz</sub>  | $V_{In} = V_{DD} \text{ or } V_{SS}$ | —                     | —                | 1                    | μA   |

| -   |   | -                                        | PTF1/RESET,<br>PTE5/XTAL pins           |                  | $V_{In} = V_{DD} \text{ or } V_{SS}$ | —                     | _                | 2                    | μA   |

|     |   | Pullup or Pulldown <sup>3</sup> resist   | ors; when enabled                       |                  |                                      |                       |                  |                      |      |

| 16  | Ρ |                                          |                                         | $R_{PU}, R_{PD}$ |                                      | 17                    | 37               | 52                   | kΩ   |

|     | С |                                          | PTF1/RESET <sup>4</sup>                 | R <sub>PU</sub>  |                                      | 17                    | 37               | 52                   | kΩ   |

|     | D | DC injection current <sup>5, 6, 7,</sup> | 8                                       |                  |                                      |                       |                  |                      |      |

|     |   |                                          | Single pin limit                        |                  | $V_{IN} > V_{DD}$                    | 0                     | _                | 2                    | mA   |

| 17  |   |                                          |                                         | I <sub>IC</sub>  | $V_{IN} < V_{SS}$                    | 0                     | _                | -0.2                 | mA   |

|     |   |                                          | Total MCU limit, includes               |                  | $V_{IN} > V_{DD}$                    | 0                     | —                | 25                   | mA   |

|     |   |                                          | sum of all stressed pins                |                  | $V_{IN} < V_{SS}$                    | 0                     | _                | -5                   | mA   |

#### Table 7. DC Characteristics (continued)

| Num | С | Characteristic                                                                                       | Symbol            | Condition  | Min          | Typ <sup>1</sup> | Max          | Unit |

|-----|---|------------------------------------------------------------------------------------------------------|-------------------|------------|--------------|------------------|--------------|------|

| 13  | С | Input Capacitance, all pins                                                                          | C <sub>In</sub>   |            |              | —                | 8            | pF   |

| 14  | С | RAM retention voltage                                                                                | V <sub>RAM</sub>  |            | —            | 0.6              | 1.0          | V    |

| 15  | С | POR re-arm voltage <sup>9</sup>                                                                      | V <sub>POR</sub>  |            | 0.9          | 1.4              | 2.0          | V    |

| 16  | D | POR re-arm time                                                                                      | t <sub>POR</sub>  |            | 10           | —                | _            | μs   |

| 17  | Р | Low-voltage detection threshold —<br>high range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVD1</sub> |            | 3.9<br>4.0   | 4.0<br>4.1       | 4.1<br>4.2   | v    |

| 18  | Ρ | Low-voltage detection threshold —<br>low range<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising  | V <sub>LVD0</sub> |            | 2.48<br>2.54 | 2.56<br>2.62     | 2.64<br>2.70 | v    |

| 19  | Ρ | Low-voltage warning threshold —<br>high range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVW3</sub> |            | 4.5<br>4.6   | 4.6<br>4.7       | 4.7<br>4.8   | v    |

| 20  | Ρ | Low-voltage warning threshold —<br>high range 0<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVW2</sub> |            | 4.2<br>4.3   | 4.3<br>4.4       | 4.4<br>4.5   | v    |

| 21  | Ρ | Low-voltage warning threshold<br>low range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising    | V <sub>LVW1</sub> |            | 2.84<br>2.90 | 2.92<br>2.98     | 3.00<br>3.06 | v    |

| 22  | Ρ | Low-voltage warning threshold —<br>low range 0<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising  | V <sub>LVW0</sub> |            | 2.66<br>2.72 | 2.74<br>2.80     | 2.82<br>2.88 | v    |

| 23  | Т | Low-voltage inhibit reset/recover hysteresis                                                         | V <sub>hys</sub>  | 5 V<br>3 V |              | 100<br>60        | _            | mV   |

| 24  | Р | Bandgap voltage reference at 25°C <sup>10</sup>                                                      |                   |            | 1.18         | 1.202            | 1.21         | V    |

| 25  | Ρ | Bandgap voltage reference across temperature range <sup>10</sup>                                     | V <sub>BG</sub>   |            | 1.17         | -                | 1.22         | v    |

#### Table 7. DC Characteristics (continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

<sup>2</sup> DC potential difference.

<sup>3</sup> When keyboard interrupt is configured to detect rising edges, pulldown resistors are used in place of pullup resistors.

<sup>4</sup> The specified resistor value is the actual value internal to the device. The pullup value may measure higher when measured externally on the pin.

- <sup>5</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current (V<sub>In</sub> > V<sub>DD</sub>) is greater than I<sub>DD</sub>, the injection current may flow out of V<sub>DD</sub> and could result in external power supply going out of regulation. Ensure external V<sub>DD</sub> load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- <sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- $^7$  All functional non-supply pins except PTF1/RESET are internally clamped to V\_{SS} and V\_{DD}

- $^{8}$  The PTF1/RESET pin does not have a clamp diode to V\_DD. Do not drive this pin above V\_DD.

- <sup>9</sup> Maximum is highest voltage that POR is guaranteed.

<sup>10</sup> Factory trimmed at  $V_{DD} = 5.0 \text{ V}$

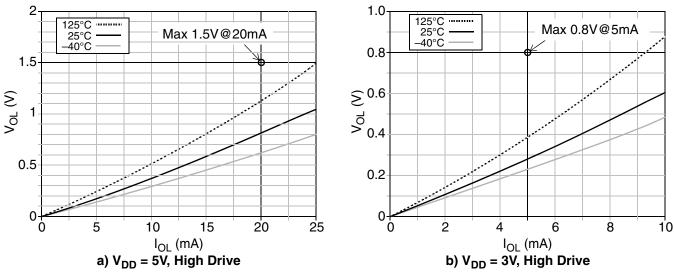

Figure 5. Typical  $V_{OL}$  vs  $I_{OL}$ , High Drive Strength (except PTF1/RESET)

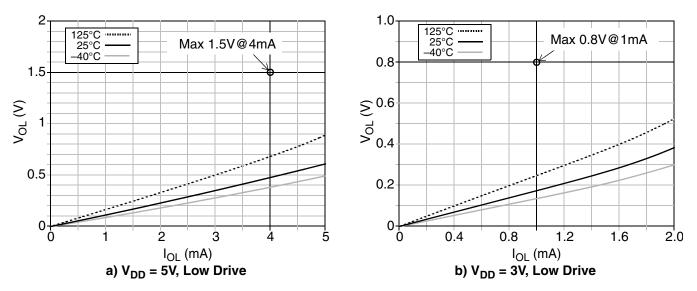

Figure 6. Typical V<sub>OL</sub> vs I<sub>OL</sub>, Low Drive Strength (except PTF1/RESET)

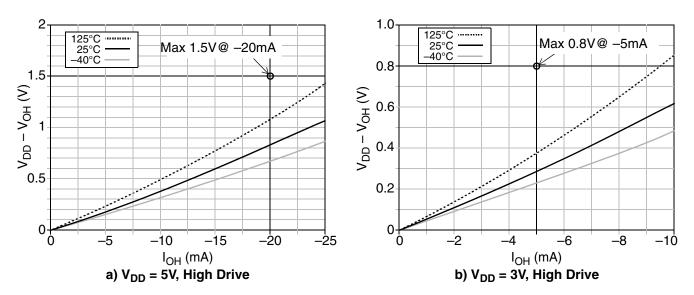

Figure 7. Typical  $V_{DD} - V_{OH}$  vs  $I_{OH}$ , High Drive Strength

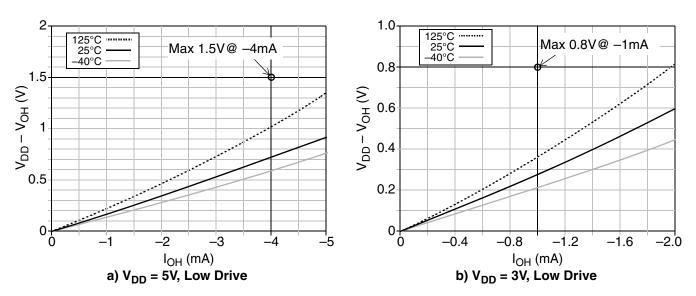

Figure 8. Typical V<sub>DD</sub> – V<sub>OH</sub> vs I<sub>OH</sub>, Low Drive Strength

### 2.7 Supply Current Characteristics

This section includes information about power supply current in various operating modes.

#### **Table 8. Supply Current Characteristics**

| Num | С | Parameter                                      | Symbol           | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----|---|------------------------------------------------|------------------|------------------------|------------------|------------------|------|

| 1   | С | Run supply current measured at                 | RI <sub>DD</sub> | 5                      | 2.16             | 3                | mA   |

|     | С | (CPU clock = 4 MHz, f <sub>Bus</sub> = 2 MHz)  | טטייי            | 3                      | 1.8              | 2.5              |      |

| 2   | Ρ | Run supply current <sup>3</sup> measured at    | RI <sub>DD</sub> | 5                      | 5.26             | 7.5              | mA   |

| 2   | С | (CPU clock = 16 MHz, f <sub>Bus</sub> = 8 MHz) | ם מייי           | 3                      | 4.92             | 7                |      |

| Num | с              | Parameter                                                                                                            | Symbol            | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----|----------------|----------------------------------------------------------------------------------------------------------------------|-------------------|------------------------|------------------|------------------|------|

| 2   | С              | Run supply current <sup>4</sup> measured at                                                                          | DI                | 5                      | 9.4              | 10               | m 4  |

| 3   | С              | (CPU clock = 32 MHz, f <sub>Bus</sub> = 16 MHz)                                                                      | RI <sub>DD</sub>  | 3                      | 9                | 10               | mA   |

| 4   | Р              | Run supply current measured at                                                                                       | RI <sub>DD</sub>  | 5                      | 14.3             | 30               | mA   |

| -   | С              | (CPU clock = 51.34 MHz, f <sub>Bus</sub> = 25.67 MHz)                                                                | ם מייי            | 3                      | 13.9             | 20               |      |

| 5   | Р              | Run supply current measured at                                                                                       | RI <sub>DD</sub>  | 5                      | 16               | 30               | mA   |

| •   | —              | (CPU clock = 40 MHz, f <sub>Bus</sub> = 20 MHz)                                                                      | 00                | 3                      | _                | _                |      |

| 6   | с              | Wait mode supply current measured at<br>(CPU clock = 8 MHz, f <sub>Bus</sub> = 4 MHz)<br>(FEI mode, all modules off) | WI <sub>DD</sub>  | 5                      | 2.7              | _                | mA   |

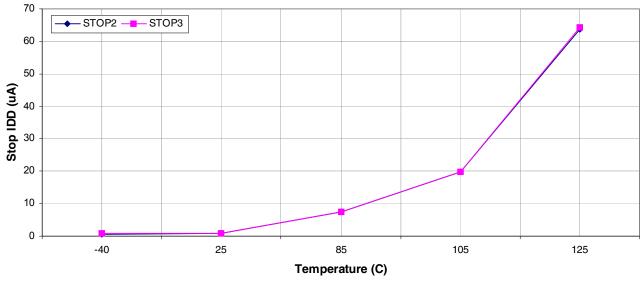

|     |                | Stop3 mode supply current                                                                                            |                   |                        |                  |                  | •    |

|     | С              | -40°C                                                                                                                |                   |                        | 0.96             | _                |      |

|     | Р              | 25°C                                                                                                                 |                   |                        | 1.3              |                  |      |

|     | С              | 85°C                                                                                                                 |                   | 5                      | 7.5              | 25               | μA   |

|     | P <sup>6</sup> | 105°C                                                                                                                |                   |                        | 37               | 90               |      |

| 7   | Р              | 125°C                                                                                                                | S3I <sub>DD</sub> |                        | 65               | 150              |      |

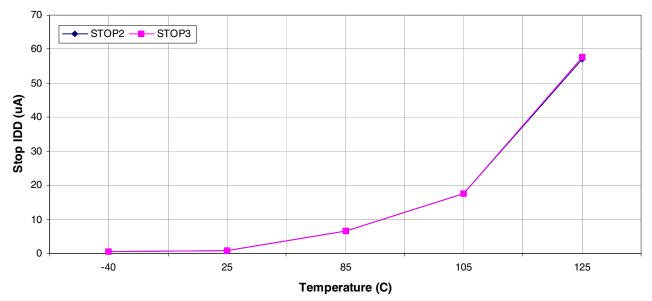

|     | С              | -40°C                                                                                                                | DD                |                        | 0.85             | _                |      |

|     | Р              | 25°C                                                                                                                 |                   |                        | 1.2              | _                |      |

|     | С              | 85°C                                                                                                                 |                   | 3                      | 6.5              | 20               | μA   |

|     | P <sup>6</sup> | 105°C                                                                                                                |                   |                        | 32.7             | 80               |      |

|     | Р              | 125°C                                                                                                                |                   |                        | 58               | 130              |      |

|     |                | Stop2 mode supply current                                                                                            |                   |                        |                  |                  | •    |

|     | С              | -40°C                                                                                                                |                   |                        | 0.94             | _                |      |

|     | Р              | 25°C                                                                                                                 |                   |                        | 1.25             |                  |      |

|     | С              | 85°C                                                                                                                 |                   | 5                      | 7                | 25               | μA   |

|     | Р <sup>6</sup> | 105°C                                                                                                                |                   |                        | 30               | 65               |      |

| 8   | Р              | 125°C                                                                                                                | S2I <sub>DD</sub> |                        | 64               | 120              |      |

|     | С              | -40°C                                                                                                                | 'DD               |                        | 0.83             |                  |      |

|     | Ρ              | 25°C                                                                                                                 |                   |                        | 1.1              |                  |      |

|     | С              | 85°C                                                                                                                 |                   | 3                      | 6.3              | 20               | μA   |

|     | P <sup>6</sup> | 105°C                                                                                                                |                   |                        | 25               | 55               |      |

|     | Р              | 125°C                                                                                                                |                   |                        | 57               | 100              |      |

| 9   | С              | RTC adder to stop2 or stop3 <sup>7</sup>                                                                             | S23I              | 5                      | 300              | 500              | nA   |

| Э   |                |                                                                                                                      |                   | 3                      | 300              | 500              | nA   |

| Table 8. Supply Current Characteristics (continued) |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Num | с | Parameter                                                           | Symbol               | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----|---|---------------------------------------------------------------------|----------------------|------------------------|------------------|------------------|------|

| 10  | С | LVD adder to stop3 (LVDE = LVDSE = 1)                               | S3I <sub>DDLVD</sub> | 5                      | 110              | 180              | μA   |

| 10  |   |                                                                     |                      | 3                      | 90               | 160              | μA   |

| 11  | С | Adder to stop3 for oscillator enabled <sup>8</sup><br>(EREFSTEN =1) | S3I <sub>DDOSC</sub> | 5,3                    | 5                | 8                | μA   |

#### Table 8. Supply Current Characteristics (continued)

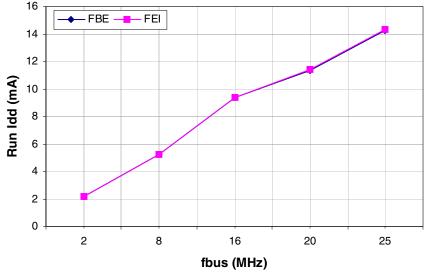

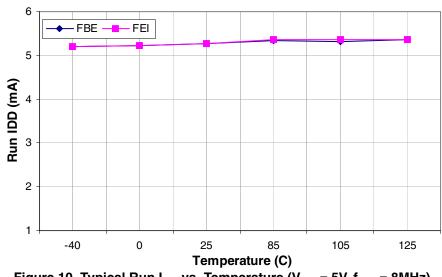

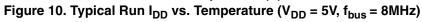

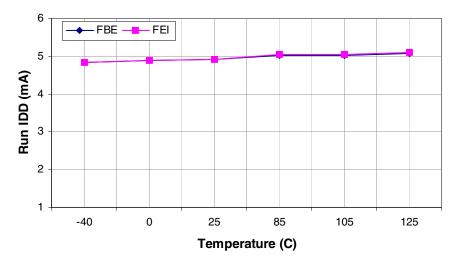

<sup>1</sup> Typical values are based on characterization data at 25°C. See Figure 9 through Figure 14 for typical curves across temperature and voltage.

<sup>2</sup> Max values in this column apply for the full operating temperature range of the device unless otherwise noted.

<sup>3</sup> All modules except ADC active, ICS configured for FBELP, and does not include any dc loads on port pins

<sup>4</sup> All modules except ADC active, ICS configured for FEI, and does not include any dc loads on port pins

<sup>5</sup> All modules except ADC active, ICS configured for FEI, and does not include any dc loads on port pins

<sup>6</sup> Stop currents are tested in production for 25°C on all parts. Tests at other temperatures depend upon the part number suffix and maturity of the product. Freescale may eliminate a test insertion at a particular temperature from the production test flow once sufficient data has been collected and is approved.

<sup>7</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode.

<sup>8</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal and low power mode (HGO = 0).

Figure 9. Typical Run  $I_{DD}$  vs. Bus Frequency ( $V_{DD} = 5V$ )

Figure 11. Typical Run  $I_{DD}$  vs. Bus Frequency ( $V_{DD}$  = 3V)

Figure 12. Typical Run  $I_{DD}$  vs. Temperature (V<sub>DD</sub> = 3V, f<sub>bus</sub> = 8MHz)

Figure 13. Typical Stop  $I_{DD}$  vs. Temperature ( $V_{DD}$  = 5V)

Figure 14. Typical Stop  $I_{DD}$  vs. Temperature ( $V_{DD} = 3V$ )

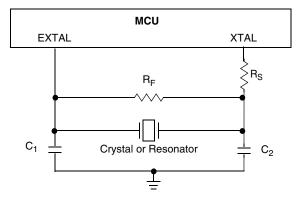

## 2.8 External Oscillator (XOSC) Characteristics

Table 9. Oscillator Electrical Specifications

| Num | С | Rating                                                           | Symbol                         | Min | Typ <sup>1</sup> | Max        | Unit |

|-----|---|------------------------------------------------------------------|--------------------------------|-----|------------------|------------|------|

|     |   | Oscillator crystal or resonator (EREFS = 1, ERCLKEN = 1)         |                                |     |                  |            |      |

|     |   | Low range (RANGE = 0)                                            | f <sub>lo</sub>                | 32  | —                | 38.4       | kHz  |

| 1   | С | High range (RANGE = 1) FEE <sup>2</sup> or FBE <sup>3</sup> mode | f <sub>hi</sub>                | 1   | _                | 16         | MHz  |

|     |   | High range (RANGE = 1, HGO = 1) FBELP mode                       | f <sub>hi-hgo</sub>            | 1   | —                | 16         | MHz  |

|     |   | High range (RANGE = 1, HGO = 0) FBELP mode                       | f <sub>hi-Ip</sub>             | 1   | —                | 8          | MHz  |

| 2   | _ | Load capacitors                                                  | C <sub>1,</sub> C <sub>2</sub> |     | -                | r resonato |      |

|     |   | Feedback resistor                                                |                                |     |                  |            |      |

| 3   | — | Low range (32 kHz to 100 kHz)                                    | R <sub>F</sub>                 | —   | 10               | —          | MΩ   |

|     |   | High range (1 MHz to 16 MHz)                                     |                                | —   | 1                | —          |      |

|     |   | Series resistor                                                  |                                |     |                  |            |      |

|     |   | Low range, low gain (RANGE = 0, HGO = 0)                         |                                | —   | 0                | —          |      |

|     |   | Low range, high gain (RANGE = 0, HGO = 1)                        |                                | —   | 100              | —          |      |

| 4   | _ | High range, low gain (RANGE = 1, HGO = 0)                        | R <sub>S</sub>                 | —   | 0                | —          | kΩ   |

| 4   |   | High range, high gain (RANGE = 1, HGO = 1)                       |                                |     |                  |            | NS2  |

|     |   | ≥ 8 MHz                                                          |                                | —   | 0                | 0          |      |

|     |   | 4 MHz                                                            |                                | —   | 0                | 10         |      |

|     |   | 1 MHz                                                            |                                | _   | 0                | 20         |      |

| Num | С | Rating                                                     | Symbol                | Min     | Typ <sup>1</sup> | Max   | Unit |

|-----|---|------------------------------------------------------------|-----------------------|---------|------------------|-------|------|

|     |   | Crystal start-up time <sup>4</sup>                         |                       |         |                  |       |      |

|     |   | Low range, low gain (RANGE = 0, HGO = 0)                   | t<br>CSTL-LP          | —       | 200              | —     |      |

| 5   | Т | Low range, high gain (RANGE = 0, HGO = 1)                  | <sup>t</sup> CSTL-HGO | —       | 400              | —     | ms   |

|     |   | High range, low gain (RANGE = 1, HGO = $0$ ) <sup>5</sup>  | t<br>CSTH-LP          | _       | 5                | —     |      |

|     |   | High range, high gain (RANGE = 1, HGO = $1)^4$             | t<br>CSTH-HGO         | —       | 20               | —     |      |

|     |   | Square wave input clock frequency (EREFS = 0, ERCLKEN = 1) |                       |         |                  |       |      |

| 6   | т | FEE mode <sup>2</sup>                                      | f                     | 0.03125 | —                | 51.34 | MHz  |

| 0   | I | FBE mode <sup>3</sup>                                      | f <sub>extal</sub>    | 0       | _                | 51.34 | MHz  |

|     |   | FBELP mode                                                 |                       | 0       | —                | 51.34 | MHz  |

#### Table 9. Oscillator Electrical Specifications (continued)

<sup>1</sup> Typical data was characterized at 5.0 V, 25°C or is recommended value.

$^2$  The input clock source must be divided using RDIV to within the range of 31.25 kHz to 39.0625 kHz.

$^3$  The input clock source must be divided using RDIV to less than or equal to 39.0625 kHz.

<sup>4</sup> This parameter is characterized and not tested on each device. Proper PC board layout procedures must be followed to achieve specifications.

<sup>5</sup> 4 MHz crystal

## 2.9 Internal Clock Source (ICS) Characteristics

#### **Table 10. ICS Frequency Specifications**

| Num | С | Characteristic                                                                                                                                            | Symbol              | Min   | Typ <sup>1</sup> | Max   | Unit |

|-----|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|------------------|-------|------|

| 1a  | Ρ | Average internal reference frequency — factory trimmed<br>(consumer- and industrial-qualified devices)<br>at V <sub>DD</sub> = 5 V and temperature = 25°C | f <sub>int_t</sub>  | _     | 32.768           | _     | kHz  |

| 1b  | Ρ | Average internal reference frequency — factory trimmed<br>(automotive-qualified devices)<br>at V <sub>DD</sub> = 5 V and temperature = 25°C               | f <sub>int_t</sub>  | _     | 31.25            | _     | kHz  |

| 2   | Ρ | Internal reference frequency — user trimmed                                                                                                               | f <sub>int_t</sub>  | 31.25 | —                | 39.06 | kHz  |

| 3   | Т | Internal reference start-up time                                                                                                                          | t <sub>irefst</sub> | —     | 60               | 100   | μS   |

| Num | С | Chara                                                                                                                  | cteristic                                      | Symbol                   | Min | Typ <sup>1</sup> | Мах   | Unit              |  |

|-----|---|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------|-----|------------------|-------|-------------------|--|

|     | Ρ |                                                                                                                        | Low range (DRS=00)                             |                          | 16  |                  | 20    |                   |  |

| 4   | С | DCO output frequency range — trimmed <sup>2</sup>                                                                      | Mid range (DRS=01)                             | f <sub>dco_t</sub>       | 32  | —                | 40    | MHz               |  |

|     | Ρ |                                                                                                                        | High range (DRS=10)                            |                          |     | 48               | —     | 60                |  |

|     | Ρ | DCO output frequency <sup>2</sup>                                                                                      | Low range (DRS=00)                             | f <sub>dco_DMX32</sub>   |     | 19.92            |       |                   |  |

| 5   | Ρ | Reference = 32768 Hz and                                                                                               | Mid range (DRS=01)                             |                          |     | 39.85            |       | MHz               |  |

|     | Ρ | DMX32 = 1                                                                                                              | High range (DRS=10)                            |                          |     | 59.77            |       |                   |  |

| 6   | С | Resolution of trimmed DCO output frequency at fixed voltage and temperature (using FTRIM)                              |                                                | $\Delta f_{dco\_res\_t}$ | _   | ± 0.1            | ± 0.2 | %f <sub>dco</sub> |  |

| 7   | С | Resolution of trimmed DCO outp temperature (not using FTRIM)                                                           | ut frequency at fixed voltage and              | $\Delta f_{dco\_res\_t}$ | _   | ± 0.2            | ± 0.4 | %f <sub>dco</sub> |  |

| 8   | Ρ | Total deviation of trimmed DCO of temperature                                                                          | output frequency over voltage and              | $\Delta f_{dco_t}$       | _   | ± 0.8            | ±2    | %f <sub>dco</sub> |  |

| 9   | С | Total deviation of trimmed DCO output frequency over fixed voltage and temperature range of 0°C to 70 $^\circ\text{C}$ |                                                | $\Delta f_{dco_t}$       |     | ± 0.5            | ± 1   | %f <sub>dco</sub> |  |

| 10  | С | FLL acquisition time <sup>3</sup>                                                                                      |                                                | t <sub>Acquire</sub>     | _   | —                | 1     | ms                |  |

| 11  | С | Long term jitter of DCO output cl                                                                                      | ock (averaged over 2-ms interval) <sup>4</sup> | C <sub>Jitter</sub>      |     | 0.02             | 0.2   | %f <sub>dco</sub> |  |

#### Table 10. ICS Frequency Specifications (continued)

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25°C or is typical recommended value.

<sup>2</sup> The resulting bus clock frequency should not exceed the maximum specified bus clock frequency of the device.

<sup>3</sup> This specification applies to any time the FLL reference source or reference divider is changed, trim value changed or changing from FLL disabled (FBELP, FBILP) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

<sup>4</sup> Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>Bus</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the FLL circuitry via V<sub>DD</sub> and V<sub>SS</sub> and variation in crystal oscillator frequency increase the C<sub>Jitter</sub> percentage for a given interval.

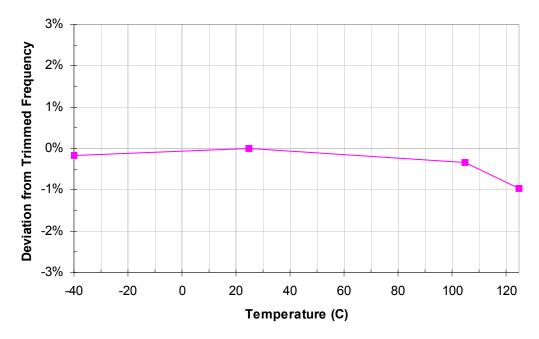

Figure 15. Typical Frequency Deviation vs Temperature (ICS Trimmed to 25 MHz bus@25°C, 5V, FEI)<sup>1</sup>

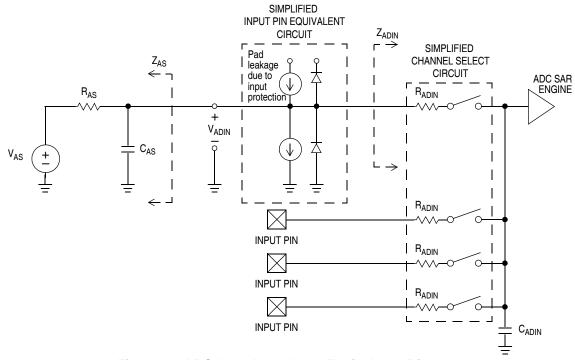

## 2.10 ADC Characteristics

| Characteristic              | Conditions                                                          | Symbol            | Min               | Typ <sup>1</sup> | Max               | Unit | Comment         |

|-----------------------------|---------------------------------------------------------------------|-------------------|-------------------|------------------|-------------------|------|-----------------|

| Supply voltage              | Absolute                                                            | V <sub>DDA</sub>  | 2.7               | _                | 5.5               | V    |                 |

| Input Voltage               |                                                                     | V <sub>ADIN</sub> | V <sub>REFL</sub> | _                | V <sub>REFH</sub> | V    |                 |

| Input Capacitance           |                                                                     | C <sub>ADIN</sub> |                   | 4.5              | 5.5               | pF   |                 |

| Input Resistance            |                                                                     | R <sub>ADIN</sub> |                   | 3                | 5                 | kΩ   |                 |

| Analog Source<br>Resistance | 12 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz | R <sub>AS</sub>   |                   |                  | 2<br>5            | kΩ   | External to MCU |

|                             | 10 bit mode<br>f <sub>ADCK</sub> > 4MHz<br>f <sub>ADCK</sub> < 4MHz |                   | _                 | _                | 5<br>10           |      |                 |

|                             | 8 bit mode (all valid f <sub>ADCK</sub> )                           | ]                 | _                 | —                | 10                |      |                 |

| ADC Conversion              | High Speed (ADLPC=0)                                                | f <sub>ADCK</sub> | 0.4               | —                | 8.0               | MHz  |                 |

| Clock Freq.                 | Low Power (ADLPC=1)                                                 | 1                 | 0.4               | —                | 4.0               |      |                 |

Table 11. 12-bit ADC Operating Conditions

Typical values assume  $V_{DDAD}$  = 5.0V, Temp = 25°C, f<sub>ADCK</sub>=1.0MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

1

<sup>1.</sup> Based on the average of several hundred units from a typical characterization lot.

Figure 16. ADC Input Impedance Equivalency Diagram

| Table 12. 12-bit ADC Characteristics (V <sub>REFH</sub> = V <sub>DDAD</sub> , V <sub>REFL</sub> = V <sub>SSAD</sub> ) |

|-----------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------|

| С | Characteristic                                  | Conditions           | Symb               | Min  | Typ <sup>1</sup> | Мах | Unit | Comment                                      |

|---|-------------------------------------------------|----------------------|--------------------|------|------------------|-----|------|----------------------------------------------|

| Т | Supply Current<br>ADLPC=1<br>ADLSMP=1<br>ADCO=1 |                      | I <sub>DDA</sub>   |      | 133              |     | μA   |                                              |

| Т | Supply Current<br>ADLPC=1<br>ADLSMP=0<br>ADCO=1 |                      | I <sub>DDA</sub>   |      | 218              | _   | μA   |                                              |

| Т | Supply Current<br>ADLPC=0<br>ADLSMP=1<br>ADCO=1 |                      | I <sub>DDA</sub>   |      | 327              | _   | μA   |                                              |

| Т | Supply Current<br>ADLPC=0<br>ADLSMP=0<br>ADCO=1 |                      | I <sub>DDA</sub>   |      | 0.582            | _   | mA   |                                              |

| Р | ADC Asynchronous<br>Clock Source                | High Speed (ADLPC=0) | f <sub>ADACK</sub> | 2    | 3.3              | 5   | MHz  | t <sub>ADACK</sub> =<br>1/f <sub>ADACK</sub> |

|   |                                                 | Low Power (ADLPC=1)  |                    | 1.25 | 2                | 3.3 |      |                                              |

| - | Table 12. 12-bit Abo onalacteristics (VREFH = VDDAD, VREFL = VSSAD) (continued) |                          |                     |     |                  |                 |                  |                                                                                      |  |

|---|---------------------------------------------------------------------------------|--------------------------|---------------------|-----|------------------|-----------------|------------------|--------------------------------------------------------------------------------------|--|

| С | Characteristic                                                                  | Conditions               | Symb                | Min | Typ <sup>1</sup> | Max             | Unit             | Comment                                                                              |  |

| D | D Conversion Time<br>(Including sample<br>time)                                 | Short Sample (ADLSMP=0)  | t <sub>ADC</sub>    |     | 20               | —               | ADCK<br>cycles   | See ADC<br>chapter in the<br>Reference<br>Manual for<br>conversion time<br>variances |  |

|   |                                                                                 | Long Sample (ADLSMP=1)   |                     | —   | 40               | —               |                  |                                                                                      |  |

| D | D Sample Time                                                                   | Short Sample (ADLSMP=0)  | t <sub>ADS</sub>    |     | 3.5              | —               | ADCK<br>cycles   |                                                                                      |  |

|   |                                                                                 | Long Sample (ADLSMP=1)   |                     | —   | 23.5             | —               |                  |                                                                                      |  |

| Т | T Temp Sensor<br>Slope                                                          | -40°C to 25°C            | m                   | _   | 3.266            | —               | mV/°C            |                                                                                      |  |

|   |                                                                                 | 25°C to 125°C            |                     | _   | 3.638            | —               |                  |                                                                                      |  |

| Т | Temp Sensor<br>Voltage                                                          | 25°C                     | V <sub>TEMP25</sub> | _   | 1.396            | —               | mV               |                                                                                      |  |

| Т | Total Unadjusted                                                                | 12 bit mode              | E <sub>TUE</sub>    |     | ±3.0             | ±6.5            | LSB <sup>2</sup> | Includes<br>quantization                                                             |  |

| Р | Error                                                                           | 10 bit mode              |                     |     | ±1               | ±2.5            |                  |                                                                                      |  |

| Т |                                                                                 | 8 bit mode               |                     |     | ±0.5             | ±1.0            |                  |                                                                                      |  |

| Т | Differential                                                                    | 12 bit mode              | DNL                 |     | ±1.75            | ±3.5            | LSB <sup>2</sup> |                                                                                      |  |

| Р | Non-Linearity                                                                   | 10 bit mode <sup>3</sup> |                     |     | ±0.5             | ±1.0            |                  |                                                                                      |  |

| Т |                                                                                 | 8 bit mode <sup>3</sup>  |                     |     | ±0.3             | ±0.5            |                  |                                                                                      |  |

| Т | Integral                                                                        | 12 bit mode              | INL                 |     | ±1.5             | ±4.5            | LSB <sup>2</sup> |                                                                                      |  |

| Р | Non-Linearity                                                                   | 10 bit mode              |                     |     | ±0.5             | ±1.0            |                  |                                                                                      |  |

| Т |                                                                                 | 8 bit mode               |                     |     | ±0.3             | ±0.5            |                  |                                                                                      |  |

| Т | Zero-Scale Error                                                                | 12 bit mode              | E <sub>ZS</sub>     | _   | ±1.5             | 0.0/<br>-3.0    | LSB <sup>2</sup> | V <sub>ADIN</sub> = V <sub>SSAD</sub>                                                |  |

| Р |                                                                                 | 10 bit mode              |                     |     | ±0.5             | ±1.5            |                  |                                                                                      |  |

| Т |                                                                                 | 8 bit mode               |                     |     | ±0.5             | ±0.5            |                  |                                                                                      |  |

| Т | Full-Scale Error                                                                | 12 bit mode              | E <sub>FS</sub>     | —   | ±1.0             | +1.75/<br>-1.25 | LSB <sup>2</sup> | $V_{ADIN} = V_{DDAD}$                                                                |  |

| Т |                                                                                 | 10 bit mode              |                     |     | ±0.5             | ±1              |                  |                                                                                      |  |

| Т |                                                                                 | 8 bit mode               |                     |     | ±0.5             | ±0.5            |                  |                                                                                      |  |