# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# INTEGRATED CIRCUITS

Product specification

2004 Mar 04

HILIP

| CONTENTO |

|----------|

| CONTENTS |

| 1                               | FEATURES                                                                                                          |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 2                               | GENERAL DESCRIPTION                                                                                               |

| 3                               | QUICK REFERENCE DATA                                                                                              |

| 4                               | ORDERING INFORMATION                                                                                              |

| 5                               | BLOCK DIAGRAM                                                                                                     |

| 6                               | PINNING                                                                                                           |

| 7                               | FUNCTIONAL DESCRIPTION                                                                                            |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5 | Reset conditions<br>Input formatter<br>RGB LUT<br>Cursor insertion<br>RGB Y-C <sub>B</sub> -C <sub>B</sub> matrix |

| 7.6                             | Horizontal scaler                                                                                                 |

| 7.7                             | Vertical scaler and anti-flicker filter                                                                           |

| 7.8                             | FIFO                                                                                                              |

| 7.9                             | Border generator                                                                                                  |

| 7.10                            | Oscillator and Discrete Time Oscillator (DTO)                                                                     |

| 7.11                            | Low-pass Clock Generation Circuit (CGC)                                                                           |

| 7.12                            | Encoder                                                                                                           |

| 7.13                            | RGB processor                                                                                                     |

| 7.14                            | Triple DAC                                                                                                        |

| 7.15                            | HD data path                                                                                                      |

| 7.16                            | Timing generator                                                                                                  |

| 7.17                            | Pattern generator for HD sync pulses                                                                              |

| 7.18                            | I <sup>2</sup> C-bus interface                                                                                    |

| 7.19                            | Power-down modes                                                                                                  |

| 7.20                            | Programming the SAA7104E; SAA7105E                                                                                |

| 7.21                            | Input levels and formats                                                                                          |

| 7.22                            | Bit allocation map                                                                                                |

| 7.23                            | I <sup>2</sup> C-bus format                                                                                       |

| 7.24                            | Slave receiver                                                                                                    |

| 7.25                            | Slave transmitter                                                                                                 |

| 8                               | BOUNDARY SCAN TEST                                                                                                |

| 8.1                             | Initialization of boundary scan circuit                                                                           |

8.2 Device identification codes

# SAA7104E; SAA7105E

| 9                    | LIMITING VALUES                                                                   |

|----------------------|-----------------------------------------------------------------------------------|

| 10                   | THERMAL CHARACTERISTICS                                                           |

| 11                   | CHARACTERISTICS                                                                   |

| 11.1                 | Teletext timing                                                                   |

| 12                   | APPLICATION INFORMATION                                                           |

| 12.1<br>12.2<br>12.3 | Reconstruction filter<br>Analog output voltages<br>Suggestions for a board layout |

| 13                   | PACKAGE OUTLINE                                                                   |

| 14                   | SOLDERING                                                                         |

| 14.1                 | Introduction to soldering surface mount<br>packages                               |

| 14.2                 | Reflow soldering                                                                  |

| 14.3<br>14.4         | Wave soldering<br>Manual soldering                                                |

| 14.5                 | Suitability of surface mount IC packages for wave and reflow soldering methods    |

| 15                   | DATA SHEET STATUS                                                                 |

| 16                   | DEFINITIONS                                                                       |

| 17                   | DISCLAIMERS                                                                       |

| 18                   | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                   |

# SAA7104E; SAA7105E

## **1 FEATURES**

- Digital PAL/NTSC encoder with integrated high quality scaler and anti-flicker filter for TV output from a PC

- Supports Intel® Digital Video Out (DVO) low voltage interfacing to graphics controller

- 27 MHz crystal-stable subcarrier generation

- Maximum graphics pixel clock 85 MHz at double edged clocking, synthesized on-chip or from external source

- Programmable assignment of clock edge to bytes (in double edged mode)

- Synthesizable pixel clock (PIXCLK) with minimized output jitter, can be used as reference clock for the VGC, as well)

- PIXCLK output and bi-phase PIXCLK input (VGC clock loop-through possible)

- Hot-plug detection through dedicated interrupt pin

- Supported VGA resolutions for PAL or NTSC legacy video output up to 1280 × 1024 graphics data at 60 or 50 Hz frame rate

- Supported VGA resolutions for HDTV output up to  $1\,920\times1080$  interlaced graphics data at 60 or 50 Hz frame rate

- Three Digital-to-Analog Converters (DACs) for CVBS (BLUE, C<sub>B</sub>), VBS (GREEN, CVBS) and C (RED, C<sub>R</sub>) at 27 MHz sample rate (signals in parenthesis are optionally), all at 10-bit resolution

- Non-interlaced  $C_B$ -Y- $C_R$  or RGB input at maximum 4 : 4 : 4 sampling

- Downscaling and upscaling from 50 to 400%

- Optional interlaced C<sub>B</sub>-Y-C<sub>R</sub> input of Digital Versatile Disk (DVD) signals

- Optional non-interlaced RGB output to drive second VGA monitor (bypass mode, maximum 85 MHz)

- 3 × 256 bytes RGB Look-Up Table (LUT)

- Support for hardware cursor

- HDTV up to 1920 × 1080 interlaced and 1280 × 720 progressive, including 3-level sync pulses

- Programmable border colour of underscan area

- Programmable 5 line anti-flicker filter

- On-chip 27 MHz crystal oscillator (3rd-harmonic or fundamental 27 MHz crystal)

- Fast I<sup>2</sup>C-bus control port (400 kHz)

- Encoder can be master or slave

- Adjustable output levels for the DACs

- Programmable horizontal and vertical input synchronization phase

- Programmable horizontal sync output phase

- Internal Colour Bar Generator (CBG)

- Optional support of various Vertical Blanking Interval (VBI) data insertion

- Macrovision<sup>™(1)</sup> Pay-per-View copy protection system rev. 7.01, rev. 6.1 and rev. 1.03 (525p) as option; this applies to the SAA7104E only. The device is protected by USA patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. Use of the Macrovision anti-copy process in the device is licensed for non-commercial home use only. Reverse engineering or disassembly is prohibited. Please contact your nearest Philips Semiconductors sales office for more information.

- Optional cross-colour reduction for PAL and NTSC CVBS outputs

- Power-save modes

- Joint Test Action Group (JTAG) boundary scan test

- Monolithic CMOS 3.3 V device, 5 V tolerant I/Os.

(1) Macrovision<sup>™</sup> is a trademark of the Macrovision Corporation.

# SAA7104E; SAA7105E

### 2 GENERAL DESCRIPTION

The SAA7104E; SAA7105E is an advanced next-generation video encoder which converts PC graphics data at maximum  $1280 \times 1024$  resolution (optionally  $1920 \times 1080$  interlaced) to PAL (50 Hz) or NTSC (60 Hz) video signals. A programmable scaler and anti-flicker filter (maximum 5 lines) ensures properly sized and flicker-free TV display as CVBS or S-video output.

Alternatively, the three Digital-to-Analog Converters (DACs) can output RGB signals together with a TTL composite sync to feed SCART connectors.

When the scaler/interlacer is bypassed, a second VGA monitor can be connected to the RGB outputs and separate H and V-syncs as well, thereby serving as an auxiliary monitor at maximum  $1280 \times 1024$  resolution/60 Hz (PIXCLK < 85 MHz). Alternatively this port can provide Y, P<sub>B</sub> and P<sub>R</sub> signals for HDTV monitors.

The device includes a sync/clock generator and on-chip DACs.

All inputs intended to interface to the host graphics controller are designed for low-voltage signals between down to 1.1 V and up to 3.6 V.

#### 3 QUICK REFERENCE DATA

| SYMBOL                 | PARAMETER                                                                                             | MIN.     | TYP.    | MAX. | UNIT |

|------------------------|-------------------------------------------------------------------------------------------------------|----------|---------|------|------|

| V <sub>DDA</sub>       | analog supply voltage                                                                                 | 3.15     | 3.3     | 3.45 | V    |

| V <sub>DDD</sub>       | digital supply voltage                                                                                | 3.15     | 3.3     | 3.45 | V    |

| I <sub>DDA</sub>       | analog supply current                                                                                 | 1        | 110     | 115  | mA   |

| I <sub>DDD</sub>       | digital supply current                                                                                | 1        | 175     | 200  | mA   |

| Vi                     | input signal voltage levels                                                                           | TTL comp | batible |      |      |

| V <sub>o(p-p)</sub>    | analog CVBS output signal voltage for a 100/100 colour bar at 75/2 $\Omega$ load (peak-to-peak value) | -        | 1.23    | -    | V    |

| RL                     | load resistance                                                                                       | -        | 37.5    | -    | Ω    |

| ILE <sub>lf(DAC)</sub> | low frequency integral linearity error of DACs                                                        | -        | -       | ±3   | LSB  |

| DLE <sub>lf(DAC)</sub> | low frequency differential linearity error of DACs                                                    | -        | -       | ±1   | LSB  |

| T <sub>amb</sub>       | ambient temperature                                                                                   | 0        | _       | 70   | °C   |

#### 4 ORDERING INFORMATION

|              |        | PACKAGE                                          |          |

|--------------|--------|--------------------------------------------------|----------|

| I TPE NUMBER | NAME   | DESCRIPTION                                      | VERSION  |

| SAA7104E     | BGA156 | plastic ball grid array package; 156 balls; body | SOT472-1 |

| SAA7105E     |        | $15 \times 15 \times 1.15 \text{ mm}$            |          |

2004 Mar 04

\_

Philips Semiconductors

Digital video encoder

S

Product specification

SAA7104E; SAA7105E

S

# SAA7104E; SAA7105E

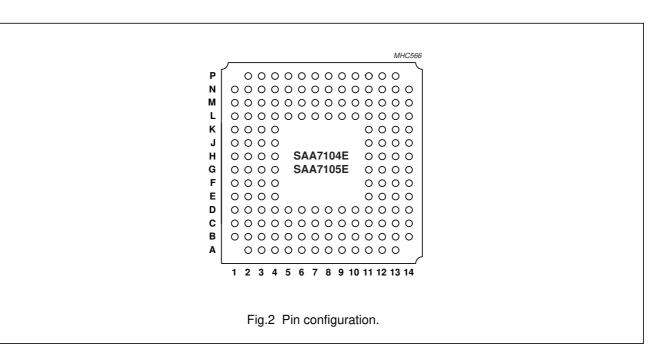

## 6 PINNING

| SYMBOL            | PIN             | <b>TYPE</b> <sup>(1)</sup> | DESCRIPTION                                                                                                                           |  |  |

|-------------------|-----------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PD7               | A2              | I                          | MSB with $C_B$ -Y- $C_R$ 4 : 2 : 2; see Tables 9 to 14 for pin assignment                                                             |  |  |

| PD4               | A3              | I                          | $MSB - 3 \text{ with } C_B-Y-C_R 4 : 2 : 2; \text{ see Tables 9 to 14 for}$<br>pin assignment                                         |  |  |

| TRST              | A4              | l/pu                       | test reset input for BST; active LOW; notes 2, 3 and 4                                                                                |  |  |

| XTALI             | A5              | I                          | crystal oscillator input                                                                                                              |  |  |

| XTALO             | A6              | 0                          | crystal oscillator output                                                                                                             |  |  |

| DUMP              | A7, B7          | 0                          | DAC reference pin; connected via 12 $\Omega$ resistor to analog ground                                                                |  |  |

| V <sub>SSA2</sub> | A8              | S                          | analog ground 2                                                                                                                       |  |  |

| RSET              | A9              | 0                          | DAC reference pin; connected via 1 k $\Omega$ resistor to analog ground (do not use capacitor in parallel with 1 k $\Omega$ resistor) |  |  |

| V <sub>DDA1</sub> | A10, B9, C9, D9 | S                          | analog supply voltage 1 (3.3 V for DACs)                                                                                              |  |  |

| PD9               | B1              | I                          | see Tables 9 to 14 for pin assignment                                                                                                 |  |  |

| PD8               | B2              | I                          | see Tables 9 to 14 for pin assignment                                                                                                 |  |  |

| PD5               | B3              | I                          | MSB – 2 with $C_B$ -Y- $C_R$ 4 : 2 : 2; see Tables 9 to 14 for pin assignment                                                         |  |  |

| PD6               | B4              | I                          | $MSB - 1$ with $C_B$ -Y- $C_R$ 4 : 2 : 2; see Tables 9 to 14 for pin assignment                                                       |  |  |

| TDI               | B5              | I                          | test data input for BST; note 2                                                                                                       |  |  |

| V <sub>DDA2</sub> | B6              | S                          | analog supply voltage 2 (3.3 V for DACs)                                                                                              |  |  |

| V <sub>DDA4</sub> | B6              | S                          | analog supply voltage 4 (3.3 V)                                                                                                       |  |  |

| V <sub>SSA1</sub> | B8              | S                          | analog ground 1                                                                                                                       |  |  |

| PD11              | C1              | I                          | see Tables 9 to 14 for pin assignment                                                                                                 |  |  |

| PD10              | C2              | I                          | see Tables 9 to 14 for pin assignment                                                                                                 |  |  |

| TTX_SRES          | C3              | I                          | teletext input or sync reset input                                                                                                    |  |  |

| TTXRQ_XCLKO2      | C4              | 0                          | teletext request output or 13.5 MHz clock output of the crystal oscillator; note 5                                                    |  |  |

| V <sub>SSD1</sub> | C5, D5, E4      | S                          | digital ground 1                                                                                                                      |  |  |

| V <sub>SSD2</sub> | C5, D5, E4      | S                          | digital ground 2                                                                                                                      |  |  |

| V <sub>SSD3</sub> | C5, D5, E4      | S                          | digital ground 3                                                                                                                      |  |  |

| V <sub>SSD4</sub> | C5, D5, E4      | S                          | digital ground 4                                                                                                                      |  |  |

| BLUE_CB_CVBS      | C6              | 0                          | analog output of BLUE or C <sub>B</sub> or CVBS signal                                                                                |  |  |

| GREEN_VBS_CVBS    | C7              | 0                          | analog output of GREEN or VBS or CVBS signal                                                                                          |  |  |

| RED_CR_C_CVBS     | C8              | 0                          | analog output of RED or C <sub>R</sub> or C or CVBS signal                                                                            |  |  |

| TDO               | D1              | 0                          | test data output for BST; note 2                                                                                                      |  |  |

| RESET             | D2              | I                          | reset input; active LOW                                                                                                               |  |  |

| TMS               | D3              | l/pu                       | test mode select input for Boundary Scan Test (BST); note 2                                                                           |  |  |

| V <sub>DDD2</sub> | D4              | S                          | digital supply voltage 2 (3.3 V for I/Os)                                                                                             |  |  |

| V <sub>DDD3</sub> | D4              | S                          | digital supply voltage 3 (3.3 V for core)                                                                                             |  |  |

| V <sub>DDD4</sub> | D4              | S                          | digital supply voltage 4 (3.3 V for core)                                                                                             |  |  |

| V <sub>DDA3</sub> | D6              | S                          | analog supply voltage 3 (3.3 V for oscillator)                                                                                        |  |  |

# SAA7104E; SAA7105E

| SYMBOL            | PIN | <b>TYPE</b> <sup>(1)</sup> | DESCRIPTION                                                                                                 |  |  |

|-------------------|-----|----------------------------|-------------------------------------------------------------------------------------------------------------|--|--|

| VSM               | D7  | 0                          | vertical synchronization output to monitor (non-interlaced auxiliary RGB)                                   |  |  |

| HSM_CSYNC         | D8  | 0                          | horizontal synchronization output to monitor (non-interlaced auxiliary RGB) or composite sync for RGB-SCART |  |  |

| TCK               | E1  | l/pu                       | test clock input for BST; note 2                                                                            |  |  |

| SCL               | E2  |                            | I <sup>2</sup> C-bus serial clock input                                                                     |  |  |

| HSVGC             | E3  | I/O                        | horizontal synchronization output to VGC (optional input); note 5                                           |  |  |

| reserved          | E12 | -                          | to be reserved for future applications                                                                      |  |  |

| VSVGC             | F1  | I/O                        | vertical synchronization output to VGC (optional input); note 5                                             |  |  |

| PIXCLKI           | F2  |                            | pixel clock input (looped through)                                                                          |  |  |

| PD3               | F3  | I                          | $MSB - 4$ with $C_B$ -Y- $C_R$ 4 : 2 : 2; see Tables 9 to 14 for pin assignment                             |  |  |

| V <sub>DDD1</sub> | F4  | S                          | digital supply voltage 1 for pins PD11 to PD0, PIXCLKI, PIXCLKO, FSVGC, VSVGC, HSVGC, CBO and TVD           |  |  |

| TVD               | F12 | 0                          | interrupt if TV is detected at DAC output                                                                   |  |  |

| FSVGC             | G1  | I/O                        | frame synchronization output to Video Graphics Controller (VGC) (optional input); note 5                    |  |  |

| SDA               | G2  | I/O                        | I <sup>2</sup> C-bus serial data input/output                                                               |  |  |

| CBO               | G3  | I/O                        | composite blanking output to VGC; active LOW; note 5                                                        |  |  |

| PIXCLKO           | G4  | 0                          | pixel clock output to VGC                                                                                   |  |  |

| PD2               | H1  | I                          | MSB – 5 with $C_B$ -Y-C <sub>R</sub> 4 : 2 : 2; see Tables 9 to 14 for pin assignment                       |  |  |

| PD1               | H2  | I                          | $MSB - 6$ with $C_B$ -Y- $C_R 4 : 2 : 2$ ; see Tables 9 to 14 for pin assignment                            |  |  |

| PD0               | НЗ  | I                          | $MSB - 7$ with $C_B$ -Y- $C_R$ 4 : 2 : 2; see Tables 9 to 14 for pin assignment                             |  |  |

#### Notes

- 1. Pin type: I = input, O = output, S = supply, pu = pull-up.

- 2. In accordance with the *"IEEE1149.1"* standard the pins TDI, TMS, TCK and TRST are input pins with an internal pull-up resistor and TDO is a 3-state output pin.

- 3. For board design without boundary scan implementation connect TRST to ground.

- 4. This pin provides easy initialization of the Boundary Scan Test (BST) circuit. TRST can be used to force the Test Access Port (TAP) controller to the TEST\_LOGIC\_RESET state (normal operation) at once.

- 5. The pins FSVGC, VSVGC, CBO, HSVGC and TTXRQ\_XCLKO2 are used for bootstrapping; see Section 7.1.

# SAA7104E; SAA7105E

Table 1

Pin assignment (top view)

|   | 1     | 2       | 3            | 4                                                                                | 5                                                                                | 6                                      | 7                      | 8                         | 9                 | 10                | 11 | 12       | 13 | 14 |

|---|-------|---------|--------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------|------------------------|---------------------------|-------------------|-------------------|----|----------|----|----|

| A |       | PD7     | PD4          | TRST                                                                             | XTALI                                                                            | XTALO                                  | DUMP                   | V <sub>SSA2</sub>         | RSET              | V <sub>DDA1</sub> |    |          |    |    |

| В | PD9   | PD8     | PD5          | PD6                                                                              | TDI                                                                              | V <sub>DDA2</sub><br>V <sub>DDA4</sub> | DUMP                   | V <sub>SSA1</sub>         | V <sub>DDA1</sub> |                   |    |          |    |    |

| С | PD11  | PD10    | TTX_<br>SRES | TTXRQ_<br>XCLKO2                                                                 | V <sub>SSD1</sub><br>V <sub>SSD2</sub><br>V <sub>SSD3</sub><br>V <sub>SSD4</sub> | BLUE_<br>CB_<br>CVBS                   | GREEN_<br>VBS_<br>CVBS | RED_<br>CR_<br>C_<br>CVBS | V <sub>DDA1</sub> |                   |    |          |    |    |

| D | TDO   | RESET   | TMS          | V <sub>DDD2</sub><br>V <sub>DDD3</sub><br>V <sub>DDD4</sub>                      | V <sub>SSD1</sub><br>V <sub>SSD2</sub><br>V <sub>SSD3</sub><br>V <sub>SSD4</sub> | V <sub>DDA3</sub>                      | VSM                    | HSM_<br>CSYNC             | V <sub>DDA1</sub> |                   |    |          |    |    |

| E | тск   | SCL     | HSVGC        | V <sub>SSD1</sub><br>V <sub>SSD2</sub><br>V <sub>SSD3</sub><br>V <sub>SSD4</sub> |                                                                                  |                                        |                        |                           |                   |                   |    | reserved |    |    |

| F | VSVGC | PIXCLKI | PD3          | V <sub>DDD1</sub>                                                                |                                                                                  |                                        |                        |                           |                   |                   |    | TVD      |    |    |

| G | FSVGC | SDA     | CBO          | PIXCLKO                                                                          |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| н | PD2   | PD1     | PD0          |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| J |       |         |              |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| к |       |         |              |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| L |       |         |              |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| М |       |         |              |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| Ν |       |         |              |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

| Ρ |       |         |              |                                                                                  |                                                                                  |                                        |                        |                           |                   |                   |    |          |    |    |

SAA7104E; SAA7105E

# Digital video encoder

#### 7 FUNCTIONAL DESCRIPTION

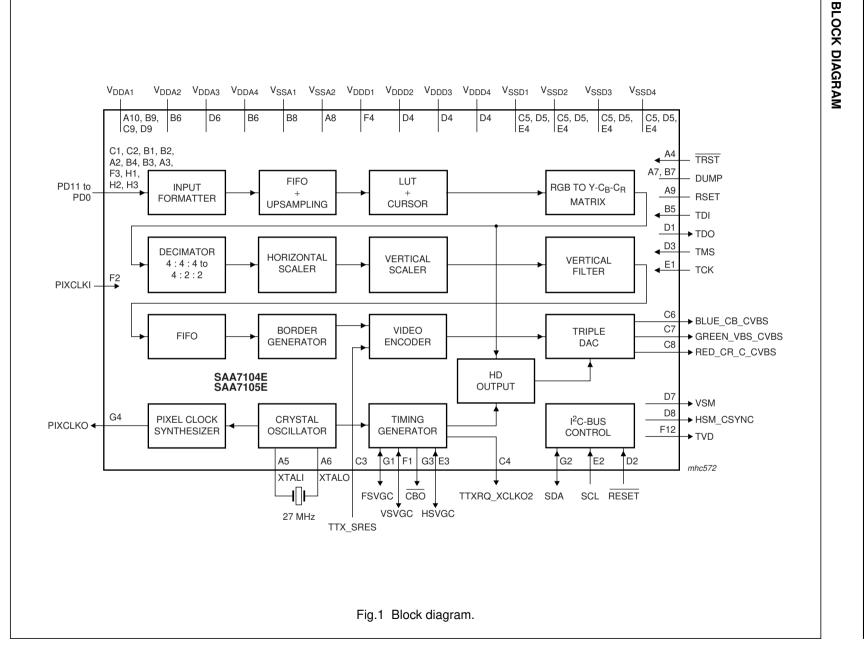

The digital video encoder encodes digital luminance and colour difference signals ( $C_B$ -Y- $C_R$ ) or digital RGB signals into analog CVBS, S-video and, optionally, RGB or  $C_R$ -Y- $C_B$  signals. NTSC M, PAL B/G and sub-standards are supported.

The SAA7104E; SAA7105E can be directly connected to a PC video graphics controller with a maximum resolution of  $1280 \times 1024$  (progressive) or  $1920 \times 1080$  (interlaced) at a 50 or 60 Hz frame rate. A programmable scaler scales the computer graphics picture so that it will fit into a standard TV screen with an adjustable underscan area. Non-interlaced-to-interlaced conversion is optimized with an adjustable anti-flicker filter for a flicker-free display at a very high sharpness.

Besides the most common 16-bit 4 : 2 : 2  $C_B$ -Y- $C_R$  input format (using 8 pins with double edge clocking), other  $C_B$ -Y- $C_R$  and RGB formats are also supported; see Tables 9 to 14.

A complete  $3 \times 256$  bytes Look-Up Table (LUT), which can be used, for example, as a separate gamma corrector, is located in the RGB domain; it can be loaded either through the video input port PD (Pixel Data) or via the l<sup>2</sup>C-bus.

The SAA7104E; SAA7105E supports a  $32 \times 32 \times 2$ -bit hardware cursor, the pattern of which can also be loaded through the video input port or via the l<sup>2</sup>C-bus.

It is also possible to encode interlaced 4 : 2 : 2 video signals such as PC-DVD; for that the anti-flicker filter, and in most cases the scaler, will simply be bypassed.

Besides the applications for video output, the SAA7104E; SAA7105E can also be used for generating a kind of auxiliary VGA output, when the RGB non-interlaced input signal is fed to the DACs. This may be of interest for example, when the graphics controller provides a second graphics window at its video output port.

The basic encoder function consists of subcarrier generation, colour modulation and insertion of synchronization signals at a crystal-stable clock rate of 13.5 MHz (independent of the actual pixel clock used at the input side), corresponding to an internal 4 : 2 : 2 bandwidth in the luminance/colour difference domain. Luminance and chrominance signals are filtered in accordance with the standard requirements of *"RS-170-A"* and *"ITU-R BT.470-3"*.

For ease of analog post filtering the signals are twice oversampled to 27 MHz before digital-to-analog conversion.

The total filter transfer characteristics (scaler and anti-flicker filter are not taken into account) are illustrated in Figs 4 to 9. All three DACs are realized with full 10-bit resolution. The C<sub>R</sub>-Y-C<sub>B</sub> to RGB dematrix can be bypassed (optionally) in order to provide the upsampled C<sub>R</sub>-Y-C<sub>B</sub> input signals.

# SAA7104E; SAA7105E

The 8-bit multiplexed  $C_B$ -Y- $C_R$  formats are *"ITU-R BT.656"* (D1 format) compatible, but the SAV and EAV codes can be decoded optionally, when the device is operated in slave mode. For assignment of the input data to the rising or falling clock edge see Tables 9 to 14.

In order to display interlaced RGB signals through a euro-connector TV set, a separate digital composite sync signal (pin HSM\_CSYNC) can be generated; it can be advanced up to 31 periods of the 27 MHz crystal clock in order to be adapted to the RGB processing of a TV set.

The SAA7104E; SAA7105E synthesizes all necessary internal signals, colour subcarrier frequency and synchronization signals from that clock.

Wide screen signalling data can be loaded via the  $I^2$ C-bus and is inserted into line 23 for standards using a 50 Hz field rate.

VPS data for program dependent automatic start and stop of such featured VCRs is loadable via the I<sup>2</sup>C-bus.

The IC also contains Closed Caption and extended data services encoding (line 21), and supports teletext insertion for the appropriate bit stream format at a 27 MHz clock rate (see Fig.14). It is also possible to load data for the copy generation management system into line 20 of every field (525/60 line counting).

A number of possibilities are provided for setting different video parameters such as:

- Black and blanking level control

- Colour subcarrier frequency

- Variable burst amplitude etc.

#### 7.1 Reset conditions

To activate the reset a pulse at least of 2 crystal clocks duration is required.

During reset ( $\overline{\text{RESET}}$  = LOW) plus an extra 32 crystal clock periods, FSVGC, VSVGC,  $\overline{\text{CBO}}$ , HSVGC and TTX\_SRES are set to input mode and HSM\_CSYNC and VSM are set to 3-state. A reset also forces the l<sup>2</sup>C-bus interface to abort any running bus transfer and sets it into receive condition.

After reset, the state of the I/Os and other functions is defined by the strapping pins until an I<sup>2</sup>C-bus access redefines the corresponding registers; see Table 2.

#### Table 2 Strapping pins

| PIN          | TIED | PRESET                                                                         |  |  |  |  |  |

|--------------|------|--------------------------------------------------------------------------------|--|--|--|--|--|

| FSVGC        | LOW  | NTSC M encoding, PIXCLK<br>fits to 640 × 480 graphics<br>input                 |  |  |  |  |  |

|              | HIGH | PAL B/G encoding, PIXCLK<br>fits to 640 × 480 graphics<br>input                |  |  |  |  |  |

| VSVGC        | LOW  | $4:2:2 Y-C_B-C_R$ graphics input (format 0)                                    |  |  |  |  |  |

|              | HIGH | 4:4:4 RGB graphics input<br>(format 3)                                         |  |  |  |  |  |

| CBO          | LOW  | input demultiplex phase:<br>LSB = LOW                                          |  |  |  |  |  |

|              | HIGH | input demultiplex phase:<br>LSB = HIGH                                         |  |  |  |  |  |

| HSVGC        | LOW  | input demultiplex phase:<br>MSB = LOW                                          |  |  |  |  |  |

|              | HIGH | input demultiplex phase:<br>MSB = HIGH                                         |  |  |  |  |  |

| TTXRQ_XCLKO2 | LOW  | slave (FSVGC, VSVGC and<br>HSVGC are inputs, internal<br>colour bar is active) |  |  |  |  |  |

|              | HIGH | master (FSVGC, VSVGC and HSVGC are outputs)                                    |  |  |  |  |  |

#### 7.2 Input formatter

The input formatter converts all accepted PD input data formats, either RGB or  $Y-C_B-C_R$ , to a common internal RGB or  $Y-C_B-C_R$  data stream.

When double-edge clocking is used, the data is internally split into portions PPD1 and PPD2. The clock edge assignment must be set according to the I<sup>2</sup>C-bus control bits SLOT and EDGE for correct operation.

If Y- $C_B$ - $C_R$  is being applied as a 27 Mbyte/s data stream, the output of the input formatter can be used directly to feed the video encoder block.

The horizontal upscaling is supported via the input formatter. According to the programming of the pixel clock dividers (see Section 7.10), it will sample up the data stream to  $1 \times, 2 \times$  or  $4 \times$  the input data rate. An optional interpolation filter is available. The clock domain transition is handled by a 4 entries wide FIFO which gets initialized every field or explicitly at request. A bypass for the FIFO is available, especially for high input data rates.

## 7.3 RGB LUT

The three 256 byte RAMs of this block can be addressed by three 8-bit wide signals, thus it can be used to build any transformation, e.g. a gamma correction for RGB signals. In the event that the indexed colour data is applied, the RAMs are addressed in parallel.

The LUTs can either be loaded by an I<sup>2</sup>C-bus write access or can be part of the pixel data input through the PD port. In the latter case,  $256 \times 3$  bytes for the R, G and B LUT are expected at the beginning of the input video line, two lines before the line that has been defined as first active line, until the middle of the line immediately preceding the first active line. The first 3 bytes represent the first RGB LUT data, and so on.

### 7.4 Cursor insertion

A 32  $\times$  32 dots cursor can be overlaid as an option; the bit map of the cursor can be uploaded by an I<sup>2</sup>C-bus write access to specific registers or in the pixel data input through the PD port. In the latter case, the 256 bytes defining the cursor bit map (2 bits per pixel) are expected immediately following the last RGB LUT data in the line preceding the first active line.

The cursor bit map is set up as follows: each pixel occupies 2 bits. The meaning of these bits depends on the CMODE I<sup>2</sup>C-bus register as described in Table 5. Transparent means that the input pixels are passed through, the 'cursor colours' can be programmed in separate registers.

The bit map is stored with 4 pixels per byte, aligned to the least significant bit. So the first pixel is in bits 0 and 1, the next pixel in bits 3 and 4 and so on. The first index is the column, followed by the row; index 0,0 is the upper left corner.

| Table 3         Layout of a byte in the cursor bit map |

|--------------------------------------------------------|

|--------------------------------------------------------|

| D7      | D6  | D5          | D4 | D3          | D2 | D1      | D0 |

|---------|-----|-------------|----|-------------|----|---------|----|

| pixel n | + 3 | pixel n + 2 |    | pixel n + 1 |    | pixel n |    |

| D1      | D0  | D1          | D0 | D1          | D0 | D1      | D0 |

For each direction, there are 2 registers controlling the position of the cursor, one controls the position of the 'hot spot', the other register controls the insertion position.

# SAA7104E; SAA7105E

The hot spot is the 'tip' of the pointer arrow. It can have any position in the bit map. The actual position registers describe the co-ordinates of the hot spot. Again 0,0 is the upper left corner. While it is not possible to move the hot spot beyond the left respectively upper screen border this is perfectly legal for the right respectively lower border. It should be noted that the cursor position is described relative to the input resolution.

| Table 4 | Cursor | bit | map |

|---------|--------|-----|-----|

|---------|--------|-----|-----|

| BYTE | D7                    | D6 | D5                    | D4 | D3                   | D2 | D1                   | D0 |

|------|-----------------------|----|-----------------------|----|----------------------|----|----------------------|----|

| 0    | row 0<br>column 3     |    | row 0<br>column 2     |    | row 0<br>column 1    |    | row 0<br>column 0    |    |

| 1    | row 0<br>colun        |    | row 0<br>column 6     |    | row 0<br>column 5    |    | row 0<br>column 4    |    |

| 2    | row 0<br>column<br>11 |    | row 0<br>column<br>10 |    | row 0<br>column 9    |    | row 0<br>column 8    |    |

|      |                       |    |                       |    |                      |    |                      |    |

| 6    | row 0<br>colun<br>27  |    | row (<br>colun<br>26  |    | row (<br>colun<br>25 |    | row 0<br>colun<br>24 |    |

| 7    | row 0<br>column<br>31 |    | row 0<br>colun<br>30  |    | row (<br>colun<br>29 |    | row 0<br>colun<br>28 |    |

|      |                       |    |                       |    |                      |    |                      |    |

| 254  | row 3<br>colun<br>27  | -  | row 3<br>colun<br>26  |    | row 3<br>colun<br>25 |    | row 3<br>colun<br>24 |    |

| 255  | row 3<br>colun<br>31  | -  | row 3<br>colun<br>30  |    | row 3<br>colun<br>29 | -  | row 3<br>colun<br>28 |    |

Table 5

Cursor modes

| CURSOR  | CURSOR MODE          |                            |  |  |

|---------|----------------------|----------------------------|--|--|

| PATTERN | CMODE = 0            | CMODE = 1                  |  |  |

| 00      | second cursor colour | second cursor colour       |  |  |

| 01      | first cursor colour  | first cursor colour        |  |  |

| 10      | transparent          | transparent                |  |  |

| 11      | inverted input       | auxiliary cursor<br>colour |  |  |

### 7.5 RGB Y-C<sub>B</sub>-C<sub>R</sub> matrix

RGB input signals to be encoded to PAL or NTSC are converted to the  $Y-C_B-C_R$  colour space in this block. The colour difference signals are fed through low-pass filters and formatted to a ITU-R BT.601 like 4 : 2 : 2 data stream for further processing.

A gain adjust option corrects the level swing of the graphics world (black-to-white as 0 to 255) to the required range of 16 to 235.

The matrix and formatting blocks can be bypassed for  $Y-C_B-C_R$  graphics input.

When the auxiliary VGA mode is selected, the output of the cursor insertion block is immediately directed to the triple DAC.

#### 7.6 Horizontal scaler

The high quality horizontal scaler operates on the 4 : 2 : 2 data stream. Its control engines compensate the colour phase offset automatically.

The scaler starts processing after a programmable horizontal offset and continues with a number of input pixels. Each input pixel is a programmable fraction of the current output pixel (XINC/4096). A special case is XINC = 0, this sets the scaling factor to 1.

If the SAA7104E; SAA7105E input data is in accordance with *"ITU-R BT.656"*, the scaler enters another mode. In this event, XINC needs to be set to 2048 for a scaling factor of 1. With higher values, upscaling will occur.

The phase resolution of the circuit is 12 bits, giving a maximum offset of 0.2 after 800 input pixels. Small FIFOs rearrange a 4:2:2 data stream at the scaler output.

#### 7.7 Vertical scaler and anti-flicker filter

The functions scaling, Anti-Flicker Filter (AFF) and re-interlacing are implemented in the vertical scaler.

Besides the entire input frame, it receives the first and last lines of the border to allow anti-flicker filtering.

The circuit generates the interlaced output fields by scaling down the input frames with different offsets for odd and even fields. Increasing the YSKIP setting reduces the anti-flicker function. A YSKIP value of 4095 switches it off; see Table 86.

An additional, programmable vertical filter supports the anti-flicker function. This filter is not available at upscaling factors of more than 2.

# SAA7104E; SAA7105E

The programming is similar to the horizontal scaler. For the re-interlacing, the resolutions of the offset registers are not sufficient, so the weighting factors for the first lines can also be adjusted. YINC = 0 sets the scaling factor to 1; YIWGTO and YIWGTE must not be 0.

Due to the re-interlacing, the circuit can perform upscaling by a maximum factor of 2. The maximum factor depends on the setting of the anti-flicker function and can be derived from the formulae given in Section 7.20.

An additional upscaling mode allows to increase the upscaling factor to maximum 4 as it is required for the old VGA modes like  $320 \times 240$ .

### 7.8 FIFO

The FIFO acts as a buffer to translate from the PIXCLK clock domain to the XTAL clock domain. The write clock is PIXCLK and the read clock is XTAL. An underflow or overflow condition can be detected via the I<sup>2</sup>C-bus read access.

In order to avoid underflows and overflows, it is essential that the frequency of the synthesized PIXCLK matches to the input graphics resolution and the desired scaling factor.

#### 7.9 Border generator

When the graphics picture is to be displayed as interlaced PAL, NTSC, S-video or RGB on a TV screen, it is desired in many cases not to lose picture information due to the inherent overscanning of a TV set. The desired amount of underscan area, which is achieved through appropriate scaling in the vertical and horizontal direction, can be filled in the border generator with an arbitrary true colour tint.

#### 7.10 Oscillator and Discrete Time Oscillator (DTO)

The master clock generation is realized as a 27 MHz crystal oscillator, which can operate with either a fundamental wave crystal or a 3rd-harmonic crystal.

The crystal clock supplies the DTO of the pixel clock synthesizer, the video encoder and the  $l^2$ C-bus control block. It also usually supplies the triple DAC, with the exception of the auxiliary VGA or HDTV mode, where the triple DAC is clocked by the pixel clock (PIXCLK).

The DTO can be programmed to synthesize all relevant pixel clock frequencies between circa 40 and 85 MHz. Two programmable dividers provide the actual clock to be used externally and internally. The dividers can be programmed to factors of 1, 2, 4 and 8. For the internal pixel clock, a divider ratio of 8 makes no sense and is thus forbidden.

SAA7104E; SAA7105E

The internal clock can be switched completely to the pixel clock input. In this event, the input FIFO is useless and will be bypassed.

The entire pixel clock generation can be locked to the vertical frequency. Both pixel clock dividers get re-initialized every field. Optionally, the DTO can be cleared with each V-sync. At proper programming, this will make the pixel clock frequency a precise multiple of the vertical and horizontal frequencies. This is required for some graphic controllers.

#### 7.11 Low-pass Clock Generation Circuit (CGC)

This block reduces the phase jitter of the synthesized pixel clock. It works as a tracking filter for all relevant synthesized pixel clock frequencies.

#### 7.12 Encoder

#### 7.12.1 VIDEO PATH

The encoder generates luminance and colour subcarrier output signals from the Y,  $C_B$  and  $C_R$  baseband signals, which are suitable for use as CVBS or separate Y and C signals.

Input to the encoder, at 27 MHz clock (e.g. DVD), is either originated from computer graphics at pixel clock, fed through the FIFO and border generator, or a ITU-R BT.656 style signal.

Luminance is modified in gain and in offset (the offset is programmable in a certain range to enable different black level set-ups). A blanking level can be set after insertion of a fixed synchronization pulse tip level, in accordance with standard composite synchronization schemes. Other manipulations used for the Macrovision anti-taping process, such as additional insertion of AGC super-white pulses (programmable in height), are supported by the SAA7104E only.

To enable easy analog post filtering, luminance is interpolated from a 13.5 MHz data rate to a 27 MHz data rate, thereby providing luminance in a 10-bit resolution. The transfer characteristics of the luminance interpolation filter are illustrated in Figs 6 and 7. Appropriate transients at start/end of active video and for synchronization pulses are ensured.

Chrominance is modified in gain (programmable separately for  $C_B$  and  $C_R$ ), and a standard dependent burst is inserted, before baseband colour signals are interpolated from a 6.75 MHz data rate to a 27 MHz data rate. One of the interpolation stages can be bypassed, thus providing a higher colour bandwidth, which can be used for the Y and C output.

The transfer characteristics of the chrominance interpolation filter are illustrated in Figs 4 and 5.

The amplitude (beginning and ending) of the inserted burst, is programmable in a certain range that is suitable for standard signals and for special effects. After the succeeding quadrature modulator, colour is provided on the subcarrier in 10-bit resolution.

The numeric ratio between the Y and C outputs is in accordance with the standards.

7.12.2 TELETEXT INSERTION AND ENCODING (NOT SIMULTANEOUSLY WITH REAL-TIME CONTROL)

Pin TTX\_SRES receives a WST or NABTS teletext bitstream sampled at the crystal clock. At each rising edge of the output signal (TTXRQ) a single teletext bit has to be provided after a programmable delay at input pin TTX\_SRES.

Phase variant interpolation is achieved on this bitstream in the internal teletext encoder, providing sufficient small phase jitter on the output text lines.

TTXRQ\_XCLKO2 provides a fully programmable request signal to the teletext source, indicating the insertion period of bitstream at lines which can be selected independently for both fields. The internal insertion window for text is set to 360 (PAL WST), 296 (NTSC WST) or 288 (NABTS) teletext bits including clock run-in bits. The protocol and timing are illustrated in Fig.14.

Alternatively, this pin can be provided with a buffered crystal clock (XCLK) of 13.5 MHz.

7.12.3 VIDEO PROGRAMMING SYSTEM (VPS) ENCODING

Five bytes of VPS information can be loaded via the  $I^2C$ -bus and will be encoded in the appropriate format into line 16.

#### 7.12.4 CLOSED CAPTION ENCODER

Using this circuit, data in accordance with the specification of Closed Caption or extended data service, delivered by the control interface, can be encoded (line 21). Two dedicated pairs of bytes (two bytes per field), each pair preceded by run-in clocks and framing code, are possible.

The actual line number in which data is to be encoded, can be modified in a certain range.

The data clock frequency is in accordance with the definition for NTSC M standard 32 times horizontal line frequency.

# SAA7104E; SAA7105E

Data LOW at the output of the DACs corresponds to 0 IRE, data HIGH at the output of the DACs corresponds to approximately 50 IRE.

It is also possible to encode Closed Caption data for 50 Hz field frequencies at 32 times the horizontal line frequency.

#### 7.12.5 ANTI-TAPING (SAA7104E ONLY)

For more information contact your nearest Philips Semiconductors sales office.

#### 7.13 RGB processor

This block contains a dematrix in order to produce RED, GREEN and BLUE signals to be fed to a SCART plug.

Before Y,  $C_B$  and  $C_R$  signals are de-matrixed, individual gain adjustment for Y and colour difference signals and 2 times oversampling for luminance and 4 times oversampling for colour difference signals is performed. The transfer curves of luminance and colour difference components of RGB are illustrated in Figs 8 and 9.

### 7.14 Triple DAC

Both Y and C signals are converted from digital-to-analog in a 10-bit resolution at the output of the video encoder. Y and C signals are also combined into a 10-bit CVBS signal.

The CVBS output signal occurs with the same processing delay as the Y, C and optional RGB or C<sub>R</sub>-Y-C<sub>B</sub> outputs. Absolute amplitude at the input of the DAC for CVBS is reduced by  $^{15}\!\!\!\!/_{16}$  with respect to Y and C DACs to make maximum use of the conversion ranges.

RED, GREEN and BLUE signals are also converted from digital-to-analog, each providing a 10-bit resolution.

The reference currents of all three DACs can be adjusted individually in order to adapt for different output signals. In addition, all reference currents can be adjusted commonly to compensate for small tolerances of the on-chip band gap reference voltage.

Alternatively, all currents can be switched off to reduce power dissipation.

All three outputs can be used to sense for an external load (usually 75  $\Omega$ ) during a pre-defined output. A flag in the I<sup>2</sup>C-bus status byte reflects whether a load is applied or not. In addition, an automatic sense mode can be activated which indicates a 75  $\Omega$  load at any of the three outputs at the dedicated interrupt pin TVD.

If the SAA7104E; SAA7105E is required to drive a second (auxiliary) VGA monitor or an HDTV set, the DACs receive the signal coming from the HD data path. In this event, the DACs are clocked at the incoming PIXCLKI instead of the 27 MHz crystal clock used in the video encoder.

### 7.15 HD data path

This data path allows the SAA7104E; SAA7105E to be used with VGA or HDTV monitors. It receives its data directly from the cursor generator and supports RGB and  $Y-P_B-P_R$  output formats (RGB not with  $Y-P_B-P_R$  input formats). No scaling is done in this mode.

A gain adjustment either leads the full level swing to the digital-to-analog converters or reduces the amplitude by a factor of 0.69. This enables sync pulses to be added to the signal as it is required for display units expecting signals with sync pulses, either regular or 3-level syncs.

### 7.16 Timing generator

The synchronization of the SAA7104E; SAA7105E is able to operate in two modes; slave mode and master mode.

In slave mode, the circuit accepts sync pulses on the bidirectional FSVGC (frame sync), VSVGC (vertical sync) and HSVGC (horizontal sync) pins: the polarities of the signals can be programmed. The frame sync signal is only necessary when the input signal is interlaced, in other cases it may be omitted. If the frame sync signal is present, it is possible to derive the vertical and the horizontal phase from it by setting the HFS and VFS bits. HSVGC and VSVGC are not necessary in this case, so it is possible to switch the pins to output mode.

Alternatively, the device can be triggered by auxiliary codes in a ITU-R BT.656 data stream via PD7 to PD0.

Only vertical frequencies of 50 and 60 Hz are allowed with the SAA7104E; SAA7105E. In slave mode, it is not possible to lock the encoders colour carrier to the line frequency with the PHRES bits.

In the (more common) master mode, the time base of the circuit is continuously free-running. The IC can output a frame sync at pin FSVGC, a vertical sync at pin VSVGC, a horizontal sync at pin HSVGC and a composite blanking signal at pin CBO. All of these signals are defined in the PIXCLK domain. The duration of HSVGC and VSVGC are fixed, they are 64 clocks for HSVGC and 1 line for VSVGC. The leading slopes are in phase and the polarities can be programmed.

# SAA7104E; SAA7105E

The input line length can be programmed. The field length is always derived from the field length of the encoder and the pixel clock frequency that is being used.

$\overline{\text{CBO}}$  acts as a data request signal. The circuit accepts input data at a programmable number of clocks after  $\overline{\text{CBO}}$ goes active. This signal is programmable and it is possible to adjust the following (see Figs 12 and 13):

- · The horizontal offset

- The length of the active part of the line

- The distance from active start to first expected data

- · The vertical offset separately for odd and even fields

- The number of lines per input field.

In most cases, the vertical offsets for odd and even fields are equal. If they are not, then the even field will start later. The SAA7104E; SAA7105E will also request the first input lines in the even field, the total number of requested lines will increase by the difference of the offsets.

As stated above, the circuit can be programmed to accept the look-up and cursor data in the first 2 lines of each field. The timing generator provides normal data request pulses for these lines; the duration is the same as for regular lines. The additional request pulses will be suppressed with LUTL set to logic 0; see Table 109. The other vertical timings do not change in this case, so the first active line can be number 2, counted from 0.

#### 7.17 Pattern generator for HD sync pulses

The pattern generator provides appropriate synchronization patterns for the video data path in auxiliary monitor or HDTV mode. It provides maximum flexibility in terms of raster generation for all interlaced and non-interlaced computer graphics or ATSC formats. The sync engine is capable of providing a combination of event-value pairs which can be used to insert certain values in the outgoing data stream at specified times. It can also be used to generate digital signals associated with time events. These can be used as digital horizontal and vertical synchronization signals on pins HSM\_CSYNC and VSM.

The picture position is adjustable through the programmable relationship between the sync pulses and the video contents.

The generation of embedded analog sync pulses is bound to a number of events which can be defined for a line. Several of these line timing definitions can exist in parallel. For the final sync raster composition a certain sequence of lines with different sync event properties has to be defined. The sequence specifies a series of line types and the number of occurrences of this specific line type. Once the sequence has been completed, it restarts from the beginning. All pulse shapes are filtered internally in order to avoid ringing after analog post filters.

The sequence of the generated pulse stream must fit precisely to the incoming data stream in terms of the total number of pixels per line and lines per frame.

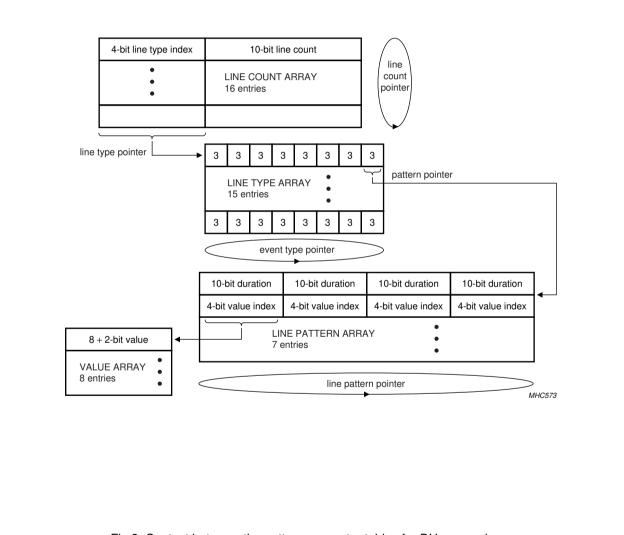

The sync engines flexibility is achieved by using a sequence of linked lists carrying the properties for the image, the lines as well as fractions of lines. Figure 3 illustrates the context between the various tables.

The first table serves as an array to hold the correct sequence of lines that compose the synchronization raster; it can contain up to 16 entries. Each entry holds a 4-bit index to the next table and a 10-bit counter value which specifies how often this particular line is invoked. If the necessary line count for a particular line exceeds the 10 bits, it has to use two table entries.

The 4-bit index in the line count array points to the line type array. It holds up to 15 entries (index 0 is not used), index 1 points to the first entry, index 2 to the second entry of the line type array etc.

Each entry of the line type array can hold up to 8 index pointers to another table. These indices point to portions of a line pulse pattern: A line could be split up e.g. into a sync, a blank, and an active portion followed by another blank portion, occupying four entries in one table line.

Each index of this table points to a particular line of the next table in the linked list. This table is called the line pattern array and each of the up to seven entries stores up to four pairs of a duration in pixel clock cycles and an index to a value table. The table entries are used to define portions of a line representing a certain value for a certain number of clock cycles.

The value specified in this table is actually another 3-bit index into a value array which can hold up to eight 8-bit values. If bit 4 (MSB) of the index is logic 1, the value is inserted into the G or Y signal, only; if bit 4 = 0, the associated value is inserted into all three signals.

Two additional bits of the entries in the value array (LSBs of the second byte) determine if the associated events appear as a digital pulse on the HSM\_CSYNC and/or VSM outputs.

SAA7104E; SAA7105E

Fig.3 Context between the pattern generator tables for DH sync pulses.

2004 Mar 04

\_

16

# SAA7104E; SAA7105E

To ease the trigger set-up for the sync generation module, a set of registers is provided to set up the screen raster which is defined as width and height. A trigger position can be specified as an x,y co-ordinate within the overall dimensions of the screen raster. If the x,y counter matches the specified co-ordinates, a trigger pulse is generated which pre-loads the tables with their initial values.

The listing in Table 6 outlines an example on how to set up the sync tables for a 1080i HD raster.

#### Important note:

Due to a problem in the programming interface, writing to the line pattern array (address D2) might destroy the data of the line type array (address D1). A work around is to write the line pattern array data before writing the line type array. Reading of the arrays is possible but all address pointers must be initialized before the next write operation.

| Table 6 | Example for set-up of the sync tables |

|---------|---------------------------------------|

|---------|---------------------------------------|

| SEQUENCE                | COMMENT                                                                                                                                               |  |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Write to subaddress D0H |                                                                                                                                                       |  |  |  |

| 00                      | points to first entry of line count array (index 0)                                                                                                   |  |  |  |

| 05 20                   | generate 5 lines of line type index 2 (this is the second entry of the line type array); will be the first vertical raster pulse                      |  |  |  |

| 01 40                   | generate 1 line of line type index 4; will be sync-black-sync-black sequence after the first vertical pulse                                           |  |  |  |

| 0E 60                   | generate 14 lines of line type index 6; will be the following lines with sync-black sequence                                                          |  |  |  |

| 1C 12                   | generate 540 lines of line type index 1; will be lines with sync and active video                                                                     |  |  |  |

| 02 60                   | generate 2 lines of line type index 6; will be the following lines with sync-black sequence                                                           |  |  |  |

| 01 50                   | generate 1 line of line type index 5; will be the following line (line 563) with sync-black-sync-black-null sequence (null is equivalent to sync tip) |  |  |  |

| 04 20                   | generate 4 lines of line type index 2; will be the second vertical raster pulse                                                                       |  |  |  |

| 01 30                   | generate 1 line of line type index 3; will be the following line with sync-null-sync-black sequence                                                   |  |  |  |

| 0F 60                   | generate 15 lines of line type index 6; will be the following lines with sync-black sequence                                                          |  |  |  |

| 1C 12                   | generate 540 lines of line type index 1; will be lines with sync and active video                                                                     |  |  |  |

| 02 60                   | generate 2 lines of line type index 6; will be the following lines with sync-black sequence; now, 1 125 lines are defined                             |  |  |  |

| Write to subaddress D2H | l (insertion is done into all three analog output signals)                                                                                            |  |  |  |

| 00                      | points to first entry of line pattern array (index 1)                                                                                                 |  |  |  |

| 6F 33 2B 30 00 00 00 00 | $880 \times \text{value}(3) + 44 \times \text{value}(3)$ ; (subtract 1 from real duration)                                                            |  |  |  |

| 6F 43 2B 30 00 00 00 00 | $880 \times value(4) + 44 \times value(3)$                                                                                                            |  |  |  |

| 3B 30 BF 03 BF 03 2B 30 | $60 \times \text{value}(3) + 960 \times \text{value}(0) + 960 \times \text{value}(0) + 44 \times \text{value}(3)$                                     |  |  |  |

| 2B 10 2B 20 57 30 00 00 | $44 \times value(1) + 44 \times value(2) + 88 \times value(3)$                                                                                        |  |  |  |

| 3B 30 BF 33 BF 33 2B 30 | $60 \times \text{value}(3) + 960 \times \text{value}(3) + 960 \times \text{value}(3) + 44 \times \text{value}(3)$                                     |  |  |  |

| Write to subaddress D1H |                                                                                                                                                       |  |  |  |

| 00                      | points to first entry of line type array (index 1)                                                                                                    |  |  |  |

| 34 00 00 00             | use pattern entries 4 and 3 in this sequence (for sync and active video)                                                                              |  |  |  |

| 24 24 00 00             | use pattern entries 4, 2, 4 and 2 in this sequence (for 2 × sync-black-null-black)                                                                    |  |  |  |

| 24 14 00 00             | use pattern entries 4, 2, 4 and 1 in this sequence (for sync-black-null-black-null)                                                                   |  |  |  |

| 14 14 00 00             | use pattern entries 4, 1, 4 and 1 in this sequence (for sync-black-sync-black)                                                                        |  |  |  |

# SAA7104E; SAA7105E

| SEQUENCE              | COMMENT                                                                             |  |

|-----------------------|-------------------------------------------------------------------------------------|--|

| 14 24 00 00           | use pattern entries 4, 1, 4 and 2 in this sequence (for sync-black-sync-black-null) |  |

| 54 00 00 00           | use pattern entries 4 and 5 in this sequence (for sync-black)                       |  |

| Write to subaddress D | 3H (no signals are directed to pins HSM_CSYNC and VSM)                              |  |

| 00                    | points to first entry of value array (index 0)                                      |  |

| CC 00                 | black level, to be added during active video                                        |  |

| 80 00                 | sync level LOW (minimum output voltage)                                             |  |

| 0A 00                 | sync level HIGH (3-level sync)                                                      |  |

| CC 00                 | black level (needed elsewhere)                                                      |  |

| 80 00                 | null (identical to sync level LOW)                                                  |  |

| Write to subaddress D | СН                                                                                  |  |

| 0B                    | insertion is active, gain for signal is adapted accordingly                         |  |

### 7.18 I<sup>2</sup>C-bus interface

The I<sup>2</sup>C-bus interface is a standard slave transceiver, supporting 7-bit slave addresses and 400 kbits/s guaranteed transfer rate. It uses 8-bit subaddressing with an auto-increment function. All registers are write and read, except two read only status bytes.

The register bit map consists of an RGB Look-Up Table (LUT), a cursor bit map and control registers. The LUT contains three banks of 256 bytes, where each RGB triplet is assigned to one address. Thus a write access needs the LUT address and three data bytes following subaddress FFH. For further write access auto-incrementing of the LUT address is performed. The cursor bit map access is similar to the LUT access but contains only a single byte per address.

The I<sup>2</sup>C-bus slave address is defined as 88H.

#### 7.19 Power-down modes

In order to reduce the power consumption, the SAA7104E; SAA7105E supports 2 power-down modes, accessible via the  $l^2$ C-bus. The analog power-down mode (DOWNA = 1) turns off the digital-to-analog converters and the pixel clock synthesizer. The digital power-down mode turns off all internal clocks and sets the digital outputs to LOW except the  $l^2$ C-bus interface. The IC keeps its programming and can still be accessed in this mode, however not all registers can be read or written to. Reading or writing to the look-up tables, the cursor and the HD sync generator require a valid pixel clock. The typical supply current in full power-down is approximately 5 mA. Because the analog power-down mode turns off the pixel clock synthesizer, there are limitations in some applications. If there is no pixel clock, the IC is not able to set its outputs to LOW. So, in most cases, DOWNA and DOWND should be set to logic 1 simultaneously. If the EIDIV bit is logic 1, it should be set to logic 0 before power-down.

#### 7.20 Programming the SAA7104E; SAA7105E

The SAA7104E; SAA7105E needs to provide a continuous data stream at its analog outputs as well as receive a continuous stream of data from its data source. Because there is no frame memory isolating the data streams, restrictions apply to the input frame timings.

Input and output processing of the SAA7104E; SAA7105E are only coupled through the vertical frequencies. In master mode, the encoder provides a vertical sync and an odd/even pulse to the input processing. In slave mode, the encoder receives them.

The parameters of the input field are mainly given by the memory capacity of the SAA7104E; SAA7105E. The rule is that the scaler and thus the input processing needs to provide the video data in the same time frames as the encoder reads them. Therefore, the vertical active video times (and the vertical frequencies) need to be the same.

The second rule is that there has to be data in the buffer FIFO when the encoder enters the active video area. Therefore, the vertical offset in the input path needs to be a bit shorter than the offset of the encoder.

The following Sections give the set of equations required to program the IC for the most common application: A post processor in master mode with non-interlaced video input data.

Some variables are defined below:

- InPix: the number of active pixels per input line

- InPpI: the length of the entire input line in pixel clocks

- InLin: the number of active lines per input field/frame

- TPclk: the pixel clock period

- RiePclk: the ratio of internal to external pixel clock

- OutPix: the number of active pixels per output line

- OutLin: the number of active lines per output field

- TXclk: the encoder clock period (37.037 ns).

#### 7.20.1 TV DISPLAY WINDOW

At 60 Hz, the first visible pixel has the index 256, 710 pixels can be encoded; at 50 Hz, the index is 284, 702 pixels can be visible.

The output lines should be centred on the screen. It should be noted that the encoder has 2 clocks per pixel; see Table 59.

$\begin{array}{l} \mathsf{ADWHS} = 256 + 710 - \mathsf{OutPix} \ (60 \ \mathsf{Hz});\\ \mathsf{ADWHS} = 284 + 702 - \mathsf{OutPix} \ (50 \ \mathsf{Hz});\\ \mathsf{ADWHE} = \mathsf{ADWHS} + \mathsf{OutPix} \times 2 \ (\mathsf{all frequencies}) \end{array}$

For vertical, the procedure is the same. At 60 Hz, the first line with video information is number 19, 240 lines can be active. For 50 Hz, the numbers are 23 and 287; see Table 65.

$$FAL = 19 + \frac{240 - OutLin}{2} (60 \text{ Hz});$$

$$FAL = 23 + \frac{287 - OutLin}{2} (50 \text{ Hz});$$

LAL = FAL + OutLin (all frequencies)

Most TV sets use overscan, and not all pixels respectively lines are visible. There is no standard for the factor, it is highly recommended to make the number of output pixels and lines adjustable. A reasonable underscan factor is 10%, giving approximately 640 output pixels per line.

#### 7.20.2 INPUT FRAME AND PIXEL CLOCK

The total number of pixel clocks per line and the input horizontal offset need to be chosen next. The only constraint is that the horizontal blanking has at least 10 clock pulses.

# SAA7104E; SAA7105E

The required pixel clock frequency can be determined in the following way: Due to the limited internal FIFO size, the input path has to provide all pixels in the same time frame as the encoders vertical active time. The scaler also has to process the first and last border lines for the anti-flicker function. Thus:

$$TPclk = \frac{262.5 \times 1716 \times TXclk}{InPpl \times integer\left(\frac{InLin + 2}{OutLin} \times 262.5\right)}$$

(60 Hz)

$$TPclk = \frac{312.5 \times 1728 \times TXclk}{InPpl \times integer\left(\frac{InLin + 2}{Outl in} \times 312.5\right)} (50 \text{ Hz})$$

and for the pixel clock generator

$\label{eq:PCL} \text{PCL} \; = \; \frac{\text{TXclk}}{\text{TPclk}} \times 2^{20 \, + \, \text{PCLE}} \; \; (\text{all frequencies});$

see Tables 68, 70 and 71. The divider PCLE should be set according to Table 70. PCLI may be set to a lower or the same value. Setting a lower value means that the internal pixel clock is higher and the data get sampled up. The difference may be 1 at  $640 \times 480$  pixels resolution and 2 at resolutions with 320 pixels per line as a rule of thumb. This allows horizontal upscaling by a maximum factor of 2 respectively 4 (this is the parameter RiePclk).

$$PCLI = PCLE - \frac{\log RiePclk}{\log 2}$$

(all frequencies)