# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**HD-CODEC**

Rev. 03 — 6 February 2007

### 1. General description

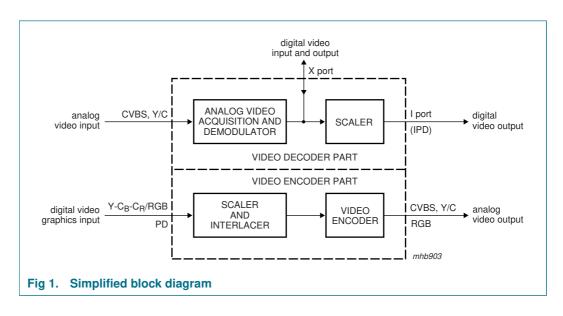

The SAA7108AE; SAA7109AE is a new multistandard video decoder and encoder chip, offering high quality video input and TV output processing as required by PC-99 specifications. It enables hardware manufacturers to implement versatile video functions on a significantly reduced printed-circuit board area at very competitive costs.

Separate pins for supply voltages as well as for I<sup>2</sup>C-bus control and boundary scan test have been provided for the video encoder and decoder sections to ensure both flexible handling and optimized noise behavior.

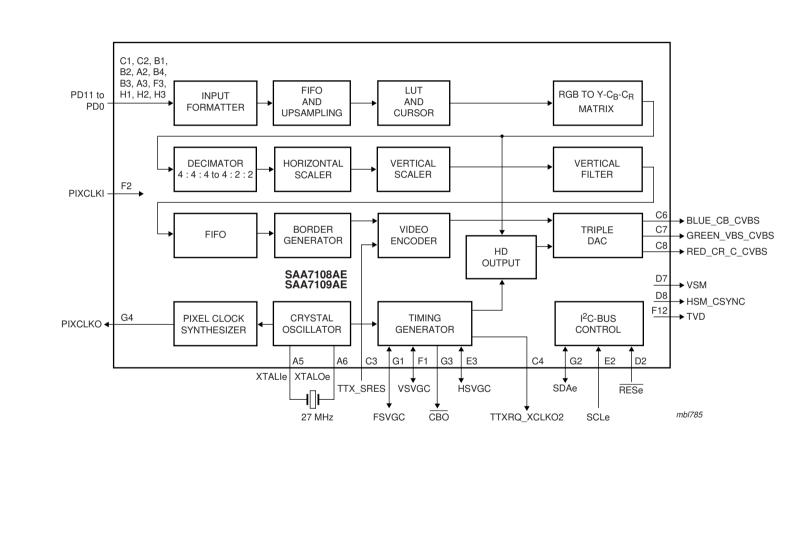

The **video encoder** is used to encode PC graphics data at maximum  $1280 \times 1024$  resolution (optionally  $1920 \times 1080$  interlaced) to PAL (50 Hz) or NTSC (60 Hz) video signals. A programmable scaler and anti-flicker filter (maximum 5 lines) ensures properly sized and flicker-free TV display as CVBS or S-video output.

Alternatively, the three Digital-to-Analog Converters (DACs) can output RGB signals together with a TTL composite sync to feed SCART connectors.

When the scaler/interlacer is bypassed, a second VGA monitor can be connected to the RGB outputs and separate H and V-syncs as well, thereby serving as an auxiliary monitor at maximum  $1280 \times 1024$  resolution/60 Hz (PIXCLK < 85 MHz). Alternatively this port can provide Y, P<sub>B</sub> and P<sub>R</sub> signals for HDTV monitors.

The encoder section includes a sync/clock generator and on-chip DACs.

All inputs intended to interface to the host graphics controller are designed for low-voltage signals down to 1.1 V and up to 3.45 V.

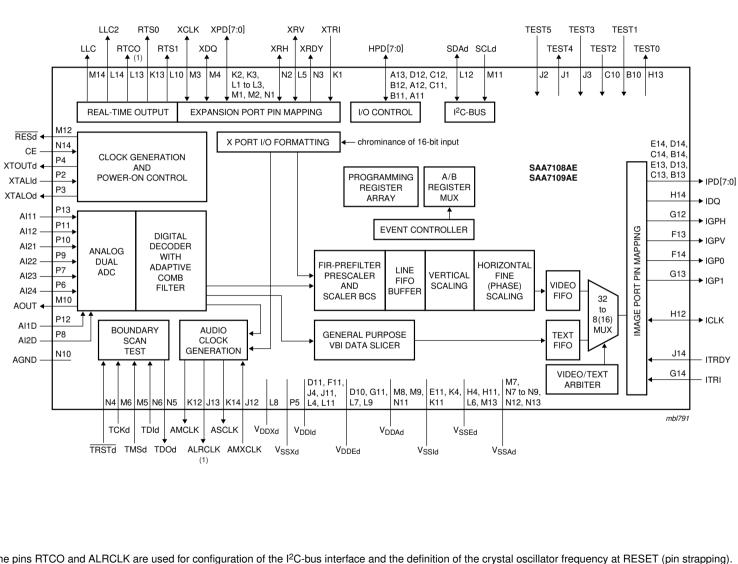

The **video decoder**, a 9-bit video input processor, is a combination of a 2-channel analog pre-processing circuit including source selection, anti-aliasing filter and Analog-to-Digital Converter (ADC), automatic clamp and gain control, a Clock Generation Circuit (CGC), and a digital multistandard decoder (PAL BGHI, PAL M, PAL N, combination PAL N, NTSC M, NTSC M, NTSC N, NTSC 4.43 and SECAM).

The decoder includes a brightness, contrast and saturation control circuit, a multistandard VBI data slicer and a 27 MHz VBI data bypass. The pure 3.3 V (5 V compatible) CMOS circuit SAA7108AE; SAA7109AE, consisting of an analog front-end and digital video decoder, a digital video encoder and analog back-end, is a highly integrated circuit especially designed for desktop video applications.

The decoder is based on the principle of line-locked clock decoding and is able to decode the color of PAL, SECAM and NTSC signals into ITU-R BT.601 compatible color component values.

The encoder can operate fully independently at its own variable pixel clock, transporting graphics input data, and at the line-locked, single crystal-stable video encoding clock.

As an option, it is possible to slave the video PAL/NTSC encoding to the video decoder clock with the encoder FIFO acting as a buffer to decouple the line-locked decoder clock from the crystal-stable encoder clock.

### 2. Features

### 2.1 Video decoder

- Six analog inputs, internal analog source selectors, e.g. 6 × CVBS or (2 × Y/C and 2 × CVBS) or (1 × Y/C and 4 × CVBS)

- Two analog preprocessing channels in differential CMOS style for best S/N performance

- Fully programmable static gain or Automatic Gain Control (AGC) for the selected CVBS or Y/C channel

- Switchable white peak control

- Two built-in analog anti-aliasing filters

- Two 9-bit video CMOS Analog-to-Digital Converters (ADCs), digitized CVBS or Y/C signals are available on the Image Port Data (IPD) port under I<sup>2</sup>C-bus control

- On-chip clock generator

- Line-locked system clock frequencies

- Digital PLL for horizontal sync processing and clock generation, horizontal and vertical sync detection

- Requires only one crystal (either 24.576 MHz or 32.11 MHz) for all standards

- Automatic detection of 50 Hz and 60 Hz field frequency, and automatic switching between PAL and NTSC standards

- Luminance and chrominance signal processing for PAL BGHI, PAL N, combination PAL N, PAL M, NTSC M, NTSC-Japan, NTSC N, NTSC 4.43 and SECAM

- User programmable luminance peaking or aperture correction

- Cross-color reduction for NTSC by chrominance comb filtering

- PAL delay line for correcting PAL phase errors

- Brightness Contrast Saturation (BCS) and hue control on-chip

- Two multifunctional real-time output pins controlled by the I<sup>2</sup>C-bus

- Multistandard VBI data slicer decoding World Standard Teletext (WST), North-American Broadcast Text System (NABTS), Closed Caption (CC), Wide Screen Signalling (WSS), Video Programming System (VPS), Vertical Interval Time Code (VITC) variants (EBU/SMPTE) etc.

- Standard ITU 656 Y-C<sub>B</sub>-C<sub>R</sub> 4 : 2 : 2 format (8-bit) on IPD output bus

- Enhanced ITU 656 output format on IPD output bus containing:

- Active video

- Raw CVBS data for INTERCAST applications (27 MHz data rate)

- Decoded VBI data

- Detection of copy protected input signals according to the Macrovision standard. Can be used to prevent unauthorized recording of pay-TV or video tape signals

### 2.2 Video scaler

- Both up and downscaling

- Conversion to square pixel format

- NTSC to 288 lines (video phone)

- Phase accuracy better than <sup>1</sup>/<sub>64</sub> pixel or line, horizontally or vertically

- Independent scaling definitions for odd and even fields

- Anti-alias filter for horizontal scaling

- Provides output as:

- Scaled active video

- Raw CVBS data for INTERCAST, WAVE-PHORE, POPCON applications or general VBI data decoding (27 MHz or sample rate converted)

- Local video output for Y-C<sub>B</sub>-C<sub>R</sub> 4 : 2 : 2 format (VMI, VIP and ZV)

### 2.3 Video encoder

- Digital PAL/NTSC encoder with integrated high quality scaler and anti-flicker filter for TV output from a PC

- Supports Intel Digital Video Out (DVO) low-voltage interfacing to graphics controller

- 27 MHz crystal-stable subcarrier generation

- Maximum graphics pixel clock 85 MHz at double edged clocking, synthesized on-chip or from external source

- Programmable assignment of clock edge to bytes (in double edged mode)

- Synthesizable pixel clock (PIXCLK) with minimized output jitter, can be used as reference clock for the VGC, as well

- PIXCLK output and bi-phase PIXCLK input (VGC clock loop-through possible)

- Hot-plug detection through dedicated interrupt pin

- Supported VGA resolutions for PAL or NTSC legacy video output up to 1280 × 1024 graphics data at 60 Hz or 50 Hz frame rate

- Supported VGA resolutions for HDTV output up to 1920 × 1080 interlaced graphics data at 60 Hz or 50 Hz frame rate

- Three Digital-to-Analog Converters (DACs) for CVBS (BLUE, C<sub>B</sub>), VBS (GREEN, CVBS) and C (RED, C<sub>R</sub>) at 27 MHz sample rate (signals in parenthesis are optionally selected), all at 10-bit resolution

- Non-interlaced C<sub>B</sub>-Y-C<sub>R</sub> or RGB input at maximum 4 : 4 : 4 sampling

- Downscaling and upscaling from 50 % to 400 %

- Optional interlaced C<sub>B</sub>-Y-C<sub>R</sub> input of Digital Versatile Disk (DVD) signals

- Optional non-interlaced RGB output to drive second VGA monitor (bypass mode, maximum 85 MHz)

- 3 × 256 bytes RGB Look-Up Table (LUT)

- Support for hardware cursor

- HDTV up to 1920 × 1080 interlaced and 1280 × 720 progressive, including 3-level sync pulses

- Programmable border color of underscan area

- Programmable 5-line anti-flicker filter

- On-chip 27 MHz crystal oscillator (3rd harmonic or fundamental 27 MHz crystal)

- Fast I<sup>2</sup>C-bus control port (400 kHz)

**HD-CODEC**

- Encoder can be master or slave

- Adjustable output levels for the DACs

- Programmable horizontal and vertical input synchronization phase

- Programmable horizontal sync output phase

- Internal Color Bar Generator (CBG)

- Optional support of various Vertical Blanking Interval (VBI) data insertion

- Macrovision Pay-per-View copy protection system rev. 7.01, rev. 6.1 and rev. 1.03 (525p) as option; this applies to the SAA7108AE only.

### 2.4 Common features

- 5 V tolerant digital inputs and I/O ports

- I<sup>2</sup>C-bus controlled (full read-back ability by an external controller, bit rate up to 400 kbit/s)

- Versatile Power-save modes

- Boundary scan test circuit complies with the "IEEE Std. 1149.b1-1994" (separate ID codes for decoder and encoder)

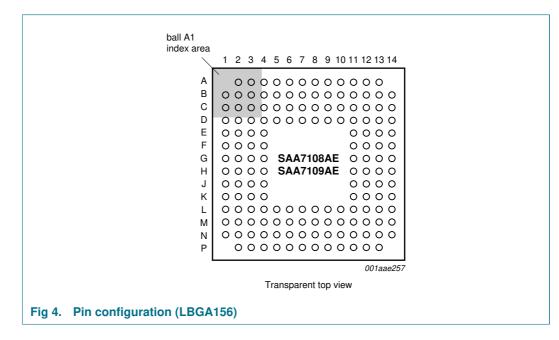

- LBGA156 package

- Moisture Sensitive Level (MSL): e3

### 3. Applications

- Notebook (low-power consumption)

- PCMCIA card application

- AGP based graphics cards

- PC editing

- Image processing

- Video phone applications

- INTERCAST and PC teletext applications

- Security applications

- Hybrid satellite set-top boxes

### 4. Quick reference data

| Table 1.         | Quick reference data                 |            |            |      |     |      |      |

|------------------|--------------------------------------|------------|------------|------|-----|------|------|

| Symbol           | Parameter                            | Conditions |            | Min  | Тур | Max  | Unit |

| $V_{\text{DDD}}$ | digital supply voltage               |            |            | 3.15 | 3.3 | 3.45 | V    |

| $V_{DDA}$        | analog supply voltage                |            |            | 3.15 | 3.3 | 3.45 | V    |

| T <sub>amb</sub> | ambient temperature                  |            |            | 0    | -   | 70   | °C   |

| $P_{A+D}$        | analog and digital power dissipation |            | <u>[1]</u> | -    | -   | 1.7  | W    |

[1] Power dissipation is extremely dependent on programming and selected application.

**HD-CODEC**

### 5. Ordering information

| Table 2. Ordering information |         |                                                         |          |  |  |  |  |

|-------------------------------|---------|---------------------------------------------------------|----------|--|--|--|--|

| Туре                          | Package |                                                         |          |  |  |  |  |

| number                        | Name    | Description                                             | Version  |  |  |  |  |

| SAA7108AE                     | LBGA156 | plastic low profile ball grid array package; 156 balls; | SOT700-1 |  |  |  |  |

| SAA7109AE                     |         | body $15 \times 15 \times 1.05$ mm                      |          |  |  |  |  |

### 6. Block diagram

SAA7108AE\_SAA7109AE\_3

Product data sheet

Rev. 03

L

6 February 2007

NXP Semiconductors

SAA7108AE; SAA7109AE

HD-CODEC

Fig 2. Block diagram (video encoder part)

© NXP B.V. 2007. All rights reserved. 6 of 208

SAA7108AE\_SAA7109AE\_3 Product data sheet

Rev. ິ 6 February 2007

> © NXP B.V. 2007. All rights re 1 of 208

Fig 3. Block diagram (video decoder part)

(1) The pins RTCO and ALRCLK are used for configuration of the I<sup>2</sup>C-bus interface and the definition of the crystal oscillator frequency at RESET (pin strapping).

NXP Semiconductors

S **AA7108AE;** ິ **AA7109AE**

HD-CODEC

**HD-CODEC**

### 7. Pinning information

### 7.1 Pinning

SAA7108AE\_SAA7109AE\_3

Product data sheet

| А |       | PD7     | PD4          | TRSTe                | XTALle            | XTALOe            | DUMP               |

|---|-------|---------|--------------|----------------------|-------------------|-------------------|--------------------|

| В | PD9   | PD8     | PD5          | PD6                  | TDle              | V <sub>DDAe</sub> | DUMP               |

| С | PD11  | PD10    | TTX_<br>SRES | TTXRQ_<br>XCLKO2     | V <sub>SSle</sub> | BLUE_<br>CB_CVBS  | GREEN_<br>VBS_CVBS |

| D | TDOe  | RESe    | TMSe         | V <sub>DDIEe</sub>   | V <sub>SSle</sub> | V <sub>DDXe</sub> | VSM                |

| E | TCKe  | SCLe    | HSVGC        | V <sub>SSEe</sub>    |                   |                   |                    |

| F | VSVGC | PIXCLKI | PD3          | V <sub>DD(DVO)</sub> |                   |                   |                    |

| G | FSVGC | SDAe    | CBO          | PIXCLKO              |                   |                   |                    |

| н | PD2   | PD1     | PD0          | V <sub>SSEd</sub>    |                   |                   |                    |

| J | TEST4 | TEST5   | TEST3        | V <sub>DDld</sub>    |                   |                   |                    |

| к | XTRI  | XPD7    | XPD6         | V <sub>SSId</sub>    |                   |                   |                    |

| L | XPD5  | XPD4    | XPD3         | V <sub>DDld</sub>    | XRV               | V <sub>SSEd</sub> | V <sub>DDEd</sub>  |

| М | XPD2  | XPD1    | XCLK         | XDQ                  | TMSd              | TCKd              | V <sub>SSAd</sub>  |

| Ν | XPD0  | XRH     | XRDY         | TRSTd                | TDOd              | TDId              | V <sub>SSAd</sub>  |

XTALOd

XTOUTd

V<sub>SSXd</sub>

3

5

4

6

AI24

7

8

V<sub>SSXe</sub>

V<sub>SSAe</sub>

RED\_CR\_ C\_CVBS

HSM\_CSYNC

V<sub>DDXd</sub>

$V_{DDAd}$

V<sub>SSAd</sub>

AI2D

9

RSET

V<sub>DDAe</sub>

VDDAe

V<sub>DDAe</sub>

V<sub>DDEd</sub>

V<sub>DDAd</sub>

V<sub>SSAd</sub>

AI22

10

V<sub>DDAe</sub>

TEST1

TEST2

$V_{\mathsf{DDEd}}$

RTS1

AOUT

AGND

AI21

11

HPD0

HPD1

HPD2

V<sub>DDId</sub>

V<sub>SSId</sub>

V<sub>DDId</sub>

V<sub>SSEd</sub>

V<sub>DDId</sub>

V<sub>DDId</sub>

SCLd

$V_{\mathsf{DDAd}}$

AI12

12

HPD3

HPD4

HPD5

HPD6

n.c. TVD

IGPH

ICLK

AMXCLK

AMCLK

SDAd

RESd

V<sub>SSAd</sub>

AI1D

2

XTALId

Fig 5. Pin configuration (LBGA156 top view)

Р

1

© NXP B.V. 2007. All rights reserved. 9 of 208

Rev. 03 — 6 February 2007

AI23

| NXP            |

|----------------|

| Semiconductors |

|                |

14

IPD4

IPD5

IPD6

IPD7

IGP0

ITRI

IDQ

ITRDY

ASCLK

LLC2

LLC

CE

001aaf638

13

HPD7

IPD0

IPD1

IPD2

IPD3

IGPV

IGP1

TEST0

ALRCLK

RTS0

RTCO

VSSEd

VSSAd

AI11

SAA7108AE; SAA7109AE

HD-CODEC

| Pin | Symbol            | Pin | Symbol            | Pin | Symbol            | Pin      | Symbol               |

|-----|-------------------|-----|-------------------|-----|-------------------|----------|----------------------|

| A2  | PD7               | A3  | PD4               | A4  | TRSTe             | A5       | XTALIe               |

| A6  | XTALOe            | A7  | DUMP              | A8  | V <sub>SSXe</sub> | A9       | RSET                 |

| A10 | V <sub>DDAe</sub> | A11 | HPD0              | A12 | HPD3              | A13      | HPD7                 |

| B1  | PD9               | B2  | PD8               | B3  | PD5               | B4       | PD6                  |

| B5  | TDIe              | B6  | V <sub>DDAe</sub> | B7  | DUMP              | B8       | V <sub>SSAe</sub>    |

| B9  | V <sub>DDAe</sub> | B10 | TEST1             | B11 | HPD1              | B12      | HPD4                 |

| B13 | IPD0              | B14 | IPD4              |     |                   |          |                      |

| C1  | PD11              | C2  | PD10              | C3  | TTX_SRES          | C4       | TTXRQ_XCLKO2         |

| C5  | V <sub>SSIe</sub> | C6  | BLUE_CB_CVBS      | C7  | GREEN_VBS_CVBS    | C8       | RED_CR_C_CVBS        |

| C9  | V <sub>DDAe</sub> | C10 | TEST2             | C11 | HPD2              | C12      | HPD5                 |

| C13 | IPD1              | C14 | IPD5              |     |                   |          |                      |

| D1  | TDOe              | D2  | RESe              | D3  | TMSe              | D4       | V <sub>DDIEe</sub>   |

| D5  | V <sub>SSIe</sub> | D6  | V <sub>DDXe</sub> | D7  | VSM               | D8       | HSM_CSYNC            |

| D9  | V <sub>DDAe</sub> | D10 | V <sub>DDEd</sub> | D11 | V <sub>DDId</sub> | D12      | HPD6                 |

| D13 | IPD2              | D14 | IPD6              |     |                   |          |                      |

| E1  | TCKe              | E2  | SCLe              | E3  | HSVGC             | E4       | V <sub>SSEe</sub>    |

| E11 | V <sub>SSId</sub> | E12 | n.c.              | E13 | IPD3              | E14      | IPD7                 |

| F1  | VSVGC             | F2  | PIXCLKI           | F3  | PD3               | F4       | V <sub>DD(DVO)</sub> |

| F11 | V <sub>DDId</sub> | F12 | TVD               | F13 | IGPV              | F14      | IGP0                 |

| G1  | FSVGC             | G2  | SDAe              | G3  | CBO               | G4       | PIXCLKO              |

| G11 | V <sub>DDEd</sub> | G12 | IGPH              | G13 | IGP1              | G14      | ITRI                 |

| H1  | PD2               | H2  | PD1               | H3  | PD0               | H4       | V <sub>SSEd</sub>    |

| H11 | V <sub>SSEd</sub> | H12 | ICLK              | H13 | TEST0             | H14      | IDQ                  |

| J1  | TEST4             | J2  | TEST5             | J3  | TEST3             | J4       | V <sub>DDId</sub>    |

| J11 | V <sub>DDId</sub> | J12 | AMXCLK            | J13 | ALRCLK            | J14      | ITRDY                |

| K1  | XTRI              | K2  | XPD7              | К3  | XPD6              | K4       | V <sub>SSId</sub>    |

| K11 | V <sub>SSId</sub> | K12 | AMCLK             | K13 | RTS0              | K14      | ASCLK                |

| L1  | XPD5              | L2  | XPD4              | L3  | XPD3              | L4       | V <sub>DDId</sub>    |

| L5  | XRV               | L6  | V <sub>SSEd</sub> | L7  | V <sub>DDEd</sub> | L8       | V <sub>DDXd</sub>    |

| L9  | V <sub>DDEd</sub> | L10 | RTS1              | L11 | V <sub>DDId</sub> | L12      | SDAd                 |

| L13 | RTCO              | L14 | LLC2              |     |                   |          |                      |

| M1  | XPD2              | M2  | XPD1              | MЗ  | XCLK              | M4       | XDQ                  |

| M5  | TMSd              | M6  | TCKd              | M7  | V <sub>SSAd</sub> | M8       | V <sub>DDAd</sub>    |

| M9  | V <sub>DDAd</sub> | M10 | AOUT              | M11 | SCLd              | M12      | RESd                 |

| M13 | V <sub>SSEd</sub> | M14 | LLC               |     |                   |          |                      |

| N1  | XPD0              | N2  | XRH               | N3  | XRDY              | N4       | TRSTd                |

| N5  | TDOd              | N6  | TDId              | N7  | V <sub>SSAd</sub> | N8       | V <sub>SSAd</sub>    |

| N9  | V <sub>SSAd</sub> | N10 | AGND              | N11 | V <sub>DDAd</sub> | N12      | V <sub>SSAd</sub>    |

| N13 | V <sub>SSAd</sub> | N14 | CE                |     |                   | <u>-</u> | JOAU                 |

HD-CODEC

| Table 3.         Pin allocation tablecontinued |        |     |        |     |        |     |                   |  |

|------------------------------------------------|--------|-----|--------|-----|--------|-----|-------------------|--|

| Pin                                            | Symbol | Pin | Symbol | Pin | Symbol | Pin | Symbol            |  |

| P2                                             | XTALId | P3  | XTALOd | P4  | XTOUTd | P5  | V <sub>SSXd</sub> |  |

| P6                                             | AI24   | P7  | AI23   | P8  | AI2D   | P9  | AI22              |  |

| P10                                            | AI21   | P11 | Al12   | P12 | AI1D   | P13 | Al11              |  |

### 7.2 Pin description

| Table 4.          | Pin descrip |             | - 141               |                                                                                                                                                                 |

|-------------------|-------------|-------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            |             | Pin         | Type <sup>[1]</sup> | Description                                                                                                                                                     |

| PD7               | A           | 42          | I                   | MSB of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; see <u>Table 12</u> to <u>Table 18</u> for pin assignment                                              |

| PD4               | Δ           | 43          | I                   | MSB – 3 of encoder input bus with CB-Y-CR 4 : 2 : 2; see Table 12 to Table 18 for pin assignment                                                                |

| TRSTe             | Ą           | <b>\</b> 4  | l/pu                | test reset input for Boundary Scan Test (BST) (encoder); active LOW; with internal pull-up <sup>[2][3]</sup>                                                    |

| XTALle            | A           | <b>\</b> 5  | I                   | 27 MHz crystal input (encoder)                                                                                                                                  |

| XTALOe            | A           | <b>\</b> 6  | 0                   | 27 MHz crystal output (encoder)                                                                                                                                 |

| DUMP              | Α           | 47          | 0                   | DAC reference pin (encoder); 12 $\Omega$ resistor connected to $V_{SSAe}$                                                                                       |

| V <sub>SSXe</sub> | A           | 48          | S                   | ground for oscillator (encoder)                                                                                                                                 |

| RSET              | Α           | 49          | 0                   | DAC reference pin (encoder); 1 $k\Omega$ resistor connected to $V_{SSAe}$                                                                                       |

| V <sub>DDAe</sub> | Α           | <b>\10</b>  | S                   | 3.3 V analog supply voltage (encoder)                                                                                                                           |

| HPD0              | Α           | <b>\</b> 11 | I/O                 | MSB – 7 of Host Port Data (HPD) output bus                                                                                                                      |

| HPD3              | Α           | A12         | I/O                 | MSB – 4 of HPD output bus                                                                                                                                       |

| HPD7              | Α           | <b>\</b> 13 | I/O                 | MSB of HPD output bus                                                                                                                                           |

| PD9               | E           | 31          | I                   | see <u>Table 12</u> , <u>Table 17</u> and <u>Table 18</u> for pin assignment with different encoder input formats                                               |

| PD8               | E           | 32          | I                   | see <u>Table 12</u> , <u>Table 17</u> and <u>Table 18</u> for pin assignment with different encoder input formats                                               |

| PD5               | E           | 33          | I                   | $MSB-2$ of encoder input bus with $C_B\mbox{-}Y\mbox{-}C_R\mbox{-}4:2:2;$ see $\underline{\mbox{Table 12}}$ to $\underline{\mbox{Table 18}}$ for pin assignment |

| PD6               | E           | 34          | I                   | $MSB-1$ of encoder input bus with $C_B\mbox{-}Y\mbox{-}C_R\mbox{-}4$ : 2 : 2; see Table 12 to Table 18 for pin assignment                                       |

| TDle              | E           | 35          | l/pu                | test data input for BST (encoder) <sup>[4]</sup>                                                                                                                |

| V <sub>DDAe</sub> | E           | 36          | S                   | 3.3 V analog supply voltage (encoder)                                                                                                                           |

| DUMP              | E           | 37          | 0                   | DAC reference pin (encoder); connected to A7                                                                                                                    |

| V <sub>SSAe</sub> | E           | 38          | S                   | analog ground (encoder)                                                                                                                                         |

| V <sub>DDAe</sub> | E           | 39          | S                   | 3.3 V analog supply voltage (encoder)                                                                                                                           |

| TEST1             | E           | 310         | I                   | scan test input 1; do not connect                                                                                                                               |

| HPD1              | E           | 311         | I/O                 | MSB – 6 of HPD output bus                                                                                                                                       |

| HPD4              | E           | 312         | I/O                 | MSB – 3 of HPD output bus                                                                                                                                       |

| IPD0              | E           | 313         | 0                   | MSB – 7 of IPD output bus                                                                                                                                       |

| IPD4              | E           | 314         | 0                   | MSB – 3 of Image Port Data (IPD) output bus                                                                                                                     |

| PD11              | C           | C1          | I                   | see <u>Table 12</u> , <u>Table 17</u> and <u>Table 18</u> for pin assignment with different encoder input formats                                               |

### **NXP Semiconductors**

# SAA7108AE; SAA7109AE

HD-CODEC

| Symbol             | Pin | Type <sup>[1]</sup> | Description                                                                                      |

|--------------------|-----|---------------------|--------------------------------------------------------------------------------------------------|

| PD10               | C2  | I                   | see Table 12, Table 17 and Table 18 for pin assignment with different encoder input formats      |

| TTX_SRES           | C3  | I                   | teletext input or sync reset input (encoder)                                                     |

| TTXRQ_XCLKO2       | C4  | 0                   | teletext request output or 13.5 MHz clock output of the crystal oscillator (encoder)             |

| V <sub>SSIe</sub>  | C5  | S                   | digital ground core (encoder)                                                                    |

| BLUE_CB_CVBS       | C6  | 0                   | BLUE or C <sub>B</sub> or CVBS output                                                            |

| GREEN_VBS_CVBS     | C7  | 0                   | GREEN or VBS or CVBS output                                                                      |

| RED_CR_C_CVBS      | C8  | 0                   | RED or C <sub>R</sub> or C or CVBS output                                                        |

| V <sub>DDAe</sub>  | C9  | S                   | 3.3 V analog supply voltage (encoder)                                                            |

| TEST2              | C10 | I                   | scan test input 2; do not connect                                                                |

| HPD2               | C11 | I/O                 | MSB – 5 of HPD output bus                                                                        |

| HPD5               | C12 | I/O                 | MSB – 2 of HPD output bus                                                                        |

| IPD1               | C13 | 0                   | MSB – 6 of IPD output bus                                                                        |

| IPD5               | C14 | 0                   | MSB – 2 of IPD output bus                                                                        |

| TDOe               | D1  | 0                   | test data output for BST (encoder) <sup>[4]</sup>                                                |

| RESe               | D2  | I                   | reset input (encoder); active LOW                                                                |

| TMSe               | D3  | l/pu                | test mode select input for BST (encoder) <sup>[4]</sup>                                          |

| V <sub>DDIEe</sub> | D4  | S                   | 3.3 V digital supply voltage for core and peripheral cells (encoder)                             |

| V <sub>SSIe</sub>  | D5  | S                   | digital ground core (encoder)                                                                    |

| V <sub>DDXe</sub>  | D6  | S                   | 3.3 V supply voltage for oscillator (encoder)                                                    |

| VSM                | D7  | 0                   | vertical synchronization output to VGA monitor (non-interlaced)                                  |

| HSM_CSYNC          | D8  | 0                   | horizontal synchronization output to VGA monitor (non-interlaced) or composit sync for RGB-SCART |

| V <sub>DDAe</sub>  | D9  | S                   | 3.3 V analog supply voltage (encoder)                                                            |

| V <sub>DDEd</sub>  | D10 | S                   | 3.3 V digital supply voltage for peripheral cells (decoder)                                      |

| V <sub>DDId</sub>  | D11 | S                   | 3.3 V digital supply voltage for core (decoder)                                                  |

| HPD6               | D12 | I/O                 | MSB – 1 of HPD output bus                                                                        |

| IPD2               | D13 | 0                   | MSB – 5 of IPD output bus                                                                        |

| IPD6               | D14 | 0                   | MSB – 1 of IPD output bus                                                                        |

| TCKe               | E1  | l/pu                | test clock input for BST (encoder) <sup>[4]</sup>                                                |

| SCLe               | E2  | I(/O)               | serial clock input (I <sup>2</sup> C-bus encoder) with inactive output path                      |

| HSVGC              | E3  | I/O                 | horizontal synchronization output to Video Graphics Controller (VGC) (optiona input)             |

| V <sub>SSEe</sub>  | E4  | S                   | digital ground peripheral cells (encoder)                                                        |

| V <sub>SSId</sub>  | E11 | S                   | digital ground core (decoder)                                                                    |

| n.c.               | E12 | -                   | not connected                                                                                    |

| IPD3               | E13 | 0                   | MSB – 4 of IPD output bus                                                                        |

| IPD7               | E14 | 0                   | MSB of IPD output bus                                                                            |

| VSVGC              | F1  | I/O                 | vertical synchronization output to VGC (optional input)                                          |

| PIXCLKI            | F2  | I                   | pixel clock input (looped through)                                                               |

SAA7108AE\_SAA7109AE\_3

Product data sheet

### **NXP Semiconductors**

# SAA7108AE; SAA7109AE

HD-CODEC

| PD3F3IMSB – 4 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; set<br>pin assignment $V_{DD(DVO)}$ F4Sdigital supply voltage for DVO cells $V_{DDId}$ F11S3.3 V digital supply voltage for core (decoder)TVDF12OTV detector; hot-plug interrupt pin; HIGH if TV is connIGPVF13Omulti-purpose vertical reference output with IPD outputIGP0F14Ogeneral purpose output signal 0 with IPD output busFSVGCG1I/Oframe synchronization output to VGC (optional input)SDAeG2I/Oserial data input/output (I²C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decodeIGPHG12Omulti-purpose horizontal reference output with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; set<br>pin assignmentPD1H2IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; set<br>pin assignmentVSEdH4Sdigital ground for peripheral cells (decoder)VssEdH11Sdigital ground for peripheral cells (decoder)VssEdH1IOscan test output; do not connectIDQH13Oscan test output; do not connectIDQH14O <td< th=""><th>ected<br/>t bus<br/>er)<br/>tput bus</th></td<> | ected<br>t bus<br>er)<br>tput bus        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| VDDIdF11S3.3 V digital supply voltage for core (decoder)TVDF12OTV detector; hot-plug interrupt pin; HIGH if TV is connIGPVF13Omulti-purpose vertical reference output with IPD outpuIGP0F14Ogeneral purpose output signal 0 with IPD output busFSVGCG1I/Oframe synchronization output to VGC (optional input)SDAeG2I/Oserial data input/output (I <sup>2</sup> C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decodeIGPHG12Omulti-purpose horizontal reference output with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD1H2IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test                              | t bus<br>er)<br>tput bus                 |

| TVDF12OTV detector; htt-plug interrupt pin; HIGH if TV is connIGPVF13Omulti-purpose vertical reference output with IPD outputIGP0F14Ogeneral purpose output signal 0 with IPD output busFSVGCG1I/Oframe synchronization output to VGC (optional input)SDAeG2I/Oserial data input/output (I <sup>2</sup> C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decodeIGPHG12Omulti-purpose horizontal reference output with IPD outIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)V <sub>SSEd</sub> H1Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                      | t bus<br>er)<br>tput bus                 |

| IGPVF13Omulti-purpose vertical reference output with IPD output<br>general purpose output signal 0 with IPD output bus<br>FSVGCG1I/Oframe synchronization output to VGC (optional input)SDAeG2I/Oserial data input/output (I²C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decoder)IGPHG12Omulti-purpose output signal 1 with IPD output busIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentVSSEdH11Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                               | t bus<br>er)<br>tput bus                 |

| IGP0F14Ogeneral purpose output signal 0 with IPD output busFSVGCG1I/Oframe synchronization output to VGC (optional input)SDAeG2I/Oserial data input/output (I²C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decoded)IGPHG12Omulti-purpose horizontal reference output with IPD outIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with CB-Y-CR 4 : 2 : 2; se<br>pin assignmentPD1H2IMSB – 6 of encoder input bus with CB-Y-CR 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; se<br>pin assignmentVSSEdH1Sdigital ground for peripheral cells (decoder)VSSEdH1Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Oscan test output; do not connect                                                                                                                                                                                                                                                                       | er)<br>tput bus                          |

| FSVGCG1I/Oframe synchronization output to VGC (optional input)SDAeG2I/Oserial data input/output (I²C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decodeIGPHG12Omulti-purpose horizontal reference output with IPD outIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD1H2IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentVSSEdH1Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                               | put bus                                  |

| SDAeG2I/Oserial data input/output (I²C-bus encoder)CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decodedIGPHG12Omulti-purpose horizontal reference output with IPD outputIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD1H2IMSB – 6 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH1ISIDQH13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                 | put bus                                  |

| CBOG3Ocomposite blanking output to VGC; active LOWPIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decodedIGPHG12Omulti-purpose horizontal reference output with IPD outIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with CB-Y-CR 4 : 2 : 2; setpin assignmentPD1H2IPD0H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setpin assignmentVSSEdH4SVSSEdH1Sdigital ground for peripheral cells (decoder)VSSEdH1Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | put bus                                  |

| PIXCLKOG4Opixel clock output to VGCVDDEdG11S3.3 V digital supply voltage for peripheral cells (decoderIGPHG12Omulti-purpose horizontal reference output with IPD outputIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H2IMSB – 6 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD0H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H2IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; setPD1H3IOVSEdH1Sdigital ground for peripheral cells (decoder)ICLKH11Sdigital ground for peripheral cells (decoder)IEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1O<                                                                                                                                             | put bus                                  |

| VDDEdG11S3.3 V digital supply voltage for peripheral cells (decodedIGPHG12Omulti-purpose horizontal reference output with IPD outIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with CB-Y-CR 4 : 2 : 2; sePD1H2IMSB – 6 of encoder input bus with CB-Y-CR 4 : 2 : 2; sePD0H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; seVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | put bus                                  |

| IGPHG12Omulti-purpose horizontal reference output with IPD outIGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; sePD1H2IMSB – 6 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; sePD0H3IMSB – 7 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; seVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | put bus                                  |

| IGP1G13Ogeneral purpose output signal 1 with IPD output busITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD1H2IMSB – 6 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentVSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| ITRIG14I(/O)programmable control signals for IPD output busPD2H1IMSB – 5 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; see<br>pin assignmentPD1H2IMSB – 6 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; see<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; see<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; see<br>pin assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ee Table 12 to Table 18 fo               |

| PD2H1IMSB – 5 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; see<br>pin assignmentPD1H2IMSB – 6 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; see<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with $C_B$ -Y- $C_R$ 4 : 2 : 2; see<br>pin assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ee <u>Table 12</u> to <u>Table 18</u> fo |

| pin assignmentPD1H2IMSB – 6 of encoder input bus with CB-Y-CR 4 : 2 : 2; set<br>pin assignmentPD0H3IMSB – 7 of encoder input bus with CB-Y-CR 4 : 2 : 2; set<br>pin assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ee Table 12 to Table 18 fo               |

| PD0H3IMSB – 7 of encoder input bus with C <sub>B</sub> -Y-C <sub>R</sub> 4 : 2 : 2; se<br>pin assignmentV <sub>SSEd</sub> H4Sdigital ground for peripheral cells (decoder)V <sub>SSEd</sub> H11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          |

| Print assignmentVSSEdH4Sdigital ground for peripheral cells (decoder)VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ee <u>Table 12</u> to <u>Table 18</u> fo |

| VSSEdH11Sdigital ground for peripheral cells (decoder)ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ee <u>Table 12</u> to <u>Table 18</u> fo |

| ICLKH12I/Oclock for IPD output bus (optional clock input)TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |

| TEST0H13Oscan test output; do not connectIDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |

| IDQH14Odata qualifier for IPD output busTEST4J1Oscan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |

| TEST4 J1 O scan test output; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          |

| TEST5 J2 I scan test input; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          |

| TEST3 J3 I scan test input; do not connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| V <sub>DDId</sub> J4 S 3.3 V digital supply voltage for core (decoder)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |

| V <sub>DDId</sub> J11 S 3.3 V digital supply voltage for core (decoder)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |

| AMXCLK J12 I audio master external clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          |

| ALRCLK J13 (I/)O audio left/right clock output; can be strapped <sup>[5][6]</sup> to su<br>to indicate that the default 24.576 MHz crystal (pin AL<br>pull-down) has been replaced by a 32.110 MHz crysta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RCLK = LOW; internal                     |

| ITRDY J14 I target ready input for IPD output bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |

| XTRI K1 I control signal for all X port pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |

| XPD7 K2 I/O MSB of XPD bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |