Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ICs for Communications

Enhanced Serial Communication Controller ESCC2

SAB 82532 SAF 82532

Version 3.2

User's Manual 07.96

| SAB 82532<br>SAF 82532<br>Revision Histo | ory:                        | Current Version: 07.96                                                             |

|------------------------------------------|-----------------------------|------------------------------------------------------------------------------------|

| Previous Versi                           | on: User's Manu             | al 07.93                                                                           |

| Page<br>(in previous<br>Version)         | Page<br>(in new<br>Version) | Subjects (major changes since last revision)                                       |

| -                                        | 10                          | new package provided: P-MQFP-80                                                    |

| -                                        | 72                          | Selectable out-of-band flow control in ASYNC mode: description added               |

| -                                        | 75                          | In-band flow control transparency: description added                               |

| -                                        | 87                          | Selectable enhanced resolution BRG: description added                              |

| 110, 141, 167                            | 124, 170, 208               | Timer register (TIMR): description extended for V3.x                               |

| 107, 127                                 | 120, 149                    | RSTA register, ISR0 register (RME interrupt): description extended                 |

| 115, 146, 172                            | 133, 179, 217               | XBCH, bit XC: description extended                                                 |

| 124,152, 179                             | 144, 187, 227               | Baud rate generator register (BGR): description extended                           |

| 133                                      | 157                         | Channel configuration register 4 (CCR4) in HDLC mode: description extended         |

| 138                                      | 164                         | STAR, bit XFW: description extended                                                |

| 140                                      | 168                         | Mode register (MODE) in ASYNC mode: new bits (FRTS, FRCS)                          |

| 144                                      | 175                         | RFIFO Control Register (RFC) in ASYNC mode: new bit (DXS)                          |

| -                                        | 198, 237                    | Channel Configuration Register 4 (CCR4) in ASYNC and BISYNC mode: new register     |

| 204                                      | 256                         | XTAL1 clock period, high time and low time: min. values for N-10 version corrected |

#### Edition 07.96

This edition was realized using the software system FrameMaker<sup>®</sup>.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1996.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Table of                                                                                              | Contents                                                                                                                                                                                                                                                                                                                 | Page                                                     |

|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.6.1<br>1.6.2<br>1.6.2.1<br>1.6.2.2                   | Introduction Features Pin Configuration Pin Definitions and Functions Logic Symbol Functional Block Diagram System Integration General Aspects Environment ESCC2 with SAB 8051 Microcontroller ESCC2 with SAB 80188 Microprocessor ESCC2 with SAB 80286 Microprocessor and SAB 82258 Advanced DMA Controller (ADMA)      | 7<br>9<br>23<br>25<br>25<br>26                           |

| 1.6.2.4<br>1.6.2.5<br>1.6.2.6<br>1.6.2.7<br>1.6.2.8                                                   | ESCC2 with MC 68008                                                                                                                                                                                                                                                                                                      | 29<br>30<br>31                                           |

| <b>2</b><br>2.1<br>2.2                                                                                | Basic Functional Principles  General  FIFO Structure                                                                                                                                                                                                                                                                     | . 37                                                     |

| <b>3</b><br>3.1<br>3.2<br>3.3                                                                         | Microprocessor Interface Register Set Data Transfer Modes Interrupt Interface                                                                                                                                                                                                                                            | . 42<br>. 44                                             |

| 4                                                                                                     | DMA Interface                                                                                                                                                                                                                                                                                                            | . 48                                                     |

| 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.3<br>5.4<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5 | HDLC/SDLC Serial Mode Operating Modes Procedural Support (layer-2 functions) Full-Duplex LAPB/LAPD Operation Half-Duplex SDLC-NRM Operation Error Handling SDLC Loop Special Functions Shared Flags Preamble Transmission CRC-32 Extended Transparent Transmission and Reception Cyclic Transmission (fully transparent) | 49<br>53<br>53<br>58<br>61<br>61<br>64<br>64<br>64<br>64 |

| 5.4.6<br>5.4.7                                                                                        | Continuous Transmission (DMA mode only)                                                                                                                                                                                                                                                                                  | . 65                                                     |

| Table of                                                                                                          | Contents                                                                                                                                                                                                                                                                                                                                            | Page                                               |

|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 5.4.8<br>5.4.9<br>5.4.10                                                                                          | One Bit Insertion                                                                                                                                                                                                                                                                                                                                   | 67                                                 |

| 6<br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.3<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3<br>6.4.4<br>6.4.5                      | Asynchronous Serial Mode Character Frame Data Reception Operating Modes Storage of Data Data Transmission Special Features Break Detection/Generation Flow Control by XON/XOFF (version 2 upward) Selectable Out-of-band Flow Control for Transmitter and Receiver (V3.x) In-band Flow Control Transparency Continuous Transmission (DMA mode only) | 68<br>69<br>70<br>70<br>70<br>71<br>72             |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3                                                   | Character Oriented Serial Mode (MONOSYNC/BISYNC)  Data Frame  Data Reception  Data Transmission  Special Functions  Preamble Transmission  Continuous Transmission (DMA mode only)  CRC Parity Inhibit                                                                                                                                              | 76<br>77<br>78<br>79<br>79                         |

| 8<br>8.1<br>8.2<br>8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5<br>8.4<br>8.5<br>8.5.1<br>8.5.2<br>8.6<br>8.7 | Serial Interface (layer-1 functions)  Clock Modes  Clock Recovery (DPLL)  Bus Configuration  Bus Access Procedure  Collisions  Priority (HDLC/SDLC mode only)  Timing Modes  Functions of RTS Output  Data Encoding  Modem Control Functions (RTS/CTS, CD)  RTS/CTS Handshaking  Carrier Detect (CD) Receiver Control  Test Mode  Universal Port    | 80<br>81<br>91<br>92<br>93<br>93<br>97<br>98<br>98 |

| <b>9</b><br>9.1<br>9.2                                                                                            | Operational Description         Reset                                                                                                                                                                                                                                                                                                               | . 100                                              |

| Table of                                                                                 | Contents                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                             |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 9.3<br>9.3.1<br>9.3.1.1<br>9.3.1.2<br>9.3.2<br>9.3.2.1<br>9.3.2.2                        | Operational Phase Data Transmission Interrupt Mode DMA Mode Data Reception Interrupt Mode DMA Mode                                                                                                                                                                                                                                                                               | . 105<br>. 105<br>. 108<br>. 109                                                 |

| 10<br>10.1<br>10.1.1<br>10.1.2<br>10.2<br>10.2.1<br>10.2.2<br>10.3<br>10.3.1<br>10.3.2   | Detailed Register Description Status/Control Registers in HDLC Mode Register Addresses Register Definitions Status/Control Registers in ASYNC Mode Register Addresses Register Definitions Status/Control Registers in BISYNC Mode Register Addresses Register Addresses Register Definitions                                                                                    | . 112<br>. 114<br>. 159<br>. 159<br>. 161<br>. 199                               |

| 11.4.1.2<br>11.4.2<br>11.4.3<br>11.4.3.1<br>11.4.3.2<br>11.4.3.3<br>11.4.3.4<br>11.4.3.5 | Electrical Characteristics Absolute Maximum Ratings DC Characteristics Capacitances AC Characteristics Microprocessor Interface Siemens/Intel Bus Interface Mode Motorola Bus Interface Mode Parallel Port Timing Serial Interface Clock Input Timing Receive Cycle Timing Transmit Cycle Timing Strobe Timing (clock mode 1) Synchronization Timing (clock mode 5) Reset Timing | 238<br>238<br>240<br>241<br>242<br>250<br>255<br>256<br>256<br>257<br>261<br>263 |

| 12                                                                                       | Package Outlines                                                                                                                                                                                                                                                                                                                                                                 | . 265                                                                            |

| <b>13</b><br>13.1<br>13.2                                                                | Appendix  Baud Rate Generator Tables  Development Board EASY532                                                                                                                                                                                                                                                                                                                  |                                                                                  |

### 1 Introduction

The Enhanced Serial Communication Controller ESCC2 (SAB 82532/SAF 82532) is a multiprotocol data communication controller with two symmetrical serial channels. It has been designed to implement high-speed communication links and to reduce hardware and software overhead needed for serial synchronous/asynchronous communications.

Each channel contains an independent clock generator, DPLL, encoder/decoder and programmable protocol hardware. Data communication with asynchronous, synchronous character oriented, and HDLC based protocols with extended support of X.25 LAPB, the ISDN LAPD, and SDLC protocols is implemented. Like the SAB 82525 (HSCX) which is a functional subset of the ESCC2, the ESCC2 is capable of handling a large set of layer-2 protocol functions independently of the host processor.

The version 82532N-10 of the Enhanced Serial Communication Controller (ESCC2) opens a wide area for applications which use time division multiplex methods (e.g. time-slot oriented PCM systems, systems designed for packet switching, ISDN applications) by its programmable telecom-specific features. In this special operating mode (clock mode 5), which is applicable to all serial modes (HDLC/SDLC, ASYNC, BISYNC), the ESCC2 can transmit or receive data packets in one of up to 64 time-slots of programmable width.

The device is controlled via a parallel 16-bit wide interface which is directly compatible with the most popular 8/16 bit microprocessors (Siemens/Intel or Motorola type). The internal FIFOs (64 bytes per direction and channel) with additional DMA capability provide a powerful interface to the higher layers implemented in a microcontroller. For interrupt controlled systems, the ESCC2 supports daisy chaining and interrupt vector generation.

The ESCC2 is fabricated using SIEMENS advanced CMOS technology and is available in a P-LCC-68 and a P-MQFP-80 package.

### **Applications**

- Universal, multiprotocol communication board for Workstation- and PC-boards

- · Terminal controllers

- Computer peripherals

- Time slotted packet networks

- · Multimaster communication networks

- LANs

# **Enhanced Serial Communication Controller ESCC2**

**SAB 82532 SAF 82532**

### **CMOSIC**

### 1.1 Features

#### **Serial Interface**

- Two independent full duplex serial channels

- On chip clock generation or external clock source

- On chip DPLL for clock recovery of each channel

- Two independent baud rate generators

- Independent time-slot assignment for each channel with programmable time-slot length (1 ... 256 bits)

- Async, sync character oriented (MONOSYNC/BISYNC) or HDLC/SDLC modes (including SDLC LOOP)

- Transparent receive/transmit of data bytes without framing

- · NRZ, NRZI, FM and Manchester encoding

- Modem control lines (RTS, CTS, CD)

- · CRC support:

- HDLC/SDLC: CRC-CCITT or CRC-32 (automatic handling for transmit/receive direction)

- BISYNC: CRC-16 or CRC-CCITT (support for transmit direction)

| Туре           | Ordering Code | Package   | Max. Data Rat | te                | Time Slot<br>Mode |

|----------------|---------------|-----------|---------------|-------------------|-------------------|

|                |               |           | ext. i        | nt. (DPLL)<br>ked |                   |

| SAB 82532 N    | Q67101-H6790  | P-LCC-68  | 2.048 Mbit/s  | 2 Mbit/s          | no                |

| SAB 82532 N-10 | Q67101-H6791  | P-LCC-68  | 10 Mbit/s     | 2 Mbit/s          | yes               |

| SAB 82532 H    | Q67101-H6788  | P-MQFP-80 | 2.048 Mbit/s  | 2 Mbit/s          | no                |

| SAB 82532 H-10 | Q67101-H6789  | P-MQFP-80 | 10 Mbit/s     | 2 Mbit/s          | yes               |

| SAF 82532 N-10 | on request    | P-LCC-68  | 10 Mbit/s     | 2 Mbit/s          | yes               |

| SAF 82532 H-10 | on request    | P-MQFP-80 | 10 Mbit/s     | 2 Mbit/s          | yes               |

- Support of bus configuration by collision detection and resolution

- Statistical multiplexing

- Continuous transmission of 1 to 32 bytes possible

- Programmable preamble (8 bit) with selectable repetition rate (HDLC/SDLC and BISYNC)

- Data rate up to 10 Mbit/s

- Master clock mode with data rate up to 4 Mbit/s

## **Protocol Support (HDLC/SDLC)**

- Various types of protocol support depending on operating mode

- Auto mode (automatic handling of S- and I-frames)

- Non-auto mode

- Transparent mode

- · Handling of bit oriented functions

- Support of LAPB/LAPD/SDLC/HDLC protocol in auto mode (I- and S-frame handling)

- Modulo-8 or modulo-128 operation

- · Programmable time-out and retry conditions

- Programmable maximum packet size checking

#### MP Interface and Ports

- 64 byte FIFOs per channel and direction (byte or word access)

- 8/16 bit microprocessor bus interface (Intel or Motorola type)

- All registers directly accessible (byte and word access)

- · Efficient transfer of data blocks from/to system memory via DMA or interrupt request

- Support of Daisy Chaining and Slave Operation with Interrupt Vector generation

- 8-bit programmable bi-directional universal port

### General

- Advanced CMOS technology

- Low power consumption: active 40 mW at 2 MHz/standby 5 mW (typical values)

- P-LCC-68 Package

- P-MQFP-80 Package

07.96

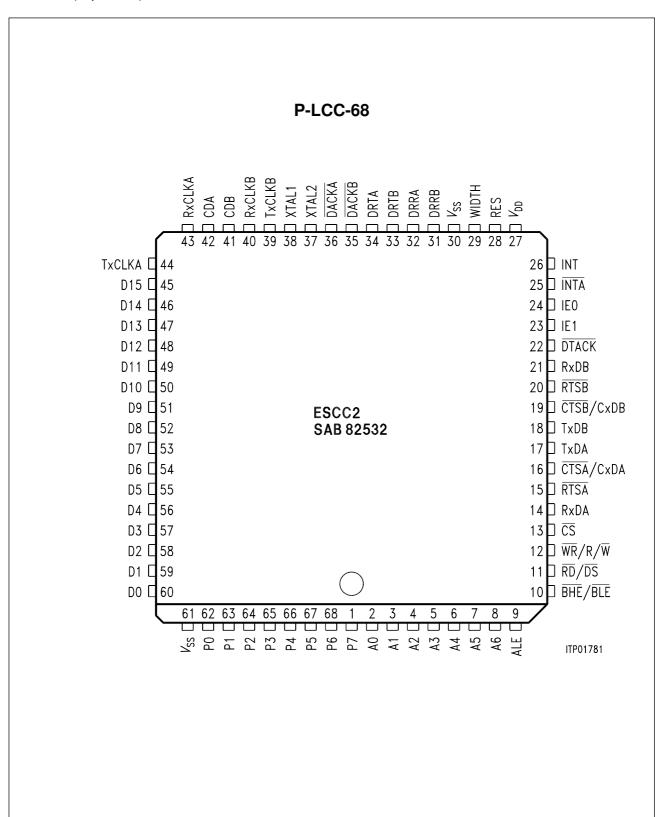

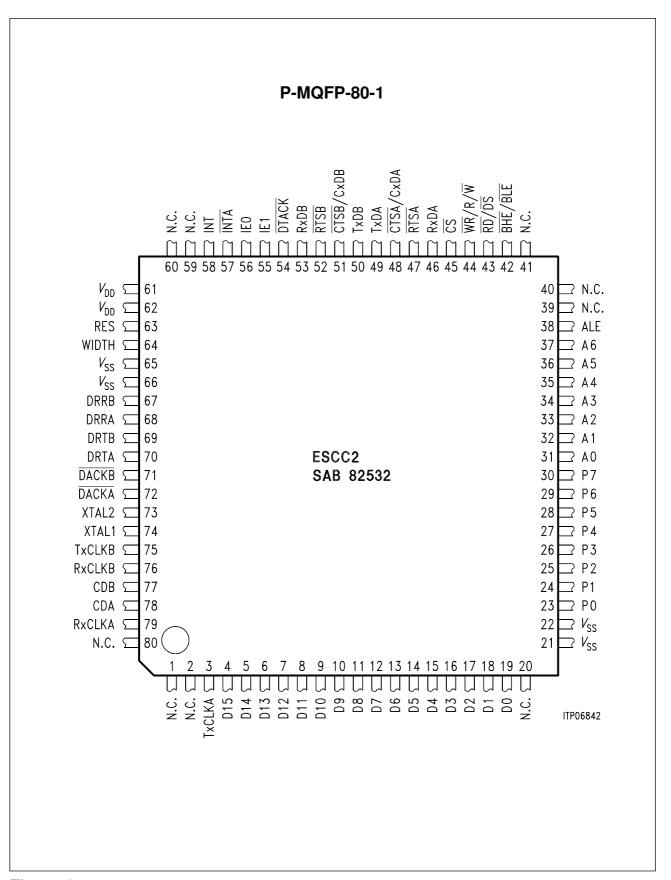

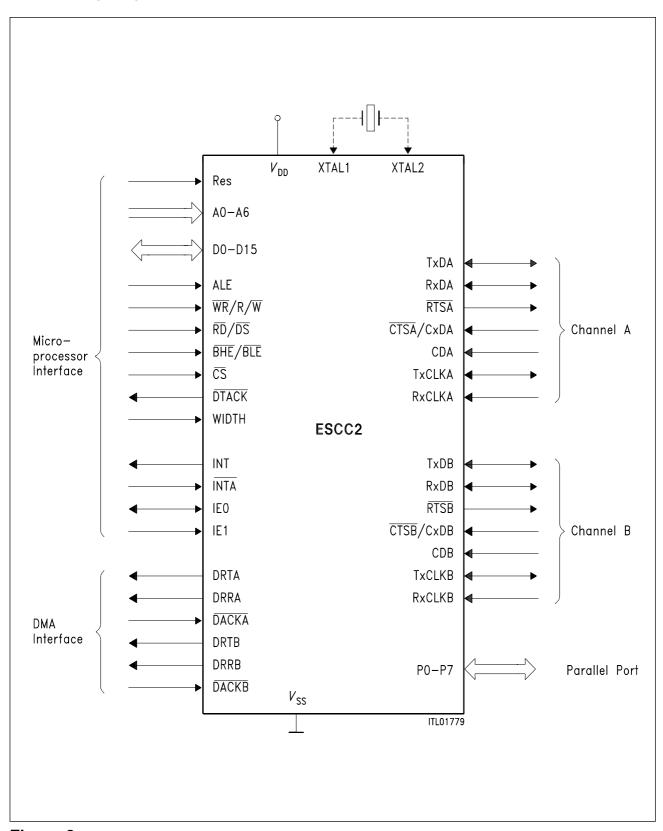

## 1.2 Pin Configuration

(top view)

Figure 1

Figure 2

## 1.3 Pin Definitions and Functions

| Pin No.  |           | Symbol Input (I) | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----------|------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 | -                | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2 8      | 31 37     | A0 A6            | I          | Address Bus These inputs interface with seven bits of the system's address bus to select one of the internal registers for read or write.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 60 45    | 19 4      | D0 D15           | I/O        | Bi-directional three-state data lines which interface with the system's data bus. Their configuration is controlled by the level of pin WIDTH:  - 8-bit mode (WIDTH = 0): D0 D7 are active.  D8 D15 are in high impedance and have to be connected to V <sub>DD</sub> or V <sub>SS</sub> .  - 16-bit mode (WIDTH = 1): D0 D15 are active. In case of byte transfers, the active half of the bus is determined by A0 and BHE/BLE and the selected bus interface mode (via ALE). The unused half is in high impedance. For detailed information, refer to <b>chapter 3.1</b> . |

| 9        | 38        | ALE              |            | Address Latch Enable The level at this pin defines the bus interface mode: Fixed to $V_{\rm SS}$ : Demultiplexed Siemens/Intel bus interface Fixed to '1': Demultiplexed Motorola bus interface Switching: Multiplexed Siemens/Intel bus interface The address information provided on lines A0 A6 is internally latched with the falling edge of ALE. This function allows the ESCC2 to be directly connected to a multiplexed address/data bus. In this case, pins A0 A6 must be externally connected to the Data Bus pins (e.g. D0 D6 for 8-bit CPUs).                    |

Note: All unused input pins have to be connected to a defined level.

| Pin No.  |           | Symbol In | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------|-----------|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P-LCC-68 | P-MQFP-80 | _         | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 11       | 43        | RD/DS     |            | Read Enable (Siemens/Intel bus mode) This signal indicates a read operation. When the ESCC2 is selected via CS the READ signal enables the bus drivers to output data from an internal register addressed via A0 A6 on to Data Bus. For more information about control/status register and FIFO access in the different bus interface modes refer to chapter 2. If DMA transfer is selected via DACKA or DACKB, the RD signal enables the bus drivers to put data from the corresponding Receive FIFO on the Data Bus. Inputs A1 A6 are ignored. A0 and BHE/BLE are used to select byte or word access. Data Strobe (Motorola bus mode) This pin serves as input to control read/write operations. |  |

| 12       | 44        | WR/R/W    |            | Write Enable (Siemens/Intel bus mode) This signal indicates a write operation. When CS is active the ESCC2 loads an internal register with data provided via the Data Bus. For more information about control/status register and FIFO access in the different bus interface modes refer to chapter 2.  If DMA transfer is selected via DACKA or DACKB, the WR signal enables latching data from the Data Bus on the top of the corresponding Transmit FIFO. Inputs A0 A6 are ignored.  Read/Write Enable (Motorola bus mode) This signal distinguishes between read and write operation.                                                                                                          |  |

| 13       | 45        | CS        | 1          | Chip Select A low signal selects the ESCC2 for read/write operations. CS has no function in interrupt acknowledge or DMA cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

Introduction

| Р        | in No.    | Symbol  | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-----------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |         | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28       | 63        | RES     |            | Reset A high signal on this pin forces the ESCC2 into reset state. During Reset the ESCC2 is in power up mode, after Reset in power-down mode. Re-activation of each channel is done via bit CCR0:PU (refer to chapter 9.2).  During Reset  - all uni-directional output stages are in high-impedance state,  - all bi-directional output stages (data bus) are in high-impedance state,  - output XTAL2 is in high-impedance if input XTAL1 is 'high' (the internal oscillator is disabled during reset),  - signals RD and INTA have to be 'high'                                                                                   |

| 10       | 42        | BHE/BLE |            | Bus High Enable (Siemens/Intel bus mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the upper byte of the data bus (D8D15). In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD}$ . Refer to <b>chapter 3.1</b> for detailed information. Bus Low Enable (Motorola bus mode) If 16-bit bus interface mode is enabled, this signal indicates a data transfer on the lower byte of the data bus (D0 D7). In 8-bit bus interface mode this signal has no function and should be tied to $V_{\rm DD}$ . Refer to <b>chapter 3.1</b> for detailed information. |

| 29       | 64        | WIDTH   | I          | Width Of Bus Interface (Bus Interface Mode) A low signal on this input selects the 8-bit bus interface mode. A high signal on this input selects the 16-bit bus interface mode. In this case word transfer to/from the internal registers is enabled.  Moreover, byte transfers (in conjunction with A0 and BHE/BLE) are allowed, too.                                                                                                                                                                                                                                                                                                |

| Р        | in No.    | Symbol Input (I) | Function   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------|-----------|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P-LCC-68 | P-MQFP-80 |                  | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 22       | 54        | DTACK            | O (oD)     | Data Transfer Acknowledge During a bus cycle (read/write, asynchronous bus), this signal indicates that ESCC2 is ready for data transfer. The signal remains active until the data strobe $(\overline{DS}, \overline{RD} \text{ or } \overline{WR})$ and/or the Chip Select signal $(\overline{CS})$ or the Interrupt Acknowledge $(\overline{INTA})$ go inactive. An external resistor has to be tied to $V_{DD}$ if this function is used.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 26       | 58        | INT              | O (oD)     | Interrupt Request INT serves as general interrupt request which may include all serial mode specific interrupt sources and the requests of the 8-bit universal port if programmed. These interrupt sources can be masked via registers IMR0, IMR1 (channel) and PIM (universal port). Interrupt status is reported via registers GIS (Global Interrupt Status), ISR0, ISR1 (channel) and PIS (universal port). Output characteristics (push-pull active low/high, open drain) are determined by programming the IPC register. In Daisy Chain cascading mode INT signal generation is only enabled if the Interrupt Enable input IE1 is active (logical '1'). INT is reset if  interrupts are disabled in Daisy Chain cascading mode (pin IE1 = '0'),  no further interrupt is pending, i.e. all interrupt status bits are reset. |  |

| Р        | in No.    | Symbol | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 | 1      | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25       | 57        | ĪNTĀ   |            | Interrupt Acknowledge  If the interrupt is acknowledged via pin INTA, an interrupt vector is output on D0 D7. All interrupt sources are organized in 8 groups with fixed priority (refer to chapter 2). The generated interrupt vector refers to the interrupt group with currently highest priority (although more than one interrupt source/group may be active). Reaction on INTA signal depends on the bus interface mode and the cascading mode in conjunction with the Interrupt Enable pins IEO and IE1 (ref. to IPC register):  Motorola bus mode: INT is reset with the rising edge of the following valid INTA cycle if no further interrupt is pending. The interrupt vector is output with signal DS.  Siemens/Intel bus mode: INT is reset with the rising edge of the second valid INTA cycle (2-cycle '86 mode) if no further interrupt is pending. Slave mode: Interrupt acknowledge is accepted if an interrupt signal has been generated and the slave address provided via IEO, IE1 corresponds to the programmed value (IPC register).  Daisy Chaining mode: Interrupt acknowledge is accepted if an interrupt signal has been generated and Interrupt acknowledge is accepted if an interrupt signal has been generated and Interrupt signal has been generated and Interrupt Enable input IE1 is active during the following INTA cycle.  Note: Pins CS, DACKA and DACKB have to be inactive during an INTA cycle. If pin INTA is not used, it has to be tied to VDD. |

| Pin No.  |           | Symbol Input (I) | Function   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----------|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |                  | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24 23    | 56<br>55  | IEO IE1          |            | Interrupt Enable 0, 1 The function depends on the selected cascading mode: Slave mode: IE0 and IE1 are inputs. Interrupt acknowledge is accepted if an interrupt signal has been generated and the slave address provided via IE0, IE1 corresponds to the programmed value (IPC register). If not used, IE0 and IE1 should be tied to GND and the slave address should be set to '0' (e.g. single device application).  Daisy Chaining mode: IE0 is output, IE1 is input.  Normally, IE1 is connected to the IE0 pin of devices with higher priority. If not used, IE1 has to be fixed to '1'. If IE1 is reset ('0')  — the IE0 output is reset immediately, — an active INT signal will be prohibited or aborted.  As long as INTA input is inactive, IE1 = '1' enables INT signal generation. If INT goes active, pin IE0 immediately is set to '0'. Interrupt acknowledge is accepted if the Interrupt Enable input IE1 is active during the following INTA cycle. During this cycle, and additionally 'till the end of the second INTA cycle in Siemens/Intel bus mode, triggering of INT signal generation is prohibited, i.e. no interrupt will be generated while (another) device is under service. This is valid even for devices with higher priority.  Pin IE0 returns to active state (logical '1') when INT is reset and IE1 input is high. |

| Pin No.  |           | Symbol       | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |              | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 34 33    | 70<br>69  | DRTA<br>DRTB | O          | DMA Request Transmitter (channel A/channel B) The transmitter of ESCC2 requests a DMA transfer by activating this line. The request remains active as long as the respective Transmit FIFO requires data transfers. The amount of data bytes to be transferred from the system memory to the ESCC2 (= byte count) must be written first to the XBCH, XBCL registers. Always blocks of data (n × 32 bytes + REST, n = 0, 1,) are transferred 'till the Byte Count is reached. DRTn is deactivated with the beginning of the last write cycle. |

| 32<br>31 | 68<br>67  | DRRA<br>DRRB | O          | DMA Request Receiver (channel A/channel B) The receiver of ESCC2 requests a DMA transfer by activating this line. The request remains active as long as the corresponding Receive FIFO requires data transfers, thus always blocks of data are transferred. DRRn is deactivated immediately following the falling edge of the last read cycle.                                                                                                                                                                                               |

| Pin No.  |           | Symbol           | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----------|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |                  | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 36 35    | 72<br>71  | DACKA<br>DACKB   |            | DMA Acknowledge (channel A/channel B) A low signal on these pins informs the ESCC2 that the requested DMA cycle controlled via DRTA/B or DRRA/B is in progress, i.e. the DMA controller has achieved bus mastership from the CPU and will start data transfer cycles (either write or read). In conjunction with a read or write operation these inputs serve as Access Enable (similar to $\overline{\text{CS}}$ ) to the respective FIFOs. If $\overline{\text{DACK}}$ is active, the input to pins A1 A6 is ignored and the $\overline{\text{FIFOs}}$ are implicitly selected. A0 and $\overline{\text{BHE/BLE}}$ are used to select byte or word access. If not used, these pins must be connected to $V_{\text{DD}}$ . |

| 14<br>21 | 46<br>53  | RxDA<br>RxDB     | (O/oD)     | Receive Data (channel A/channel B) Serial data is received on these pins. May be switched to TxD function via bit CCR2:SOC1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 43 40    | 79<br>76  | RxCLKA<br>RxCLKB | I          | Receive Clock (channel A/channel B) The function of these pins depends on the selected clock mode. In each channel, RxCLKn may supply either  - the receive clock (clock mode 0), or  - the receive and transmit clock (clock mode 1, 5), or  - the clock input for the baud rate generator (clock mode 2, 3).                                                                                                                                                                                                                                                                                                                                                                                                              |

Introduction

| Pin No.  |           | Symbol                         | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----------|--------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |                                | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15<br>20 | 47<br>52  | RTSA<br>RTSB                   | 0          | Request to Send (channel A/channel B) When the RTS bit in the MODE register is set, the RTS signal goes low. When the RTS bit is reset, the signal goes high if the transmitter has finished and there is no further request for a transmission. In bus configuration, RTS can be programmed via CCR2 to:  — go low during the actual transmission of a frame shifted by one clock period, excluding collision bits.  — go low during reception of a data frame.  — stay always high (RTS disabled). |

| 16<br>19 | 48<br>51  | CTSA/<br>CxDA<br>CTSB/<br>CxDB |            | Clear to Send (channel A/channel B) A low on the CTSn input enables the respective transmitter. Additionally, an interrupt may be issued if a state transition occurs at the CTSn pin (programmable feature).  If no 'Clear To Send' function is required, the CTSn inputs can be directly connected to GND.  Collision Data (channel A/channel B) In a bus configuration, the external serial bus must be connected to the corresponding CxDn pin for collision detection.                          |

| Pin No.  |           | Symbol       | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-----------|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |              | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 42 41    | 78<br>77  | CDA<br>CDB   | 1          | Carrier Detect (channel A/channel B) The function of this pin depends on the selected clock mode. It can supply - either a modem control or a general purpose input (clock modes 0, 2, 3, 4, 6, 7). If auto-start is programmed, it functions as a receiver enable signal or a receive strobe signal (clock mode 1) or a frame synchronization signal in time-slot oriented operation mode (clock mode 5). Additionally, an interrupt may be issued if a state transition occurs at the CDn pin (programmable feature). |

| 17<br>18 | 49<br>50  | TxDA<br>TxDB | O/oD       | Transmit Data (channel A/channel B) Transmit data is shifted out via these pins. They can be programmed to be either a push-pull or open drain output to support bus configurations.  Note: Pin TxD is 'OR'ed with pin RTS if NRZI encoding and IDLE as Interframe  Note: Time Fill are selected and bit MODE:RTS is reset.  May be switched to RxD function via bit CCR2:SOC1.                                                                                                                                         |

| Pin No.  |           | Symbol         | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----------|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80 |                | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 44 39    | 3 75      | TxCLKA TxCLKB  | I/O        | Transmit Clock (channel A/channel B) The function of this pin depends on the selected clock mode and the value of the SSEL bit (CCR2 register). For detailed information about the clock modes refer to chapter 2.  If programmed as an input, this pin supplies either  - the transmit clock for the channel (clock mode 0, 2, 6; SSEL bit in CCR2 is reset), or  - a transmit strobe signal for the channel (clock mode 1).  If programmed as an output (bit CCR2:TOE is set), this pin supplies either  - the transmit clock for the channel which is generated  • either from the baud rate generator (clock mode 2, 3, 6, 7; SSEL bit in CCR2 is set),  • or from the DPLL circuit (clock mode 3, 7; SSEL bit in CCR2 is reset)  • or from the crystal oscillator (clock mode 4),  • or an active-low tri-state control signal marking the programmed transmit time-slot (clock mode 5) if bit CCR2:TOE is set. |

| 38 37    | 74<br>73  | XTAL1<br>XTAL2 | I<br>(O)   | Crystal Connection  If the internal oscillator is used for clock generation the external crystal has to be connected to these pins. Moreover, XTAL1 may be used as common clock input for channel A and channel B provided by an external clock generator. All versions: common use for both channels in clock modes 4, 6, 7.  Version 2 upward: additionally used in clock mode 0b and for master clock applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## 1.3 Pin Definitions and Functions (cont'd)

| Pin No.  |                | Symbol      | Input (I)  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|----------------|-------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-LCC-68 | P-MQFP-80      |             | Output (O) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 62 68,1  | 23 30          | P0 P7       | I/O        | Parallel Port A general purpose 8-bit bi-directional parallel port is provided on pins P0 P7. Every pin is individually programmable to operate as an output or an input (Port Configuration Register PCR).  If defined as output, the state of the pin is directly controlled via the microprocessor interface (Port Value Register PVR).  If defined as input, its state can be read via PVR. All changes may be indicated via an interrupt status (Port Interrupt Mask register PIM, Port Interrupt Status register PIS, interrupt is output on pin INT). |

| 30<br>61 | 21, 22, 65, 66 | $V_{ m SS}$ | I          | Ground (0 V) For correct operation, all pins have to be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27       | 61, 62         | $V_{DD}$    | I          | Positive power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Note: All unused input pins have to be connected to a defined level.

## 1.4 Logic Symbol

Figure 3 ESCC2 Logic Symbol

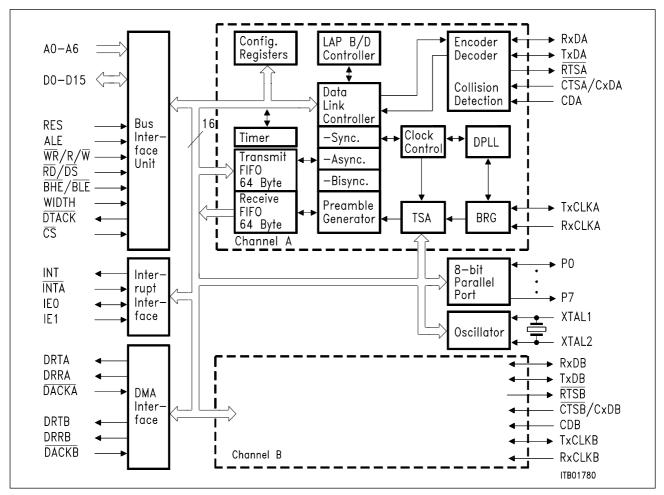

## 1.5 Functional Block Diagram

Figure 4

Functional Block Diagram SAB 82532/SAF 82532

The ESCC2 (SAB 82532/SAF 82532) comprises two completely independent full-duplex serial interfaces (channel A and channel B) which support HDLC/SDLC, BISYNC and ASYNC protocols. Layer-1 functions are performed by means of internal oscillator, Baud Rate Generator (BRG), Digital Phase Locked Loop (DPLL), and Time-Slot Assignment circuits (TSA, only available for versions SAB/SAF 82532 N-10 and SAB/SAF 82532 H-10). Encoding/decoding of serial data can be done by using NRZ, NRZI, FM0, FM1 and Manchester encoding schemes. An 8-bit universal bi-directional port is provided which can be used for additional modem control lines or for general I/O purposes.

Associated with each serial channel is a set of independent command and status registers and 64-byte deep FIFOs for transmit and receive direction. Access is done via the flexible 8/16-bit microprocessor interface. DMA capability has been added to the ESCC2 by means of a 4-channel DMA interface with one DMA request line for each transmitter and receiver of both channels. The interrupt structure of ESCC2 supports interrupt driven systems using interrupt polling, daisy chaining or interrupt vector control.

## 1.6 System Integration

### 1.6.1 General Aspects

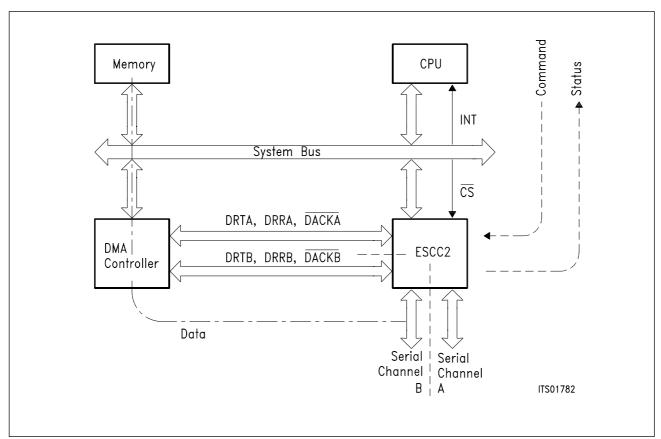

Figure 5

General System Integration of ESCC2

Figure 5 gives a general overview of system integration of ESCC2.

The ESCC2's bus interface consists of an 8/16-bit bidirectional data bus (D0 ... D15), seven Address Line inputs (A0 ... A6), three control inputs (RD/DS, WR/R/W, CS), four signals for interrupt support (INT, INTA, IE0, IE1) and a 4-channel DMA interface (DRTA, DRRA, DACKA, DRTB, DRRB, DACKB). Mode input pins (strapping options) allow the bus interface to be configured for 8/16-bit bus width and for either Siemens/Intel or Motorola environment.

Generally, there are two types of transfers occurring via the system bus:

- Command/Status transfers, which are always controlled by the CPU. The CPU sets the operation mode (initialization), controls function sequences and gets status information by writing or reading the ESCC2's registers (via CS, WR or RD, and register address via A0 ... A6).

- Data Transfers, which are effectively performed by DMA without CPU interaction using the ESCC2's DMA interface (DMA mode). Optionally, interrupt controlled data transfer can be done by the CPU (interrupt mode).