Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Dual Channel 2.5MHz, 1.7A Synchronous Buck Regulator

## POWER MANAGEMENT Features

- V<sub>IN</sub> Range 2.75 5.5V

- V<sub>OUT</sub> Selectable 1.0 3.3V

- Up to1.7A Output Current for Each Channel

- Package with Ultra-Small Footprint: 3 x 3 x 0.75(mm)

- Switching Frequency 2.5MHz

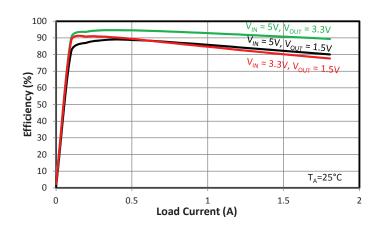

- Efficiency Up to 94%

- Low Output Noise in CCM

- Excellent Transient Response

- Start Up into Pre-Biased Output

- 100% Duty-Cycle Low Dropout Operation

- Shutdown Current <1µA

- Internal Soft-Start

- Input Under-Voltage Lockout

- Output Over-Voltage, Current Limit Protection

- Over-Temperature Protection

- V<sub>OUT</sub> Further Adjustable Using External Resistors

- PGOOD Feature

- Lead-free, Halogen-free, and RoHS/WEEE Compliant

- AEC-Q100 (Grade-2) Qualified, See Derating Curve on Page 15 for Application Information.

### **Applications**

- Desktop Computing

- Set-Top Box

- LCDTV

- Network Cards

- Automotive Car Navigation/Infotainment

#### **Description**

The SC284AQ is a dual channel 1.7A synchronous stepdown regulator designed to operate with an input voltage range of 2.75 to 5.5 Volts. Each channel offers seven pre-determined output voltages via three control pins programmable from 1.0 to 3.3 Volts. The control pins allow for on-the-fly voltage changes, enabling system designers to implement dynamic power savings. The SC284AQ is also capable of adjusting the output voltage via an external resistor divider.

The SC284AQ is optimized for maximum efficiency over a wide range of load currents. The device operates in PWM mode with fixed 2.5MHz oscillator frequency, allowing the use of small surface mount external components.

Connecting CTL0 — CTL2 to logic low forces the device into shutdown mode reducing the supply current to less than  $1\mu A$ . Connecting any of the control pins to logic high enables the converter and sets the output voltage according to Table 1. Other features include undervoltage lockout, soft-start to limit inrush current, and over-temperature protection.

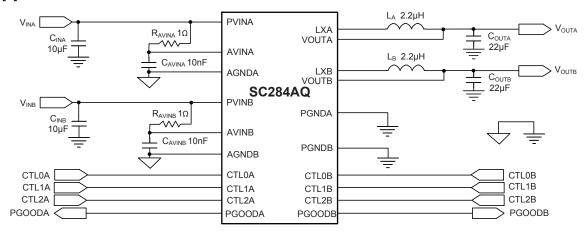

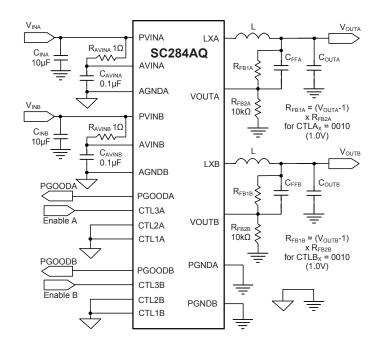

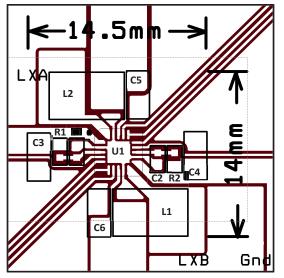

### **Typical Application Circuit**

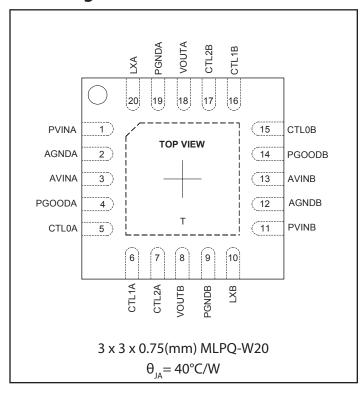

## **Pin Configuration**

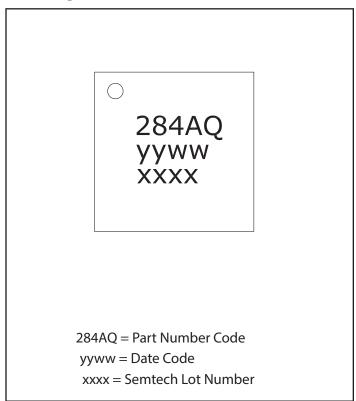

### **Marking Information**

### **Ordering Information**

| Device                         | Package                   |

|--------------------------------|---------------------------|

| SC284AQWLTRT <sup>(1)(2)</sup> | 3 x 3 x 0.75(mm) MLPQ-W20 |

| SC284AQEVB                     | Evaluation Board          |

#### Notes:

- (1) Available in tape and reel only. A reel contains 3,000 devices.

- (2) Available in lead-free package only. Device is fully WEEE and RoHS compliant and halogen-free.

Table 1 – Output Voltage Settings

| CTL2[A/B] | CTL1[A/B] | CTL0[A/B] | Output Voltage |

|-----------|-----------|-----------|----------------|

| 0         | 0         | 0         | Disabled       |

| 0         | 0         | 1         | 1.0V           |

| 0         | 1         | 0         | 1.1V           |

| 0         | 1         | 1         | 1.2V           |

| 1         | 0         | 0         | 1.5V           |

| 1         | 0         | 1         | 1.8V           |

| 1         | 1         | 0         | 2.5V           |

| 1         | 1         | 1         | 3.3V           |

### **Absolute Maximum Ratings**

| AVINA, AVINB, PVINA, PVINB Supply (V)0.3 to +6.0       |

|--------------------------------------------------------|

| LXA and LXB (V)1 to $V_{IN}$ + 1, -3 (20ns Max), 6 Max |

| VOUTA and VOUTB (V)0.3 to ( $V_{_{\mathrm{IN}}}$ +0.3) |

| CTLXA/B pins (V)0.3 to $(V_{IN} + 0.3)$                |

| Peak IR Reflow Temperature (°C)                        |

| ESD Protection Level <sup>(2)</sup> (kV)               |

| Output Short Circuit to GND                            |

|                                                        |

#### **Recommended Operating Conditions**

| V <sub>INA</sub> and V <sub>INB</sub> Supply (V) | 2.75 to 5 | .5 |

|--------------------------------------------------|-----------|----|

| Ambient Temperature (°C)                         | -40 to 10 | )5 |

| Junction Temperature (°C)                        | -40 to 12 | 25 |

#### **Thermal Information**

| Thermal Resistance, Junction to Ambient $^{(1)}$ (°C/W) | 40  |

|---------------------------------------------------------|-----|

| Maximum Junction Temperature (°C) + `                   | 150 |

| Storage Temperature Range (°C)65 to +                   | 150 |

Exceeding the absolute maximum ratings may result in permanent damage to the device and/or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### Notes

- (1) Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

- (2) Tested according to JEDEC standard JS-001-2012.

#### **Electrical Characteristics** —

Unless specified:  $V_{INA} = V_{INB} = 5.0V$ ,  $V_{OUTA} = V_{OUTB} = 1.5V$ ,  $C_{INA} = C_{INB} = 10 \mu F$ ,  $C_{OUTA} = C_{OUTB} = 22 \mu F$ ,  $L = 2.2 \mu H$ ,  $-40 ^{\circ}C \le T_{J} \le +125 ^{\circ}C$ . Unless otherwise noted typical values are  $T_{A} = +25 ^{\circ}C$ .

| Parameter                   | Symbol                         | Conditions                                                                   | Min  | Тур  | Max  | Units |

|-----------------------------|--------------------------------|------------------------------------------------------------------------------|------|------|------|-------|

| Input Voltage Range         | V <sub>INA/B</sub>             |                                                                              | 2.75 |      | 5.5  | V     |

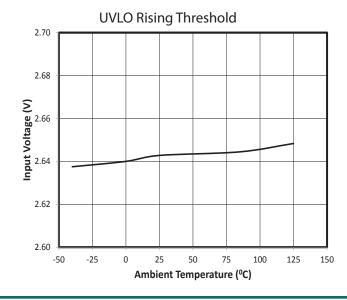

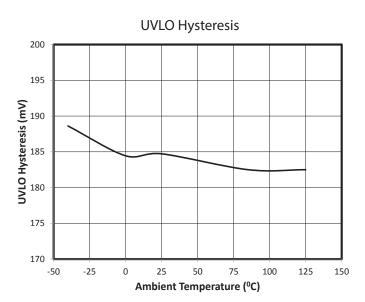

| Linday Voltago Lockout      | V                              | Rising $V_{INA}^{},V_{INB}^{}$                                               | 2.55 | 2.65 | 2.75 | V     |

| Under-Voltage Lockout       | V <sub>UVLO</sub>              | Hysteresis                                                                   |      | 200  |      | mV    |

| Quiescent Current           | I <sub>Q</sub>                 | Channel A & B, PWM mode excluding I <sub>out</sub> ,<br>per channel          |      | 6.6  |      | mA    |

| Shutdown Current            | I <sub>SHDN</sub>              | CTL <sub>0-2</sub> = GND, Per channel                                        |      | 1    | 10   | μΑ    |

| Soft-Start Time             | t <sub>ss</sub>                | Channel A & B; I <sub>OUT</sub> = 1.8A, V <sub>OUT</sub> =90% of final value |      | 1700 |      | μs    |

| Output Voltage Range        | V <sub>out</sub>               |                                                                              | 1.0  |      | 3.3  | V     |

| Output Voltage Tolerance(1) | $\Delta V_{ m out}$            | Channel A & B                                                                | -3.0 |      | +3.0 | %     |

| CTL Settings Regulation     | $\Delta V_{\text{CTL-REG}}$    | Channel A & B; Relative to V <sub>OUT</sub> at CTL=100                       |      | ±1   |      | %     |

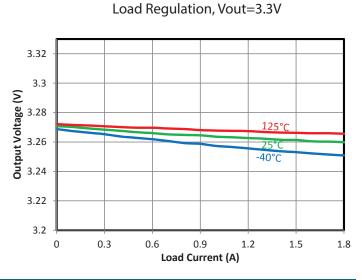

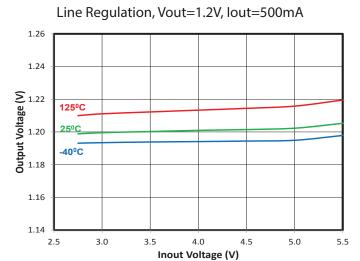

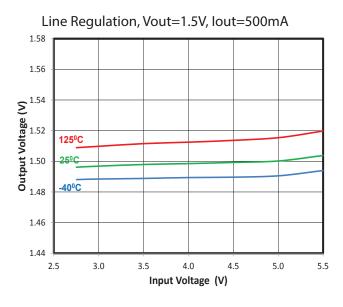

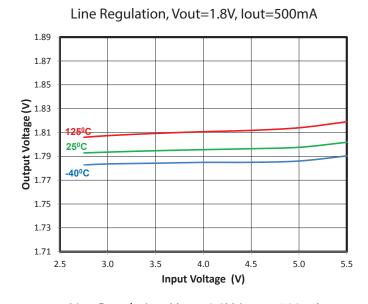

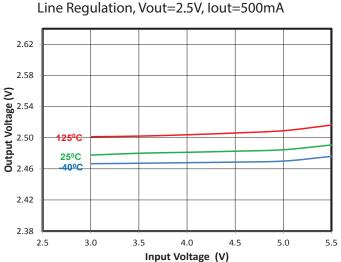

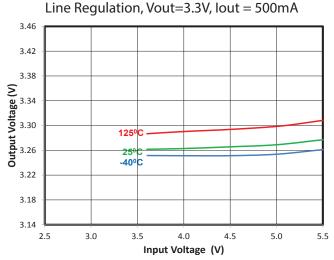

| Line Regulation             | $\Delta V_{\text{LINE-REG}}$   | Channel A & B; V <sub>IN</sub> = 2.75 – 5.5V                                 |      | ±0.2 |      | %/V   |

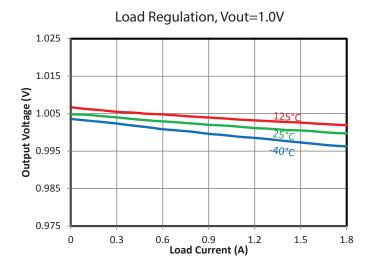

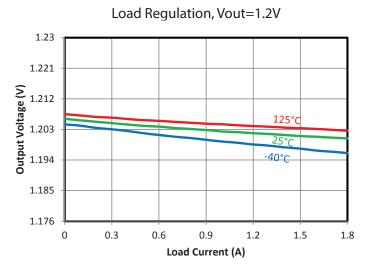

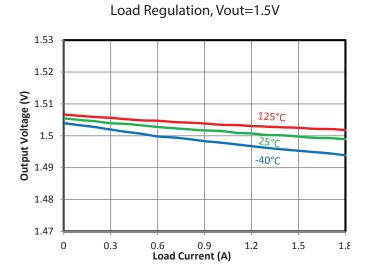

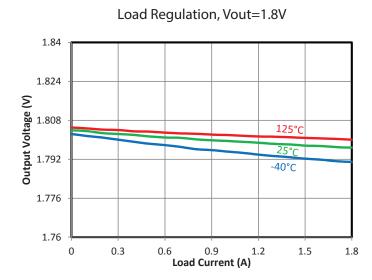

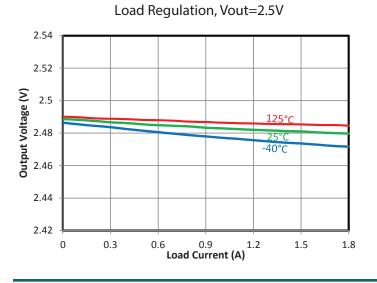

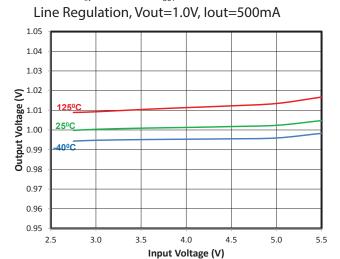

| Load Regulation             | $\Delta V_{_{LOAD	ext{-}REG}}$ | Channel A & B; V <sub>IN</sub> = 5.0V; I <sub>OUT</sub> = 0mA – 1.8A         |      | ±1   |      | %/A   |

| Current Limit Threshold     | I <sub>LIMIT</sub>             | Channel A & B; Peak LX current; Open loop DC Test                            | 2.2  | 3.0  | 3.9  | А     |

| Oscillator Frequency        | f <sub>osc</sub>               | Channel A & B                                                                | 2.0  | 2.5  | 3.0  | MHz   |

### **Electrical Characteristics (continued)**

| Parameter                                   | Symbol                | Conditions                                                                                                             | Min  | Тур  | Max | Units |

|---------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------|------|------|-----|-------|

|                                             |                       | Channel A & B; $V_{IN} = 5.5V$ ; LX = 0V; $CTL_{0.2} = GND$<br>$0^{\circ}C \le (T_A = T_J) \le +125^{\circ}C$          |      | -1   |     |       |

| LX Leakage Current <sup>(2)</sup>           | l <sub>eakLX</sub>    | Channel A & B; $V_{IN} = 5.5V$ ; LX = 5.0V; CTL <sub>0-2</sub> = GND<br>$0^{\circ}C \le (T_A = T_J) \le +125^{\circ}C$ |      | 1    | 10  | - μΑ  |

| Foldback Holding Current                    | I <sub>CL_HOLD</sub>  | Average LX Current                                                                                                     |      | 600  |     | mA    |

| High Side Switch Resistance <sup>(3)</sup>  | R <sub>DSON_P</sub>   | Channel A & B; $I_{LX}$ = 100mA, $T_{J}$ = 25 °C                                                                       |      | 116  |     | - mΩ  |

| Low Side Switch Resistance                  | R <sub>DSON_N</sub>   | Channel A & B; I <sub>LX</sub> = -100mA, T <sub>J</sub> = 25 °C                                                        |      | 103  |     | mcz   |

| CTLx Input Current <sup>(2)</sup>           | I <sub>CTLx_iN</sub>  | Channel A & B; $CTL_{0.2}$ =VIN or GND<br>$0^{\circ}C \le (T_A = T_J) \le +125^{\circ}C$                               | -2.0 |      | 2.0 | μΑ    |

| CTLx Input High Threshold                   | V <sub>CTLx_HI</sub>  | Channel A & B                                                                                                          | 1.7  |      |     | V     |

| CTLx Input Low Threshold                    | V <sub>CTLx_LO</sub>  | Channel A & B                                                                                                          |      |      | 0.4 | V     |

| Impedence of PGOOD Low                      | R <sub>PGOOD_LO</sub> | Channel A & B                                                                                                          |      | 8    |     | Ω     |

| PGOOD Threshold                             | V <sub>PG_TH</sub>    | Vout rising                                                                                                            |      | 90   |     | %     |

| DCOOD Dalay                                 | _                     | Asserted                                                                                                               |      | 2    |     | ms    |

| PGOOD Delay                                 | t <sub>PG_DLY</sub> - | PGOOD= Low                                                                                                             |      | 20   |     | μs    |

| PGOOD High-Level Output Leakage             | I <sub>OH-PG</sub>    | V <sub>PG</sub> =5V                                                                                                    |      | 0.05 |     | μΑ    |

| V <sub>out</sub> Over Voltage Protection    | V <sub>OVP</sub>      | Channel A & B                                                                                                          |      | 115  |     | %     |

| Thermal Shutdown Temperature <sup>(4)</sup> | T <sub>sD</sub>       | Channel A & B                                                                                                          |      | 160  |     | °C    |

| Thermal Shutdown Hysteresis <sup>(4)</sup>  | T <sub>SD_HYS</sub>   | Channel A & B                                                                                                          |      | 10   |     | °C    |

#### Notes:

- (1) The "Output Voltage Tolerance" includes output voltage accuracy, voltage drift over temperature.

- (2) A negative current means the current flows from the pin and a positive current means the current flows into the pin.

- (3) Measured from  $VIN_{A/B}$  to  $LX_{A/B}$ .

- (4) Thermal shutdown protection is independent for each channel.

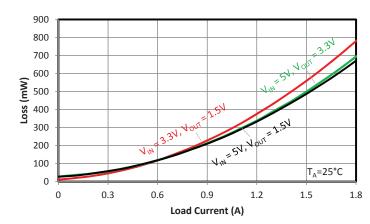

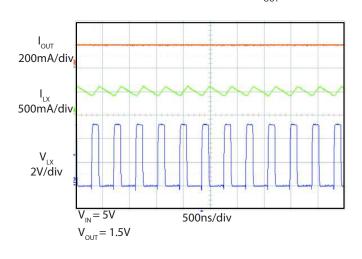

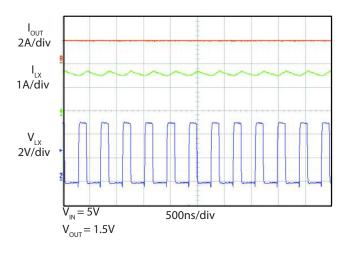

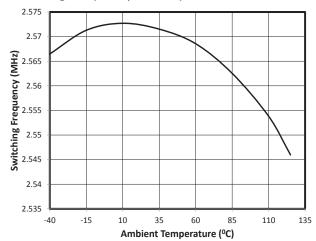

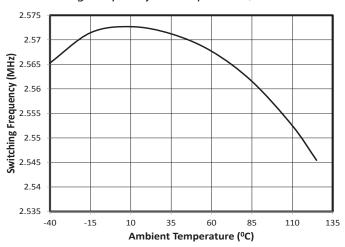

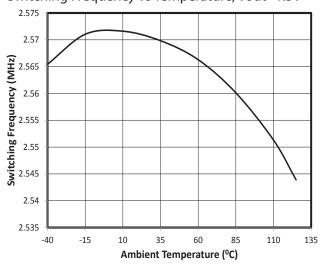

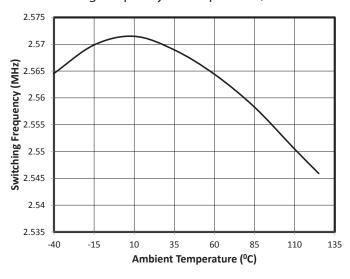

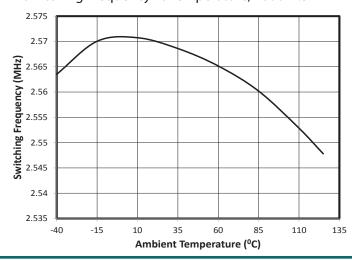

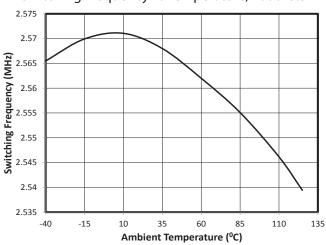

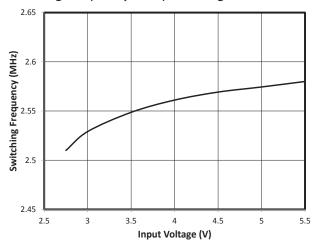

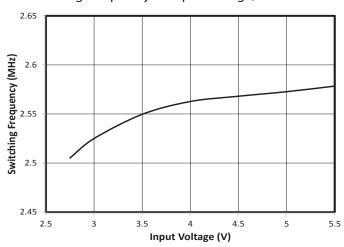

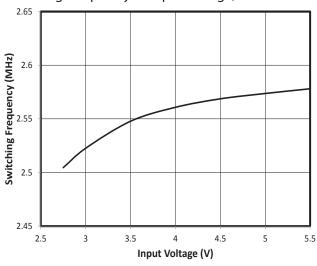

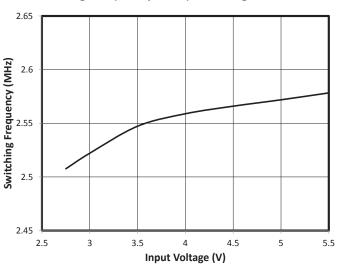

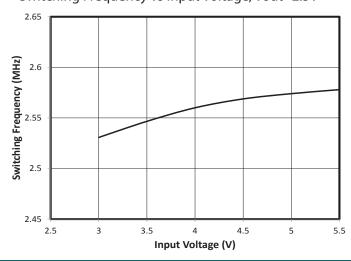

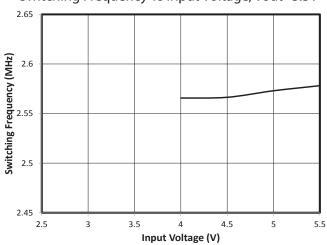

**Typical Characteristics** Circuit Conditions:  $C_{IN} = 10 uF/6.3 V$ ;  $C_{OUT} = 22 uF/6.3 V$ , Unless otherwise noted, L= 2.2 uH (Coilcraft: XFL4020-222ME).

#### Efficiency vs. Load Current

#### Total Loss (Per Channel) vs. Load Current

Steady State (PWM) Operation ( $I_{OUT}$ =200mA)

Steady State (PWM) Operation  $(I_{OUT}=2A)$

## **Typical Characteristics**

Circuit Conditions:  $C_{IN} = 10 uF/6.3V$ ;  $C_{OUT} = 22 uF/6.3V$ , Unless otherwise noted, L= 2.2uH (Coilcraft: XFL4020-222ME).

$\begin{tabular}{ll} \textbf{Typical Characteristics} \\ \textbf{Circuit Conditions: $C_{IN}$= $10uF/6.3V$; $C_{OUT}$= $22uF/6.3V$, Unless otherwise noted, $L=2.2uH$ (Coilcraft: XFL4020-222ME). } \end{tabular}$

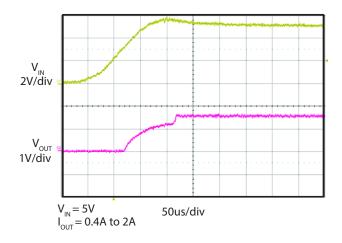

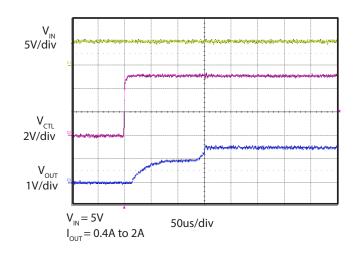

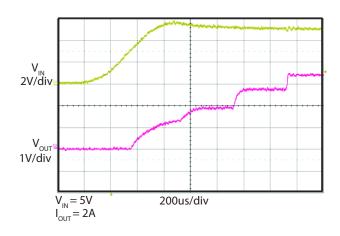

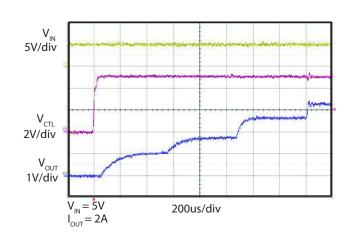

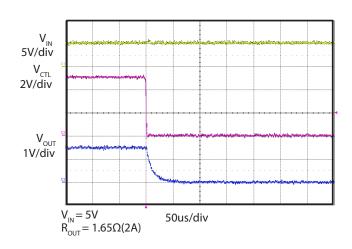

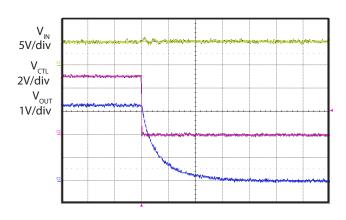

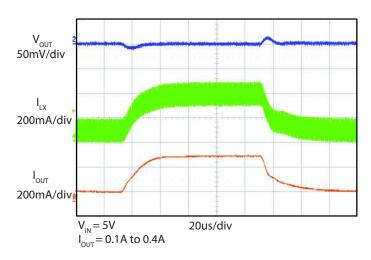

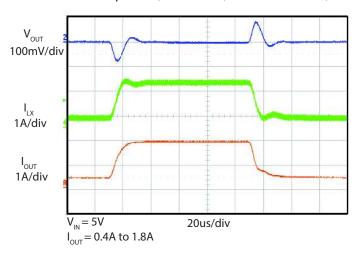

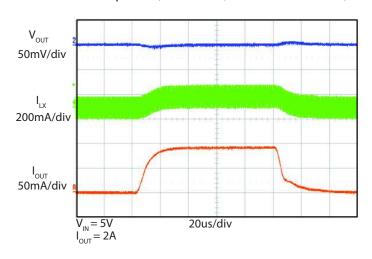

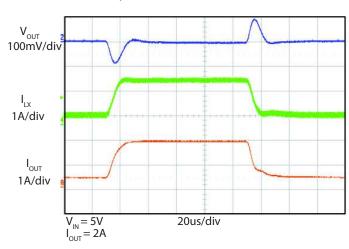

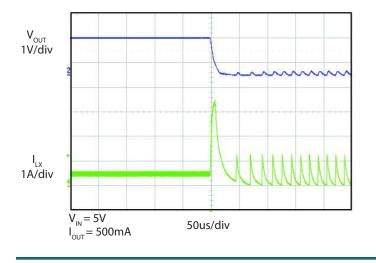

**Typical Waveforms** Circuit Conditions:  $C_{IN}$ = 10uF/6.3V;  $C_{OUT}$ = 22uF/6.3V, L= 2.2uH (Coilcraft: XFL4020-222ME).

Start Up (Power up  $V_{IN}=V_{CTLx}$ ) ( $V_{OUT}=1.5V$ )

Start Up (Power up

$$V_{IN}=V_{CTLx}$$

) ( $V_{OUT}=3.3V$ )

Start Up (Enable)  $(V_{OUT}=3.3V)$

Shutdown (Disable)(V<sub>OUT</sub>=1.5V)

Shutdown (Disable)( $V_{OUT}$ =3.3V)

$\begin{tabular}{ll} \textbf{Typical Characteristics} \\ \textbf{Circuit Conditions: $C_{IN}$= $10uF/6.3V$; $C_{OUT}$= $22uF/6.3V$, Unless otherwise noted, $L=2.2uH$ (Coilcraft: XFL4020-222ME). } \end{tabular}$

Switching Frequency Vs Temperature, Vout=1.0V

Switching Frequency Vs Temperature, Vout=1.2V

Switching Frequency Vs Temperature, Vout=1.5V

Switching Frequency Vs Temperature, Vout=1.8V

Switching Frequency Vs Temperature, Vout=2.5V

Switching Frequency vs Temperature, Vout=3.3V

**Typical Characteristics** Circuit Conditions:  $C_{IN} = 10 uF/6.3 V$ ;  $C_{OUT} = 22 uF/6.3 V$ , Unless otherwise noted, L = 2.2 uH (Coilcraft: XFL4020-222ME).

Switching Frequency Vs Input Voltage, Vout=1.0V

Switching Frequency Vs Input Voltage, Vout=1.2V

Switching Frequency Vs Input Voltage, Vout=1.5V

Switching Frequency Vs Input Voltage, Vout=1.8V

Switching Frequency Vs Input Voltage, Vout=2.5V

Switching Frequency vs Input Voltage, Vout=3.3V

$\begin{tabular}{ll} \textbf{Typical Waveforms} \\ \textbf{Circuit Conditions: C}_{IN} = 10 uF/6.3 V; C_{OUT} = 22 uF/6.3 V, L = 2.2 uH (Coilcraft: XFL4020-222 ME). \\ \end{tabular}$

Transient Response (Vout=1.5V, lout=0.1A to 0.4A)

Transient Response (Vout=1.5V, lout=0.4A to 2A)

Transient Response (Vout=1.5V, lout=0.01A to 0.1A)

Transient Response (Vout=3.3V, lout=0.4A to 2A)

Output Hard Short ( $V_{OUT}$ =1.5V)

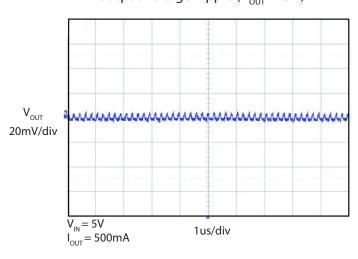

Output Voltage Ripple ( $V_{OUT}$ =1.5V)

## **Pin Descriptions**

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                                                                  |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PVINA    | Channel A — Input supply voltage for the converter power stage and internal circuitry.                                                                                                                                                                        |

| 2     | AGNDA    | Ground connection for internal circuitry — connect directly to PGNDA.                                                                                                                                                                                         |

| 3     | AVINA    | Power supply for internal circuitry — must be connected to PVINA using an R-C filter of $1\Omega$ and $10$ nF.                                                                                                                                                |

| 4     | PGOODA   | Power Good indicator for channel A. When the output voltage reaches the PGOODA threshold, this pin will be open drain (after the PGOOD delay), otherwise it is pulled low internally.                                                                         |

| 5     | CTL0A    | Channel A — Control bit 0, see Table 1 for decoding. This pin has a 1 M $\Omega$ internal pull-down resistor. This resistor is switched in circuit whenever the pin voltage is below the input high threshold, or when the part is in under-voltage lockout.  |

| 6     | CTL1A    | Channel A — Control bit 1, see Table 1 for decoding. This pin has a 1 M $\Omega$ internal pull-down resistor. This resistor is switched in circuit whenever the pin voltage is below the input high threshold, or when the part is in under-voltage lockout.  |

| 7     | CTL2A    | Channel A — Control bit 2, see Table 1 for decoding. This pin has a 1 M $\Omega$ internal pull-down resistor. This resistor is switched in circuit whenever the pin voltage is below the input high threshold, or when the part is in under-voltage lockout.  |

| 8     | VOUTB    | Output voltage sense pin of Channel B                                                                                                                                                                                                                         |

| 9     | PGNDB    | Channel B — Ground connection for converter power stage and internal circuitry.                                                                                                                                                                               |

| 10    | LXB      | Switching node of Channel B — connect an inductor between this pin and the output capacitor.                                                                                                                                                                  |

| 11    | PVINB    | Channel B — Input supply voltage for the converter power stage and internal circuitry.                                                                                                                                                                        |

| 12    | AGNDB    | Ground connection for internal circuitry — connect directly to PGNDB.                                                                                                                                                                                         |

| 13    | AVINB    | Power supply for internal circuitry — must be connected to PVINB using an R-C filter of $1\Omega$ and $10$ nF.                                                                                                                                                |

| 14    | PGOODB   | Power Good indicator for channel B. When the output voltage reaches the PGOODB threshold, this pin will be open drain (after the PGOOD delay), otherwise it is pulled low internally.                                                                         |

| 15    | CTLOB    | Channel B — Control bit 0, see Table 1 for decoding. This pin has a 1 M $\Omega$ internal pulld-own resistor. This resistor is switched in circuit whenever the pin voltage is below the input high threshold, or when the part is in under-voltage lockout.  |

| 16    | CTL1B    | Channel B — Control bit 1 - see Table 1 for decoding. This pin has a 1 M $\Omega$ internal pull-down resistor. This resistor is switched in circuit whenever the pin voltage is below the input high threshold, or when the part is in under-voltage lockout. |

| 17    | CTL2B    | Channel B — Control bit 2, see Table 1 for decoding. This pin has a 1 M $\Omega$ internal pull-down resistor. This resistor is switched in circuit whenever the pin voltage is below the input high threshold, or when the part is in under-voltage lockout.  |

| 18    | VOUTA    | Output voltage sense pin of Channel A                                                                                                                                                                                                                         |

| 19    | PGNDA    | Channel A — Ground connection for converter power stage and internal circuitry.                                                                                                                                                                               |

| 20    | LXA      | Switching node of Channel A — connect an inductor between this pin and the output capacitor.                                                                                                                                                                  |

|       | PAD      | Thermal pad for heatsinking purposes.                                                                                                                                                                                                                         |

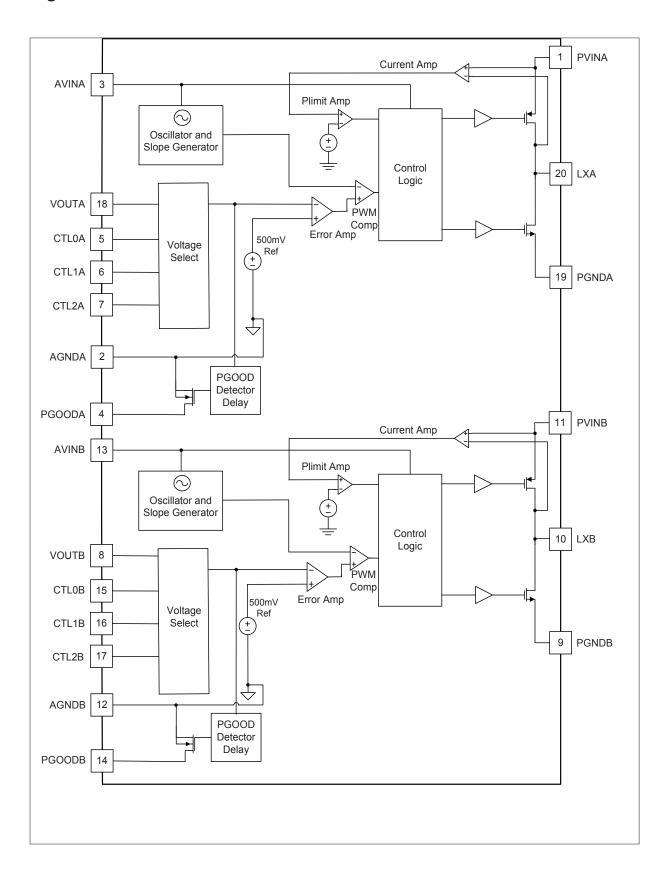

### **Block Diagram**

#### **Applications Information**

#### **Detailed Description**

The SC284AQ is a two channel synchronous step-down converter. Both channels of this device are designed to operate at a fixed-frequency of 2.5MHz in CCM and provide the same current capacity of up to 1.7A. The switching frequency is chosen to minimize the size of the external inductor and capacitors while maintaining high efficiency. Both channels of SC284AQ are independent.

#### Operation

During normal operation, the PMOS FET is activated on each rising edge of the internal oscillator. The voltage feedback loop uses an internal feedback resistor divider. The period is set by the internal oscillator. The device has an internal synchronous NMOS rectifier and does not require a Schottky diode on the LX pin.

#### **Programmable Output Voltage**

Both channels on SC284AQ have seven pre-determined output voltage values which can be individually selected by programming the CTL input pins (see Table 1 — Output Voltage Settings). Each CTL pin has an active 1 M $\Omega$  internal pull-down resistor. The  $1M\Omega$  resistor is switched in circuit whenever the CTL input voltage is below the input threshold, or when the part is in under-voltage lockout. It is recommended to tie all high CTL pins together and use an external pull-up resistor to  $V_{IN}$  if there is no enable signal, or if the enable input is an open drain/collector signal. The CTL pins may be driven by a microprocessor to allow dynamic voltage adjustment for systems that reduce the supply voltage when entering sleep states. Avoid all zeros being present on the CTL pins when changing programmable output voltages as this would momentarily disable the device.

SC284AQ is also capable of regulating a different (higher) output voltage, which is not shown in the Table 1, via an external resistor divider. There will be a typical  $2\mu A$  current flowing into the  $V_{OUT}$  pin. The typical schematic for an adjustable output voltage option from the standard 1.0V with CTL\_x=[001], is shown in Figure 1.  $R_{FB1A/B}$  and  $R_{FB2A/B}$  are used to adjust the desired output voltage. If the  $R_{FB2A/B}$  current is such that the  $2\mu A\,V_{OUT}$  pin current can be ignored, then  $R_{FB1A/B}$  can be found by the next equation.  $R_{FB2A/B}$  need to be low

enough in value for the current through the resistor chain to be at least  $20\mu A$  in order to ignore the  $V_{OUT}$  pin current.

$$R_{FB1} = \frac{V_{OUT} - V_{OSTD}}{V_{OSTD}} \times R_{FB2}$$

where  $V_{\text{OSTD}}$  is the pre-determined output voltage via the CTL pins.

$C_{\rm FF}$  is needed to maintain good transient response performance. The correct value of  $C_{\rm FF}$  can be found using the following equation.

$$C_{FF}[nF] = 2.5 \times \frac{(V_{OUT} - 0.5)^2}{R_{FB1}[k\Omega] \times (V_{OUT} - V_{OSTD})} \times \left(\frac{V_{OSTD}}{V_{OSTD} - 0.5}\right)$$

To simplify the design, it is recommended to program the desired output voltage from a standard 1.0V as shown in Figure 1 with the correct  $C_{\rm FF}$  calculated from Equation 2. For programming the output voltage from other standard voltages,  $R_{\rm FB1}$ ,  $R_{\rm FB2}$  and  $C_{\rm FF}$  need to be adjusted to meet Equations 1 and 2.

Figure 1 — Output Voltage Programming

#### **Power Good**

PGOOD is an open-drain output. When the output voltage drops below nominal voltage, the PGOOD pin is pulled low after a 20µs delay. During start-up, PGOOD will be asserted 2ms (typ.) after the output voltage reaches 90% of the final regulation voltage. Over voltage, fold-back current limit and thermal shutdown will force PGOOD low after a 20µs delay. When recovering from a fault, PGOOD will be asserted 2ms (typ.) after Vout reaches 90% of the final regulation voltage.

#### **Maximum Power Dissipation**

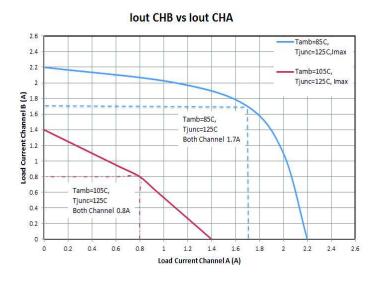

Each channel of SC284AQ has its own  $\Theta_{JA}$  of 40°C/W when only one channel is in operation. Since both channels are within the same package, please make sure to use both channels for power calculations. To guarantee an operating junction temperature of less than 125°C, Figure 2 shows the maximum allowable power loss for each channel. The curve is based upon the junction temperature of either channel reaching a maximum of 125°C. Each channel of SC284AQ can support up to 1.7A load current.

Figure 2 — Load current on dual channels for a maximum junction temperature of 125°C

#### **Protection Features**

The SC284AQ provides the following protection features:

- Current Limit

- Over-Voltage Protection

- Soft-Start

- Thermal Shutdown

#### **Current Limit**

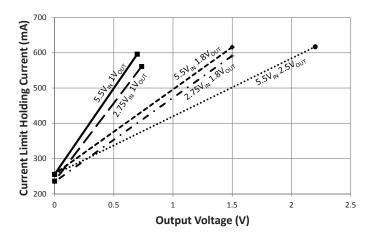

The internal PMOS power device in the switching stage is protected by a current limit feature. If the inductor current is above the PMOS current limit for 16 consecutive cycles, the part enters foldback current limit mode and the output current is limited to the current limit holding current (I<sub>CL\_HOLD</sub>) of a few hundred milliampere. Under this condition, the output voltage will be the product of I<sub>CL\_HOLD</sub> and the load resistance. The load presented must fall below the current limit holding current for the part to exit foldback current limit mode. Figure 3 shows how the typical current limit holding current varies with output voltage. The SC284AQ is capable of sustaining an indefinite short circuit without damage and will resume normal operation when the fault is removed. The foldback current limit mode is disabled during soft-start.

vs. Output Voltage

#### **Over-Voltage Protection**

In the event of a 15% over-voltage on the output, the PWM drive is disabled leaving the LX pin floating.

#### **Soft-Start**

Soft-start is activated once VIN reaches the UVLO and one or more CTL pins are set high to enable the part. A thermal shutdown event will also activate the soft-start sequence. Soft-start controls the maximum current during startup thus limiting inrush current. The PMOS current limit is

stepped through four soft-start levels of approximately 20%, 25%, 40%, & 100%. Each step is maintained for 400 $\mu$ s following an internal reference start up duration of 100 $\mu$ s giving a total nominal startup period of 1700 $\mu$ s. During startup, the chip operates by controlling the inductor current swings between 0A and current limit. If at any time  $V_{OUT}$  reaches 86% of the target or at the end of the soft-start period, the SC284AQ will switch to PWM mode operation.

The SC284AQ is capable of starting up into a pre-biased output.

#### **Shut Down**

When all CTL pins of a channel are low, the corresponding channel will be disabled, drawing less than  $1\mu A$  from that input power supply. The internal switches and bandgap voltage will be immediately turned off.

#### **Thermal Shutdown**

The device has a thermal shutdown feature to protect the SC284AQ if the junction temperature exceeds 160°C. During thermal shutdown, the on-chip power devices are disabled, tri-stating the LX output. When the temperature drops by 10°C, it will initiate a soft-start cycle to resume normal operation.

#### **Inductor Selection**

The SC284AQ converter has internal loop compensation. The compensation is designed to work with an output filter corner frequency of less than 40kHz for a  $V_{IN}$  of 5V and 50KHz for a  $V_{IN}$  of 3.3V over any operating condition. The corner frequency of the output filter is shown in the following equation.

$$f_C = \frac{1}{2\pi\sqrt{L \times C_{OUT}}}$$

Values outside this range may lead to instability, malfunction, or out-of-specification performance.

In general, the inductance is chosen by making the inductor ripple current to be less than 30% of maximum load current. When choosing an inductor, it is important to consider the change in inductance with DC bias current. The inductor saturation current is specified as the current at which the inductance drops a specific

percentage from the nominal value. This is approximately 30%. Except for short-circuit or other fault conditions, the peak current must always be less than the saturation current specified by the manufacturer. The peak current is the maximum load current plus one half of the inductor ripple current at the maximum input voltage. Load and/or line transients can cause the peak current to exceed this level for short durations. Maintaining the peak current below the inductor saturation specification keeps the inductor ripple current and the output voltage ripple at acceptable levels. Manufacturers often provide graphs of actual inductance and saturation characteristics versus applied inductor current. The saturation characteristics of the inductor can vary significantly with core temperature. Core and ambient temperatures should be considered when examining the core saturation characteristics.

When the inductance has been determined, the DC resistance (DCR) must be examined. The efficiency that can be achieved is dependent upon the DCR of the inductor. Lower values give higher efficiency. The RMS DC current rating of the inductor is associated with losses in the copper windings and the resulting temperature rise of the inductor. This is usually specified as the current which produces a 40°C temperature rise. Most copper windings are rated to accommodate this temperature rise above maximum ambient.

Magnetic fields associated with the output inductor can interfere with nearby circuitry. This can be minimized by the use of low noise shielded inductors which use the minimum gap possible to limit the distance that magnetic fields can radiate from the inductor. However shielded inductors typically have a higher DCR and are thus less efficient than a similarly sized non-shielded inductor. Final inductor selection depends upon various design considerations such as efficiency, EMI, size, and cost. Table 2 lists the manufacturers of recommended inductor options. The saturation characteristics and DC current ratings are also shown.

| Manufacturer<br>Part Number                   | L<br>(μH) | DCR<br>Max<br>(Ω) | Rated<br>Current<br>(A) | L at<br>Rated<br>Current<br>(μΗ) | Dimen-<br>sions<br>LxWxH<br>(mm) |

|-----------------------------------------------|-----------|-------------------|-------------------------|----------------------------------|----------------------------------|

| Coilcraft<br>XFL4020-222ME<br>AutomotiveGrade | 2.2±20%   | 0.023             | 3.1                     | 1.98                             | 4×4×2.10                         |

| TOKO<br>1071AS-1R0N                           | 1.00±30%  | 0.040             | 2.70                    | 0.70                             | 2.8x3.0x1.5                      |

| TOKO<br>1127AS-2R2M                           | 2.20±20%  | 0.048             | 2.50                    | 1.54                             | 3.5x3.7x1.8                      |

| Panasonic<br>ELLVGG1R0N                       | 1.00±23%  | 0.062             | 2.20                    | 0.70                             | 3.2x3.2x1.5                      |

Table 2 - Recommended Inductors

#### **C**<sub>OUT</sub> Selection

The internal voltage loop compensation in the SC284AQ limits the minimum output capacitor value to  $22\mu F$  if using a  $2.2\mu H$  inductor or  $44\mu F$  if using a  $1\mu H$  inductor. This is due to its influence on the the loop crossover frequency, phase margin, and gain margin. The total output capacitance should not exceed  $50\mu F$  to avoid any start-up problems. For most typical applications it is recommended to use an output capacitance of  $22\mu F$  to  $44\mu F$ . When choosing the output capacitor's capacitance, verify the voltage derating effect from the capacitor vendor's data sheet.

Capacitors with X7R or X5R ceramic dielectric are recommended for their low ESR and superior temperature and voltage characteristics. Y5V capacitors should not be used as their temperature coefficients make them unsuitable for this application.

The output voltage droop due to a load transient is determined by the capacitance of the ceramic output capacitor. The ceramic capacitor supplies the load current initially until the loop responds. Within a few switching cycles the loop will respond and the inductor current will increase to match the required load. The output voltage droop during the period prior to the loop responding can be related to the choice of output capacitor by the relationship from the following equation.

$$C_{OUT} = \frac{3 \times \Delta I_{LOAD}}{V_{DROOP} \times f_{OSC}}$$

The output capacitor RMS ripple current may be calculated from the following equation.

$$I_{COUT(RMS)} = \frac{1}{2\sqrt{3}} \left[ \frac{V_{OUT} \times (V_{IN(MAX)} - V_{OUT})}{L \times f_{OSC} \times V_{IN}} \right]$$

Table 3 lists the manufac turers of recommended capacitor options.

| Manufacturer<br>Part Nunber | Value<br>(μF) | Туре | Rated<br>Voltage<br>(VDC) | Value<br>at<br>3.3V<br>(μF) | Dimensions<br>LxWxH<br>(mm) |

|-----------------------------|---------------|------|---------------------------|-----------------------------|-----------------------------|

| Murata<br>GRM21BR60J106K    | 10±10%        | X5R  | 6.3                       | 4.74                        | 2.0x1.25x1.25<br>(EIA:0805) |

| Murata<br>GRM219R60J106K    | 10±10%        | X5R  | 6.3                       | 4.05                        | 2.0x1.25x0.85<br>(EIA:0805) |

| Murata<br>GRM21BR60J226M    | 22±20%        | X5R  | 6.3                       | 13.2                        | 2.0x1.25x1.25<br>(EIA:0805) |

| Murata<br>GRM31CR70J226K    | 22±10%        | X7R  | 6.3                       | 17.6                        | 3.2×1.6×1.6<br>(EIA:1206)   |

| Murata<br>GRM31CR60J476M    | 47±20%        | X5R  | 6.3                       | 20.3                        | 3.2x1.6x1.6<br>(EIA:1206)   |

Table 3 - Recommended Capacitors

### **C**<sub>IN</sub> Selection

The SC284AQ source input current is a DC supply current with a triangular ripple imposed on it. To prevent large input voltage ripple, a low ESR ceramic capacitor is required. A minimum value of  $10\mu F$  should be used. It is important to consider the DC voltage coefficient characteristics when determining the actual required value. It should be noted a  $10\mu F$ , 6.3V, X5R ceramic capacitor with 5V DC applied may exhibit a capacitance as low as  $4.05\mu F$ . To estimate the required input capacitor, determine the acceptable input ripple voltage and calculate the minimum value required for  $C_{\rm IN}$  as shown by the following equation.

$$C_{IN} = \frac{\frac{V_{OUT}}{V_{IN}} \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}{\left(\frac{\Delta V}{I_{OUT}} - ESR\right) \times f_{OSC}}$$

The input capacitor RMS ripple current varies with the input and output voltage. The maximum input capacitor RMS current is found from the next equation .

$$I_{\rm CIN(RMS)} = \sqrt{\frac{V_{\rm OUT}}{V_{\rm IN}} \bigg(1 - \frac{V_{\rm OUT}}{V_{\rm IN}}\bigg)}$$

The input voltage ripple and RMS current ripple are at a maximum when the input voltage is twice the output voltage or 50% duty cycle.

The input capacitor provides a low impedance loop for the edges of pulsed current drawn by the PMOS switch. Low ESR/ESL X5R ceramic capacitors are recommended for this function. To minimize stray inductance, the capacitor should be placed as close as possible to the VIN and GND pins of the SC284AQ.

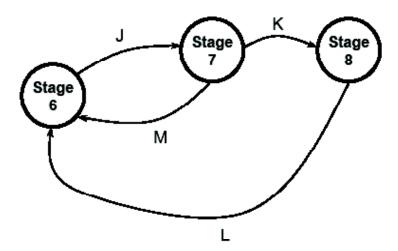

Figure 5 — Current Limit Protection

| Stages | Operation description                                                                                                                                                    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Soft start ends.                                                                                                                                                         |

| 6      | Normal PWM operation                                                                                                                                                     |

|        | Overload protection is enabled and peak current limit at 100% level                                                                                                      |

| 7      | Cycle by cycle peak current limit                                                                                                                                        |

| 8      | OCP protection is activated. foldback peak current limit. PWM "ON" when inductor current of 0A PWM "OFF" when inductor current hits peak current limit of foldback mode. |

| Conditions | Operation description                           |

|------------|-------------------------------------------------|

| J          | Inductor current hits peak current limit        |

| K          | Peak current limit for 16 consecutive cycles    |

| L          | Vout ≥ 100% target                              |

| М          | Inductor current doesn't hit peak current limit |

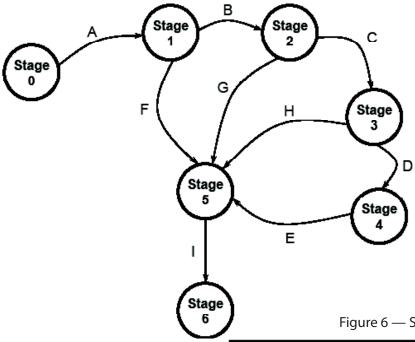

| Figure | 6 — | Soft | Start | Ope | ration |

|--------|-----|------|-------|-----|--------|

|--------|-----|------|-------|-----|--------|

| Stages | Operation description                                                                                                                                    |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0      | Chip is OFF.                                                                                                                                             |  |  |  |

| 1      | Peak current limit at 20% level PWM "ON" when inductor current of 0A PWM "OFF" when inductor current hits peak current limit Stage duration of 200µs     |  |  |  |

| 2      | Peak current limit at 25% level PWM "ON" when inductor current of 0A PWM "OFF" when inductor current hits peak current limit Stage duration of 200µs     |  |  |  |

| 3      | Peak current limit at 40% level PWM "ON" when inductor current of 500mA PWM "OFF" when inductor current hits peak current limit Stage duration of 200µs  |  |  |  |

| 4      | Peak current limit at 100% level PWM "ON" when inductor current of 500mA PWM "OFF" when inductor current hits peak current limit Stage duration of 200µs |  |  |  |

| 5      | Peak current limit at 100% level<br>Switch to closed-loop PWM operation.                                                                                 |  |  |  |

| 6      | Soft Start ends.<br>Normal PWM operation<br>Overload protection is enabled                                                                               |  |  |  |

| Conditions | Operation description                                                                              |  |  |

|------------|----------------------------------------------------------------------------------------------------|--|--|

| A          | VIN > UVLO Threshold<br>AND<br>One or more CTL pin is high.<br>AND<br>Internal reference is ready. |  |  |

| В          | End of stage 1 AND Vout<86% of target                                                              |  |  |

| С          | End of stage 2 AND Vout<86% of target                                                              |  |  |

| D          | End of stage 3 AND Vout<86% of target                                                              |  |  |

| E          | End of stage 4 AND Vout<86% of target                                                              |  |  |

| F          | Vout>86% of target                                                                                 |  |  |

| G          | Vout>86% of target                                                                                 |  |  |

| Н          | Vout>86% of target                                                                                 |  |  |

| I          | End of soft start time of 800µs                                                                    |  |  |

#### **PCB Layout Considerations**

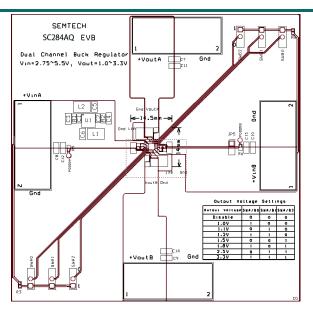

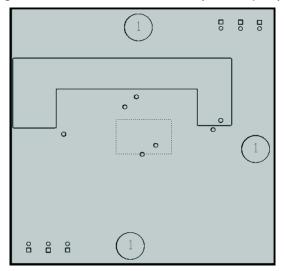

The layout diagram in Figure 7 shows a recommended PCB top layer for the SC284AQ and supporting components. Figure 8 shows the bottom layer for this PCB. Fundamental layout rules must be followed since the layout is critical for achieving the performance specified in the Electrical Characteristics table. Poor layout can degrade the performance of the DC-DC converter and can contribute to EMI problems, ground bounce, and resistive voltage losses. Poor regulation and instability can result. The following guidelines are recommended when developing a PCB layout:

- The input capacitor, C<sub>IN</sub>, should be placed as close to the VIN and PGND pins as possible. This capacitor provides a low impedance loop for the pulsed currents present at the buck converter's input. Use short wide traces to connect as closely to the IC as possible. This will minimize EMI and input voltage ripple by localizing the high frequency current pulses.

- Keep the LX pin traces as short as possible to minimize pickup of high frequency switching edges to other parts of the circuit. C<sub>OUT</sub> and L should be connected as close as possible between the LX and PGND pins, with a direct return to the PGND pin from C<sub>OUT</sub>.

- Route the output voltage feedback/sense path away from the inductor and LX node to minimize noise and magnetic interference.

- Use a ground plane referenced to the SC284AQ PGND pin. Use several vias to connect to the component side ground to further reduce noise and interference on sensitive circuit nodes.

- 5. If possible, minimize the resistance from the output and PGND pin to the load. This will reduce the voltage drop on the ground plane and improve the load regulation. It will also improve the overall efficiency by reducing the copper losses on the output and ground planes.

- 6. Connect the AGND pins to the thermal pad.

Figure 7 — Recommended PCB Layout (Top Layer)

Figure 8 — PCB Bottom Layer

Figure 9 — Recommended PCB Layout (Top Layer Details)

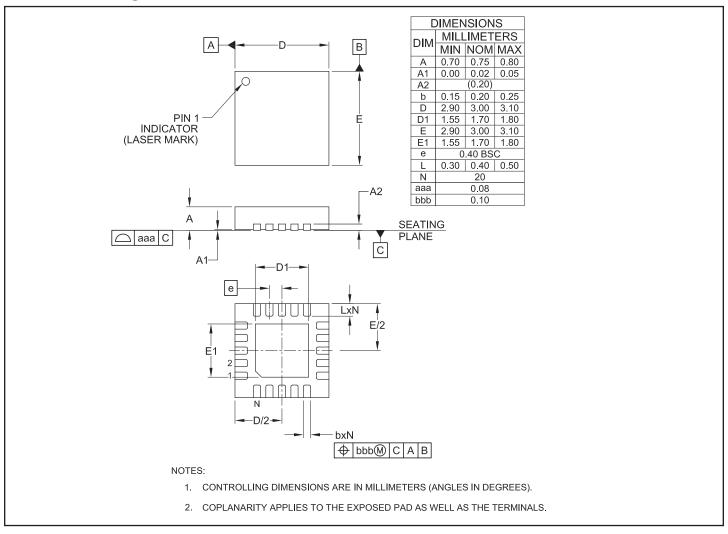

### Outline Drawing – 3x3 MLPQ-W

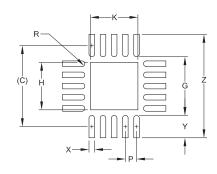

#### Land Pattern - 3x3 MLPQ-W

| DIMENSIONS |             |  |  |

|------------|-------------|--|--|

| DIM        | MILLIMETERS |  |  |

| С          | (2.90)      |  |  |

| G          | 2.10        |  |  |

| Н          | 1.70        |  |  |

| K          | 1.70        |  |  |

| Р          | 0.40        |  |  |

| R          | 0.10        |  |  |

| Х          | 0.20        |  |  |

| Υ          | 0.80        |  |  |

| Ζ          | 3.70        |  |  |

#### NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY.

CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR

COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 3. THERMAL VIAS IN THE LAND PATTERN OF THE EXPOSED PAD SHALL BE CONNECTED TO A SYSTEM GROUND PLANE. FAILURE TO DO SO MAY COMPROMISE THE THERMAL AND/OR FUNCTIONAL PERFORMANCE OF THE DEVICE.

#### © Semtech 2016

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY ATTHE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

#### **Contact Information**

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com