Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **SDA-2000**

### GaAs Distributed Amplifier

RFMD's SDA-2000 is a directly coupled (DC) GaAs microwave monolithic integrated circuit (MMIC) distributed driver amplifier die designed to support a wide array of high frequency commercial, military, and space applications. They are ideal for wideband amplifier gain blocks, modulators, clock drivers, broadband automated test equipment (ATE), military, and aerospace applications.

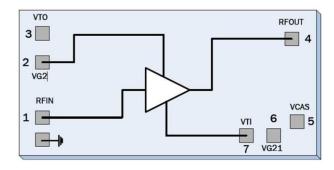

Functional Block Diagram

## **Ordering Information**

SDA-2000 GaAs Distributed Amplifier, GelPak, 10 pieces or more

SDA-2000SB Sample Bag, GaAs Distributed Amplifier, GelPak, 2 pieces

Package: Die, 3.1mm x 1.45mm x 0.102mm

#### **Features**

- DC to 22GHz Operation

- Output Voltage to 8V<sub>PP</sub>

- Gain = 12dB Typical

- Noise Figure = 5.5dB Typical

- 410mA Total Current

#### **Applications**

- Drive for Single-Ended (SE) MZM

- NRZ, DPSK, ODB, RZ

- Clock Driver for RZ and CS Pulse Carver

- Broadband ATE

- Military

- Aerospace

#### **Absolute Maximum Ratings**

| Parameter                                               | Rating                       | Unit     |

|---------------------------------------------------------|------------------------------|----------|

| Drain Bias Voltage (V <sub>DD</sub> )                   | +9.0                         | $V_{DC}$ |

| Gate Bias Voltage (V <sub>TI</sub> )                    | -2 to +1                     | $V_{DC}$ |

| Gate Bias Voltage (V <sub>G2</sub> )                    | ( $V_{DD}$ -8.0) to $V_{DD}$ | $V_{DC}$ |

| RF Input Power (V <sub>DD</sub> = +7.0V <sub>DC</sub> ) |                              | dBm      |

| Operating Junction Temperature (T <sub>J</sub> )        | +175                         | °C       |

| Continuous Power Dissipation (T = +85°C)                | 5                            | W        |

| Thermal Resistance (Pad to Die Bottom)                  | 17                           | °C/W     |

| Storage Temperature                                     | -40 to +150                  | °C       |

| Operating Temperature                                   | -40 to +85                   | °C       |

| ESD JESD22-A114 Human Body<br>Model (HBM)               | Class 0 (All Pads)           |          |

Caution! ESD sensitive device.

RFMD Green: RoHS compliant per EU Directive 2011/65/EU, halogen free per IEC 61249-2-21, <1000ppm each of antimony trioxide in polymeric materials and red phosphorus as a flame retardant, and <2% antimony solder.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

#### **Nominal Operating Parameters**

| Damandan                 | Sp  | Specification |     |                  |                                                                                      |  |

|--------------------------|-----|---------------|-----|------------------|--------------------------------------------------------------------------------------|--|

| Parameter                | Min | Тур           | Max | Unit             | Condition                                                                            |  |

| General Performance      |     |               |     |                  | $T_A = +25^{\circ}C$ , $V_{DD} = +8V$ , $V_{G2} = +3.5V_{DC}$ , $I_{DD} = 410mA^{*}$ |  |

| Operating Frequency      | DC  |               | 22  | GHz              | 3dB BW                                                                               |  |

| Gain                     |     | 12            |     | dB               | 10GHz                                                                                |  |

| Output Voltage           |     | 8             |     | V <sub>P-P</sub> |                                                                                      |  |

| OIP3 at Mid-Band         |     | 38            |     | dBm              | 10GHz                                                                                |  |

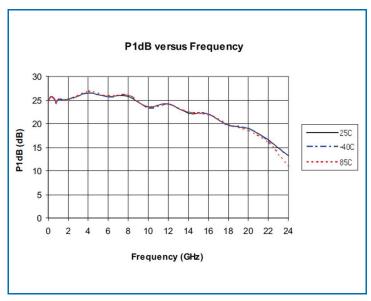

| P1dB at Mid-Band         |     | 24            |     | dBm              | 10GHz                                                                                |  |

| Noise Figure at Mid-Band |     | 6.0           |     | dB               | 10GHz                                                                                |  |

| Input Return Loss        |     | 20            |     | dB               |                                                                                      |  |

| Output Return Loss       |     | 17.5          |     |                  |                                                                                      |  |

| Supply Current           |     | 410           |     | mA               |                                                                                      |  |

| Supply Voltage           |     | 8.0           |     | $V_{DC}$         |                                                                                      |  |

<sup>\*</sup>Adjust VTI between -2.0 $V_{DC}$  to  $0V_{DC}$  to achieve  $I_{DD}$  = 410mA typical.

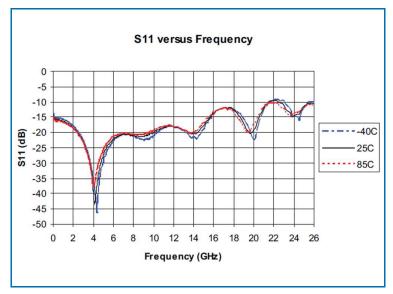

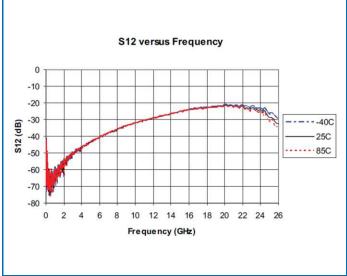

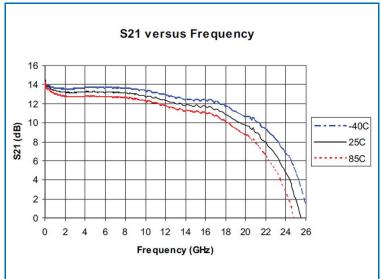

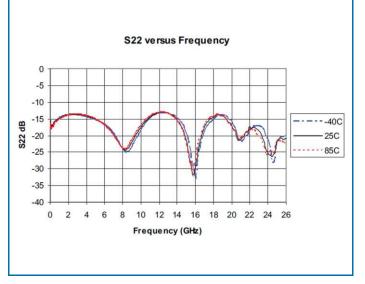

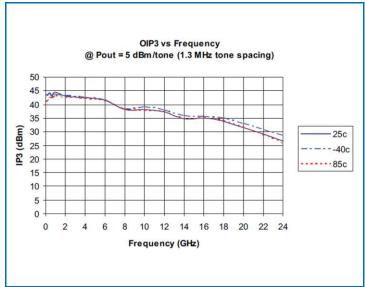

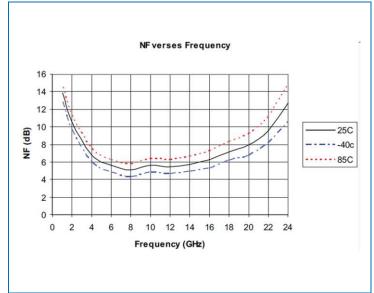

#### Typical Performance: $V_{DD} = 5.0V$ , $V_{G2} = 2.2V$

(See section at the end of the data sheet for measurement comments)

3 of 8

#### **Typical Performance (Continued)**

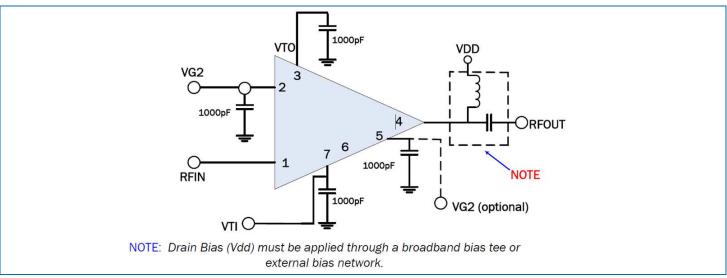

#### **Application Schematic**

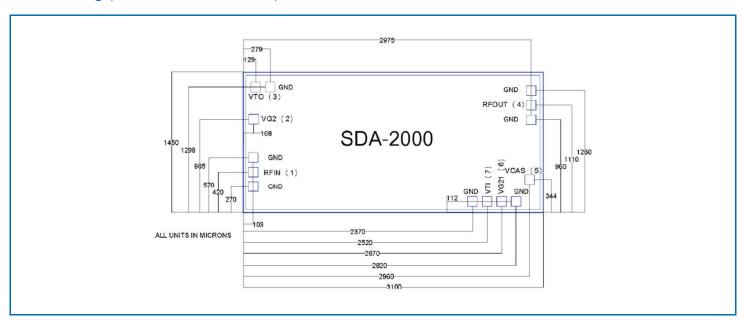

#### Die Drawing (Dimensions in microns)

#### Notes:

- 1. No connection required for unlabeled bond pads

- 2. Die thickness is 0.102mm (4mil)

- 3. Typical bond pad is 0.100mm square

- 4. Backside metallization: gold

- 5. Backside metal is ground

- 6. Bond pad metallization: gold

#### **Pin Names and Descriptions**

| Pin | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Interface Schematic                                                                                           |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 1   | RFIN             | RF Input. This pad is DC coupled and matched to $50\Omega$ from DC to 22GHz. $50\Omega$ microstrip transmission line on 0.127mm (5mil) thick alumina thin film substrate is recommended for RF input and output. A DC blocking capacitor is required for this connection. The calue of this capacitor will be based on the desired frequency range of application.                                                                                                                     | RFIN O                                                                                                        |

| 2   | VG2              | Each amplifier stage in the SDA-2000 is a cascade configuration. The gate of each upper FET in the cascade amplifiers is biased with the $3.5V_{\rm DC}$ (for $V_{\rm DD}=8V$ ). The DC connection for the upper device gates runs across the length of the die. Pads 2 and 5 are both on this DC connection but are on opposite ends of the die. The $V_{\rm G2}$ connection can therefore be placed on either pad. A bypass capacitor is recommended on both ends, pads 2 and 5.     | 1000 pF                                                                                                       |

| 3   | VTO              | The output drain termination pad. This pad requires a 1000pF bypass capacitor with the shortest wirebond length to prevent low frequency gain ripple.                                                                                                                                                                                                                                                                                                                                  | 1000 pF                                                                                                       |

| 4   | RFOUT and<br>VDD | RF Output. $50\Omega$ microstrip transmission line on 0.127mm (5mil) thick alumina thin film substrate is recommended for RF input and output. Connect the DC bias ( $V_{DD}$ ) network to provide drain current ( $I_{DD}$ ). Note: Drain Bias ( $V_{DD}$ ) must be applied through a broadband bias tee or external bias network.                                                                                                                                                    | VDD  VDD  RFOUT  Note: Drain Bias (VDD) must be applied through a broadband bias tee or external bias network |

| 5   | VCAS             | Each amplifier stage in the SDA-2000 is a cascade configuration. The gate of each upper FET in the cascade amplifiers is biased with the 3.5V $_{\rm DC}$ (for V $_{\rm DD}$ = 8V). The DC connection for the upper device gates runs across the length of the die. Pads 2 and 5 are both on this DC connection but are on opposite ends of the die. The V $_{\rm G2}$ connection can therefore be placed on either pad. A bypass capacitor is recommended on both ends, pads 2 and 5. | 1000 pF                                                                                                       |

| 6   | VG21             | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                               |

| 7   | VTI              | Input gate voltage for the lower devices in the cascade amplifier. This pad also serves as the RF ground for the input termination resistor. The DC voltage applied to this pad will be between -2.0V $_{\rm DC}$ (device is pinched OFF) to 0V $_{\rm DC}$ (fully ON). The value of this capacitor will effect the low frequency response of the amplifier.                                                                                                                           | 1000 pF 👤                                                                                                     |

| Die | GND              | Ground connection. Connect die bottom directly to ground plane for best performance. NOTE: The die should be connected directly to the ground plane with conductive epoxy.                                                                                                                                                                                                                                                                                                             |                                                                                                               |

#### **Bias Sequence (Turn Device On):**

VTI - Apply negative -2.0 volts. (This shuts the device off.)

VG2 - Apply positive 3.5 volts.

VDD - Apply positive 8.0 volts to the RF output bias tee.

Important - Adjust VTI between -2 to +1.0 volts to achieve IDD = 410mA nominal.

#### **Bias Sequence (Turn Device Off):**

VTI - Return to negative -2.0 volts.

VDD - Remove positive 8.0 volts to the RF output bias tee.

VG2 - Remove positive 3.5 volts.

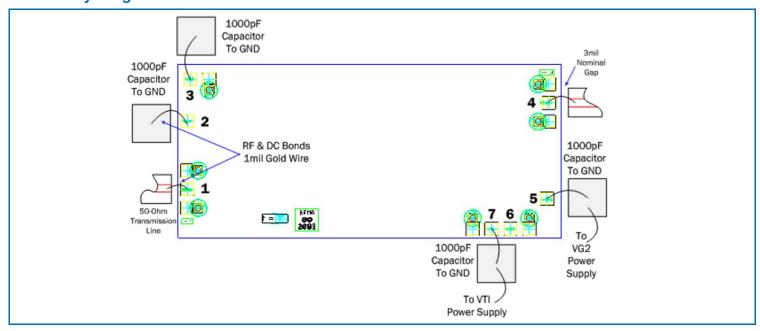

#### **Assembly Diagram**

#### **Measurement Technique**

All data presented in this document represents the integrated circuit and accompanying bond wires.

All performance data reported in this document were measured in the following manner. Data was taken using a temperature controlled probe station utilizing 150µm pitch GSG probes. The interface between the probes and integrated circuit was made with a coplanar to microstrip ceramic test interface. The test interface was wire bonded to the die using 1mil diameter bondwires. The spacing between the test interface and the die was 200µm, and the bond wire loop height was 100µm. The calibration of the test fixture included the probes and test interfaces, so that the measurement reference plane was at the point of bond wire attachment to the ceramic interface.

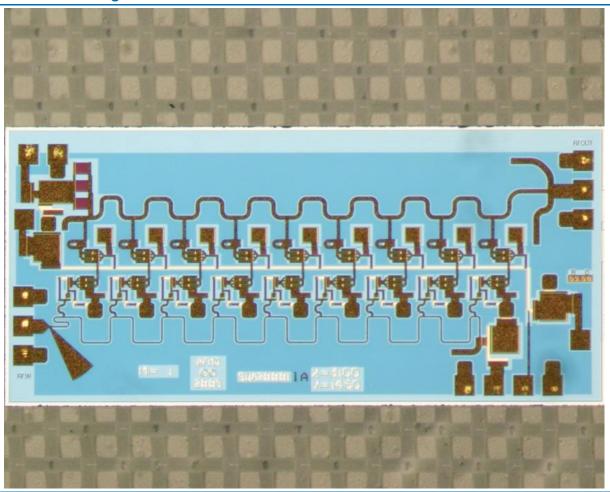

#### **SDA-2000 Product Image**