# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

SDIO101A SD/SDIO/MMC/CE-ATA host controller Rev. 1 — 13 June 2013

**Product data sheet**

## 1. General description

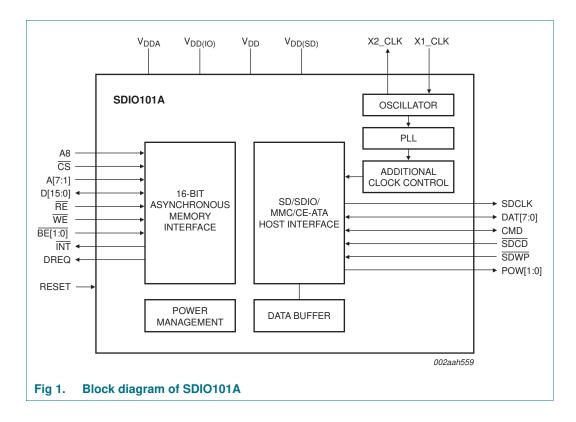

The SDIO101A is a SD/SDIO/MMC/CE-ATA host controller with a standard 16-bit asynchronous memory interface. The device conforms to the *SD Host Standard Specification Version 2.0* (see <u>Ref. 1</u>). The SDIO101A manages the physical layer of SD, SDIO, MMC and CE-ATA protocols and can be used together with SD Host Standard compatible driver software to add SD/SDIO/MMC/CE-ATA host functionality to a variety of microprocessor systems.

The SDIO101A supports both full-speed (< 25 MHz) and high-speed (< 52 MHz) data transmissions on the SD/SDIO/MMC/CE-ATA port. The SDIO101A offers separate pins for SD/SDIO/MMC/CE-ATA port supply voltage, host interface supply voltage and core supply voltage. The SD/SDIO/MMC/CE-ATA port can operate at a wide voltage range (1.8 V to 3.6 V) which allows the device to interface to a large variety of SD, SDIO, MMC or CE-ATA devices. The SDIO101A allows 1-bit and 4-bit SD transactions and 8-bit MMC/CE-ATA transactions. The 16-bit asynchronous memory interface can operate at a 2.5 V to 3.6 V voltage range.

A built-in, 2 kB data buffer allows for a low interrupt latency time and efficient communication with the host processor at high data rates. The SDIO101A provides a DMA request line that can be connected to an external DMA controller to off-load the host processor and increase overall system performance.

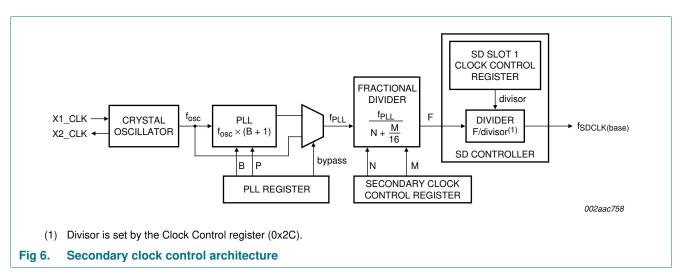

An on-board PLL allows a large range of SD/SDIO/MMC/CE-ATA clock speeds to be generated from a single externally available clock source. An additional fractional divider allows the SD clock speed to be fine-tuned with very fine granularity, which enables the user to achieve the maximum desired SD clock speed from the external clock source.

The SDIO101A offers 5 levels of power saving, including a 'Hibernate mode' where the on-board oscillator, PLL and data buffer memories are switched off, and a 'Coma mode' in which supply power to most of the device is internally switched off. This allows the device to be used in very power-critical applications.

## 2. Features and benefits

#### 2.1 General

- Provides 1 SD/SDIO/MMC/CE-ATA slot, operating in 1-bit, 4-bit and 8-bit (MMC/CE-ATA) modes

- 2.5 V to 3.3 V host interface

- 1.8 V core supply voltage

- Separate SD supply voltage pin. SD/SDIO/MMC/CE-ATA slot is able to operate at a wide voltage range (1.8 V to 3.3 V).

#### SD/SDIO/MMC/CE-ATA host controller

- Compliant with *SDIO card specification version 2.00* (see <u>Ref. 2</u>)

- Compliant with SD Host Controller Standard Specification Version 2.0 (see Ref. 1)

- Compliant with SD Physical Layer Specification version 2.0 (see Ref. 3)

- Compliant with MMC Specification version 3.31 and 4.2 (see Ref. 4)

- Supports CE-ATA Digital Protocol revision 1.1 (see <u>Ref. 5</u>)

- Supports CE-ATA Digital Protocol commands (CMD60/CMD61)

- Dedicated SD Card Detection input pin (insertion/removal)

- Dedicated SD Card Write Protection input pin

- Full speed (< 25 MHz) and high-speed (< 52 MHz) SD data transmissions

- Supports interrupt and slave-DMA transfer operation

- Built-in 2 kB double data buffer (with 1 kB maximum block size) for efficient communication with host processor

- Supports SDIO features Multi-block, Suspend/Resume, Read Wait and Wake-up Control

- Up to 400 Mbit/s read and write data transfer rates at 50 MHz using MMC 8 data lines

- Up to 208 Mbit/s read and write data transfer rates at 52 MHz using SD 4 data lines

- On-board crystal oscillator and PLL

- 5 levels of power saving, including a 'Hibernate mode' where oscillator, PLL and memories are switched off, and a 'Coma mode' that internally switches off supply power to most of the chip

- Additional on-board fractional clock divider for fine-grained SD clock speed control

- Cyclic Redundancy Check (CRC) for command and data

- Programmable pull-up resistor on SD CMD and SD DATn lines

- Programmable drive strength for SDCLK output to optimize SD/SDIO/MMC/CE-ATA clock speed

#### 2.2 Host processor interface

- Supports 16-bit asynchronous memory interface

- Separate host interface power supply pin, able to operate on 2.5 V to 3.3 V

- Programmable open collector or push-pull mode for INT interrupt pin output

## 3. Ordering information

| Table 1. Ordering information               |         |         |                                                                                                                               |           |  |  |

|---------------------------------------------|---------|---------|-------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Type number         Topside         Package |         |         |                                                                                                                               |           |  |  |

|                                             | marking | Name    | Description                                                                                                                   | Version   |  |  |

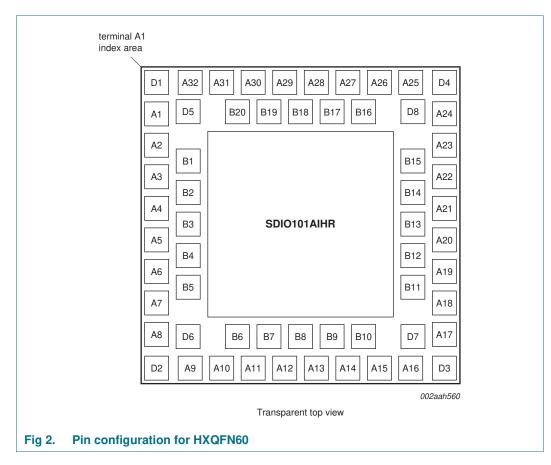

| SDIO101AIHR                                 | D101A   | HXQFN60 | plastic compatible thermal enhanced extremely thin quad flat package; no leads; 60 terminals; body $5 \times 5 \times 0.5$ mm | SOT1133-2 |  |  |

## 3.1 Ordering options

| Table 2. Orde | ering options            |         |                                                       |                              |                                                    |

|---------------|--------------------------|---------|-------------------------------------------------------|------------------------------|----------------------------------------------------|

| Type number   | Orderable<br>part number | Package | Packing method                                        | Minimum<br>order<br>quantity | Temperature                                        |

| SDIO101AIHR   | SDIO101AIHRZ             | HXQFN60 | Reel 7" Q1/T1 *standard mark dry<br>pack              | 1500                         | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

| SDIO101AIHR   | SDIO101AIHRE             | HXQFN60 | Standard marking<br>* Tray dry pack, bakeable, single | 490                          | $T_{amb} = -40 \text{ °C to } +85 \text{ °C}$      |

## 4. Block diagram

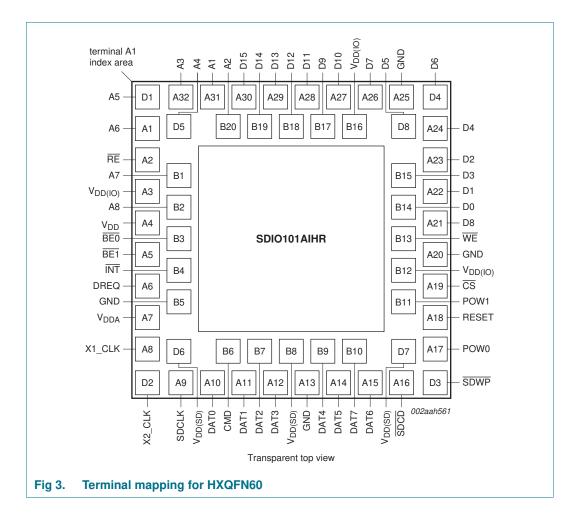

# 5. Pinning information

## 5.1 Pinning

#### SD/SDIO/MMC/CE-ATA host controller

SDIO101A Product data sheet

### 5.2 Pin description

#### 5.2.1 Pin description by function

Following are the signal descriptions on the SDIO101A interfaces. Pins are organized by function.

|           |          | <pre>ption by function put; O = output; n.</pre> | c. = not connected.                        |

|-----------|----------|--------------------------------------------------|--------------------------------------------|

| Symbol    | Pin      | Туре                                             | Description                                |

| SD/SDIO/M | MC/CE-AT | A interface signa                                | lls                                        |

| SDCLK     | 40       | 0                                                | SD alook output. This output alook is driv |

| SDCLK       | A9                  | 0          | <b>SD clock output.</b> This output clock is driven by the host controller during read and write transactions.                                                                    |

|-------------|---------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD         | B6                  | В          | <b>SD command line.</b> This bidirectional signal is used to transfer commands and responses between the host and the card.                                                       |

| DAT0        | A10                 | В          | SD Data bit 0.                                                                                                                                                                    |

| DAT1        | A11                 | В          | SD Data bit 1.                                                                                                                                                                    |

| DAT2        | B7                  | В          | SD Data bit 2.                                                                                                                                                                    |

| DAT3        | A12                 | В          | SD Data bit 3.                                                                                                                                                                    |

| DAT4        | B9                  | В          | SD Data bit 4.                                                                                                                                                                    |

| DAT5        | A14                 | В          | SD Data bit 5.                                                                                                                                                                    |

| DAT6        | A15                 | В          | SD Data bit 6.                                                                                                                                                                    |

| DAT7        | B10                 | В          | SD Data bit 7.                                                                                                                                                                    |

| SDCD        | A16                 | Ι          | <b>SD card detect (active LOW).</b> This pin can be used to detect insertion and removal of SD/SDIO/MMC cards.                                                                    |

| SDWP        | D3                  | I          | <b>SD write protect (active LOW).</b> This pin can be used to detect if the inserted SD/SDIO/MMC card is write protected.                                                         |

| System inte | erface signals      |            |                                                                                                                                                                                   |

| X1_CLK      | A8                  | Ι          | <b>Clock input.</b> Must be connected to the system clock which is used to generate the host bus interface (see Section 6.4.3.1).                                                 |

| X2_CLK      | D2                  | 0          | Clock output.                                                                                                                                                                     |

| RESET       | A18                 | Ι          | Asynchronous reset (active HIGH). This active HIGH input pin unconditionally resets the entire device.                                                                            |

| Card powe   | r supply control ir | nterface s | signals                                                                                                                                                                           |

| POW[1:0]    | B11, A17            | 0          | <b>SD power supply control bits.</b> These bits can be used to control the voltage of an external power supply for the SD/SDIO/MMC/CE-ATA device. See <u>Table 5</u> for details. |

#### SD/SDIO/MMC/CE-ATA host controller

| Symbol              | Pin                                                                                      | Туре | Description                                                                                                                                                                                                                       |

|---------------------|------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interfa        | ace control signals                                                                      |      |                                                                                                                                                                                                                                   |

| CS                  | A19                                                                                      | I    | Chip Select (active LOW).                                                                                                                                                                                                         |

| A[7:1]              | B1, A1, D1, D5,<br>A32, B20, A31                                                         | I    | <b>Address lines.</b> Can be used to address the 256 bytes of the Standard Host register space.                                                                                                                                   |

| A8                  | B2                                                                                       | I    | Address 8. When accessing SDIO101A transmit or receive buffer under DMA control, this pin must be HIGH. This pin must be LOW when accessing other registers or when accessing transmit or receive buffer under interrupt control. |

| D[15:0]             | A30, B19, A29,<br>B18, A28, A27,<br>B17, A21, A26,<br>D4, D8, A24, B15,<br>A23, A22, B14 | В    | <b>Data lines.</b> Used to transfer data between host controller and the processor.                                                                                                                                               |

| RE                  | A2                                                                                       | I    | <b>Read Enable (active LOW).</b> Initiates a read transactio when active.                                                                                                                                                         |

| WE                  | B13                                                                                      | I    | Write Enable (active LOW). Initiates a write transactio when active.                                                                                                                                                              |

| BE[1:0]             | A5, B3                                                                                   | I    | Byte write enables (active LOW). When $\overline{BE[0]}$ is active, the least significant byte on the data bus can be written. When $\overline{BE[1]}$ is active, the most significant byte on the data bus can be written.       |

| INT                 | B4                                                                                       | 0    | Interrupt request (active LOW). Can be configured as push/pull or open-collector output.                                                                                                                                          |

| DREQ                | A6                                                                                       | 0    | DMA request.                                                                                                                                                                                                                      |

| Power inte          | rface signals                                                                            |      |                                                                                                                                                                                                                                   |

| V <sub>DD</sub>     | A4                                                                                       | -    | Core power supply pin, 1.8 V.                                                                                                                                                                                                     |

| V <sub>DDA</sub>    | A7                                                                                       | -    | Analog power supply, 1.8 V.                                                                                                                                                                                                       |

| V <sub>DD(SD)</sub> | D6, B8, D7                                                                               | -    | SD power supply pins, 1.8 V to 3.3 V.                                                                                                                                                                                             |

| V <sub>DD(IO)</sub> | B12, B16, A3                                                                             | -    | Host interface power supply pins, 2.5 V to 3.3 V.                                                                                                                                                                                 |

| GND                 | B5, A13, A20,<br>A25 <mark>11</mark>                                                     | -    | Ground.                                                                                                                                                                                                                           |

| GND                 | center pad <sup>[1]</sup>                                                                | -    | Ground.                                                                                                                                                                                                                           |

#### **Table 3.** Pin description by function ... continued $B = bidirectional: I = input: \Omega = output: n.c. = not connected.$

[1] HXQFN60 package die supply ground is connected to both GND pins and exposed center pad. GND pins must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias need to be incorporated in the PCB in the thermal pad region.

## 6. Functional description

The SDIO101A offers the SD Standard Host register set as defined in the *SD Host Standard Specification Version 2.0* (see <u>Ref. 1</u>), through which the Host Driver software can configure the host controller and initiate transactions to and from an SD/SDIO/MMC/CE-ATA target. On top of the Standard Host registers, 4 extra registers are available in the Host Controller register space, which can be used to control the additional features in the SDIO101A. These features are described in detail in <u>Section 6.4</u>. <u>Section 6.2</u> gives an overview of the SDIO101A register set.

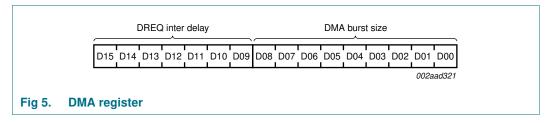

#### 6.1 DMA mode

The SDIO101A supports slave DMA where the transferring of data between the host and the SDIO101A is under the control of the host's DMA controller. In this mode, the software can program DMA burst size (number of 16-bit words per DMA cycle) as well as the delay between back-to-back DMA requests from SDIO101A.

In DMA mode, Buffer Data Port 0 (0x20) and Buffer Data Port 1 (0x22) are mapped differently than in Interrupt mode — address line A8 must be at logic 1 when Buffer Data Ports are being accessed while the rest of the address lines are ignored by the SDIO101A. Once the DMA operation starts, all the accesses to the SDIO101A with A8 set to logic 1 will be considered as Buffer Data Ports access. To access other SDIO101A internal registers, address A8 must be set to logic 0.

The total number of DMA accesses to the Buffer Data Ports must be an even number. The first access from the host will be to Buffer Data Port 0, and the second access will be to Buffer Data Port 1. The SDIO101A will automatically alternate between Buffer Data Port 0 and Buffer Data Port 1 on each access by the host. This scheme allows the SDIO101A Buffer Data Ports to look like a continuous block of memory or FIFO to the DMA controller.

There are two registers that must be programmed for the SDIO101A to support DMA operation:

- Miscellaneous register (0xF8) bit 1 (enable slave DMA) must be set to logic 1.

- DMA burst size and DMA inter delay (back-to-back DREQs) must be programmed through DMA register (0xF4). DMA register bit [8:0] programs the DMA burst size (the number of 16-bit words to be transferred between the DMA controller and the SDIO101A), and DMA register bit [15:9] programs the delay time between two back-to-back DMA requests from SDIO101A (the inter delay value in bit [15:9] represents the number of SD clocks).

#### 6.1.1 DMA read

When the receive buffer is empty, DREQ is at LOW state. Once the receive buffer has at least the number of 16-bit words equal to the programmed DMA burst size (DMA register [8:0]) DREQ goes HIGH. The DMA controller then can perform a block read of the receive buffer with the block size equal to the programmed DMA burst size in the DMA register.

The DREQ will go LOW once a block of data has been read from the SDIO101A's receive buffer, and DREQ will remain LOW for a period defined by DMA register bit [15:9]. The DREQ signal will go HIGH again if the receive buffer still holds at least the burst size of 16-bit word data.

#### 6.1.2 DMA write

When the transmit buffer is empty, DREQ is at HIGH state. The DMA controller then can perform a block write to the receive buffer with the block size equal to the programmed DMA burst size programmed in DMA register [9:0].

The DREQ will go LOW once a block of data has been written to the SDIO101A's transmit buffer, and DREQ will remain LOW for a period defined by DMA register bit [15:9]. The DREQ signal will go HIGH again if the transmit buffer still has space to hold at least the burst size of 16-bit word data.

#### 6.2 Standard Host register overview

| Offset                | Bits 15:8                     | Bits 7:0                                | Offset  | Bits 15:8                      | Bits 7:0        |

|-----------------------|-------------------------------|-----------------------------------------|---------|--------------------------------|-----------------|

| 0x02                  | System Address (              | high)                                   | 0x00    | System Address                 | (low)           |

| 0x06                  | Block Count                   |                                         | 0x04    | Block Size                     |                 |

| 0x0A                  | Argument1                     |                                         | 0x08    | Argument0                      |                 |

| 0x0E                  | Command                       |                                         | 0x0C    | Transfer Mode                  |                 |

| 0x12                  | Response1                     |                                         | 0x10    | Response0                      |                 |

| 0x16                  | Response3                     |                                         | 0x14    | Response2                      |                 |

| 0x1A                  | Response5                     |                                         | 0x18    | Response4                      |                 |

| 0x1E                  | Response7                     |                                         | 0x1C    | Response6                      |                 |

| 0x22                  | Buffer Data Port1             |                                         | 0x20    | Buffer Data Port               | 0               |

| 0x26                  | Present State                 |                                         | 0x24    | Present State                  |                 |

| 0x2A                  | Wake-up Control               | Block Gap Control                       | 0x28    | Power Control                  | Host Contro     |

| 0x2E                  | Software Reset                | Time-out Control                        | 0x2C    | Clock Control                  |                 |

| 0x32                  | Error Interrupt Sta           | tus                                     | 0x30    | Normal Interrupt Status        |                 |

| 0x36                  | Error Interrupt Sta           | tus Enable                              | 0x34    | Normal Interrupt Status Enable |                 |

| 0x3A                  | Error Interrupt Sig           | nal Enable                              | 0x38    | Normal Interrupt Signal Enable |                 |

| 0x3E                  | reserved                      |                                         | 0x3C    | Auto CMD12 Erro                | or Status       |

| 0x42                  | Capabilities                  |                                         | 0x40    | Capabilities                   |                 |

| 0x46                  | Capabilities (reser           | rved)                                   | 0x44    | Capabilities (rese             | erved)          |

| 0x4A                  | Maximum Current               | Capabilities                            | 0x48    | Maximum Currer                 | nt Capabilities |

| 0x4E                  | Maximum Current<br>(reserved) | Maximum Current Capabilities (reserved) |         | Maximum Currer<br>(reserved)   | nt Capabilities |

| 0x52                  | (reserved)                    |                                         | 0x50[1] | IO-cell Configura              | tion            |

| -                     | -                             |                                         | -       | -                              |                 |

| 0xF6 <mark>[1]</mark> | Secondary Clock               | Control                                 | 0xF4[1] | DMA register                   |                 |

| 0xFA[1]               | PLL                           |                                         | 0xF8[1] | Miscellaneous                  |                 |

| 0xFE                  | Host Controller Ve            | ersion                                  | 0xFC    | Slot Interrupt Sta             | tus             |

#### Table 4. SD Host Controller register map

[1] This register is not part of the Standard Host register set.

#### 6.3 Standard Host register set description

The SDIO101A registers that are part of the Standard Host register set are described in detail in <u>Ref. 1</u>. In this paragraph, we will only describe the specific implementation of the Standard register set in the SDIO101A that are different from <u>Ref. 1</u>.

#### 6.3.1 System Address register (offset 0x00)

Since master-DMA functionality is not implemented, all bits in this register will always read zero. Writes to this register will be ignored.

#### 6.3.2 Block Size register (offset 0x04)

Data written to bits R[14:12] will be ignored. The maximum block size that can be programmed is 1 kB. Any block size higher than that will default to 1 kB.

#### 6.3.3 Transfer Mode register (offset 0x0C)

Since master-DMA functionality is not implemented, bit R[00] will always read zero. Writes to this bit will be ignored.

#### 6.3.4 Present State register (offset 0x24)

The SDIO101A supports multiple buffers, that is, the available data buffer space (2 kB) is larger than the Maximum Block Size (1 kB). The Buffer Write Enable bit R[10] indicates that there is room to write at least one more single block length (as specified in the Block Size register) in the data buffer even though previously-written blocks might still be present. Similarly, the Buffer Read Enable R[11] bit indicates that there is at least one single block length (as specified in the Block Size register) available in the data buffer.

#### 6.3.5 Host Control register (offset 0x28)

A separate LED control pin SDLD is **not** supported in the SDIO101A. If desired, the user can use a GPIO pin on the Host Processor to implement this functionality. Bit R[00] in the Host Control register will always read zero, and writing to it will have no effect.

#### 6.3.6 Power Control register (offset 0x29)

Bits R[03:00] control the POW[1:0] pins of the SDIO101A, which can be used to control an external power supply that powers the SD/SDIO/MMC/CE-ATA device. Two power modes are supported: 'normal' and 'low power'. It is up to the user to decide what voltage to associate with normal and low-power modes, but a typical implementation is 3.3 V for normal and 1.8 V for low-power mode. <u>Table 5</u> shows the relation between the Power Control register and the POW[1:0] pins.

# Power Control register R[03:00]POW[1:0]Descriptionxxx0b00bSD power off1011b01bSD low power (1.8 V) on1101b10bSD normal power (3.3 V) on

10b

#### Table 5. Relation between the Power Control register and the POW[1:0] pins

|  | Product | data | sheet |

|--|---------|------|-------|

|--|---------|------|-------|

SDIO101A

1111b

SD normal power (3.3 V) on

#### 6.3.7 Capabilities register (offset 0x40)

The SDIO101A Capabilities register contents are shown in Table 6.

| Table 6. | Contents of the Capabilities register (offset 0x40) |         |                                                  |  |

|----------|-----------------------------------------------------|---------|--------------------------------------------------|--|

| Location | Attribute                                           | Default | Description                                      |  |

| 63:30    | reserved                                            | 00h     | reserved                                         |  |

| 29       | reserved                                            | 1b      | reserved                                         |  |

| 28       | reserved                                            | 1b      | reserved                                         |  |

| 27       | reserved                                            | 1b      | reserved                                         |  |

| 26       | R                                                   | 1b      | low voltage (1.8 V) supported                    |  |

| 25       | R                                                   | 0b      | 3.0 V not supported (defaults to normal voltage) |  |

| 24       | R                                                   | 1b      | normal voltage (3.3 V) supported                 |  |

| 23       | R                                                   | 1b      | suspend/resume supported                         |  |

| 22       | R                                                   | 0b      | master DMA not supported                         |  |

| 21       | R                                                   | 1b      | high-speed SD (> 25 MHz) supported               |  |

| 20:18    | R                                                   | 001b    | 8-bit supported                                  |  |

| 17:16    | R                                                   | 10b     | 2 kB maximum block length                        |  |

| 15:14    | reserved                                            | 00h     | reserved                                         |  |

| 13:08    | R                                                   | 00h     | get info through other method (Ref. 1)           |  |

| 07       | R                                                   | 1b      | time-out clock unit in MHz                       |  |

| 06       | reserved                                            | 0b      | reserved                                         |  |

| 05:00    | R                                                   | 00h     | get info through other method (Ref. 1)           |  |

#### 6.4 Additional register set description

The additional registers are not part of the *SD Host Standard Specification Version 2.0* (see <u>Ref. 1</u>). These registers do not have to be initialized, so Standard Host Driver software does not have to be aware of them.

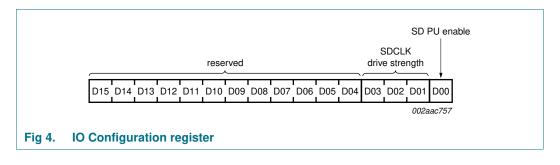

#### 6.4.1 IO Configuration register (offset 0x50)

The IO Configuration register offers three bits to set the drive strength of the IO cell used for driving the SDCLK pin. This way the user can adjust SDCLK rise/fall times according to their system performance requirements. Typically, drive strength should be set to LOW when the SD slot is operating on normal (2.7 V to 3.3 V) voltage, and to HIGH when the SD slot is operating on low voltage (1.8 V). Also, a bit is offered to disable the default pull-up resistors on the SD CMD and SD DATn lines, in case they are not required and the possible leakage current through these resistors is undesired.

All information provided in this document is subject to legal disclaimers.

Table 7.

Contents of the IO Configuration register (offset 0x50)

|          |           |         | <b>3 3 ( )</b>                                                                                                                                    |

|----------|-----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Location | Attribute | Default | Description                                                                                                                                       |

| 15:04    | reserved  | 0h      | reserved                                                                                                                                          |

| 03:01    | R/W       | 0h      | SDCLK drive strength select. These bits can be used to program the drive strength of the SDCLK IO cell. <u>Table 8</u> shows the possible values. |

| 00       | R/W       | 0b      | SD line pull-up. If set to b1, the internal pull-up resistors on the SD CMD and SD DATn lines are switched ON.                                    |

#### Table 8. SDCLK drive strength programming

| IO Configuration register R[03:01] | SDCLK drive strength                 |

|------------------------------------|--------------------------------------|

| 000b                               | low (SD operating on 2.7 V to 3.6 V) |

| 0001b                              | reserved                             |

| 010b                               | reserved                             |

| 011b                               | reserved                             |

| 100b                               | high (SD operating on 1.8 V)         |

| 101b                               | reserved                             |

| 110b                               | reserved                             |

| 111b                               | reserved                             |

#### 6.4.2 DMA register (offset 0xF4)

The DMA register is located in the Common register area. This register controls the DREQ output. The DREQ LOW and HIGH times are programmed with DMA inter delay and DMA burst size.

#### Table 9. DREQ control programming

| Location | Attribute | Default | Description                                                                 |

|----------|-----------|---------|-----------------------------------------------------------------------------|

| 15:09    | R/W       | 0h      | DREQ delay period (DREQ LOW time)<br>LOW time = value × SD clock cycle time |

| 08:01    | R/W       | 0h      | DMA burst size (DREQ HIGH time)                                             |

**Remark:** Refer to <u>Section 6.1</u> for more detailed DMA description.

Product data sheet

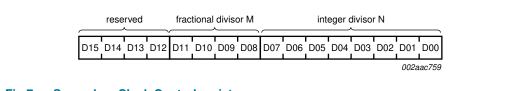

#### 6.4.3 Secondary Clock Control register (offset 0xF6)

The Secondary Clock Control register is located in the Common register area. This register gives the user more control over the clock generation. An additional fractional divider is offered to program the SDCLK base frequency with higher granularity, allowing the design to use an existing (available) clock rather than an external crystal or oscillator. Figure 6 shows the architecture of the secondary clock control.

The SDCLK base frequency can be calculated with Equation 1<sup>1</sup>:

$$f_{SDCLK(base)} = \frac{f_{PLL}}{divisor\left(N + \frac{M}{16}\right)} \tag{1}$$

Where 'divisor' is the standard divisor as programmed in the Clock Control register; N is the integer divisor as programmed in the Secondary Clock Control register R[07:00]; M is the fractional divisor as programmed in the Secondary Clock Control register R[11:08]. <u>Figure 7</u> and <u>Table 10</u> below show the register bits of the Secondary Clock Control register.

Fig 7. Secondary Clock Control register

| Table 10. | Contents of the Secondary | v Clock Control register | r (offset 0xF6) |

|-----------|---------------------------|--------------------------|-----------------|

|           |                           | olook oonklor regiotei   |                 |

| Location | Attribute | Default | Description                |

|----------|-----------|---------|----------------------------|

| 15:12    | reserved  | 00h     | reserved                   |

| 11:08    | R/W       | 00h     | fractional divisor value M |

| 07:00    | R/W       | 01h     | integer divisor value N    |

<sup>1.</sup> This is the average SD clock frequency. The peak SD clock frequency might be higher when the fractional divisor M is used.

#### 6.4.3.1 SDIO101A X1\_CLK input

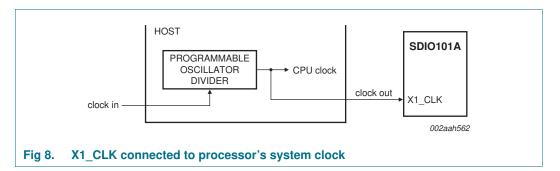

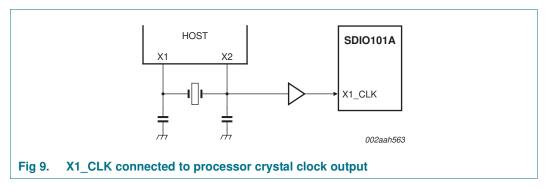

It is recommended that the SDIO101A's input clock be connected to one of the systems available clock sources to eliminate the use of an external crystal. The best use case is to have the SDIO101A's X1\_CLK input be connected to the processor's clock output (Figure 8) or processor's crystal output (Figure 9). In either case, the SDIO101A internal PLL can be used to boost up the X1\_CLK input then divided down to the desired SDIO clock by using the internal divider in combination with the built-in fractional divider.

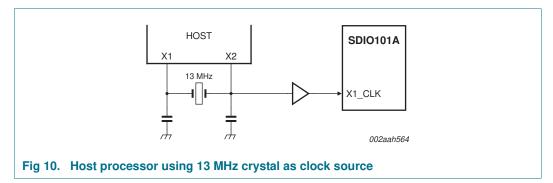

Figure 10 details a typical scenario where the host processor uses a 13 MHz crystal as its clock source, and the same clock is used by the SDIO101A to operate the SD clock as close to 50 MHz as possible.

With its input clock supplies by the processor crystal output, the SDIO101A internal PLL (0xFA) is used to boost the input frequency to 104 MHz, the standard Clock Control register (0x2C) and the fractional divider (0xF6) registers are then used to divide the 104 MHz to about 48.9 MHz to be used as SD clock.

PLL register (0xFA) settings:

Bit 15 = 0bBit 14 = 0bBit [13:7] = 0000000b Bit [6:5] = 01b Bit [4:0] = 00111b; B = 7

Fractional divider (0xF6) settings:

Bit [15:12] = 0000b; reserved bit Bit [11:8] = 0001b; M = 1 Bit [7:0] = 00000001b; N = 1

Clock Control register (0x2C) settings:

Bit [15:0] = 103h

$$f_{SDCLK(base)} = \frac{f_{PLL}}{divisor\left(N + \frac{M}{16}\right)}$$

$= (13 \text{ MHz} \times 8) / (2 \times (1 + 1 / 16))$

= 48.9 MHz

#### 6.4.4 Miscellaneous register (offset 0xF8)

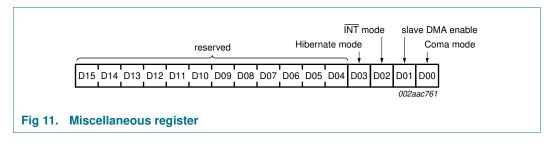

The Miscellaneous register is located in the Common register area. This register can be programmed to put the device in the 'Coma mode' or 'Hibernate mode', extra-low power-down modes on top of the Standby mode programmable through bit R[00] in the Clock Control register. Also, a bit is offered to disable the DREQ DMA request line on the Host Interface. Lastly, a bit is offered to switch between open-drain and push-pull mode for the INT interrupt output pin. Figure 11 and Table 11 below show the register bits of the Miscellaneous register.

SDIO101A Product data sheet

| Location | Attribute | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:04    | reserved  | 00h     | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 03       | R/W       | 0b      | Hibernate mode select. When set to 1b, the oscillator, PLL and supply to the buffer memory will be switched OFF. Card detection is disabled. Clearing this bit will re-instate power to the buffer memory, the oscillator and PLL are enabled.                                                                                                                                                                                                                                                         |

| 02       | R/W       | 0b      | INT mode select. When set to 0b, the $\overline{\text{INT}}$ interrupt output pin will be open-drain mode. An external 10 k $\Omega$ pull-up resistor is required in this case. When set to 1b, the $\overline{\text{INT}}$ interrupt output pin will be in push-pull mode.                                                                                                                                                                                                                            |

| 01       | R/W       | 1b      | Slave DMA enable. If programmed to 1b, the DREQ signal will be functional. If programmed to 0b, the DREQ signal will be fixed to zero.                                                                                                                                                                                                                                                                                                                                                                 |

| 00       | R/W       | Ob      | Coma mode. If programmed to 1b, power will internally be<br>switched off to most of the device, resulting in a very low coma<br>mode current. All state in the device will be lost, and no registers<br>can be read or written, with the exception of the 'Software Reset<br>for All' bit in the Software Reset register. Clearing this bit will<br>re-instate power to the entire chip, and reset the SDIO101A. A<br>hard-reset on the RESET pin will also bring the device back out<br>of Coma mode. |

Table 11.

Contents of the Miscellaneous register (offset 0xF8)

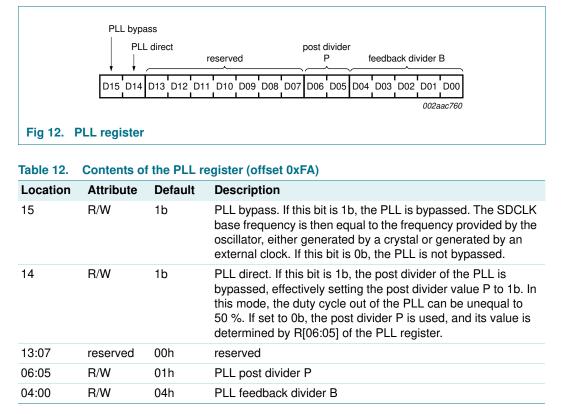

#### 6.4.5 PLL register (offset 0xFA)

The PLL register is located in the Common register area. This register provides control over the Phase-Locked Loop, which is used in the SDIO101A to generate an SD base clock frequency from the crystal oscillator or external clock source. The default values of this register are such that the PLL multiplies the incoming frequency from the crystal oscillator by 5. This means that, if the PLL register is not programmed, the frequency generated by the crystal oscillator or external clock source should be 10.4 MHz in order to generate the 52 MHz maximum SDCLK speed. For the SD base clock frequency generated by the PLL from the Crystal oscillator frequency it holds

$$f_{PLL} = (B+1) \times f_{CLK} \tag{2}$$

where B is the feedback divider value as programmed in R[04:00] of the PLL register. The user should determine the desired  $f_{PLL}$ , choose the required value B for the feedback divider based on the available clock source  $f_{osc}$ , and then choose a value for post divider P (as programmed in R[06:05]) such that the following condition gets satisfied:

156

$$MHz < 2 \times (P+1) \times f_{PLL} < 320 MHz$$

(3)

The post divider setting decided by the value of P does not affect the frequency value (in MHz) of the  $f_{PLL}$ . The only advantage of this post divider is in adjusting the duty cycle of the resulting  $f_{PLL}$  clock. The greater the value of P, the closer the duty cycle will be to 50 % (provided the condition mentioned in <u>Equation 3</u> is not violated, for a guaranteed behavior).

The PLL register also provides the possibility to bypass the PLL post divider, effectively setting a value of 1 for P. Also, the user can bypass the entire PLL. Figure 12 and Table 12 show the register bits of the PLL register.

#### SD/SDIO/MMC/CE-ATA host controller

#### 6.4.6 Host Controller Version register (offset 0xFE)

The SDIO101A Host Controller version is shown in Table 13.

#### Table 13. Contents of the Host Controller Version register (offset 0xFE)

| Location | Attribute | Default | Description             |

|----------|-----------|---------|-------------------------|

| 15:08    | R         | 10h     | SDIO101A version 1.0    |

| 07:00    | reserved  | 00h     | reserved <sup>[1]</sup> |

[1] These bits do not match Host Controller specification. Host driver should not use these bits.

#### 6.5 Power-saving modes

The SDIO101A provides 5 power-saving modes that can be used in different situations to minimize the power consumption of the device. <u>Table 14</u> below describes these modes and their associated register bits that can be programmed to enable them. Idle, Low Power and Standby modes can be used if card interrupts should still be serviced. The Hibernate mode will switch off the power to the SD device and the Coma mode switches off most of the Host Controller, therefore, card interrupts will not be generated. <u>Table 14</u> shows the 5 power-saving modes.

| Mode              | Associated register bits        | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle mode         | Clock Control<br>register R[02] | SD Card clock stopped; oscillator and PLL are active.                                                                                                                                                                                                                                                                                                                                                                              |

| Low-Power<br>mode | Power Control<br>register R[00] | SD Card power switched off.                                                                                                                                                                                                                                                                                                                                                                                                        |

| Standby mode      | Clock Control<br>register R[00] | When the Clock Control register R[00] is set to b0, the<br>SDIO101A internal clock is stopped, the PLL is in Power-down<br>mode, the oscillator is active and all register states are<br>maintained. The device will still respond to card interrupts.<br>When waking up from Standby mode, after writing a b1 in the<br>Clock Control register R[00], the data buffer FIFO pointers will<br>reset to empty.                       |

| Coma mode         | Miscellaneous<br>register R[00] | When the Miscellaneous register R[00] is set to b1, the<br>SDIO101A internal power is switched off. All device pins are<br>3-stated, and only a write to the 'Software Reset for All' bit in the<br>Software Reset register or a hard reset on the RESET pin will<br>wake up the device. All device states, including data buffer<br>contents, are lost. Card insertion and removal detection through<br>the SDCD pin is disabled. |

| Hibernate<br>mode | Miscellaneous<br>register R[03] | The oscillator, PLL and supply to the buffer memory will be<br>switched off. All states are maintained, but data buffer contents<br><u>are lost</u> . Card insertion and removal detection through the<br>SDCD pin is disabled. Upon wake-up, the data buffer FIFO<br>pointers will reset to empty.                                                                                                                                |

#### Table 14. SDIO101A Power-saving modes

## 7. Application design-in information

All information provided in this document is subject to legal disclaimers.

## 8. Basic architecture

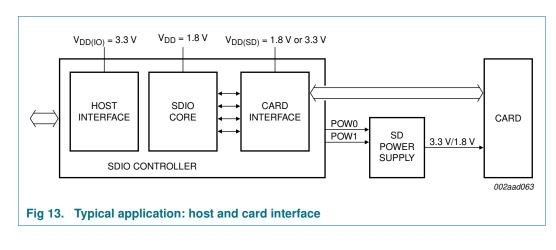

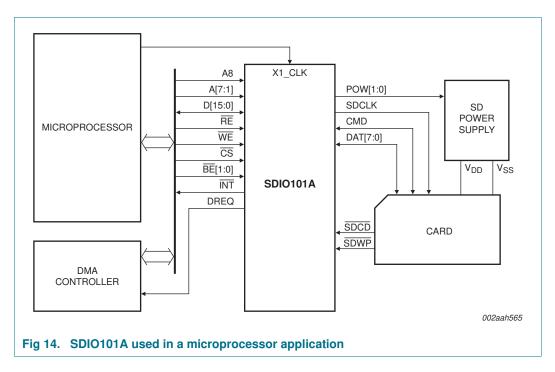

The SDIO101A provides SD/SDIO/MMC/CE-ATA functionality to a microprocessor system as illustrated in Figure 14. A standard SD/SDIO/MMC/CE-ATA driver running on the host processor will be able to access the standard host register set in the SDIO101A through the 16-bit memory interface, and initiate transactions to and from the SD card. An external SD power supply (controlled by the SDIO101A) can be used to supply the SD card.

## 9. Limiting values

#### Table 15. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                       | Conditions                                 | Min          | Max            | Unit |

|---------------------|---------------------------------|--------------------------------------------|--------------|----------------|------|

| $V_{DD(IO)}$        | input/output supply voltage     | host interface;<br>in 2.5 V to 3.3 V range | -0.3         | +4.6           | V    |

| V <sub>DD(SD)</sub> | SD supply voltage               | SD interface                               |              |                |      |

|                     |                                 | in 1.8 V range                             | -0.3         | +1.95          | V    |

|                     |                                 | in 3.3 V range                             | -0.3         | +3.6           | V    |

| V <sub>DD</sub>     | supply voltage                  | core; 1.8 V range                          | -0.3         | +2.4           | V    |

| VI                  | input voltage                   | on any input pin                           |              |                |      |

|                     |                                 | 1.8 V interface                            | $V_{SS}-0.3$ | $V_{DD} + 0.6$ | V    |

|                     |                                 | 3.3 V interface                            | -0.3         | +3.6           | V    |

| T <sub>amb</sub>    | ambient temperature             | operating                                  | -40          | +85            | °C   |

| T <sub>stg</sub>    | storage temperature             |                                            | -65          | +150           | °C   |

| $V_{\text{ESD}}$    | electrostatic discharge voltage | SD/MMC/SDIO interface;<br>Human Body Model | -4           | +4             | kV   |

| -                   |                                 |                                            |              |                |      |

# 10. Recommended operating conditions

#### Table 16.Operating conditions

| Symbol                | Parameter                   | Conditions                    | Min          | Тур | Max  | Unit |

|-----------------------|-----------------------------|-------------------------------|--------------|-----|------|------|

| V <sub>DD</sub>       | supply voltage              | core                          | 1.65         | 1.8 | 1.95 | V    |

| V <sub>DD(IO)</sub>   | input/output supply voltage | host interface                | 2.25         | 3.3 | 3.6  | V    |

| V <sub>DD(SD)</sub>   | SD supply voltage           | SD interface                  | 1.65         | 3.3 | 3.6  | V    |

| f <sub>clk(ext)</sub> | external clock frequency    |                               | <u>[1]</u> 1 | -   | 52   | MHz  |

| I <sub>DD(AV)</sub>   | average supply current      | f = 13 MHz;<br>SDCLK = 25 MHz | -            | 6   | -    | mA   |

| I <sub>DD</sub>       | supply current              | Standby mode                  | -            | 460 | -    | μA   |

|                       |                             | Hibernate mode                | -            | 69  | -    | μA   |

|                       |                             | Coma mode                     | -            | 5   | -    | μA   |

| T <sub>oper</sub>     | operating temperature       |                               | -40          | +25 | +85  | °C   |

[1] If the PLL is not bypassed, the minimum input frequency is 10 MHz.

## 11. Static characteristics

| Symbol               | Parameter                                           | Conditions              |            | $V_{DD(IO)} = 2.5 V$ |          | $V_{DD(IO)} = 3.3 V$ |                 | Unit |

|----------------------|-----------------------------------------------------|-------------------------|------------|----------------------|----------|----------------------|-----------------|------|

|                      |                                                     |                         |            | Min                  | Max      | Min                  | Max             |      |

| V <sub>IL(clk)</sub> | clock LOW-level input voltage                       | X1_CLK                  | <u>[1]</u> | -0.3                 | +0.6     | -0.3                 | +0.6            | V    |

| V <sub>IH(clk)</sub> | clock HIGH-level input voltage                      | X1_CLK                  | <u>[1]</u> | 2.4                  | $V_{DD}$ | 2.4                  | $V_{DD}$        | V    |

| V <sub>IL</sub>      | LOW-level input voltage                             |                         |            | -0.3                 | +0.65    | -0.3                 | +0.8            | V    |

| V <sub>IH</sub>      | HIGH-level input voltage                            |                         |            | 1.6                  | $V_{DD}$ | 2.1                  | $V_{\text{DD}}$ | V    |

| V <sub>OL</sub>      | LOW-level output voltage                            | $I_{OL} = 2 \text{ mA}$ |            | -                    | 0.4      | -                    | 0.4             | V    |

| V <sub>OH</sub>      | HIGH-level output voltage                           | $I_{OH} = -800 \ \mu A$ |            | 1.4                  | -        | 2.1                  | -               | V    |

| I <sub>LIL</sub>     | LOW-level input leakage current                     |                         |            | -                    | 10       | -                    | 10              | μA   |

| I <sub>LIH</sub>     | HIGH-level input leakage current                    |                         |            | -                    | 10       | -                    | 10              | μA   |

| I <sub>L(clk)</sub>  | clock leakage current                               | X1_CLK                  |            | -                    | 30       | -                    | 30              | μA   |

| Ci                   | input capacitance                                   |                         |            | -                    | 5        | -                    | 5               | pF   |

| Dynamic a            | verage supply current (V <sub>DD(SD)</sub> = 3.3 V) |                         |            |                      |          |                      |                 |      |

| I <sub>DD(AV)</sub>  | average supply current                              | 25 MHz                  | [2]        | -                    | 7        | -                    | 7               | mA   |

|                      |                                                     | 52 MHz                  | [2]        | -                    | 9        | -                    | 9               | mA   |

| I <sub>DD(IO)</sub>  | input/output supply current                         | 25 MHz                  | <u>[3]</u> | -                    | 1.3      | -                    | 1.5             | mA   |

|                      |                                                     | 52 MHz                  | <u>[3]</u> | -                    | 1.3      | -                    | 1.5             | mA   |

| I <sub>DD(SD)</sub>  | SD supply current                                   | 25 MHz                  |            | -                    | 1.5      | -                    | 1.5             | mA   |

|                      |                                                     | 52 MHz                  |            | -                    | 2.3      | -                    | 2.3             | mA   |

| Hibernate            | mode supply current (V <sub>DD(SD)</sub> = 3.3 V)   |                         |            |                      |          |                      |                 |      |

| I <sub>DD</sub>      | supply current                                      |                         | [2]        | -                    | 130      | -                    | 130             | μA   |

| I <sub>DD(IO)</sub>  | input/output supply current                         | 25 MHz                  | <u>[3]</u> | -                    | 20       | -                    | 20              | μA   |

| I <sub>DD(SD)</sub>  | SD supply current                                   |                         |            | -                    | 1.5      | -                    | 1.5             | μA   |

| Standby m            | ode supply current ( $V_{DD(SD)} = 3.3 V$ )         |                         |            |                      |          |                      |                 |      |

| I <sub>DD</sub>      | supply current                                      |                         | [2]        | -                    | 4        | -                    | 4               | mA   |

| I <sub>DD(IO)</sub>  | input/output supply current                         |                         | [3]        | -                    | 20       | -                    | 20              | μA   |

| I <sub>DD(SD)</sub>  | SD supply current                                   |                         |            | -                    | 1.5      | -                    | 1.5             | μA   |

| Coma mod             | le supply current (V <sub>DD(SD)</sub> = 3.3 V)     |                         |            |                      |          |                      |                 |      |

| I <sub>DD</sub>      | supply current                                      |                         | [2]        | -                    | 0.6      | -                    | 0.6             | μA   |

| I <sub>DD(IO)</sub>  | input/output supply current                         |                         | [3]        | -                    | 20       | -                    | 20              | μA   |

| I <sub>DD(SD)</sub>  | SD supply current                                   |                         |            | -                    | 0.5      | -                    | 0.5             | μA   |

[1] X1\_CLK = 3.3 V only.

[2]  $I_{DD}$  is the supply on  $V_{DD}$  and  $V_{DDA}$ .

[3] I<sub>DD(IO)</sub> current might be higher or lower depending on the activity of the 16-bit data bus. The numbers specified in the data sheet are measured with no activity on the host controller bus. The data bus, address bus and control signals are pulled HIGH.

SD/SDIO/MMC/CE-ATA host controller

# **12. Dynamic characteristics**

| Symbol                 | Parameter                                                                | Conditions                    | V <sub>DD(IO</sub> | <sub>)</sub> = 2.5 V | V <sub>DD(IO</sub> | <sub>)</sub> = 3.3 V | Unit |

|------------------------|--------------------------------------------------------------------------|-------------------------------|--------------------|----------------------|--------------------|----------------------|------|

|                        |                                                                          |                               | Min                | Max                  | Min                | Max                  |      |

| twL(X1_CLK)            | X1_CLK pulse width LOW                                                   |                               | 9                  | -                    | 9                  | -                    | ns   |

| WH(X1_CLK)             | X1_CLK pulse width HIGH                                                  |                               | 9                  | -                    | 9                  | -                    | ns   |

| f <sub>X1_CLK</sub>    | frequency on pin X1_CLK                                                  |                               | -                  | 52                   | -                  | 52                   | MHz  |

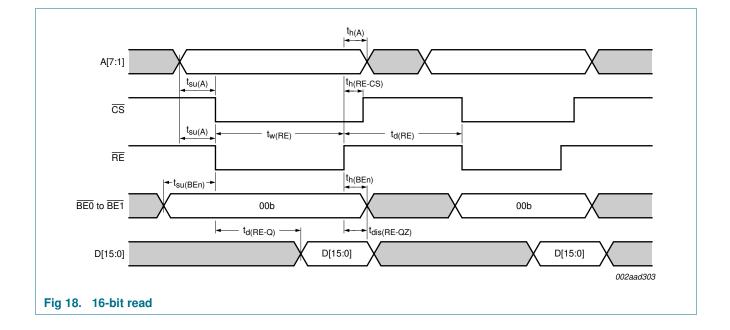

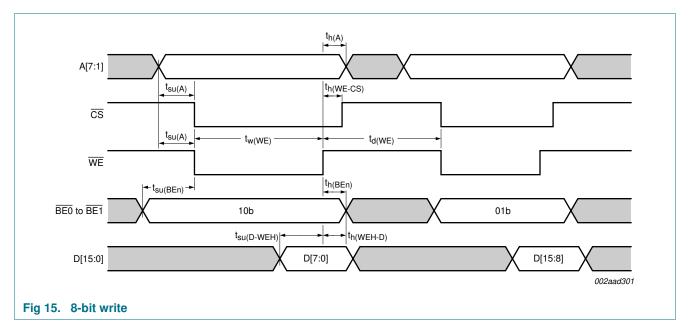

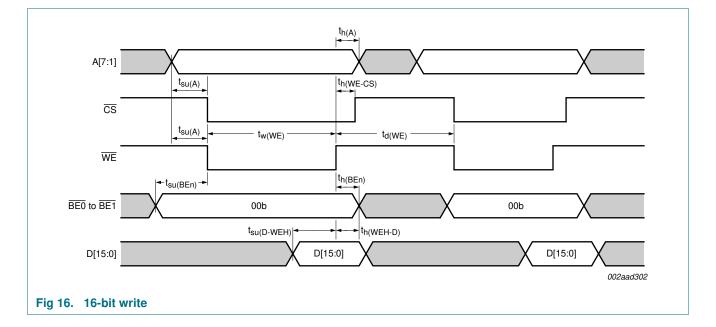

| t <sub>su(A)</sub>     | address set-up time                                                      |                               | 5                  | -                    | 5                  | -                    | ns   |

| h(A)                   | address hold time                                                        |                               | 10                 | -                    | 5                  | -                    | ns   |

| h(WE-CS)               | hold time from $\overline{WE}$ to $\overline{CS}$                        |                               | 0                  | -                    | 0                  | -                    | ns   |

| d(CSL-WEL)             | delay time from $\overline{\text{CS}}$ LOW to $\overline{\text{WE}}$ LOW |                               | 0                  | -                    | 0                  | -                    | ns   |

| w(WE)                  | WE pulse width                                                           |                               | 10                 | -                    | 20                 | -                    | ns   |

| d(WE)                  | WE delay time                                                            |                               | 10                 | -                    | 20                 | -                    | ns   |

| <sup>I</sup> su(D-WEH) | set-up time from data input to $\overline{WE}$ HIGH                      |                               | 5                  | -                    | 5                  | -                    | ns   |

| h(WEH-D)               | data input hold time after $\overline{WE}$ HIGH                          |                               | 5                  | -                    | 5                  | -                    | ns   |

| su(BEn)                | set-up time on pin BEn                                                   |                               | 5                  | -                    | 5                  | -                    | ns   |

| h(BEn)                 | hold time on pin BEn                                                     |                               | 5                  | -                    | 5                  | -                    | ns   |

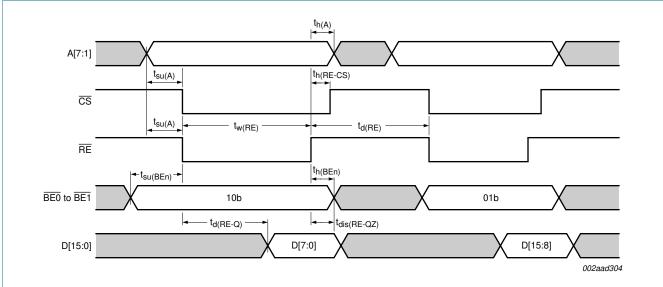

| h(RE-CS)               | hold time from $\overline{RE}$ to $\overline{CS}$                        |                               | 0                  | -                    | 0                  |                      | ns   |

| d(CS-RE)               | delay time from $\overline{CS}$ to $\overline{RE}$                       |                               | 0                  | -                    | 0                  |                      | ns   |

| w(RE)                  | RE pulse width                                                           |                               | 25                 | -                    | 20                 |                      | ns   |

| d(RE)                  | RE delay time                                                            |                               | 10                 | -                    | 10                 |                      | ns   |

| d(RE-Q)                | delay time from $\overline{RE}$ to data output                           | 25 pF load                    | -                  | 20                   | -                  | 25                   | ns   |

| dis(RE-QZ)             | disable time from RE to high-impedance data output                       | 25 pF load                    | -                  | 20                   | -                  | 15                   | ns   |

| w(RESET)               | pulse width on pin RESET                                                 |                               | 10                 | -                    | 5                  | -                    | ns   |

| d(buf_full-INTL)       | delay time from buffer full to INT LOW                                   | receive buffer<br>(receive)   | -                  | 4XTAL1               | -                  | 4XTAL1               | ns   |

| d(int_clr-INTH)        | delay time from interrupt clear to INT HIGH                              | receive buffer<br>(read)      | -                  | 300                  | -                  | 300                  | ns   |

| d(buf_emp-INTL)        | delay time from buffer empty to INT LOW                                  | transmit buffer<br>(transmit) | -                  | 4XTAL2               | -                  | 4XTAL2               | ns   |

| d(int_clr-INTH)        | delay time from interrupt clear to INT HIGH                              | transmit buffer<br>(write)    | -                  | 80                   | -                  | 80                   | ns   |

| su(A8)                 | address 8 set-up time                                                    |                               | 5                  | -                    | 5                  | -                    | ns   |

| su(A8-CS)              | set-up time from address 8 to $\overline{CS}$                            |                               | 5                  | -                    | 5                  | -                    | ns   |

| d(SDCLK-DREQH)         | delay time from SDCLK to DREQ<br>HIGH                                    |                               | -                  | 20                   | -                  | 15                   | ns   |

| d(CSH-DREQL)W          | write delay time from $\overline{\text{CS}}$ HIGH to DREQ LOW            |                               | -                  | 20                   | -                  | 15                   | ns   |

| d(CSH-DREQL)R          | read delay time from $\overline{\text{CS}}$ HIGH to DREQ LOW             |                               | -                  | 20                   | -                  | 15                   | ns   |

SD/SDIO/MMC/CE-ATA host controller

| Symbol              | Parameter         | Conditions                            | 25 MHz |     | 52 MHz |     | Unit |

|---------------------|-------------------|---------------------------------------|--------|-----|--------|-----|------|

|                     |                   |                                       | Min    | Max | Min    | Max |      |

| Clock               |                   |                                       | 1      |     | 1      |     |      |

| t <sub>WL</sub>     | clock low time    | 10 pF max.                            | 12     | -   | 8      | -   | ns   |

| t <sub>WH</sub>     | clock high time   | 10 pF max.                            | 12     | -   | 8      | -   | ns   |

| t <sub>w(clk)</sub> | clock pulse width | 10 pF max.                            | 40     | -   | 18     | -   | ns   |

| t <sub>TLH</sub>    | clock rise time   | 10 pF max.                            | -      | 10  | -      | 3   | ns   |

| t <sub>THL</sub>    | clock fall time   | 10 pF max.                            | -      | 10  | -      | 3   | ns   |

| Input CM            | D, DATn           |                                       |        |     |        |     |      |

| t <sub>ISU</sub>    | input set-up time | 10 pF max.                            | 5      | -   | 6      | -   | ns   |

| t <sub>IH</sub>     | input hold time   | 10 pF max.                            | 5      | -   | 2      | -   | ns   |

| Output C            | MD, DATn          |                                       |        |     |        |     |      |

| t <sub>ODLY</sub>   | output delay time | during data transfer mode; 40 pF max. | 0      | 14  | -      | 14  | ns   |

| t <sub>OH</sub>     | output hold time  |                                       | 2.5    | -   | 2.5    | -   | ns   |

# Table 19. Dynamic characteristics for MMC/SD/SDIO bus interface $V_{\text{DD}/\text{CD}} = 2.7 \text{ V to } 3.3 \text{ V}$

# Table 20.Dynamic characteristics for MMC/SD/SDIO bus interface $V_{DD(SD)} = 1.70 V$ to 1.95 V.

| Symbol              | Parameter         | Conditions                            | 25  | MHz | 52 MHz |     | Unit |

|---------------------|-------------------|---------------------------------------|-----|-----|--------|-----|------|

|                     |                   |                                       | Min | Max | Min    | Max |      |

| Clock               |                   |                                       | 1   |     |        |     |      |

| t <sub>WL</sub>     | clock low time    | 10 pF max.                            | 12  | -   | 8      | -   | ns   |

| t <sub>WH</sub>     | clock high time   | 10 pF max.                            | 12  | -   | 8      | -   | ns   |

| t <sub>w(clk)</sub> | clock pulse width | 10 pF max.                            | 40  | -   | 18     | -   | ns   |

| t <sub>TLH</sub>    | clock rise time   | 10 pF max.                            | -   | 10  | -      | 3   | ns   |

| t <sub>THL</sub>    | clock fall time   | 10 pF max.                            | -   | 10  | -      | 3   | ns   |

| Input CM            | D, DATn           |                                       |     |     |        |     |      |

| t <sub>ISU</sub>    | input set-up time | 10 pF max.                            | 5   | -   | 6      | -   | ns   |

| t <sub>IH</sub>     | input hold time   | 10 pF max.                            | 5   | -   | 2      | -   | ns   |

| Output C            | MD, DATn          |                                       |     |     |        |     |      |

| t <sub>ODLY</sub>   | output delay time | during data transfer mode; 40 pF max. | 0   | 14  | -      | 14  | ns   |

| t <sub>OH</sub>     | output hold time  |                                       | 2.5 | -   | 2.5    | -   | ns   |

SD/SDIO/MMC/CE-ATA host controller

## 12.1 Timing diagrams

#### **NXP Semiconductors**

# **SDIO101A**

#### SD/SDIO/MMC/CE-ATA host controller

Fig 17. 8-bit read