Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **SE98**

## DDR memory module temp sensor, 3.3 V

Rev. 04 — 2 February 2009

**Product data sheet**

## 1. General description

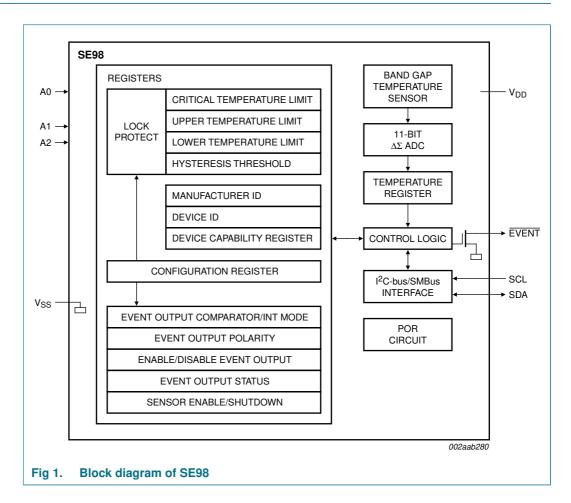

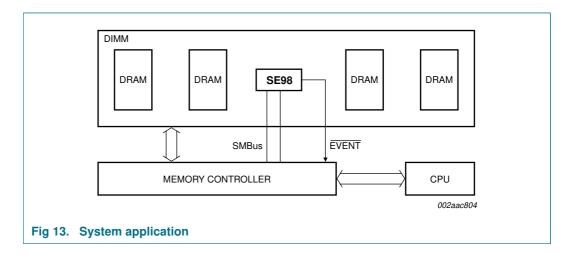

The NXP Semiconductors SE98 measures temperature from –40 °C to +125 °C communicating via the I<sup>2</sup>C-bus/SMBus. It is typically mounted on a Dual In-line Memory Module (DIMM) measuring the DRAM temperature in accordance with the new JEDEC (JC-42.4) *Mobile Platform Memory Module Thermal Sensor Component* specification.

Placing the Temp Sensor (TS) on DIMM allows accurate monitoring of the DIMM module temperature to better estimate the DRAM case temperature ( $T_{case}$ ) to prevent it from exceeding the maximum operating temperature of 85 °C. The chip set throttles the memory traffic based on the actual temperatures instead of the calculated worst-case temperature or the ambient temperature using a temp sensor mounted on the motherboard. There is up to a 30 % improvement in thin and light notebooks that are using one or two 1G SO-DIMM modules, although other memory modules such as in server applications will also see an increase in system performance. Future uses of the TS will include more dynamic control over thermal throttling, the ability to use the Alarm Window to create multiple temperature zones for dynamic throttling and to save processor time by scaling the memory refresh rate.

The TS consists of an Analog-to-Digital Converter (ADC) that monitors and updates its own temperature readings 8 times per second, converts the reading to a digital data, and latches them into the data temperature registers. User-programmable registers, such as Shutdown or Low-power modes and the specification of temperature event and critical output boundaries, provide flexibility for DIMM temperature-sensing applications.

When the temperature changes beyond the specified boundary limits, the SE98 outputs an  $\overline{\text{EVENT}}$  signal. The user has the option of setting the  $\overline{\text{EVENT}}$  output signal polarity as either an active LOW or active HIGH comparator output for thermostat operation, or as a temperature event interrupt output for microprocessor-based systems. The  $\overline{\text{EVENT}}$  output can even be configured as a critical temperature output.

The SE98 supports the industry-standard 2-wire I<sup>2</sup>C-bus/SMBus serial interface. The SMBus TIMEOUT function is supported to prevent system lock-ups. Manufacturer and Device ID registers provide the ability to confirm the identify of the device. Three address pins allow up to eight devices to be controlled on a single bus. To maintain interchangeability with the I<sup>2</sup>C-bus/SMBus interface the electrical specifications are specified with the operating voltage of 3.0 V to 3.6 V.

### DDR memory module temp sensor, 3.3 V

### 2. Features

#### 2.1 General features

- JEDEC (JC-42.4) SO-DIMM temperature sensor

- Optimized for voltage range: 3.0 V to 3.6 V

- Shutdown/Standby current: 8 μA (typ.) and 15 μA (max.)

- 2-wire interface: I<sup>2</sup>C-bus/SMBus compatible, 0 Hz to 400 kHz

- SMBus ALERT and TIMEOUT (programmable)

- Available packages: TSSOP8 and HVSON8

### 2.2 Temperature sensor features

- Temperature-to-Digital converter

- Operating current: 200 μA (typ.) and 250 μA (max.)

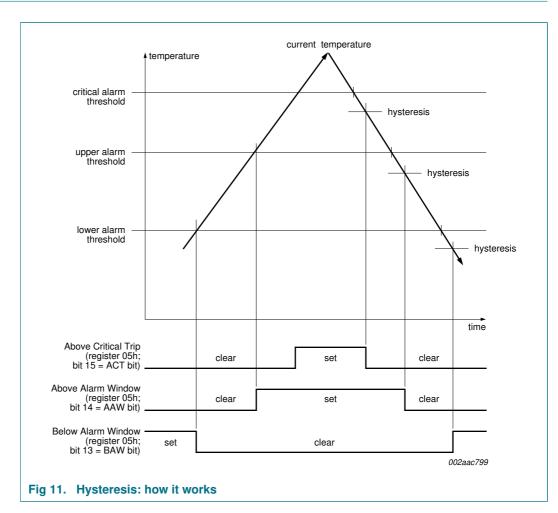

- Programmable hysteresis threshold: 0 °C, 1.5 °C, 3 °C, 6 °C

- Over/under/critical temperature EVENT output

- C grade accuracy:

- $\pm 1$  °C/ $\pm 2$  °C (typ./max.)  $\rightarrow +75$  °C to +95 °C

- $\bullet$  ±2 °C/±3 °C (typ./max.)  $\rightarrow$  +40 °C to +125 °C

- $\bullet$  ±3 °C/±4 °C (typ./max.)  $\rightarrow$  -40 °C to +125 °C

## 3. Applications

- DDR2 and DDR3 memory modules

- Laptops, personal computers and servers

- Enterprise networking

- Hard disk drives and other PC peripherals

## 4. Ordering information

Table 1. Ordering information

| Type number | Topside | Package |                                                                                                               |          |  |  |  |  |

|-------------|---------|---------|---------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|             | mark    | Name    | Description                                                                                                   | Version  |  |  |  |  |

| SE98PW      | SE98    | TSSOP8  | plastic thin shrink small outline package; 8 leads;<br>body width 4.4 mm                                      | SOT530-1 |  |  |  |  |

| SE98TK      | SE98    | HVSON8  | plastic thermal enhanced very thin small outline package; no leads; 8 terminals; body $3\times3\times0.85$ mm | SOT908-1 |  |  |  |  |

### DDR memory module temp sensor, 3.3 V

## 5. Block diagram

DDR memory module temp sensor, 3.3 V

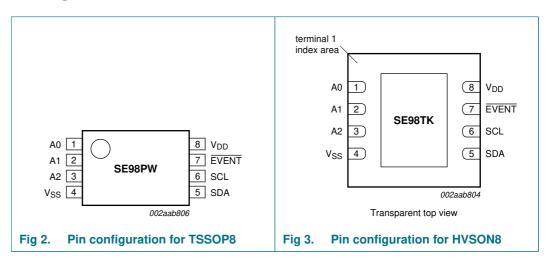

## 6. Pinning information

### 6.1 Pinning

## 6.2 Pin description

Table 2. Pin description

| Symbol   | Pin | Туре   | Description                                                                                                         |

|----------|-----|--------|---------------------------------------------------------------------------------------------------------------------|

| A0[1]    | 1   | l      | I <sup>2</sup> C-bus/SMBus slave address bit 0                                                                      |

| A1       | 2   | l      | I <sup>2</sup> C-bus/SMBus slave address bit 1                                                                      |

| A2       | 3   | l      | I <sup>2</sup> C-bus/SMBus slave address bit 2                                                                      |

| $V_{SS}$ | 4   | ground | device ground                                                                                                       |

| SDA      | 5   | I/O    | SMBus/I <sup>2</sup> C-bus serial data input/output (open-drain).<br>Must have external pull-up resistor.           |

| SCL      | 6   | l      | SMBus/I <sup>2</sup> C-bus serial clock input/output (open-drain).<br>Must have external pull-up resistor.          |

| EVENT    | 7   | 0      | Thermal alarm output for high/low and critical temperature limit (open-drain). Must have external pull-up resistor. |

| $V_{DD}$ | 8   | power  | device power supply (3.0 V to 3.6 V)                                                                                |

<sup>[1]</sup> In general, application of 10 V on the A0 pin would not damage the pin, but NXP Semiconductors does not guarantee the overvoltage for this pin.

## DDR memory module temp sensor, 3.3 V

## 7. Functional description

#### 7.1 Serial bus interface

The SE98 uses the 2-wire serial bus (I²C-bus/SMBus) to communicate with a host controller. The serial bus consists of a clock (SCL) and data (SDA) signals. The device can operate on either the I²C-bus Standard/Fast mode or SMBus. The I²C-bus Standard-mode is defined to have bus speeds from 0 Hz to 100 kHz, I²C-bus Fast-mode from 0 Hz to 400 kHz, and the SMBus is from 10 kHz to 100 kHz. The host or bus master generates the SCL signal, and the SE98 uses the SCL signal to receive or send data on the SDA line. Data transfer is serial, bidirectional, and is one bit at a time with the Most Significant Bit (MSB) transferred first, and a complete I²C-bus data is 1 byte. Since SCL and SDA are open-drain, pull-up resistors must be installed on these pins.

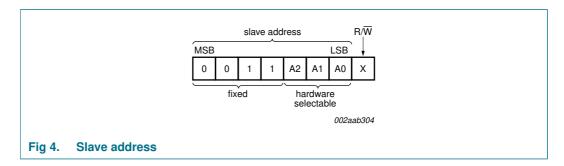

#### 7.2 Slave address

The SE98 uses a 4-bit fixed and 3-bit programmable (A0, A1 and A2) 7-bit slave address that allows a total of eight devices to co-exist on the same bus. The input of each pin is sampled at the start of each I<sup>2</sup>C-bus/SMBus access. The temperature sensor's fixed address is 0011.

#### DDR memory module temp sensor, 3.3 V

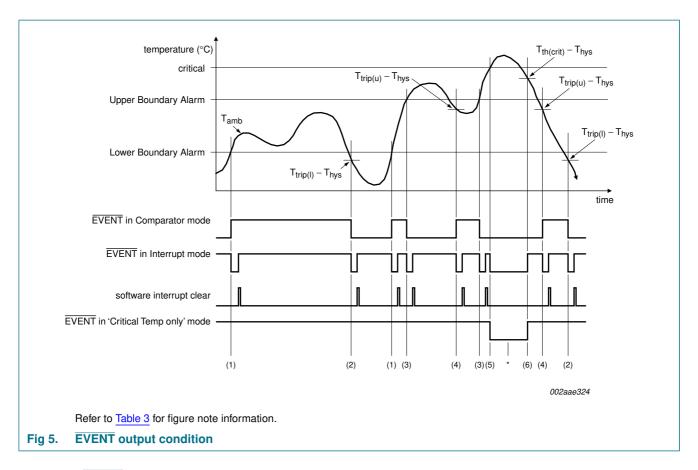

## 7.3 **EVENT** output condition

The EVENT output indicates conditions such as the temperature crossing a predefined boundary. The EVENT modes are very configurable and selected using the configuration register (CONFIG). The interrupt mode or comparator mode is selected using CONFIG[0], using either TCRIT/UPPER/LOWER or TCRIT only temperature bands (CONFIG[2]) as modified by hysteresis (CONFIG[10:9]). The UPPER/LOWER (CONFIG[6]) and TCRIT (CONFIG[7]) bands can be locked. Figure 5 shows an example of the measured temperature versus time, with the corresponding behavior of the EVENT output in each of these modes.

Upon device power-up, the default condition for the EVENT output is high-impedance to prevent spurious or unwanted alarms, but can be later enabled (CONFIG[3]). EVENT output polarity can be set to active HIGH or active LOW (CONFIG[1]). EVENT status can be read (CONFIG[4]) and cleared (CONFIG[5]).

#### · Advisory note:

- NXP device: After power-up, bit 3 (1) and bit 2 or bit 0 (leave as 0 or 1) can be set at the same time (e.g., in same byte) but once bit 3 is set (1) then changing bit 2 or bit 0 has no effect on the device operation.

- Competitor device: Does not require that bit 3 be cleared (e.g., set back to (0)) before changing bit 2 or bit 0.

- Work-around: In order to change bit 2 or bit 0 once bit 3 (1) is set, bit 3 (0) must be cleared in one byte and then change bit 2 or bit 0 and reset bit 3 (1) in the next byte.

- SE98B will allow bit 2 or bit 0 to be changed even if bit 3 is set.

If the device enters Shutdown mode (CONFIG[8]) with asserted EVENT output, the output remains asserted during shutdown.

### 7.3.1 **EVENT** pin output voltage levels and resistor sizing

The EVENT open-drain output is typically pulled up to a voltage level from 0.9 V to 3.6 V with an external pull-up resistor, but there is no real lower limit on the pull-up voltage for the EVENT pin since it is simply an open-drain output. It could be pulled up to 0.1 V and would not affect the output. From the system perspective, there will be a practical limit. That limit will be the voltage necessary for the device monitoring the interrupt pin to detect a HIGH on its input. A possible practical limit for a CMOS input would be 0.4 V. Another thing to consider is the value of the pull-up resistor. When a low supply voltage is applied to the drain (through the pull-up resistor) it is important to use a higher value pull-up resistor, to allow a larger maximum signal swing on the EVENT pin.

### DDR memory module temp sensor, 3.3 V

Table 3. **EVENT** output condition

| Figure | <b>EVENT</b> output boundary         | Ē                  | VENT outpu        | Temperature Register Status bits |                                     |                                    |                                    |

|--------|--------------------------------------|--------------------|-------------------|----------------------------------|-------------------------------------|------------------------------------|------------------------------------|

| note   | conditions                           | Comparator<br>mode | Interrupt<br>mode | Critical Temp<br>only mode       | Bit 15<br>Above<br>Critical<br>Trip | Bit 14<br>Above<br>Alarm<br>Window | Bit 13<br>Below<br>Alarm<br>Window |

| (1)    | $T_{amb} \ge T_{trip(I)}$            | Н                  | L                 | Н                                | 0                                   | 0                                  | 0                                  |

| (2)    | $T_{amb} < T_{trip(I)} - T_{hys}$    | L                  | L                 | Н                                | 0                                   | 0                                  | 1                                  |

| (3)    | $T_{amb} > T_{trip(u)}$              | L                  | L                 | Н                                | 0                                   | 1                                  | 0                                  |

| (4)    | $T_{amb} \leq T_{trip(u)} - T_{hys}$ | Н                  | L                 | Н                                | 0                                   | 0                                  | 0                                  |

| (5)    | $T_{amb} \ge T_{th(crit)}$           | L                  | L                 | L                                | 1                                   | 1                                  | 0                                  |

| (6)    | $T_{amb} < T_{th(crit)} - T_{hys}$   | L                  | Н                 | Н                                | 0                                   | 1                                  | 0                                  |

When  $T_{amb} \ge T_{th(crit)}$  and  $T_{amb} < T_{th(crit)} - T_{hys}$  the  $\overline{\text{EVENT}}$  output is in Comparator mode and bit 0 of CONFIG ( $\overline{\text{EVENT}}$  output mode) is ignored.

#### DDR memory module temp sensor, 3.3 V

#### 7.3.2 **EVENT** thresholds

#### 7.3.2.1 Alarm window

The device provides a comparison window with an UPPER trip point and a LOWER trip point, programmed through the Upper Boundary Alarm Trip register (02h), and Lower Boundary Alarm Trip register (03h). The Upper Boundary Alarm Trip register holds the upper temperature trip point, while the Lower Boundary Alarm Trip register holds the lower temperature trip point as modified by hysteresis as programmed in the Configuration register. When enabled, the EVENT output triggers whenever entering or exiting (crossing above or below) the alarm window.

#### · Advisory note:

- NXP Device: The EVENT output can be cleared through the Clear EVENT bit or SMBus Alert.

- Competitor Device: The EVENT output can be cleared only through the Clear EVENT bit.

- Work-around: Only clear EVENT output using the EVENT bit.

- There will be no change to the NXP device.

The Upper Boundary Alarm Trip should always be set above the Lower Boundary Alarm Trip.

#### Advisory note:

- NXP device: Requires one conversion cycle (125 ms) after setting the alarm window before comparing the alarm limit with temperature register to ensure that there is correct data in the temperature register before comparing with the Alarm Window and operating EVENT output.

- Competitor devices: Compares the alarm limit with temperature register at any time, so they get the EVENT output immediately when new UPPER or LOWER and Event B3 are set at the same time.

- Work-around: Wait at least 125 ms before enabling EVENT output.

- SE98B will compare alarm window and temperature register immediately after setting.

#### 7.3.2.2 Critical trip

The  $T_{th(crit)}$  temperature setting is programmed in the Critical Alarm Trip register (04h) as modified by hysteresis as programmed in the Configuration register. When the temperature reaches the critical temperature value in this register (and  $\overline{\text{EVENT}}$  is enabled), the  $\overline{\text{EVENT}}$  output asserts and cannot be de-asserted until the temperature drops below the critical temperature threshold. The Event cannot be cleared through the Clear  $\overline{\text{EVENT}}$  bit or SMBus Alert.

The Critical Alarm Trip should always be set above the Upper Boundary Alarm Trip.

#### · Advisory note:

NXP device: Requires one conversion cycle (125 ms) after setting the alarm window before comparing the alarm limit with temperature register to ensure that there is correct data in the temperature register before comparing with the Alarm Window and operating EVENT output.

© NXP B.V. 2009. All rights reserved.

## DDR memory module temp sensor, 3.3 V

- Competitor devices: Compares the alarm limit with temperature register at any time, so they get the EVENT output immediately when new T<sub>th(crit)</sub> and Event B3 are set at the same time.

- Work-around: Wait at least 125 ms before enabling EVENT output. Intel will

change Nehalem BIOS so that T<sub>th(crit)</sub> is set for more than 125 ms before Event B3

is enabled and Event value is checked.

- 1. Set T<sub>th(crit)</sub>.

- 2. Doing something else (make sure that exceeds 125 ms).

- 3. Enable the  $\overline{\text{EVENT}}$  output (B3 = 1).

- 4. Wait 20 μs.

- 5. Read Event value.

- SE98B will compare alarm window and temperature register immediately after setting.

#### 7.3.3 Event operation modes

#### 7.3.3.1 Comparator mode

In comparator mode, the EVENT output behaves like a window-comparator output that asserts when the temperature is outside the window (e.g., above the value programmed in the Upper Boundary Alarm Trip register or below the value programmed in the Lower Boundary Alarm Trip register or above the Critical Alarm Trip resister if  $T_{th(crit)}$  only is selected). Reads/writes on the registers do not affect the  $\overline{EVENT}$  output in comparator mode. The  $\overline{EVENT}$  signal remains asserted until the temperature goes inside the alarm window or the window thresholds are reprogrammed so that the current temperature is within the alarm window.

The comparator mode is useful for thermostat-type applications, such as turning on a cooling fan or triggering a system shutdown when the temperature exceeds a safe operating range.

#### 7.3.3.2 Interrupt mode

In interrupt mode,  $\overline{\text{EVENT}}$  asserts whenever the temperature crosses an alarm window threshold. After such an event occurs, writing a 1 to the Clear  $\overline{\text{EVENT}}$  bit in the configuration register de-asserts the  $\overline{\text{EVENT}}$  output until the next trigger condition occurs.

In interrupt mode,  $\overline{\text{EVENT}}$  asserts when the temperature crosses the alarm upper boundary. If the  $\overline{\text{EVENT}}$  output is cleared and the temperature continues to increase until it crosses the critical temperature threshold,  $\overline{\text{EVENT}}$  asserts again. Because the temperature is greater than the critical temperature threshold, a Clear  $\overline{\text{EVENT}}$  command does not clear the  $\overline{\text{EVENT}}$  output. Once the temperature drops below the critical temperature,  $\overline{\text{EVENT}}$  de-asserts immediately.

#### · Advisory note:

NXP device: If the EVENT output is not cleared before the temperature goes above the critical temperature threshold EVENT de-asserts immediately when temperature drops below the critical temperature.

#### DDR memory module temp sensor, 3.3 V

- Competitor devices: If the EVENT output is not cleared before or when the temperature is in the critical temperature threshold, EVENT will remain asserted after the temperature drops below the critical temperature until a Clear EVENT command.

- Work-around: Always clear the EVENT output before temperature exceeds the critical temperature.

- SE98B will keep EVENT asserted after the temperature drops below the critical temperature until a Clear EVENT command de-asserts EVENT.

#### 7.4 Conversion rate

The conversion time is the amount of time required for the ADC to complete a temperature measurement for the local temperature sensor. The conversion rate is the inverse of the conversion period which describes the number of cycles the temperature measurement completes in one second—the faster the conversion rate, the faster the temperature reading is updated. The SE98's conversion rate is at least 8 Hz or 125 ms.

### 7.5 Power-up default condition

After power-on, the SE98 is initialized to the following default condition:

- · Starts monitoring local sensor

- EVENT register is cleared—EVENT output is pulled HIGH by external pull-ups

- EVENT hysteresis is defaulted to 0 °C

- · Command pointer is defaulted to '00h'

- Critical Temp, Alarm Temperature Upper and Lower Boundary Trip register are defaulted to 0 °C

- Capability register is defaulted to '0015h'

- · Operational mode: comparator

- SMBus register is defaulted to '00h'

#### 7.6 Device initialization

SE98 temperature sensors have programmable registers, which, upon power-up, default to zero. The open-drain EVENT output is default to being disabled, comparator mode and active LOW. The alarm trigger registers default to being unprotected. The configuration registers, upper and lower alarm boundary registers and critical temperature window are defaulted to zero and need to be programmed to the desired values. SMBus TIMEOUT feature defaults to being enabled and can be programmed to disable. These registers are required to be initialized before the device can properly function. Except for the SPD, which does not have any programmable registers, and does not need to be initialized.

<u>Table 4</u> shows the default values and the example value to be programmed to these registers.

## DDR memory module temp sensor, 3.3 V

| Table 4. | Registers | to be | initialized |

|----------|-----------|-------|-------------|

|----------|-----------|-------|-------------|

| Register | Default value | Example value | Description                                       |

|----------|---------------|---------------|---------------------------------------------------|

| 01h      | 0000h         | 0209h         | Configuration register                            |

|          |               |               | <ul> <li>hysteresis = 1.5 °C</li> </ul>           |

|          |               |               | <ul> <li>EVENT output = Interrupt mode</li> </ul> |

|          |               |               | <ul> <li>EVENT output is enabled</li> </ul>       |

| 02h      | 0000h         | 0550h         | Upper Boundary Alarm Trip register = 85 °C        |

| 03h      | 0000h         | 1F40h         | Lower Boundary Alarm Trip register = -20 °C       |

| 04h      | 0000h         | 05F0h         | Critical Alarm Trip register = 95 °C              |

| 22h      | 0000h         | 0000h         | SMBus register = no change                        |

#### 7.7 SMBus time-out

The SE98 supports the SMBus time-out feature. If the host holds SCL LOW between 25 ms and 35 ms, the SE98 would reset its internal state machine to the bus idle state to prevent the system bus hang-up. This feature is turned on by default. The SMBus time-out is disabled by writing a logic 1 to bit 7 of register 22h.

**Remark:** When SMBus time-out is enabled, the I<sup>2</sup>C-bus minimum bus speed is limited by the SMBus time-out timer, and goes down to only 10 kHz.

#### 7.8 SMBus Alert

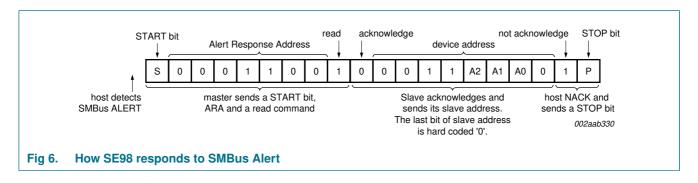

The SE98 supports SMBus Alert when it is programmed for the Interrupt mode and when the EVENT polarity bit is set to logic 0. The EVENT pin can be ANDed with other EVENT or ALERT signals from other slave devices to signal their intention to communicate with the host controller. When the host detects EVENT or ALERT signal LOW, it issues an Alert Response Address (ARA) to which a slave device would respond with its address. When there are multiple slave devices generating an Alert the SE98 performs bus arbitration. If it wins the bus, it responds to the ARA and then clears the EVENT pin.

**Remark:** Either in comparator mode or when the SE98 crosses the critical temperature, the host must also read the  $\overline{\text{EVENT}}$  status bit and provide remedy to the situation by bringing the temperature to within the alarm window or below the critical temperature if that bit is set. Otherwise, the  $\overline{\text{EVENT}}$  pin will not get de-asserted.

© NXP B.V. 2009. All rights reserved.

#### DDR memory module temp sensor, 3.3 V

## 7.9 SMBus/I<sup>2</sup>C-bus interface

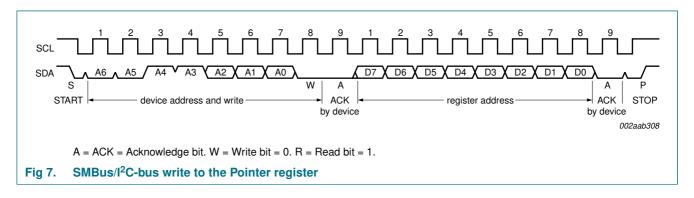

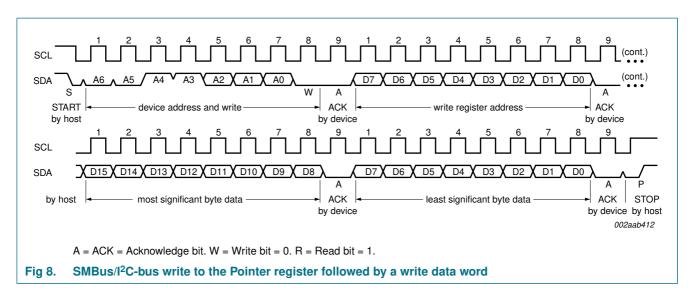

The data registers in this device are selected by the Pointer register. At power-up, the Pointer register is set to '00', the location for the Capability register. The Pointer register latches the last location it was set to. Each data register falls into one of three types of user accessibility:

- · Read only

- · Write only

- Write/Read same address.

A 'write' to this device will always include the address byte and the pointer byte. A write to any register other than the Pointer register requires two data bytes.

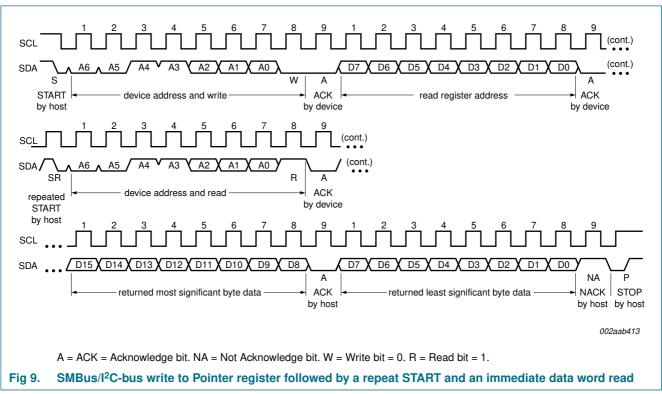

Reading this device can take place either of two ways:

- If the location latched in the Pointer register is correct (most of the time it is expected that the Pointer register will point to one of the Temperature register (as it will be the data most frequently read), then the read can simply consist of an address byte, followed by retrieving the two data bytes.

- If the Pointer register needs to be set, then an address byte, pointer byte, repeat START, and another address byte will accomplish a read.

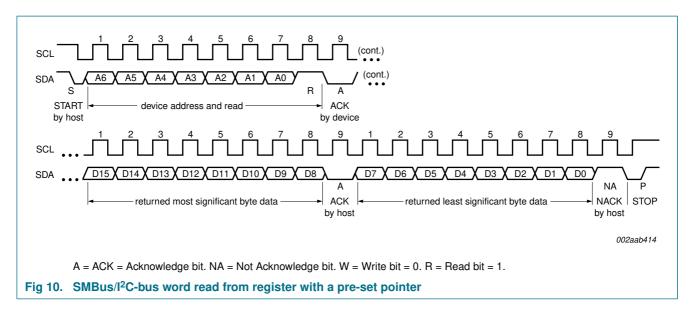

The data byte has the most significant bit first. At the end of a read, this device can accept either Acknowledge (ACK) or No Acknowledge (NACK) from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte). It takes this device 125 ms to measure the temperature. Refer to the timing diagrams in <a href="Figure 7">Figure 8</a>, Figure 9 and Figure 10 on how to program the device.

## DDR memory module temp sensor, 3.3 V

#### DDR memory module temp sensor, 3.3 V

### 7.10 Hot plugging

The SE98 can be used in hot plugging applications. Internal circuitry prevents damaging current backflow through the device when it is powered down, but with the I²C-bus, EVENT or address pins still connected. The open-drain SDA and EVENT pins (SCL and address pins are input only) effectively places the outputs in a high-impedance state during power-up and power-down, which prevents driver conflict and bus contention. The 50 ns noise filter will filter out any insertion glitches from the state machine, which is very robust and not prone to false operation.

The device needs a proper power-up sequence to reset itself, not only for the device I<sup>2</sup>C-bus and I/O initial states, but also to load specific pre-defined data or **calibration** data into its operational registers. The power-up sequence should occur correctly with a fast ramp rate and the I<sup>2</sup>C-bus active. The SE98 might not respond immediately after power-up, but it should not damage the part if the power-up sequence is abnormal. If the SCL line is held LOW, the part will not exit the power-on reset mode since the part is held in reset until SCL is released.

DDR memory module temp sensor, 3.3 V

## 8. Register descriptions

### 8.1 Register overview

This section describes all the registers used in the SE98. The registers are used for latching the temperature reading, storing the low and high temperature limits, configuring, the hysteresis threshold and the ADC, as well as reporting status. The device uses the Pointer register to access these registers. Read registers, as the name implies, are used for read only, and the write registers are for write only. Any attempt to read from a write-only register will result in reading zeroes. Writing to a read-only register will have no effect on the read even though the write command is acknowledged. The Pointer register is an 8-bit register. All other registers are 16-bit.

Table 5. Register summary

| Address         POR state         Register name           n/a         pointer register           00h         0015h         Capability register C grade = 0015h           01h         0000h         Configuration register           02h         0000h         Upper Boundary Alarm Trip register           03h         0000h         Lower Boundary Alarm Trip register           04h         0000h         Critical Alarm Trip register           05h         n/a         Temperature register           06h         1131h         Manufacturer ID register           07h         A101h         Device ID/Revision register           08h to 21h         0000h         reserved registers           22h         0000h         SMBus register           23h to FFh         0000h         reserved registers | •          | •         |                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|-------------------------------------|

| 00h0015hCapability register C grade = 0015h01h0000hConfiguration register02h0000hUpper Boundary Alarm Trip register03h0000hLower Boundary Alarm Trip register04h0000hCritical Alarm Trip register05hn/aTemperature register06h1131hManufacturer ID register07hA101hDevice ID/Revision register08h to 21h0000hreserved registers22h0000hSMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Address    | POR state | Register name                       |

| 01h 0000h Configuration register 02h 0000h Upper Boundary Alarm Trip register 03h 0000h Lower Boundary Alarm Trip register 04h 0000h Critical Alarm Trip register 05h n/a Temperature register 06h 1131h Manufacturer ID register 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | n/a        | n/a       | Pointer register                    |

| 02h 0000h Upper Boundary Alarm Trip register 03h 0000h Lower Boundary Alarm Trip register 04h 0000h Critical Alarm Trip register 05h n/a Temperature register 06h 1131h Manufacturer ID register 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00h        | 0015h     | Capability register C grade = 0015h |

| 03h 0000h Lower Boundary Alarm Trip register 04h 0000h Critical Alarm Trip register 05h n/a Temperature register 06h 1131h Manufacturer ID register 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01h        | 0000h     | Configuration register              |

| 04h 0000h Critical Alarm Trip register 05h n/a Temperature register 06h 1131h Manufacturer ID register 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 02h        | 0000h     | Upper Boundary Alarm Trip register  |

| 05h n/a Temperature register 06h 1131h Manufacturer ID register 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 03h        | 0000h     | Lower Boundary Alarm Trip register  |

| 06h 1131h Manufacturer ID register 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 04h        | 0000h     | Critical Alarm Trip register        |

| 07h A101h Device ID/Revision register 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 05h        | n/a       | Temperature register                |

| 08h to 21h 0000h reserved registers 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 06h        | 1131h     | Manufacturer ID register            |

| 22h 0000h SMBus register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 07h        | A101h     | Device ID/Revision register         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 08h to 21h | 0000h     | reserved registers                  |

| 23h to FFh 0000h reserved registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22h        | 0000h     | SMBus register                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23h to FFh | 0000h     | reserved registers                  |

A write to reserved registers my cause unexpected results which may result in requiring a reset by removing and re-applying its power.

## DDR memory module temp sensor, 3.3 V

## 8.2 Capability register (00h, 16-bit read-only)

Table 6. Capability register (address 00h) bit allocation

| Bit    | 15       | 14 | 13  | 12     | 11     | 10   | 9    | 8 |

|--------|----------|----|-----|--------|--------|------|------|---|

| Symbol |          |    |     | RFU    | [10:3] |      |      |   |

| Reset  | 0        | 0  | 0   | 0      | 0      | 0    | 0    | 0 |

| Access | R        | R  | R   | R      | R      | R    | R    | R |

| Bit    | 7        | 6  | 5   | 4      | 3      | 2    | 1    | 0 |

| Symbol | RFU[2:0] |    | TRE | S[1:0] | WRNG   | HACC | BCAP |   |

| Reset  | 0        | 0  | 0   | 1      | 0      | 1    | 0    | 1 |

| Access | R        | R  | R   | R      | R      | R    | R    | R |

Table 7. Capability register (address 00h) bit description

| Bit  | Symbol | Description                                                                              |

|------|--------|------------------------------------------------------------------------------------------|

| 15:5 | RFU    | Reserved for future use. Must be zero.                                                   |

| 4:3  | TRES   | Temperature resolution. $10 - 0.125  ^{\circ}\text{C LSB}  (11\text{-bit})$              |

| 2    | WRNG   | Wider range. 1 — can read temperatures below 0 $^{\circ}$ C and set sign bit accordingly |

| 1    | HACC   | Higher accuracy (set during manufacture).  0 — C grade accuracy                          |

| 0    | BCAP   | Basic capability. 1 — has Alarm and Critical Trips interrupt capability.                 |

## DDR memory module temp sensor, 3.3 V

## 8.3 Configuration register (01h, 16-bit read/write)

Table 8. Configuration register (address 01h) bit allocation

| Bit     | 15   | 14   | 13    | 12    | 11    | 10  | 9     | 8    |

|---------|------|------|-------|-------|-------|-----|-------|------|

| Symbol  |      |      | RFU   |       |       | HEN | [1:0] | SHMD |

| Default | 0    | 0    | 0     | 0     | 0     | 0   | 0     | 0    |

| Access  | R    | R    | R     | R     | R     | R/W | R/W   | R/W  |

| Bit     | 7    | 6    | 5     | 4     | 3     | 2   | 1     | 0    |

| Symbol  | CTLB | AWLB | CEVNT | ESTAT | EOCTL | CVO | EP    | EMD  |

| Default | 0    | 0    | 0     | 0     | 0     | 0   | 0     | 0    |

| Access  | R/W  | R/W  | R/W   | R/W   | R/W   | R/W | R/W   | R/W  |

| Table 9. | Configu | rration register (address 01h) bit description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15:11    | RFU     | reserved for future use; must be '0'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10:9     | HEN     | Hysteresis Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |         | 00 — Disable hysteresis (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |         | 01 — Enable hysteresis at 1.5 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |         | 10 — Enable hysteresis at 3 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |         | 11 — Enable hysteresis at 6 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |         | When enabled, hysteresis is applied to temperature movement around trigger points. For example, consider the behavior of the 'Above Alarm Window' bit (bit 14 of the Temperature register) when the hysteresis is set to 3 °C. As the temperature rises, bit 14 will be set to 1 (temperature is above the alarm window) when the Temperature register contains a value that is greater than the value in the Alarm Temperature Upper Boundary register. If the temperature decreases, bit 14 will remain set until the measured temperature is less than or equal to the value in the Alarm Temperature Upper Boundary register minus 3 °C. (Refer to Figure 5 and Table 10). |

|          |         | Similarly, the 'Below Alarm Window' bit (bit 13 of the Temperature register) will be set to 0 (temperature is equal to or above the Alarm Window Lower Boundary Trip register) when the value in the Temperature register is equal to or greater than the value in the Alarm Temperature Lower Boundary register. As the temperature decreases, bit 13 will be set to 1 when the value                                                                                                                                                                                                                                                                                         |

When either of the lock bits is set, these bits cannot be altered.

8 SHMD

Shutdown Mode.

0 — Enabled Temperature Sensor (default)

1 — Disabled Temperature Sensor

also applied to EVENT pin functionality.

When shut down, the thermal sensor diode and Analog-to-Digital Converter (ADC) are disabled to save power, no events will be generated. When either of the lock bits is set, this bit cannot be set until unlocked. However, it can be cleared at any time.

in the Temperature register is equal to or less than the value in the Alarm Temperature Lower Boundary register minus 3 °C. Note that hysteresis is

© NXP B.V. 2009. All rights reserved.

## DDR memory module temp sensor, 3.3 V

| Table 9. | Configuration | register | (address 01 | h) bit o | description | .continued |

|----------|---------------|----------|-------------|----------|-------------|------------|

|          |               |          |             |          |             |            |

| Dia | Cumchal | Description                                                                                                                                                                                                    |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Symbol  | Description                                                                                                                                                                                                    |

| 7   | CTLB    | Critical Trip Lock bit.                                                                                                                                                                                        |

|     |         | <ul> <li>0 — Critical Alarm Trip register is not locked and can be altered (default).</li> </ul>                                                                                                               |

|     |         | <ol> <li>Critical Alarm Trip register settings cannot be altered.</li> </ol>                                                                                                                                   |

|     |         | This bit is initially cleared. When set, this bit will return a 1, and remains locked until cleared by internal Power-on reset. This bit can be written with a single write and do not require double writes.  |

| 6   | AWLB    | Alarm Window Lock bit.                                                                                                                                                                                         |

|     |         | <ul> <li>Upper and Lower Alarm Trip registers are not locked and can be<br/>altered (default).</li> </ul>                                                                                                      |

|     |         | <ol> <li>Upper and Lower Alarm Trip registers setting cannot be altered.</li> </ol>                                                                                                                            |

|     |         | This bit is initially cleared. When set, this bit will return a 1 and remains locked until cleared by internal power-on reset. This bit can be written with a single write and does not require double writes. |

| 5   | CEVNT   | Clear EVENT (write only).                                                                                                                                                                                      |

|     |         | 0 — No effect (default).                                                                                                                                                                                       |

|     |         | 1 — Clears active $\overline{\text{EVENT}}$ in Interrupt mode. Writing to this register has no effect in Comparator mode.                                                                                      |

|     |         | When read, this register always returns zero.                                                                                                                                                                  |

| 4   | ESTAT   | EVENT Status (read only).                                                                                                                                                                                      |

|     |         | $0 - \overline{\text{EVENT}}$ output condition is not being asserted by this device (default).                                                                                                                 |

|     |         | 1 — EVENT output pin is being asserted by this device due to Alarm Window or Critical Trip condition.                                                                                                          |

|     |         | The actual event causing the event can be determined from the Read Temperature register. Interrupt Events can be cleared by writing to the 'Clear EVENT' bit. Writing to this bit will have no effect.         |

| 3   | EOCTL   | EVENT Output Control.                                                                                                                                                                                          |

|     |         | 0 — EVENT output disabled (default).                                                                                                                                                                           |

|     |         | 1 — EVENT output enabled.                                                                                                                                                                                      |

|     |         | When either of the lock bits is set, this bit cannot be altered until unlocked.                                                                                                                                |

| 2   | CVO     | Critical Event Only.                                                                                                                                                                                           |

|     |         | $0 - \overline{\text{EVENT}}$ output on Alarm or Critical temperature event (default)                                                                                                                          |

|     |         | 1 — EVENT only if temperature is above the value in the critical temperature register                                                                                                                          |

|     |         | When the Critical Trip or Alarm Window lock bit is set, this bit cannot be altered until unlocked.                                                                                                             |

|     |         | Advisory note:                                                                                                                                                                                                 |

|     |         | <ul> <li>JEDEC specification requires only the Alarm Window lock bit to be<br/>set.</li> </ul>                                                                                                                 |

|     |         | <ul> <li>Workaround: Clear both Critical Trip and Alarm Window lock bits.</li> </ul>                                                                                                                           |

|     |         | <ul> <li>Future 1.7 V to 3.6 V SE98B will require only the Alarm Window lock<br/>bit to be set.</li> </ul>                                                                                                     |

## DDR memory module temp sensor, 3.3 V

Table 9. Configuration register (address 01h) bit description ... continued

| Bit | Symbol | Description                                                                                                           |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------|

| 1   | EP     | EVENT Polarity.                                                                                                       |

|     |        | 0 — active LOW (default).                                                                                             |

|     |        | 1 — active HIGH. When either of the alarm or critical lock bits is set, this<br>bit cannot be altered until unlocked. |

| 0   | EMD    | EVENT Mode.                                                                                                           |

|     |        | 0 — comparator output mode (default)                                                                                  |

|     |        | 1 — interrupt mode                                                                                                    |

|     |        | When either of the alarm or critical lock bits is set, this bit cannot be altered until unlocked.                     |

Table 10. Hysteresis enable

| Action | Below Alarm Window Bit (bit 13) |                         | Above Alarm W     | /indow Bit (bit 14)     | Above Critical Trip bit (bit 15) |                          |  |

|--------|---------------------------------|-------------------------|-------------------|-------------------------|----------------------------------|--------------------------|--|

|        | Temperature slope               | Threshold temperature   | Temperature slope | Temperature             | Temperature slope                | Threshold temperature    |  |

| sets   | falling                         | $T_{trip(I)} - T_{hys}$ | rising            | $T_{trip(u)}$           | rising                           | T <sub>th(crit)</sub>    |  |

| clears | rising                          | $T_{trip(I)}$           | falling           | $T_{trip(u)} - T_{hys}$ | falling                          | $T_{th(crit)} - T_{hys}$ |  |

### DDR memory module temp sensor, 3.3 V

### 8.4 Temperature format

The 16-bit value used in the following Trip Point Set and Temperature Read-Back registers is 2's complement with the Least Significant Bit (LSB) equal to 0.0625 °C. For example:

- A value of 019Ch will represent 25.75 °C

- A value of 07C0h will represent 124 °C

- A value of 1E64h will represent -25.75 °C.

The resolution is 0.125  $^{\circ}$ C. The unused LSB (bit 0) is set to '0'. Bit 11 will have a resolution of 128  $^{\circ}$ C.

The upper 3 bits of the temperature register indicate Trip Status based on the current temperature, and are not affected by the status of the EVENT output.

<u>Table 11</u> lists the examples of the content of the temperature data register for positive and negative temperature for two scenarios of status bits: status bits = 000b and status bits = 111b.

Table 11. Degree Celsius and Temperature Data register

| Temperature | Content of Temperature Data register |       |                      |       |  |  |  |  |  |  |

|-------------|--------------------------------------|-------|----------------------|-------|--|--|--|--|--|--|

|             | Status bits = 000b                   |       | Status bits = 111b   |       |  |  |  |  |  |  |

|             | Binary                               | Hex   | Binary               | Hex   |  |  |  |  |  |  |

| +125 °C     | 000 0 01111101 000 0                 | 07D0h | 111 0 01111101 000 0 | E7D0h |  |  |  |  |  |  |

| +25 °C      | 000 0 00011001 000 0                 | 0190h | 111 0 00011001 000 0 | E190h |  |  |  |  |  |  |

| +1 °C       | 000 0 00000001 000 0                 | 0010h | 111 0 00000001 000 0 | E010h |  |  |  |  |  |  |

| +0.25 °C    | 000 0 00000000 010 0                 | 0004h | 111 0 00000000 010 0 | E004h |  |  |  |  |  |  |

| +0.125 °C   | 000 0 00000000 001 0                 | 0002h | 111 0 00000000 001 0 | E002h |  |  |  |  |  |  |

| 0 °C        | 000 0 00000000 000 0                 | 0000h | 111 0 00000000 000 0 | E000h |  |  |  |  |  |  |

| –0.125 °C   | 000 1 11111111 111 0                 | 1FFEh | 111 1 11111111 111 0 | FFFEh |  |  |  |  |  |  |

| –0.25 °C    | 000 1 11111111 110 0                 | 1FFCh | 111 1 11111111 110 0 | FFFCh |  |  |  |  |  |  |

| −1 °C       | 000 1 11111111 000 0                 | 1FF0h | 111 1 11111111 000 0 | FFF0h |  |  |  |  |  |  |

| –20 °C      | 000 1 11110100 000 0                 | 1F40h | 111 1 11110100 000 0 | FF40h |  |  |  |  |  |  |

| –25 °C      | 000 1 11100111 000 0                 | 1E70h | 111 1 11100111 000 0 | FE70h |  |  |  |  |  |  |

| –55 °C      | 000 1 11001001 000 0                 | 1C90h | 111 1 11001001 000 0 | FC90h |  |  |  |  |  |  |

### DDR memory module temp sensor, 3.3 V

## 8.5 Temperature Trip Point registers

### 8.5.1 Upper Boundary Alarm Trip register (16-bit read/write)

The value is the upper threshold temperature value for Alarm mode. The data format is 2's complement with bit 2 = 0.25 °C. 'RFU' bits will always report zero. Interrupts will respond to the presently programmed boundary values. If boundary values are being altered in-system, it is advised to turn off interrupts until a known state can be obtained to avoid superfluous interrupt activity.

Table 12. Upper Boundary Alarm Trip register bit allocation

|        | - 1-1- | ,   |     | 3     |     |     |       |     |

|--------|--------|-----|-----|-------|-----|-----|-------|-----|

| Bit    | 15     | 14  | 13  | 12    | 11  | 10  | 9     | 8   |

| Symbol |        | RFU |     | SIGN  |     | UBT | [9:6] |     |

| Reset  | 0      | 0   | 0   | 0     | 0   | 0   | 0     | 0   |

| Access | R      | R   | R   | R/W   | R/W | R/W | R/W   | R/W |

| Bit    | 7      | 6   | 5   | 4     | 3   | 2   | 1     | 0   |

| Symbol |        |     | UBT | [5:0] |     |     | RI    | FU  |

| Reset  | 0      | 0   | 0   | 0     | 0   | 0   | 0     | 0   |

| Access | R/W    | R/W | R/W | R/W   | R/W | R/W | R     | R   |

Table 13. Upper Boundary Alarm Trip register bit description

| Bit   | Symbol | Description                                           |

|-------|--------|-------------------------------------------------------|

| 15:13 | RFU    | reserved; always 0                                    |

| 12    | SIGN   | Sign (MSB)                                            |

| 11:2  | UBT    | Upper Boundary Alarm Trip Temperature (LSB = 0.25 °C) |

| 1:0   | RFU    | reserved; always 0                                    |

#### DDR memory module temp sensor, 3.3 V

### 8.5.2 Lower Boundary Alarm Trip register (16-bit read/write)

The value is the lower threshold temperature value for Alarm mode. The data format is 2's complement with bit 2 = 0.25 °C. RFU bits will always report zero. Interrupts will respond to the presently programmed boundary values. If boundary values are being altered in-system, it is advised to turn off interrupts until a known state can be obtained to avoid superfluous interrupt activity.

Table 14. Lower Boundary Alarm Trip register bit allocation

|        |     | -   | -   | •     |     |     |       |     |

|--------|-----|-----|-----|-------|-----|-----|-------|-----|

| Bit    | 15  | 14  | 13  | 12    | 11  | 10  | 9     | 8   |

| Symbol |     | RFU |     | SIGN  |     | LBT | [9:6] |     |

| Reset  | 0   | 0   | 0   | 0     | 0   | 0   | 0     | 0   |

| Access | R   | R   | R   | R/W   | R/W | R/W | R/W   | R/W |

| Bit    | 7   | 6   | 5   | 4     | 3   | 2   | 1     | 0   |

| Symbol |     |     | LBT | [5:0] |     |     | RI    | FU  |

| Reset  | 0   | 0   | 0   | 0     | 0   | 0   | 0     | 0   |

| Access | R/W | R/W | R/W | R/W   | R/W | R/W | R     | R   |

Table 15. Lower Boundary Alarm Trip register bit description

| Bit   | Symbol | Description                                           |

|-------|--------|-------------------------------------------------------|

| 15:13 | RFU    | reserved; always 0                                    |

| 12    | SIGN   | Sign (MSB)                                            |

| 11:2  | LBT    | Lower Boundary Alarm Trip Temperature (LSB = 0.25 °C) |

| 1:0   | RFU    | reserved; always 0                                    |

### 8.5.3 Critical Alarm Trip register (16-bit read/write)

The value is the critical temperature. The data format is 2's complement with bit 2 = 0.25 °C. RFU bits will always report zero.

Table 16. Lower Boundary Alarm Trip register bit allocation

|        |     | ,   |     | 9.0.0 |     |     |      |     |

|--------|-----|-----|-----|-------|-----|-----|------|-----|

| Bit    | 15  | 14  | 13  | 12    | 11  | 10  | 9    | 8   |

| Symbol |     | RFU |     | SIGN  |     | CT[ | 9:6] |     |

| Reset  | 0   | 0   | 0   | 0     | 0   | 0   | 0    | 0   |

| Access | R   | R   | R   | R/W   | R/W | R/W | R/W  | R/W |

| Bit    | 7   | 6   | 5   | 4     | 3   | 2   | 1    | 0   |

| Symbol |     |     | CT  | [5:0] |     |     | RI   | FU  |

| Reset  | 0   | 0   | 0   | 0     | 0   | 0   | 0    | 0   |

| Access | R/W | R/W | R/W | R/W   | R/W | R/W | R    | R   |

Table 17. Critical Alarm Trip register bit description

| Bit   | Symbol | Description                                     |

|-------|--------|-------------------------------------------------|

| 15:13 | RFU    | reserved; always 0                              |

| 12    | SIGN   | Sign (MSB)                                      |

| 11:2  | CT     | Critical Alarm Trip Temperature (LSB = 0.25 °C) |

| 1:0   | RFU    | reserved; always 0                              |

© NXP B.V. 2009. All rights reserved

### DDR memory module temp sensor, 3.3 V

## 8.6 Temperature register (16-bit read-only)

Table 18. Temperature register bit allocation

|        |     | 3.00 |     |           |    |      |        |     |

|--------|-----|------|-----|-----------|----|------|--------|-----|

| Bit    | 15  | 14   | 13  | 12        | 11 | 10   | 9      | 8   |

| Symbol | ACT | AAW  | BAW | SIGN      |    | TEMP | [10:7] |     |

| Reset  | 0   | 0    | 0   | 0         | 0  | 0    | 0      | 0   |

| Access | R   | R    | R   | R         | R  | R    | R      | R   |

| Bit    | 7   | 6    | 5   | 4         | 3  | 2    | 1      | 0   |

| Symbol |     |      |     | TEMP[6:0] |    |      |        | RFU |

| Reset  | 0   | 0    | 0   | 0         | 0  | 0    | 0      | 0   |

| Access | R   | R    | R   | R         | R  | R    | R      | R   |

Table 19. Temperature register bit description

| Bit  | Symbol | Description                                                                   |

|------|--------|-------------------------------------------------------------------------------|

| 15   | ACT    | Above Critical Trip.                                                          |

|      |        | 0 — temperature is below the Critical Alarm Trip register setting             |

|      |        | 1 — temperature is equal to or above the Critical Alarm Trip register setting |

| 14   | AAW    | Above Alarm Window.                                                           |

|      |        | 0 — temperature is equal to or below the Upper Boundary Alarm Trip register   |

|      |        | 1 — temperature is above the Alarm window                                     |

| 13   | BAW    | Below Alarm Window.                                                           |

|      |        | 0 — temperature is equal to or above the Lower Boundary Alarm Trip register   |

|      |        | 1 — temperature is below the Alarm window                                     |

| 12   | SIGN   | Sign bit.                                                                     |

|      |        | 0 — positive temperature value                                                |

|      |        | 1 — negative temperature value                                                |

| 11:1 | TEMP   | Temperature Value (2's complement). (LSB = $0.125  ^{\circ}$ C)               |

| 0    | RFU    | reserved; always 0                                                            |

|      |        |                                                                               |

## 8.7 Manufacturer's ID register (16-bit read-only)

The manufacture's ID matches that assigned to NXP Semiconductors PCI-SIG (1131h), and is intended for use to identify the manufacturer of the device.

Table 20. Manufacturer's ID register bit allocation

| Bit    | 15              | 14 | 13 | 12     | 11    | 10 | 9 | 8 |  |  |

|--------|-----------------|----|----|--------|-------|----|---|---|--|--|

| Symbol | Manufacturer ID |    |    |        |       |    |   |   |  |  |

| Reset  | 0               | 0  | 0  | 1      | 0     | 0  | 0 | 1 |  |  |

| Access | R               | R  | R  | R      | R     | R  | R | R |  |  |

| Bit    | 7               | 6  | 5  | 4      | 3     | 2  | 1 | 0 |  |  |

| Symbol |                 |    |    | (conti | nued) |    |   |   |  |  |

| Reset  | 0               | 0  | 1  | 1      | 0     | 0  | 0 | 1 |  |  |

| Access | R               | R  | R  | R      | R     | R  | R | R |  |  |

© NXP B.V. 2009. All rights reserved.

## DDR memory module temp sensor, 3.3 V

## 8.8 Device ID register

The device ID and device revision are A1h and 00h, respectively.

Table 21. Device ID register bit allocation

| Bit 15 14 13 12 11 10 9 Symbol Device ID | 8               |  |  |  |  |  |  |

|------------------------------------------|-----------------|--|--|--|--|--|--|

| Symbol Device ID                         |                 |  |  |  |  |  |  |

| 20110012                                 | Device ID       |  |  |  |  |  |  |

| <b>Reset</b> 1 0 1 0 0 0 0               | 1               |  |  |  |  |  |  |

| Access R R R R R R                       | R               |  |  |  |  |  |  |

| Bit 7 6 5 4 3 2 1                        | 0               |  |  |  |  |  |  |

| Symbol Device revision                   | Device revision |  |  |  |  |  |  |

| Reset 0 0 0 0 0 0 0                      | 1               |  |  |  |  |  |  |

| Access R R R R R R                       | R               |  |  |  |  |  |  |

## 8.9 SMBus register

Table 22. SMBus Time-out register bit allocation

| Bit    | 15     | 14        | 13 | 12 | 11 | 10 | 9 | 8     |

|--------|--------|-----------|----|----|----|----|---|-------|

| Symbol |        | RFU       |    |    |    |    |   |       |

| Reset  | 0      | 0         | 0  | 0  | 0  | 0  | 0 | 0     |

| Access | R      | R         | R  | R  | R  | R  | R | R     |

| Bit    | 7      | 6         | 5  | 4  | 3  | 2  | 1 | 0     |

| Symbol | STMOUT | RFU SALRT |    |    |    |    |   | SALRT |

| Reset  | 0      | 0         | 0  | 0  | 0  | 0  | 0 | 0     |

| Access | R/W    | R         | R  | R  | R  | R  | R | R/W   |

Table 23. SMBus Time-out register bit description

| Bit  | Symbol | Description                                                                                                                                                           |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | RFU    | reserved; always 0                                                                                                                                                    |

| 7    | STMOUT | SMBus time-out.  0 — SMBus time-out is enabled (default)  1 — disable SMBus time-out  When either of the lock bits is set, this bit cannot be altered until unlocked. |

| 6:1  | RFU    | reserved; always 0                                                                                                                                                    |

| 0    | SALRT  | SMBus Alert.  0 — SMBus Alert is enabled (default)  1 — disable SMBus Alert  When either of the lock bits is set, this bit cannot be altered until unlocked.          |

DDR memory module temp sensor, 3.3 V

## 9. Application design-in information

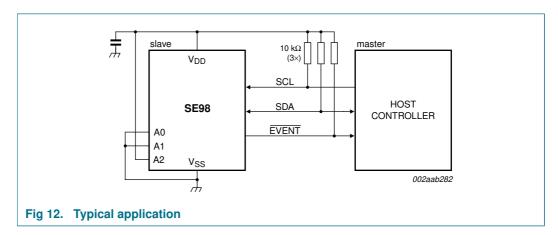

In a typical application, the SE98 behaves as a slave device and interfaces to the master (or host) via the SCL and SDA lines. The host monitors the  $\overline{\text{EVENT}}$  output pin, which is asserted when the temperature reading exceeds the programmed values in the alarm registers. The A0, A1 and A2 pins are directly connected to the shared SPD's A0, A1 and A2 pins, otherwise they must be pulled HIGH or LOW. The SDA and SCL serial interface pins are open-drain and require pull-up resistors, and are able to sink a maximum current of 3 mA with a voltage drop less than 0.4 V. Typical pull-up values for SCL and SDA are 10 k $\Omega$ , but the resistor values can be changed in order to meet the rise time requirement if the capacitance load is too large due to routing, connectors, or multiple components sharing the same bus.

#### 9.1 SE98 in memory module application

<u>Figure 13</u> shows the SE98 being placed in the memory module application. The SE98 is centered in the memory module to provide the function to monitor the temperature of the DRAM. In the event of overheat, the SE98 triggers the <u>EVENT</u> output and the memory controller can throttle the memory bus to slow the DRAM, or the CPU can increase the refresh rate for the DRAM. The memory controller can also read the SE98 and watch the DRAM thermal behavior.

© NXP B.V. 2009. All rights reserved.