Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### GLOBAL VOICE/DATA DIRECT ACCESS ARRANGEMENT

### **Features**

- PCM highway data interface

- μ-law/A-law companding

- SPI control interface

- GCI interface

- 80 dB dynamic range TX/RX

- Line voltage monitor

- Loop current monitor

- +3.2 dBm TX/RX level mode

- Parallel handset detection

- 3 µA on-hook line monitor current

- Overload detection

- Programmable line interface

- AC termination

- DC termination

- Ring detect threshold

- Ringer impedance

- TIP/RING polarity detection

- Integrated codec and 2- to 4-wire analog hybrid

- Programmable digital hybrid for near-end echo reduction

- Polarity reversal detection

- Programmable digital gain in 0.1 dB increments

- Integrated ring detector

- Type I and II caller ID support

- Pulse dialing support

- Billing tone detection

- 3.3 V power supply

- Daisy-chaining for up to 16 devices

- Greater than 5000 V isolation

- Patented isolation technology

- Ground start and loop start support

- Available in lead-free RoHS-compliant packages

# **Ordering Information** See page 102.

### **Applications**

- Computer telephony

- PBX systems

- POTS termination equipment

- Voice mail systems

- Video conferences IP telephony

### **Description**

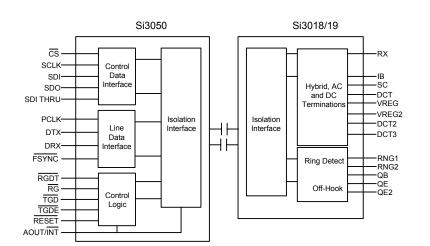

The Si3050 integrated direct access arrangement (DAA) provides a programmable line interface to meet global telephone line requirements. Available in one 20-pin TSSOP and one 16-pin TSSOP/SOIC, it eliminates the need for an analog front end (AFE), an isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid. The Si3050 dramatically reduces discrete components and the cost required to comply with global regulatory requirements. The Si3050 interfaces directly to standard telephony PCM interfaces.

### **Functional Block Diagram**

US Patent# 5,870,046 US Patent# 6,061,009 Other Patents Pending

2

# TABLE OF CONTENTS

| <u>Section</u>                               | <u>Page</u> |

|----------------------------------------------|-------------|

| 1. Electrical Specifications                 | 5           |

| 2. Typical Application Schematic             |             |

| 3. Bill of Materials                         |             |

| 4. AOUT PWM Output                           | 19          |

| 5. Functional Description                    |             |

| 5.1. Line-Side Device Support                |             |

| 5.2. Power Supplies                          |             |

| 5.3. Initialization                          |             |

| 5.4. Isolation Barrier                       |             |

| 5.5. Power Management                        | 24          |

| 5.6. Calibration                             |             |

| 5.7. In-Circuit Testing                      |             |

| 5.8. Exception Handling                      |             |

| 5.9. Revision Identification                 |             |

| 5.10. Transmit/Receive Full-Scale Level      |             |

| (Si3019 Line-Side Only)                      | 26          |

| 5.11. Parallel Handset Detection             | 26          |

| 5.12. Line Voltage/Loop Current Sensing      |             |

| 5.13. Off-Hook                               |             |

| 5.14. Ground Start Support                   |             |

| 5.15. Interrupts                             |             |

| 5.16. DC Termination                         |             |

| 5.17. AC Termination (Si3018 Line-Side Only) | 30          |

| 5.18. AC Termination (Si3019 Line-Side Only) |             |

| 5.19. Ring Detection                         |             |

| 5.20. Ring Validation                        |             |

| 5.21. Ringer Impedance and Threshold         | 33          |

| 5.22. Pulse Dialing and Spark Quenching      | 33          |

| 5.23. Billing Tone Detection and             |             |

| Receive Overload                             | 33          |

| 5.24. Billing Tone Filter (Optional)         | 34          |

| 5.25. On-Hook Line Monitor                   |             |

| 5.26. Caller ID                              | 34          |

| 5.27. Overload Detection                     | 36          |

| 5.28. Gain Control                           | 36          |

| 5.29. Transhybrid Balance                    | 37          |

| 5.30. Filter Selection                       | 37          |

| 5.31. Clock Generation                       |             |

| 5.32. Communication Interface Mode Selection | 38          |

| 5.33. PCM Highway                            |             |

| 5.34. Companding in PCM Mode                 | 42          |

# Si3050 Si3018/19

| 5.35. 16 kHz Sampling Operation in PCM Mode | 42        |

|---------------------------------------------|-----------|

| 5.36. SPI Control Interface                 | 45        |

| 5.37. GCI Highway                           | 49        |

| 5.38. Companding in GCI Mode                |           |

| 5.39. 16 kHz Sampling Operation in GCI Mode | 49        |

| 5.40. Monitor Channel                       |           |

| 5.41. Summary of Monitor Channel Commands   | 56        |

| 5.42. Device Address Byte                   | 56        |

| 5.43. Command Byte                          | 56        |

| 5.44. Register Address Byte                 | 56        |

| 5.45. SC Channel                            |           |

| 5.46. Receive SC Channel                    |           |

| 5.47. Transmit SC Channel                   |           |

| 6. Control Registers                        |           |

| Appendix—UL1950 3rd Edition                 |           |

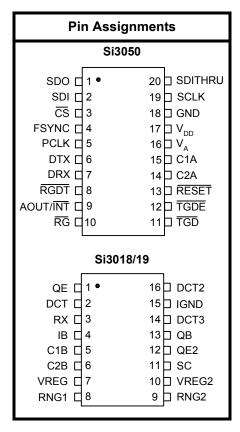

| 7. Pin Descriptions: Si3050                 |           |

| 8. Pin Descriptions: Si3018/1910            |           |

| 9. Ordering Guide                           |           |

| 10. Product Identification                  |           |

| 11. Package Outline: 20-Pin TSSOP10         |           |

| 12. Package Outline: 16-Pin SOIC            |           |

| Silicon Labs Si3050 Support Documentation10 |           |

| Document Change List                        |           |

| Contact Information                         | <b>D8</b> |

### 1. Electrical Specifications

### **Table 1. Recommended Operating Conditions**

| Parameter <sup>1</sup>         | Symbol         | Test Condition | Min <sup>2</sup> | Тур | Max <sup>2</sup> | Unit |

|--------------------------------|----------------|----------------|------------------|-----|------------------|------|

| Ambient Temperature            | T <sub>A</sub> | F/K-Grade      | 0                | 25  | 70               | °C   |

| Si3050 Supply Voltage, Digital | V <sub>D</sub> |                | 3.0              | 3.3 | 3.6              | V    |

### Notes:

- **1.** The Si3050 specifications are guaranteed when the typical application circuit (including component tolerance) and any Si3050 and any Si3018/19 are used. See "2.Typical Application Schematic" on page 17 for the typical application circuit.

- **2.** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

### **Table 2. Loop Characteristics**

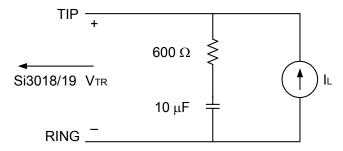

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \,^{\circ}\text{C} \text{ for K-Grade, see Figure 1 on page 6})$

| Parameter                 | Symbol          | Test Condition                                                    | Min   | Тур  | Max   | Unit             |

|---------------------------|-----------------|-------------------------------------------------------------------|-------|------|-------|------------------|

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 20 mA, ILIM = 0<br>DCV = 00, MINI = 11, DCR = 0  | _     | _    | 6.0   | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 120 mA, ILIM = 0<br>DCV = 00, MINI = 11, DCR = 0 | 9     | _    | _     | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 20 mA, ILIM = 0<br>DCV = 11, MINI = 00, DCR = 0  | _     | _    | 7.5   | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 120 mA, ILIM = 0<br>DCV = 11, MINI = 00, DCR = 0 | 9     | _    | _     | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 20 mA, ILIM = 1<br>DCV = 11, MINI = 00, DCR = 0  |       | _    | 7.5   | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 60 mA, ILIM = 1<br>DCV = 11, MINI = 00, DCR = 0  | 40    | _    | _     | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 50 mA, ILIM = 1<br>DCV = 11, MINI = 00, DCR = 0  |       | _    | 40    | V                |

| On-Hook Leakage Current   | I <sub>LK</sub> | V <sub>TR</sub> = -48 V                                           | _     | _    | 5     | μΑ               |

| Operating Loop Current    | I <sub>LP</sub> | MINI = 00, ILIM = 0                                               | 10    | _    | 120   | mA               |

| Operating Loop Current    | I <sub>LP</sub> | MINI = 00, ILIM = 1                                               | 10    | _    | 60    | mA               |

| DC Ring Current           |                 | dc current flowing through ring detection circuitry               |       | 1.5  | 3     | μA               |

| Ring Detect Voltage*      | $V_{RD}$        | RT2 = 0, RT = 0                                                   | 13.5  | 15   | 16.5  | V <sub>rms</sub> |

| Ring Detect Voltage*      | $V_{RD}$        | RT2 = 0, RT = 1                                                   | 19.35 | 21.5 | 23.65 | V <sub>rms</sub> |

| Ring Detect Voltage*      | $V_{RD}$        | RT2 = 1, RT = 1                                                   | 40.5  | 45   | 49.5  | V <sub>rms</sub> |

| Ring Frequency            | F <sub>R</sub>  |                                                                   | 13    | _    | 68    | Hz               |

| Ringer Equivalence Number | REN             |                                                                   | _     |      | 0.2   |                  |

\*Note: The ring signal is guaranteed to not be detected below the minimum. The ring signal is guaranteed to be detected above the maximum.

**Figure 1. Test Circuit for Loop Characteristics**

### Table 3. DC Characteristics, $V_D = 3.3 \text{ V}$

(V<sub>D</sub> = 3.0 to 3.6 V,  $T_A$  = 0 to 70 °C for F/K-Grade)

| Parameter                                       | Symbol          | Test Condition         | Min | Тур | Max  | Unit |

|-------------------------------------------------|-----------------|------------------------|-----|-----|------|------|

| High Level Input Voltage <sup>1</sup>           | V <sub>IH</sub> |                        | 2.0 | _   | _    | V    |

| Low Level Input Voltage <sup>1</sup>            | V <sub>IL</sub> |                        | _   | _   | 0.8  | V    |

| High Level Output Voltage                       | V <sub>OH</sub> | I <sub>O</sub> = -2 mA | 2.4 | _   | _    | V    |

| Low Level Output Voltage                        | V <sub>OL</sub> | I <sub>O</sub> = 2 mA  | _   | _   | 0.35 | V    |

| AOUT High Level Voltage                         | V <sub>AH</sub> | I <sub>O</sub> = 10 mA | 2.4 | _   | _    | V    |

| AOUT Low Level Voltage                          | V <sub>AL</sub> | I <sub>O</sub> = 10 mA | _   | _   | 0.35 | V    |

| Input Leakage Current                           | ΙL              |                        | -10 | _   | 10   | μA   |

| Power Supply Current, Digital <sup>2</sup>      | I <sub>D</sub>  | V <sub>D</sub> pin     | _   | 8.5 | 10   | mA   |

| Total Supply Current, Sleep Mode <sup>2</sup>   | I <sub>D</sub>  | PDN = 1, PDL = 0       | _   | 5.0 | 6.0  | mA   |

| Total Supply Current, Deep Sleep <sup>2,3</sup> | I <sub>D</sub>  | PDN = 1, PDL = 1       | _   | 1.0 | 1.5  | mA   |

### Notes:

- V<sub>IH</sub>/V<sub>IL</sub> do not apply to C1A/C2A.

All inputs at 0.4 or V<sub>D</sub> 0.4 (CMOS levels). All inputs are held static except clock and all outputs unloaded (Static I<sub>OUT</sub> = 0 mA).

- **3.** RGDT is not functional in this state.

### **Table 4. AC Characteristics**

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 ^{\circ}\text{C} \text{ for } F/\text{K-Grade}, Fs = 8000 \text{ Hz}, \text{ see "2.Typical Application Schematic" on page 17)}$

| Parameter                                            | Symbol            | Test Condition                                                  | Min | Тур        | Max  | Unit       |

|------------------------------------------------------|-------------------|-----------------------------------------------------------------|-----|------------|------|------------|

| Sample Rate                                          | Fs                |                                                                 | 8   | _          | 16   | kHz        |

| PCLK Input Frequency                                 | PCLK              |                                                                 | 256 | _          | 8192 | kHz        |

| Receive Frequency Response                           |                   | Low –3 dBFS Corner, FILT = 0                                    | _   | 5          | _    | Hz         |

| Receive Frequency Response                           |                   | Low –3 dBFS Corner, FILT = 1                                    | _   | 200        | _    | Hz         |

|                                                      | V <sub>FS</sub>   | FULL = 0 (0 dBm)                                                | _   | 1.1        | _    | $V_{PEAK}$ |

| Transmit Full-Scale Level <sup>1</sup>               |                   | $FULL = 1 (+3.2 \text{ dBm})^2$                                 | _   | 1.58       | _    | $V_{PEAK}$ |

|                                                      |                   | $FULL2 = 1 (+6.0 \text{ dBm})^2$                                | _   | 2.16       | _    | $V_{PEAK}$ |

|                                                      | V <sub>FS</sub>   | FULL = 0 (0 dBm)                                                | _   | 1.1        | _    | $V_{PEAK}$ |

| Receive Full-Scale Level <sup>1,3</sup>              |                   | $FULL = 1 (+3.2 \text{ dBm})^2$                                 | _   | 1.58       | _    | $V_{PEAK}$ |

|                                                      |                   | $FULL2 = 1 (+6.0 \text{ dBm})^2$                                | _   | 2.16       | _    | $V_{PEAK}$ |

| Dynamic Range <sup>4,5,6</sup>                       | DR                | ILIM = 0, DCV = 11, MINI=00<br>DCR = 0, I <sub>L</sub> = 100 mA | _   | 80         | _    | dB         |

| Dynamic Range <sup>4,5,6</sup>                       | DR                | ILIM = 0, DCV = 00, MINI=11<br>DCR = 0, I <sub>L</sub> = 20 mA  | _   | 80         | _    | dB         |

| Dynamic Range <sup>4,5,6</sup>                       | DR                | ILIM = 1, DCV = 11, MINI=00<br>DCR = 0, I <sub>L</sub> = 50 mA  | _   | 80         | _    | dB         |

| Transmit Total Harmonic<br>Distortion <sup>6,7</sup> | THD               | ILIM = 0, DCV = 11, MINI=00<br>DCR = 0, I <sub>L</sub> = 100 mA | _   | -72        | _    | dB         |

| Transmit Total Harmonic<br>Distortion <sup>6,7</sup> | THD               | ILIM = 0, DCV = 00, MINI=11<br>DCR = 0, I <sub>L</sub> = 20 mA  | _   | <b>–78</b> | _    | dB         |

| Receive Total Harmonic<br>Distortion <sup>6,7</sup>  | THD               | ILIM = 0, DCV = 00, MINI=11<br>DCR = 0, I <sub>L</sub> = 20 mA  | _   | <b>–78</b> | _    | dB         |

| Receive Total Harmonic<br>Distortion <sup>6,7</sup>  | THD               | ILIM = 1,DCV = 11, MINI=00<br>DCR = 0, I <sub>L</sub> = 50 mA   | _   | <b>–78</b> | _    | dB         |

| Dynamic Range (Caller ID mode) <sup>8</sup>          | DR <sub>CID</sub> | VIN = 1 kHz, -13 dBFS                                           | _   | 62         | _    | dB         |

| Notes:                                               |                   |                                                                 |     |            | 1    |            |

### **Notes**

- 1. Measured at TIP and RING with 600  $\Omega$  termination at 1 kHz, as shown in Figure 1 on page 6.

- 2. With FULL = 1, the transmit and receive full-scale level of +3.2 dBm can be achieved with a 600  $\Omega$  ac termination. While the transmit and receive level in dBm varies with reference impedance, the DAA will transmit and receive 1 dBV into all reference impedances. With FULL2 = 1, the transmit and receive full-scale level of +6.0 dBm can be achieved with a 600  $\Omega$  termination. In this mode, the DAA will transmit and receive +1.5 dBV into all reference impedances.

- 3. Receive full-scale level produces –0.9 dBFS at DTX.

- 4. DR = 20 x log (RMS V<sub>FS</sub>/RMS Vin) + 20 x log (RMS V<sub>in</sub>/RMS noise). The RMS noise measurement excludes harmonics. Here, V<sub>FS</sub> is the 0 dBm full-scale level per Note 1 above.

- 5. Measurement is 300 to 3400 Hz. Applies to both transmit and receive paths.

- **6.** Vin = 1 kHz, -3 dBFS.

- 7. THD =  $20 \times \log (RMS \text{ distortion/RMS signal})$ .

- 8.  $DR_{CID} = 20 \times log (RMS V_{CID}/RMS V_{IN}) + 20 \times log (RMS V_{IN}/RMS noise)$ .  $V_{CID}$  is the 1.5 V full-scale level with the enhanced caller ID circuit. With the typical CID circuit, the  $V_{CID}$  full-scale level is 6 V peak, and the  $DR_{CID}$  decreases to 50 dB.

- 9. Refer to Tables 10-11 for relative gain accuracy characteristics (passband ripple).

### Table 4. AC Characteristics (Continued)

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 ^{\circ}\text{C} \text{ for F/K-Grade, Fs} = 8000 \text{ Hz}, \text{ see "2.Typical Application Schematic" on page 17)}$

| Parameter                               | Symbol           | Test Condition                                      | Min  | Тур | Max | Unit              |

|-----------------------------------------|------------------|-----------------------------------------------------|------|-----|-----|-------------------|

| Caller ID Full-Scale Level <sup>8</sup> | V <sub>CID</sub> |                                                     | _    | 1.5 | _   | V <sub>PEAK</sub> |

| Gain Accuracy <sup>6,9</sup>            |                  | 2-W to DTX,<br>TXG2, RXG2, TXG3,<br>and RXG3 = 0000 | -0.5 | 0   | 0.5 | dB                |

| Transhybrid Balance                     |                  | 300–3.4 kHz, all ac<br>terminations                 | 20   | _   | _   | dB                |

| Transhybrid Balance                     |                  | 1 kHz, all ac<br>terminations                       | _    | 30  | _   | dB                |

| Two-Wire Return Loss                    |                  | 300–3.4 kHz, all ac<br>terminations                 | 25   | _   | _   | dB                |

| Two-Wire Return Loss                    |                  | 1 kHz, all ac terminations                          | _    | 32  | _   | dB                |

### **Notes**

- 1. Measured at TIP and RING with 600  $\Omega$  termination at 1 kHz, as shown in Figure 1 on page 6.

- 2. With FULL = 1, the transmit and receive full-scale level of +3.2 dBm can be achieved with a 600  $\Omega$  ac termination. While the transmit and receive level in dBm varies with reference impedance, the DAA will transmit and receive 1 dBV into all reference impedances. With FULL2 = 1, the transmit and receive full-scale level of +6.0 dBm can be achieved with a 600  $\Omega$  termination. In this mode, the DAA will transmit and receive +1.5 dBV into all reference impedances.

- 3. Receive full-scale level produces –0.9 dBFS at DTX.

- 4. DR = 20 x log (RMS V<sub>FS</sub>/RMS Vin) + 20 x log (RMS V<sub>in</sub>/RMS noise). The RMS noise measurement excludes harmonics. Here, V<sub>FS</sub> is the 0 dBm full-scale level per Note 1 above.

- 5. Measurement is 300 to 3400 Hz. Applies to both transmit and receive paths.

- 6. Vin = 1 kHz. -3 dBFS.

- 7. THD =  $20 \times \log (RMS \text{ distortion/RMS signal})$ .

- 8. DR<sub>CID</sub> = 20 x log (RMS V<sub>CID</sub>/RMS V<sub>IN</sub>) + 20 x log (RMS V<sub>IN</sub>/RMS noise). V<sub>CID</sub> is the 1.5 V full-scale level with the enhanced caller ID circuit. With the typical CID circuit, the V<sub>CID</sub> full-scale level is 6 V peak, and the DR<sub>CID</sub> decreases to 50 dB

- 9. Refer to Tables 10–11 for relative gain accuracy characteristics (passband ripple).

### **Table 5. Absolute Maximum Ratings**

| Parameter                                | Symbol           | Value                          | Unit |

|------------------------------------------|------------------|--------------------------------|------|

| DC Supply Voltage                        | V <sub>D</sub>   | -0.5 to 3.6                    | V    |

| Input Current, Si3050 Digital Input Pins | I <sub>IN</sub>  | ±10                            | mA   |

| Digital Input Voltage                    | V <sub>IND</sub> | -0.3 to (V <sub>D</sub> + 0.3) | V    |

| Ambient Operating Temperature Range      | T <sub>A</sub>   | -40 to 100                     | °C   |

| Storage Temperature Range                | T <sub>STG</sub> | -65 to 150                     | °C   |

**Note:** Permanent device damage can occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods might affect device reliability.

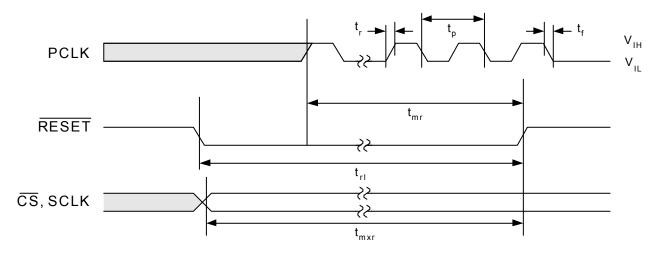

### Table 6. Switching Characteristics—General Inputs

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C for K-Grade}, C_L = 20 \text{ pF})$

| Parameter <sup>1</sup>         | Symbol              | Min     | Тур | Max     | Unit   |

|--------------------------------|---------------------|---------|-----|---------|--------|

| Cycle Time, PCLK               | t <sub>p</sub>      | 0.12207 | _   | 3.90625 | μS     |

| PCLK Duty Cycle                | t <sub>dty</sub>    | 40      | 50  | 60      | %      |

| PCLK Jitter Tolerance          | t <sub>jitter</sub> | _       | _   | 2       | ns     |

| Rise Time, PCLK                | t <sub>r</sub>      | _       | _   | 25      | ns     |

| Fall Time, PCLK                | t <sub>f</sub>      | _       | _   | 25      | ns     |

| PCLK Before RESET ↑2           | t <sub>mr</sub>     | 10      | _   | _       | cycles |

| RESET Pulse Width <sup>3</sup> | t <sub>rl</sub>     | 250     | _   | _       | ns     |

| CS, SCLK Before RESET↑         | t <sub>mxr</sub>    | 20      | _   | _       | ns     |

| Rise Time, Reset               | t <sub>r</sub>      | _       | _   | 25      | ns     |

### Notes:

- 1. All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ . Rise and Fall times are referenced to the 20% and 80% levels of the waveform. **2.** FSYNC/PCLK relationship must be fixed after RESET<sup>1</sup>.

- 3. The minimum RESET pulse width is the greater of 250 ns or 10 PCLK cycle times.

Figure 2. General Inputs Timing Diagram

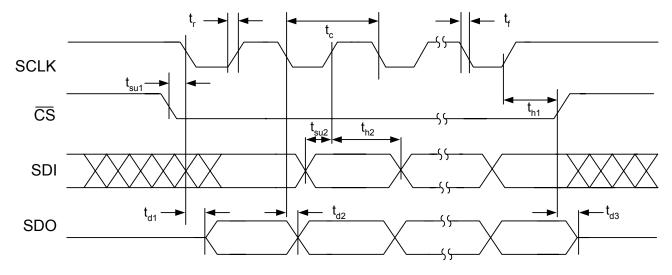

Table 7. Switching Characteristics—Serial Peripheral Interface

$(V_{IO} = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \,^{\circ}\text{C} \text{ for K-Grade, } C_L = 20 \text{ pF})$

| Parameter*                                 | Symbol           | Test<br>Conditions | Min   | Тур | Max | Unit |

|--------------------------------------------|------------------|--------------------|-------|-----|-----|------|

| Cycle Time SCLK                            | t <sub>c</sub>   |                    | 61.03 | _   | _   | ns   |

| Rise Time, SCLK                            | t <sub>r</sub>   |                    | _     | _   | 25  | ns   |

| Fall Time, SCLK                            | t <sub>f</sub>   |                    | _     | _   | 25  | ns   |

| Delay Time, SCLK Fall to SDO Active        | t <sub>d1</sub>  |                    | _     | _   | 20  | ns   |

| Delay Time, SCLK Fall to SDO<br>Transition | t <sub>d2</sub>  |                    | _     | _   | 20  | ns   |

| Delay Time, CS Rise to SDO Tri-state       | t <sub>d3</sub>  |                    | _     | _   | 20  | ns   |

| Setup Time, CS to SCLK Fall                | t <sub>su1</sub> |                    | 25    | _   | _   | ns   |

| Hold Time, SCLK to CS Rise                 | t <sub>h1</sub>  |                    | 20    | _   | _   | ns   |

| Setup Time, SDI to SCLK Rise               | t <sub>su2</sub> |                    | 25    | _   | _   | ns   |

| Hold Time, SCLK Rise to SDI Transition     | t <sub>h2</sub>  |                    | 20    | _   | _   | ns   |

| Propagation Delay, SDI to SDITHRU          |                  |                    | _     | 6   | _   | ns   |

\*Note: All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ . Rise and Fall times are referenced to the 20% and 80% levels of the waveform.

Figure 3. SPI Timing Diagram

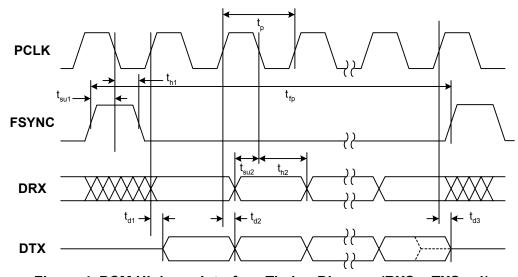

Table 8. Switching Characteristics—PCM Highway Serial Interface

( $V_D$  = 3.0 to 3.6 V,  $T_A$  = 0 to 70 °C for K-Grade,  $C_L$  = 20 pF)

| Symbol              | Test<br>Conditions                                                                                      | Min                                                                                                                                                                                                                 | Тур            | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Units                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| t <sub>p</sub>      |                                                                                                         | 122                                                                                                                                                                                                                 | _              | 3906                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ns                                                    |

|                     |                                                                                                         | _                                                                                                                                                                                                                   | 256            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   | 512            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   | 768            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   | 1.024          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   |                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   |                | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz                                                   |

|                     |                                                                                                         | _                                                                                                                                                                                                                   | 8.192          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz                                                   |

| t <sub>fp</sub>     |                                                                                                         |                                                                                                                                                                                                                     | 125            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μS                                                    |

| t <sub>dty</sub>    |                                                                                                         | 40                                                                                                                                                                                                                  | 50             | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | %                                                     |

| t <sub>jitter</sub> |                                                                                                         | _                                                                                                                                                                                                                   | _              | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                                                    |

| t <sub>jitter</sub> |                                                                                                         |                                                                                                                                                                                                                     |                | ±120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ns                                                    |

| t <sub>r</sub>      |                                                                                                         |                                                                                                                                                                                                                     |                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                    |

| t <sub>f</sub>      |                                                                                                         |                                                                                                                                                                                                                     |                | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                    |

| t <sub>d1</sub>     |                                                                                                         | _                                                                                                                                                                                                                   | _              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                    |

| t <sub>d2</sub>     |                                                                                                         |                                                                                                                                                                                                                     |                | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                    |

| t <sub>d3</sub>     |                                                                                                         | _                                                                                                                                                                                                                   | _              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ns                                                    |

| t <sub>su1</sub>    |                                                                                                         | 25                                                                                                                                                                                                                  | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                                                    |

| t <sub>h1</sub>     |                                                                                                         | 20                                                                                                                                                                                                                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                                                    |

| t <sub>su2</sub>    |                                                                                                         | 25                                                                                                                                                                                                                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ns                                                    |

| t <sub>h2</sub>     |                                                                                                         | 20                                                                                                                                                                                                                  | _              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ns                                                    |

|                     | $t_{p}$ $t_{fp}$ $t_{dty}$ $t_{jitter}$ $t_{r}$ $t_{d1}$ $t_{d2}$ $t_{d3}$ $t_{su1}$ $t_{h1}$ $t_{su2}$ | t <sub>p</sub> t <sub>fp</sub> t <sub>fp</sub> t <sub>dty</sub> t <sub>jitter</sub> t <sub>r</sub> t <sub>f</sub> t <sub>d1</sub> t <sub>d2</sub> t <sub>d3</sub> t <sub>su1</sub> t <sub>h1</sub> t <sub>su2</sub> | tp         122 | tp         122         —           256         —         512           —         768           —         1.024           —         1.536           —         2.048           —         4.096           —         8.192           tfp         —         125           tdty         40         50           tjitter         —         —           tr         —         —           tf         —         —           td1         —         —           td2         —         —           td3         —         —           tsu1         25         —           tsu2         25         — | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

### Notes:

- 1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_O 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ , rise and fall times are referenced to the 20% and 80% levels of the waveform.

- 2. FSYNC must be 8 kHz under all operating conditions.

- 3. Specification applies to PCLK fall to DTX tri-state when that mode is selected.

Figure 4. PCM Highway Interface Timing Diagram (RXS = TXS = 1)

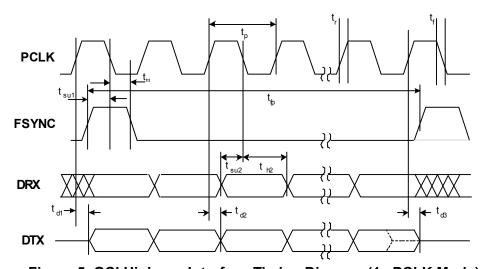

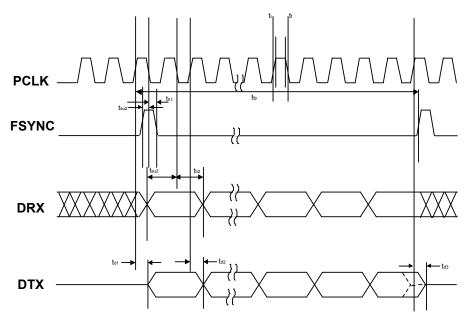

Table 9. Switching Characteristics—GCI Highway Serial Interface

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \,^{\circ}\text{C} \text{ for K-Grade, } C_L = 20 \text{ pF})$

| Parameter <sup>1</sup>                              | Symbol              | Test<br>Conditions | Min | Тур            | Max  | Units      |

|-----------------------------------------------------|---------------------|--------------------|-----|----------------|------|------------|

| Cycle Time PCLK (Single Clocking Mode)              | t <sub>p</sub>      |                    | _   | 488            | _    | ns         |

| Cycle Time PCLK (Double Clocking Mode)              | t <sub>p</sub>      |                    | _   | 244            | _    | ns         |

| Valid PCLK Inputs                                   |                     |                    | _   | 2.048<br>4.096 | _    | MHz<br>MHz |

| FSYNC Period <sup>2</sup>                           | t <sub>fp</sub>     |                    | _   | 125            | _    | μs         |

| PCLK Duty Cycle                                     | t <sub>dty</sub>    |                    | 40  | 50             | 60   | %          |

| PCLK Jitter Tolerance                               | t <sub>jitter</sub> |                    | _   | _              | 2    | ns         |

| FSYNC Jitter Tolerance                              | t <sub>jitter</sub> |                    | _   | _              | ±120 | ns         |

| Rise Time, PCLK                                     | t <sub>r</sub>      |                    | _   | _              | 25   | ns         |

| Fall Time, PCLK                                     | t <sub>f</sub>      |                    | _   | _              | 25   | ns         |

| Delay Time, PCLK Rise to DTX Active                 | t <sub>d1</sub>     |                    | _   | _              | 20   | ns         |

| Delay Time, PCLK Rise to DTX Transition             | t <sub>d2</sub>     |                    | _   | _              | 20   | ns         |

| Delay Time, PCLK Rise to DTX Tri-State <sup>3</sup> | t <sub>d3</sub>     |                    | _   | _              | 20   | ns         |

| Setup Time, FSYNC Rise to PCLK Fall                 | t <sub>su1</sub>    |                    | 25  |                | _    | ns         |

| Hold Time, PCLK Fall to FSYNC Fall                  | t <sub>h1</sub>     |                    | 20  | _              | _    | ns         |

| Setup Time, DRX Transition to PCLK Fall             | t <sub>su2</sub>    |                    | 25  | _              | _    | ns         |

| Hold Time, PCLK Falling to DRX Transition           | t <sub>h2</sub>     |                    | 20  |                | _    | ns         |

### Notes:

- 1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_O 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ , rise and fall times are referenced to the 20% and 80% levels of the waveform.

- 2. FSYNC must be 8 kHz under all operating conditions.

- 3. Specification applies to PCLK fall to DTX tri-state when that mode is selected.

Figure 5. GCI Highway Interface Timing Diagram (1x PCLK Mode)

Figure 6. GCI Highway Interface Timing Diagram (2x PCLK Mode)

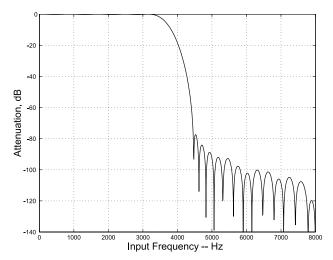

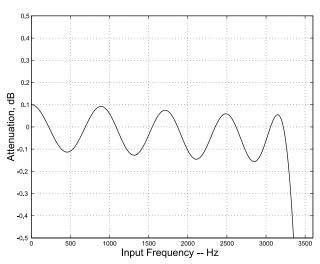

Table 10. Digital FIR Filter Characteristics—Transmit and Receive

( $V_D$  = 3.0 to 3.6 V, Sample Rate = 8 kHz,  $T_A$  = 0 to 70 °C for K-Grade)

| Parameter                                      | Symbol                | Min             | Тур              | Max | Unit |

|------------------------------------------------|-----------------------|-----------------|------------------|-----|------|

| Passband (0.1 dB)                              | F <sub>(0.1 dB)</sub> | 0               | _                | 3.3 | kHz  |

| Passband (3 dB)                                | F <sub>(3 dB)</sub>   | 0               | _                | 3.6 | kHz  |

| Passband Ripple Peak-to-Peak                   |                       | -0.1            | _                | 0.1 | dB   |

| Stopband                                       |                       | _               | 4.4              | _   | kHz  |

| Stopband Attenuation                           |                       | -74             | _                | _   | dB   |

| Group Delay                                    | t <sub>gd</sub>       | _               | 12/Fs            | _   | S    |

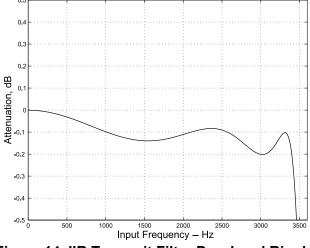

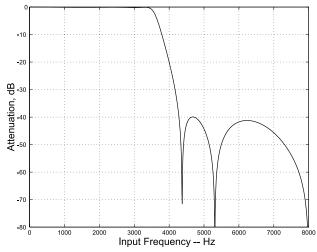

| Note: Typical FIR filter characteristics for F | s = 8000 Hz are s     | hown in Figures | 7, 8, 9, and 10. | 1   | 1    |

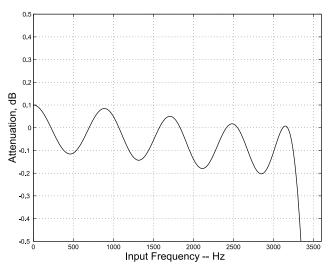

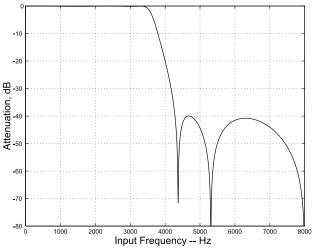

### Table 11. Digital IIR Filter Characteristics—Transmit and Receive

(V<sub>D</sub> = 3.0 to 3.6 V, Sample Rate = 8 kHz,  $T_A$  = 0 to 70 °C for K-Grade)

| Parameter                    | Symbol              | Min  | Тур    | Max | Unit |

|------------------------------|---------------------|------|--------|-----|------|

| Passband (3 dB)              | F <sub>(3 dB)</sub> | 0    | _      | 3.6 | kHz  |

| Passband Ripple Peak-to-Peak |                     | -0.2 | _      | 0.2 | dB   |

| Stopband                     |                     | _    | 4.4    | _   | kHz  |

| Stopband Attenuation         |                     | -40  | _      | _   | dB   |

| Group Delay                  | t <sub>gd</sub>     | _    | 1.6/Fs | _   | S    |

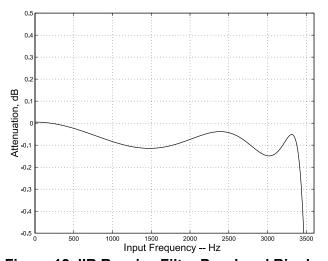

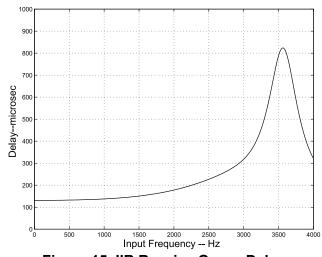

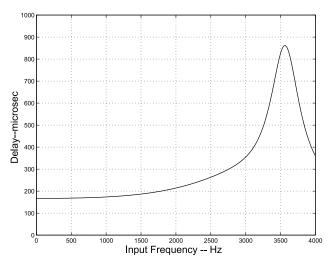

**Note:** Typical IIR filter characteristics for Fs = 8000 Hz are shown in Figures 11, 12, 13, and 14. Figures 15 and 16 show group delay versus input frequency.

-20 -40 -40 -40 -100 -100 -120 -140 0 1000 2000 3000 4000 5000 6000 7000 800 Input Frequency -- Hz

Figure 7. FIR Receive Filter Response

Figure 9. FIR Transmit Filter Response

Figure 8. FIR Receive Filter Passband Ripple

Figure 10. FIR Transmit Filter Passband Ripple

For Figures 7–10, all filter plots apply to a sample rate of Fs = 8 kHz.

For Figures 11–14, all filter plots apply to a sample rate of Fs = 8 kHz.

Figure 11. IIR Receive Filter Response

Figure 14. IIR Transmit Filter Passband Ripple

Figure 12. IIR Receive Filter Passband Ripple

Figure 15. IIR Receive Group Delay

Figure 13. IIR Transmit Filter Response

Figure 16. IIR Transmit Group Delay

# 2. Typical Application Schematic

Figure 17. Typical Application Circuit for the Si3050 and Si3018/19 (Refer to "AN67: Si3050/52/54/56 Layout Guidelines" for Recommended Layout Guidelines)

### 3. Bill of Materials

| Component               | Value                                    | Supplier(s)                        |  |  |

|-------------------------|------------------------------------------|------------------------------------|--|--|

| C1, C2                  | 33 pF, Y2, X7R, ±20%                     | Panasonic, Murata, Vishay          |  |  |

| C3 <sup>1</sup>         | 3.9 nF, 250 V, X7R, ±20%                 | Venkel, SMEC                       |  |  |

| C4                      | 1.0 μF, 50 V, Elec/Tant, ±20%            | Panasonic                          |  |  |

| C5, C6, C50, C51        | 0.1 μF, 16 V, X7R, ±20%                  | Venkel, SMEC                       |  |  |

| C7                      | 2.7 nF, 50 V, X7R, ±20%                  | Venkel, SMEC                       |  |  |

| C8, C9                  | 680 pF, Y2, X7R, ±10%                    | Panasonic, Murata, Vishay          |  |  |

| C10                     | 0.01 μF, 16 V, X7R, ±20%                 | Venkel, SMEC                       |  |  |

| C30, C31 <sup>2</sup>   | 120 pF, 250 V, X7R, ±10%                 | Venkel, SMEC                       |  |  |

| D1, D2 <sup>3</sup>     | Dual Diode, 225 mA, 300 V, (CMPD2004S)   | Central Semiconductor              |  |  |

| FB1, FB2                | Ferrite Bead, BLM18AG601SN1              | Murata                             |  |  |

| Q1, Q3                  | NPN, 300 V, MMBTA42                      | Central OnSemi, Fairchild          |  |  |

| Q2                      | PNP, 300 V, MMBTA92                      | Central OnSemi, Fairchild          |  |  |

| Q4, Q5                  | NPN, 80 V, 330 mW, MMBTA06               | Central OnSemi, Fairchild          |  |  |

| RV1                     | Sidactor, 275 V, 100 A                   | Teccor, Diodes Inc., Shindengen    |  |  |

| R1                      | 1.07 kΩ, 1/2 W, 1%                       | Venkel, SMEC, Panasonic            |  |  |

| R2                      | 150 Ω, 1/16 W, 5%                        | Venkel, SMEC, Panasonic            |  |  |

| R3                      | 3.65 kΩ, 1/2 W, 1%                       | Venkel, SMEC, Panasonic            |  |  |

| R4                      | 2.49 kΩ, 1/2 W, 1%                       | Venkel, SMEC, Panasonic            |  |  |

| R5, R6                  | 100 kΩ, 1/16 W, 5%                       | Venkel, SMEC, Panasonic            |  |  |

| R7, R8 <sup>2</sup>     | Not Installed, 20 M $\Omega$ , 1/8 W, 5% | Venkel, SMEC, Panasonic            |  |  |

| R9                      | 1 MΩ, 1/16 W, 1%                         | Venkel, SMEC, Panasonic            |  |  |

| R10                     | 536 Ω, 1/4 W, 1%                         | Venkel, SMEC, Panasonic            |  |  |

| R11                     | 73.2 Ω, 1/2 W, 1%                        | Venkel, SMEC, Panasonic            |  |  |

| R12, R13 <sup>4</sup>   | 0 Ω, 1/16 W                              | Venkel, SMEC, Panasonic            |  |  |

| R15, R16 <sup>5</sup>   | 0 Ω, 1/16 W                              | Venkel, SMEC, Panasonic            |  |  |

| R30, R32 <sup>2</sup>   | 15 MΩ, 1/8 W, 5%                         | Venkel, SMEC, Panasonic            |  |  |

| R31, R33 <sup>2</sup>   | 5.1 MΩ, 1/8 W, 5%                        | Venkel, SMEC, Panasonic            |  |  |

| R51, R52, R53, R54, R55 | 4.7 kΩ, 1/16 W, 5%                       | Venkel, SMEC, Panasonic            |  |  |

| U1                      | Si3050                                   | Silicon Labs                       |  |  |

| U2                      | Si3018/19                                | Silicon Labs                       |  |  |

| Z1                      | Zener Diode, 43 V, 1/2 W                 | General Semi, On Semi, Diodes Inc. |  |  |

### Notes:

- 1. Value for C3 above is recommended for use with the Si3019 in voice applications to improve return loss performance. When using the Si3018, a value of 10 nF (250 V, 20%) can be substituted.

- 2. R7–R8 may be substituted for R30–R33 and C30–C31 for lower cost, but reduced CID performance.

- **3.** Several diode bridge configurations are acceptable. Parts, such as a single HD04, a DF-04S, or four 1N4004 diodes, may be used (suppliers include General Semiconductor, Diodes Inc., etc.).

- **4.** 56  $\Omega$ , 1/16, 1% resistors may be substituted for R12–R13 (0  $\Omega$ ) to decrease emissions. (See AN81.)

- **5.** Murata BLM18AG601SN1 may be substituted for R15–R16 (0  $\Omega$ ) to decrease emissions. (See AN81.)

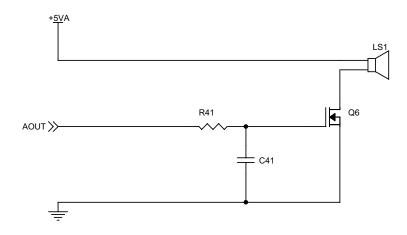

### 4. AOUT PWM Output

Figure 18 illustrates an optional circuit to support the pulse width modulation (PWM) output capability of the Si3050 for call progress monitoring purposes. To enable this mode, the INTE bit (Register 2) should be set to 0, the PWME bit (Register 1) set to 1, and the PWMM bits (Register 2) set to 00.

Figure 18. AOUT PWM Circuit for Call Progress

Table 12. Component Values—AOUT PWM

| Component | Value                   | Supplier                |  |  |

|-----------|-------------------------|-------------------------|--|--|

| LS1       | Speaker BRT1209PF-06    | Intervox                |  |  |

| Q6        | NPN KSP13               | Fairchild               |  |  |

| C41       | 0.1 μF, 16 V, X7R, ±20% | Venkel, SMEC            |  |  |

| R41       | 150 Ω, 1/10 W, ±5%      | Venkel, SMEC, Panasonic |  |  |

Registers 20 and 21 allow the receive and transmit paths to be attenuated linearly. When these registers are set to all 0s, the transmit and receive paths are muted. These registers affect the call progress output only and do not affect transmit and receive operations on the telephone line.

The PWMM[1:0] bits (Register 1, bits 5:4) select one of three different PWM output modes for the AOUT signal, including a delta-sigma data stream, a 32 kHz return to 0 PWM output, and a balanced 32 kHz PWM output.

### 5. Functional Description

The Si3050 is an integrated direct access arrangement (DAA) providing a programmable line interface that meets global telephone line requirements. The Si3050 implements Silicon Laboratories' patented isolation capacitor technology, which offers the highest level of integration by replacing an analog front end (AFE), an isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid with two thin small shrink outline packages (TSSOPs).

The Si3050 DAA is fully software programmable to meet global requirements and is compliant with FCC, TBR21, JATE, and other country-specific PTT specifications as shown in Table 13. In addition, the Si3050 meets the most stringent global requirements for out-of-band energy, emissions, immunity, high-voltage surges, and safety, including FCC Parts 15 and 68, EN55022, EN55024, and many other standards.

### 5.1. Line-Side Device Support

Two different line-side devices can be used with the Si3050 system-side device. Both line-side devices support the following features:

- Global compliance.

- Selectable 5 Hz or 200 Hz RX low-pass filter pole.

- -16.5 to 13.5 dB digital gain/attenuation adjustment in 0.1 dB increments for the transmit and receive paths.

### 5.1.1. Si3018

- Globally-compliant line-side device—targets global DAA requirements for voice/telephony applications.

This line-side device supports both FCC-compliant countries and non-FCC-compliant countries.

- · Selectable dc terminations.

- Four selectable ac terminations to increase return loss and trans-hybrid loss performance.

### 5.1.2. Si3019

- Globally-compliant, enhanced features line-side device—targets global DAA requirements for voice/ telephony applications. The Si3019 contains all the features available on the Si3018, plus the following additional features/enhancements:

- Sixteen selectable ac terminations to further increase return loss and trans-hybrid loss performance.

- Line voltage monitoring in on- and off-hook modes to enable line in-use/parallel handset detection.

- Programmable line current / voltage threshold interrupt.

- Polarity reversal interrupt.

- +3.2 dBm TX/RX level mode (600 Ω)

- Higher resolution (1.1 mA/bit) loop current measurement.

**Table 13. Country Specific Register Settings**

| Register               | 16  | 31   | 16 | 16 | 26   | 26       | 26        | 30        |

|------------------------|-----|------|----|----|------|----------|-----------|-----------|

| Country                | онѕ | OHS2 | RZ | RT | ILIM | DCV[1:0] | MINI[1:0] | ACIM[3:0] |

| Argentina              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Australia <sup>3</sup> | 1   | 0    | 0  | 0  | 0    | 01       | 01        | 0011      |

| Austria                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Bahrain                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Belgium                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Brazil                 | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Bulgaria               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0011      |

| Canada                 | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Chile                  | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| China <sup>4</sup>     | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000/1010 |

| Colombia               | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Croatia                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Cyprus                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Czech Republic         | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Denmark                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Ecuador                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Egypt                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| El Salvador            | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Finland                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| France                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Germany                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Greece                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Guam                   | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Hong Kong              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Hungary                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Iceland                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| India                  | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

### Note:

- **1.** Supported for loop current  $\geq$  20 mA.

- 2. TBR21 includes the following countries: Austria, Belgium, Denmark, Finland, France, Germany, Greece, Iceland, Ireland, Italy, Luxembourg, Netherlands, Norway, Portugal, Spain, Sweden, Switzerland, and the United Kingdom.

- 3. See "5.16.DC Termination" on page 30 for DCV and MINI settings.

- **4.** ACIM is 0000 for data applications and 1010 for voice applications.

**Table 13. Country Specific Register Settings (Continued)**

| Register              | 16  | 31   | 16 | 16 | 26   | 26       | 26        | 30        |

|-----------------------|-----|------|----|----|------|----------|-----------|-----------|

| Country               | OHS | OHS2 | RZ | RT | ILIM | DCV[1:0] | MINI[1:0] | ACIM[3:0] |

| Indonesia             | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Ireland               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Israel                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Italy                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Japan                 | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| Jordan                | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| Kazakhstan            | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Kuwait                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Latvia                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Lebanon               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Luxembourg            | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Macao                 | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Malaysia <sup>1</sup> | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| Malta                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Mexico                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Morocco               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Netherlands           | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| New Zealand           | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0100      |

| Nigeria               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Norway                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Oman                  | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| Pakistan              | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| Peru                  | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Philippines           | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| Poland                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Portugal              | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Romania               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Russia                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

### Note:

- **1.** Supported for loop current  $\geq$  20 mA.

- 2. TBR21 includes the following countries: Austria, Belgium, Denmark, Finland, France, Germany, Greece, Iceland, Ireland, Italy, Luxembourg, Netherlands, Norway, Portugal, Spain, Sweden, Switzerland, and the United Kingdom.

- 3. See "5.16.DC Termination" on page 30 for DCV and MINI settings.

- **4.** ACIM is 0000 for data applications and 1010 for voice applications.

**Table 13. Country Specific Register Settings (Continued)**

| Register           | 16  | 31   | 16 | 16 | 26   | 26       | 26        | 30        |

|--------------------|-----|------|----|----|------|----------|-----------|-----------|

| Country            | онѕ | OHS2 | RZ | RT | ILIM | DCV[1:0] | MINI[1:0] | ACIM[3:0] |

| Saudi Arabia       | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Singapore          | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Slovakia           | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Slovenia           | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| South Africa       | 0   | 0    | 1  | 0  | 0    | 11       | 00        | 0011      |

| South Korea        | 0   | 0    | 1  | 0  | 0    | 11       | 00        | 0000      |

| Spain              | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Sweden             | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Switzerland        | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Taiwan             | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| TBR21 <sup>2</sup> | 0   | 0    | 0  | 0  | 1    | 11       | 00        | 0010      |

| Thailand           | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000      |

| UAE                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| United Kingdom     | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0101      |

| USA                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

| Yemen              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000      |

### Note:

- **1.** Supported for loop current  $\geq$  20 mA.

- **2.** TBR21 includes the following countries: Austria, Belgium, Denmark, Finland, France, Germany, Greece, Iceland, Ireland, Italy, Luxembourg, Netherlands, Norway, Portugal, Spain, Sweden, Switzerland, and the United Kingdom.

- 3. See "5.16.DC Termination" on page 30 for DCV and MINI settings.

- 4. ACIM is 0000 for data applications and 1010 for voice applications.

### 5.2. Power Supplies

The Si3050 operates from a 3.0–3.6 V power supply. The Si3050 input pins can only accept 3.3 V CMOS signal levels. If support of 5 V signal levels is necessary, a level shifter is required. The Si3018/19 derives its power from two sources: the Si3050 and the telephone line. The Si3050 supplies power over the patented isolation capacitor link between the two devices, allowing the Si3019 to communicate with the Si3050 while on-hook and perform other on-hook functions, such as line voltage monitoring. When off-hook, the Si3018/19 also derives power from the line current supplied from the telephone line. This feature is exclusive to DAAs from Silicon Labs and allows the most cost-effective implementation for a DAA while still maintaining robust performance over all line conditions.

### 5.3. Initialization

Each time the  $\underline{\text{Si3050}}$  is powered up, assert the RESET pin. When the  $\overline{\text{RESET}}$  pin is deasserted, the registers have default values to guarantee the line-side device (Si3018/19) is powered down without the possibility of loading the line (i.e., off-hook). An example initialization procedure follows:

- 1. Supply the appropriate PCLK and FSYNC signals to the Si3050.

- 2. Wait until the PLL is locked. This time is less than 1 ms from the application of PCLK.

- 3. Write an 00H into Register 6 to power up the line-side device (Si3018/19).

- Set the desired line interface parameters (i.e., DCV[1:0], MINI[1:0], ILIM, DCR, ACIM[3:0], OHS, RT, RZ, TGA2, and TXG2[3:0]) shown in Table 13 on page 21.

- 5. For voice applications, set the FULL (or FULL2) + IIRE bits.

When this procedure is complete, the Si3018/19 is ready for ring detection and off-hook operation.

### 5.4. Isolation Barrier