# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Si4030/31/32-B1

# Si4030/31/32 ISM TRANSMITTER

#### Features

- Frequency range

- 240–930 MHz (Si4031/32)

- 900–960 MHz (Si4030)

- Output Power Range

- +1 to +20 dBm (Si4032)

- -8 to +13 dBm (Si4030/31)

- Low Power Consumption

- Si4032 85 mA @ +20 dBm

- Si4030/31

- 30 mA @ +13 dBm

- Data Rate = 0.123 to 256 kbps

- FSK, GFSK, and OOK modulation

- Power Supply = 1.8 to 3.6 V

#### **Applications**

- Remote control

- Home security & alarm

- Telemetry

- Personal data logging

- Toy control

- Wireless PC peripherals

#### Description

- Ultra low power shutdown mode

- Wake-up timer

- Integrated 32 kHz RC or 32 kHz XTAI

- Integrated voltage regulators

- Configurable packet handler

- TX 64 byte FIFO

- Low battery detector

- Temperature sensor and 8-bit ADC

- -40 to +85 °C temperature range

- Integrated voltage regulators

- Frequency hopping capability

- On-chip crystal tuning

- 20-Pin QFN package

- -Low BOM

- Power-on-reset (POR)

- Remote meter reading

- Remote keyless entry

- Industrial control

- Sensor networks

- Health monitors

- Silicon Laboratories' Si4030/31/32 devices are highly integrated, single-chip wireless ISM transmitters. The high-performance EZRadioPRO® family includes a complete line of transmitters, receivers, and transceivers allowing the RF system designer to choose the optimal wireless part for their application.

The Si4030/31/32 offers advanced radio features including continuous frequency coverage from 240-960 MHz with adjustable power output levels of -8 to +13 dBm on the Si4030/31 and +1 to +20 dBm on the Si4032. Power adjustments are made in 3 dB steps. The Si4030/31/32's high level of integration offers reduced BOM cost while simplifying the overall system design. The Si4032's Industry leading +20 dBm output power ensures extended range and improved link performance.

Additional system features such as an automatic wake-up timer, low battery detector, 64 byte TX FIFO, and automatic packet handling reduce overall current consumption and allow the use of lower-cost system MCUs. An integrated temperature sensor, general purpose ADC, power-on-reset (POR), and GPIOs further reduce overall system cost and size.

The direct digital transmit modulation and automatic PA power ramping ensure precise transmit modulation and reduced spectral spreading ensuring compliance with global regulations including FCC, ETSI, and ARIB regulations.

An easy-to-use calculator is provided to quickly configure the radio settings, simplifying customer's system design and reducing time to market.

See page 53.

#### Patents pending

- Home automation

# Si4030/31/32-B1

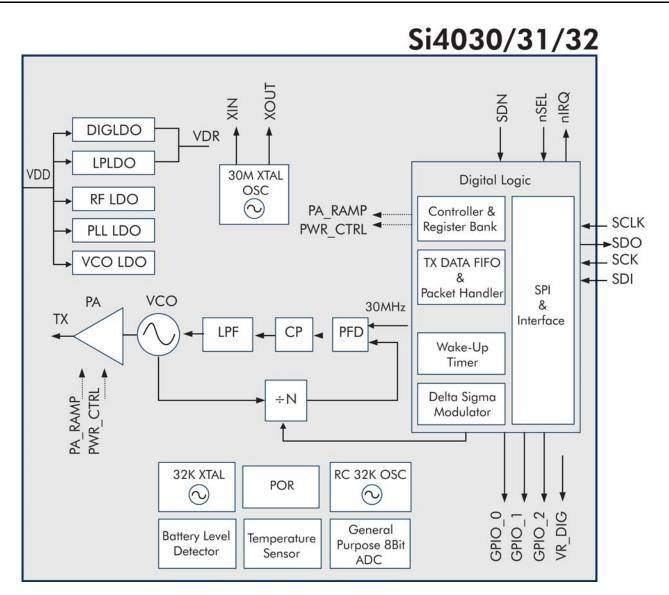

#### **Functional Block Diagram**

# TABLE OF CONTENTS

# Section

## <u>Page</u>

| <b>1. Electrical Specifications</b> 1.1. Definition of Test Conditions |     |

|------------------------------------------------------------------------|-----|

|                                                                        |     |

| 2. Functional Description                                              |     |

| 2.1. Operating Modes                                                   |     |

| 3. Controller Interface                                                |     |

| 3.1. Serial Peripheral Interface (SPI)                                 |     |

| 3.2. Operating Mode Control                                            |     |

| 3.3. Interrupts                                                        |     |

| 3.4. System Timing                                                     |     |

| 3.5. Frequency Control                                                 |     |

| 4. Modulation Options                                                  |     |

| 4.1. Modulation Type                                                   |     |

| 4.2. Modulation Data Source                                            | .28 |

| 5. Internal Functional Blocks                                          |     |

| 5.1. Synthesizer                                                       | .31 |

| 5.2. Power Amplifier                                                   | .31 |

| 5.3. Crystal Oscillator                                                | .33 |

| 5.4. Regulators                                                        | .33 |

| 6. Data Handling and Packet Handler                                    | .34 |

| 6.1. TX FIFO                                                           |     |

| 6.2. Packet Configuration                                              | .35 |

| 6.3. Packet Handler TX Mode                                            |     |

| 6.4. Data Whitening, Manchester Encoding, and CRC                      | .37 |

| 6.5. Synchronization Word Configuration                                |     |

| 6.6. TX Retransmission and Auto TX                                     |     |

| 7. Auxiliary Functions                                                 |     |

| 7.1. Smart Reset                                                       |     |

| 7.2. Microcontroller Clock                                             | .40 |

| 7.3. General Purpose ADC                                               |     |

| 7.4. Temperature Sensor                                                |     |

| 7.5. Low Battery Detector                                              |     |

| 7.6. Wake-Up Timer                                                     |     |

| 7.7. GPIO Configuration                                                |     |

| 8. Reference Design                                                    |     |

| 9. Application Notes and Reference Designs                             |     |

| 10. Customer Support                                                   |     |

| 11. Register Table and Descriptions                                    | .50 |

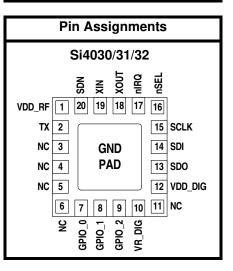

| 12. Pin Descriptions: Si4030/31/32                                     | .51 |

| 13. Ordering Information                                               |     |

| ······································                                 |     |

| 14. Package Markings (Top Marks)   | .53 |

|------------------------------------|-----|

| 14.1. Si4030/31/32 Top Mark        | .53 |

| 14.2. Top Mark Explanation         |     |

| 15. Package Outline: Si4030/31/32  | .54 |

| 16. PCB Land Pattern: Si4030/31/32 | .55 |

| Document Change List               | .57 |

| Contact Information                | .58 |

# LIST OF FIGURES

| Figure 1. SPI Timing                                                 | 15 |

|----------------------------------------------------------------------|----|

| Figure 2. SPI Timing—READ Mode                                       | 16 |

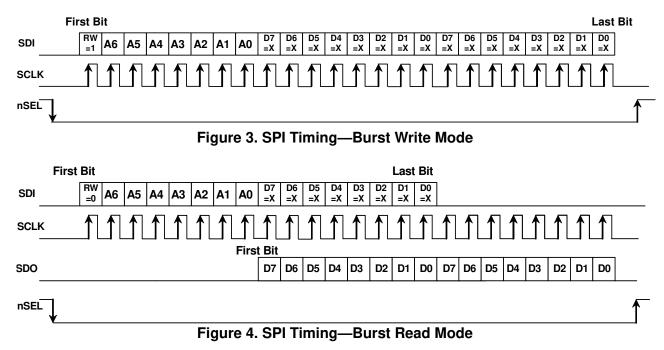

| Figure 3. SPI Timing—Burst Write Mode                                | 16 |

| Figure 4. SPI Timing—Burst Read Mode                                 | 16 |

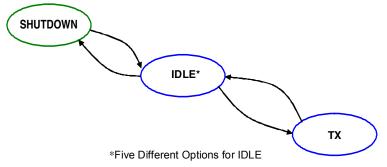

| Figure 5. State Machine Diagram                                      | 17 |

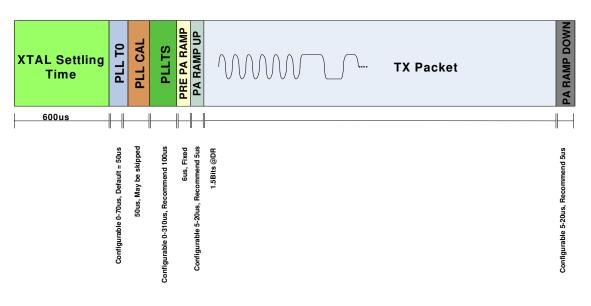

| Figure 6. TX Timing                                                  | 21 |

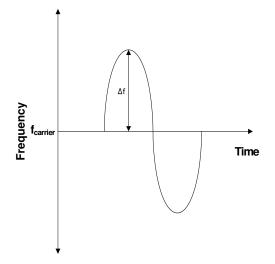

| Figure 7. Frequency Deviation                                        | 25 |

| Figure 8. FSK vs. GFSK Spectrums                                     | 27 |

| Figure 9. Microcontroller Connections                                | 30 |

| Figure 10. PLL Synthesizer Block Diagram                             | 31 |

| Figure 11. FIFO Threshold                                            |    |

| Figure 12. Packet Structure                                          | 35 |

| Figure 13. Multiple Packets in TX Packet Handler                     | 36 |

| Figure 14. Operation of Data Whitening, Manchester Encoding, and CRC | 37 |

| Figure 15. Manchester Coding Example                                 | 37 |

| Figure 16. POR Glitch Parameters                                     | 39 |

| Figure 17. General Purpose ADC Architecture                          | 41 |

| Figure 18. Temperature Ranges using ADC8                             | 43 |

| Figure 19. WUT Interrupt and WUT Operation                           | 46 |

| Figure 20. Si4031 Reference Design Schematic                         | 48 |

| Figure 21. 20-Pin Quad Flat No-Lead (QFN)                            | 54 |

| Figure 22. PCB Land Pattern                                          | 55 |

# LIST OF TABLES

| Table 1. DC Characteristics <sup>1</sup>                            | 7  |

|---------------------------------------------------------------------|----|

| Table 2. Synthesizer AC Electrical Characteristics <sup>1</sup>     | 8  |

| Table 3. Transmitter AC Electrical Characteristics <sup>1</sup>     | 9  |

| Table 4. Auxiliary Block Specifications <sup>1</sup>                | 10 |

| Table 5. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ) | 11 |

| Table 6. GPIO Specifications (GPIO_0, GPIO_1, and GPIO_2)           | 11 |

| Table 7. Absolute Maximum Ratings                                   |    |

| Table 8. Operating Modes                                            | 14 |

| Table 9. Serial Interface Timing Parameters                         | 15 |

| Table 10. Operating Modes Response Time                             | 17 |

| Table 11. Frequency Band Selection                                  | 23 |

| Table 12. Packet Handler Registers                                  | 36 |

| Table 13. POR Parameters                                            | 39 |

| Table 14. Temperature Sensor Range                                  |    |

| Table 15. Register Descriptions                                     | 50 |

| Table 16. Package Dimensions                                        | 54 |

| Table 17. PCB Land Pattern Dimensions                               | 56 |

### 1. Electrical Specifications

#### Table 1. DC Characteristics<sup>1</sup>

| Parameter                     | Symbol                  | Conditions                                                                                                                            | Min | Тур | Max | Units |

|-------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage Range          | V <sub>DD</sub>         |                                                                                                                                       | 1.8 | 3.0 | 3.6 | V     |

| Power Saving Modes            | I <sub>Shutdown</sub>   | RC Oscillator, Main Digital Regulator, and Low Power Digital Regulator OFF <sup>2</sup>                                               | _   | 15  | 50  | nA    |

|                               | I <sub>Standby</sub>    | Low Power Digital Regulator ON (Register values retained)<br>and Main Digital Regulator, and RC Oscillator OFF                        | —   | 450 | 800 | nA    |

|                               | I <sub>Sleep</sub>      | RC Oscillator and Low Power Digital Regulator ON (Register values retained) and Main Digital Regulator OFF                            | _   | 1   | —   | μA    |

|                               | I <sub>Sensor-LBD</sub> | Main Digital Regulator and Low Battery Detector ON,<br>Crystal Oscillator and all other blocks OFF <sup>2</sup>                       | _   | 1   | —   | μA    |

|                               | I <sub>Sensor-TS</sub>  | Main Digital Regulator and Temperature Sensor ON,<br>Crystal Oscillator and all other blocks OFF <sup>2</sup>                         |     | 1   | —   | μA    |

|                               | I <sub>Ready</sub>      | Crystal Oscillator and Main Digital Regulator ON,<br>all other blocks OFF. Crystal Oscillator buffer disabled                         |     | 800 | _   | μA    |

| TUNE Mode Current             | I <sub>Tune</sub>       | Synthesizer and regulators enabled                                                                                                    | _   | 8.5 | _   | mA    |

| TX Mode Current<br>—Si4032    | I <sub>TX_+20</sub>     | txpow[2:0] = 111 (+20 dBm)<br>Using Silicon Labs' Reference Design. TX current<br>consumption is dependent on match and board layout. |     | 85  |     | mA    |

| TX Mode Current<br>—Si4030/31 | I <sub>TX_+13</sub>     | txpow[2:0] = 111 (+13 dBm)<br>Using Silicon Labs' Reference Design. TX current<br>consumption is dependent on match and board layout. |     | 30  |     | mA    |

|                               | I <sub>TX_+1</sub>      | txpow[2:0] = 011 (+1 dBm)<br>Using Silicon Labs' Reference Design. TX current<br>consumption is dependent on match and board layout.  |     | 18  | _   | mA    |

All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

2. Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

## Table 2. Synthesizer AC Electrical Characteristics<sup>1</sup>

| Parameter                                       | Symbol              | Conditions                                                                                                                      | Min | Тур    | Max | Units              |

|-------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|--------------------|

| Synthesizer Frequency<br>Range—Si4031/32        | F <sub>SYN</sub>    |                                                                                                                                 | 240 | —      | 930 | MHz                |

| Synthesizer Frequency<br>Range—Si4030           | F <sub>SYN</sub>    |                                                                                                                                 | 900 | _      | 960 | MHz                |

| Synthesizer Frequency                           | F <sub>RES-LB</sub> | Low Band, 240–480 MHz                                                                                                           | —   | 156.25 | _   | Hz                 |

| Resolution <sup>2</sup>                         | F <sub>RES-HB</sub> | High Band, 480–960 MHz                                                                                                          | _   | 312.5  |     | Hz                 |

| Reference Frequency<br>Input Level <sup>2</sup> | f <sub>REF_LV</sub> | When using external reference signal<br>driving XOUT pin, instead of using<br>crystal. Measured peak-to-peak (V <sub>PP</sub> ) | 0.7 | _      | 1.6 | V                  |

| Synthesizer Settling Time <sup>2</sup>          | t <sub>LOCK</sub>   | Measured from exiting Ready mode with<br>XOSC running to any frequency.<br>Including VCO calibration.                           | _   | 200    | _   | μs                 |

| Residual FM <sup>2</sup>                        | $\Delta F_{RMS}$    | Integrated over ±250 kHz bandwidth (500 Hz lower bound of integration)                                                          | —   | 2      | 4   | kHz <sub>RMS</sub> |

| Phase Noise <sup>2</sup>                        | $L\phi(f_M)$        | ∆F = 10 kHz                                                                                                                     |     | -80    | _   | dBc/Hz             |

|                                                 |                     | ∆F = 100 kHz                                                                                                                    |     | -90    | _   | dBc/Hz             |

|                                                 |                     | $\Delta F = 1 MHz$                                                                                                              |     | -115   |     | dBc/Hz             |

|                                                 |                     | ∆F = 10 MHz                                                                                                                     | —   | -130   | _   | dBc/Hz             |

Notes:

1. All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

2. Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

#### Table 3. Transmitter AC Electrical Characteristics<sup>1</sup>

| Parameter                                                    | Symbol                 | Conditions                                                                                   | Min    | Тур   | Max  | Units |

|--------------------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------|--------|-------|------|-------|

| TX Frequency<br>Range—Si4031/32                              | F <sub>TX</sub>        |                                                                                              | 240    | _     | 930  | MHz   |

| TX Frequency<br>Range—Si4030                                 | F <sub>TX</sub>        |                                                                                              | 900    | _     | 960  | MHz   |

| FSK Data Rate <sup>2</sup>                                   | DR <sub>FSK</sub>      |                                                                                              | 0.123  |       | 256  | kbps  |

| OOK Data Rate <sup>2</sup>                                   | DR <sub>OOK</sub>      |                                                                                              | 0.123  |       | 40   | kbps  |

| Modulation Deviation                                         | Δf1                    | 860–960 MHz                                                                                  | ±0.625 |       | ±320 | kHz   |

|                                                              | Δf2                    | 240–860 MHz                                                                                  | ±0.625 |       | ±160 | kHz   |

| Modulation Deviation<br>Resolution <sup>2</sup>              | Δf <sub>RES</sub>      |                                                                                              | _      | 0.625 |      | kHz   |

| Output Power<br>Range —Si4032 <sup>3</sup>                   | P <sub>TX</sub>        |                                                                                              | +1     |       | +20  | dBm   |

| Output Power<br>Range—Si4030/31 <sup>3</sup>                 | P <sub>TX</sub>        |                                                                                              | -8     | _     | +13  | dBm   |

| TX RF Output Steps <sup>2</sup>                              | $\Delta P_{RF_OUT}$    | controlled by txpow[2:0]                                                                     |        | 3     | _    | dB    |

| TX RF Output Level <sup>2</sup><br>Variation vs. Temperature | $\Delta P_{RF_{TEMP}}$ | –40 to +85 °C                                                                                | _      | 2     | _    | dB    |

| TX RF Output Level<br>Variation vs. Frequency <sup>2</sup>   | $\Delta P_{RF_{FREQ}}$ | Measured across any one<br>frequency band                                                    | —      | 1     | —    | dB    |

| Transmit Modulation<br>Filtering <sup>2</sup>                | B*T                    | Gaussian Filtering Bandwith Time<br>Product                                                  | _      | 0.5   | _    |       |

| Spurious Emissions <sup>2</sup>                              | P <sub>OB-TX1</sub>    | P <sub>OUT</sub> = 13 dBm,<br>Frequencies <1 GHz                                             | —      | _     | -54  | dBm   |

|                                                              | P <sub>OB-TX2</sub>    | 1–12.75 GHz, excluding harmonics                                                             | _      | _     | -54  | dBm   |

| Harmonics <sup>2</sup>                                       | P <sub>2HARM</sub>     | Using reference design TX matching                                                           | _      | _     | -42  | dBm   |

|                                                              | P <sub>3HARM</sub>     | network and filter with max output<br>power. Harmonics reduce linearly with<br>output power. | _      |       | -42  | dBm   |

Notes:

1. All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

2. Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

3. Output power is dependent on matching components and board layout.

### Table 4. Auxiliary Block Specifications<sup>1</sup>

| Parameter                                                            | Symbol               | Conditions                                                                                                         | Min     | Тур  | Max | Units  |

|----------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|---------|------|-----|--------|

| Temperature Sensor<br>Accuracy <sup>2</sup>                          | TS <sub>A</sub>      | After calibrated via sensor offset register tvoffs[7:0]                                                            |         | 0.5  | _   | °C     |

| Temperature Sensor<br>Sensitivity <sup>2</sup>                       | TS <sub>S</sub>      |                                                                                                                    | —       | 5    |     | mV/°C  |

| Low Battery Detector<br>Resolution <sup>2</sup>                      | LBD <sub>RES</sub>   |                                                                                                                    | —       | 50   |     | mV     |

| Low Battery Detector<br>Conversion Time <sup>2</sup>                 | LBD <sub>CT</sub>    |                                                                                                                    | —       | 250  | _   | μs     |

| Microcontroller Clock<br>Output Frequency                            | F <sub>MC</sub>      | Configurable to 30 MHz,<br>15 MHz, 10 MHz, 4 MHz,<br>3 MHz, 2 MHz, 1 MHz, or<br>32.768 kHz                         | 32.768K |      | 30M | Hz     |

| General Purpose ADC<br>Resolution <sup>2</sup>                       | ADC <sub>ENB</sub>   |                                                                                                                    | —       | 8    | _   | bit    |

| General Purpose ADC Bit<br>Resolution <sup>2</sup>                   | ADC <sub>RES</sub>   |                                                                                                                    | _       | 4    |     | mV/bit |

| Temp Sensor & General<br>Purpose ADC Conversion<br>Time <sup>2</sup> | ADC <sub>CT</sub>    |                                                                                                                    | _       | 305  |     | μs     |

| 30 MHz XTAL Start-Up time                                            | t <sub>30M</sub>     | Using XTAL and board layout in<br>reference design. Start-up time<br>will vary with XTAL type and<br>board layout. | _       | 600  |     | μs     |

| 30 MHz XTAL Cap<br>Resolution <sup>2</sup>                           | 30M <sub>RES</sub>   |                                                                                                                    |         | 97   | _   | fF     |

| 32 kHz XTAL Start-Up Time <sup>2</sup>                               | t <sub>32k</sub>     |                                                                                                                    | _       | 6    |     | sec    |

| 32 kHz XTAL Accuracy<br>using 32 kHz XTAL <sup>2</sup>               | 32K <sub>RES</sub>   | Using 20 ppm 32 kHz Crystal                                                                                        | _       | 100  |     | ppm    |

| 32 kHz Accuracy using<br>Internal RC Oscillator <sup>2</sup>         | 32KRC <sub>RES</sub> |                                                                                                                    |         | 2500 | _   | ppm    |

| POR Reset Time                                                       | t <sub>POR</sub>     |                                                                                                                    |         | 16   |     | ms     |

| Software Reset Time <sup>2</sup>                                     | t <sub>soft</sub>    |                                                                                                                    |         | 100  |     | μs     |

Notes:

1. All specification guaranteed by production test unless otherwise noted. Production test conditions and max limits are listed in the "Production Test Conditions" section on page 13.

2. Guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13.

| Parameter                                                                                                                                              | Symbol            | Conditions                                                             | Min                   | Тур | Max | Units |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------|-----------------------|-----|-----|-------|--|--|

| Rise Time                                                                                                                                              | T <sub>RISE</sub> | 0.1 x V <sub>DD</sub> to 0.9 x V <sub>DD</sub> , C <sub>L</sub> = 5 pF | —                     | —   | 8   | ns    |  |  |

| Fall Time                                                                                                                                              | T <sub>FALL</sub> | 0.9 x V <sub>DD</sub> to 0.1 x V <sub>DD</sub> , C <sub>L</sub> = 5 pF |                       | —   | 8   | ns    |  |  |

| Input Capacitance                                                                                                                                      | C <sub>IN</sub>   |                                                                        | —                     | _   | 1   | pF    |  |  |

| Logic High Level Input Voltage                                                                                                                         | V <sub>IH</sub>   |                                                                        | V <sub>DD</sub> – 0.6 | _   |     | V     |  |  |

| Logic Low Level Input Voltage                                                                                                                          | V <sub>IL</sub>   |                                                                        |                       | _   | 0.6 | V     |  |  |

| Input Current                                                                                                                                          | I <sub>IN</sub>   | 0 <v<sub>IN&lt; V<sub>DD</sub></v<sub>                                 | -100                  | _   | 100 | nA    |  |  |

| Logic High Level Output<br>Voltage                                                                                                                     | V <sub>OH</sub>   | I <sub>OH</sub> <1 mA source, V <sub>DD</sub> =1.8 V                   | V <sub>DD</sub> – 0.6 |     | —   | V     |  |  |

| Logic Low Level Output Voltage                                                                                                                         | V <sub>OL</sub>   | I <sub>OL</sub> <1 mA sink, V <sub>DD</sub> =1.8 V                     |                       | _   | 0.6 | V     |  |  |

| Note: All specifications guaranteed by qualification. Qualification test conditions are listed in the "Production Test Conditions" section on page 13. |                   |                                                                        |                       |     |     |       |  |  |

#### Table 5. Digital IO Specifications (SDO, SDI, SCLK, nSEL, and nIRQ)

#### Table 6. GPIO Specifications (GPIO\_0, GPIO\_1, and GPIO\_2)

| Parameter                            | Symbol              | Conditions                                                                              | Min                   | Тур | Max | Units |

|--------------------------------------|---------------------|-----------------------------------------------------------------------------------------|-----------------------|-----|-----|-------|

| Rise Time                            | T <sub>RISE</sub>   | 0.1 x V <sub>DD</sub> to 0.9 x V <sub>DD</sub> ,<br>C <sub>L</sub> = 10 pF, DRV<1:0>=HH | —                     | _   | 8   | ns    |

| Fall Time                            | T <sub>FALL</sub>   | 0.9 x V <sub>DD</sub> to 0.1 x V <sub>DD,</sub><br>C <sub>L</sub> = 10 pF, DRV<1:0>=HH  | —                     | _   | 8   | ns    |

| Input Capacitance                    | C <sub>IN</sub>     |                                                                                         | —                     | —   | 1   | pF    |

| Logic High Level Input Voltage       | V <sub>IH</sub>     |                                                                                         | V <sub>DD</sub> – 0.6 | —   |     | V     |

| Logic Low Level Input Voltage        | V <sub>IL</sub>     |                                                                                         | —                     | _   | 0.6 | V     |

| Input Current                        | I <sub>IN</sub>     | 0 <v<sub>IN&lt; V<sub>DD</sub></v<sub>                                                  | -100                  | _   | 100 | nA    |

| Input Current If Pullup is Activated | I <sub>INP</sub>    | V <sub>IL</sub> =0 V                                                                    | 5                     | _   | 25  | μA    |

| Maximum Output Current               | I <sub>OmaxLL</sub> | DRV<1:0>=LL                                                                             | 0.1                   | 0.5 | 0.8 | mA    |

|                                      | I <sub>OmaxLH</sub> | DRV<1:0>=LH                                                                             | 0.9                   | 2.3 | 3.5 | mA    |

|                                      | I <sub>OmaxHL</sub> | DRV<1:0>=HL                                                                             | 1.5                   | 3.1 | 4.8 | mA    |

|                                      | I <sub>OmaxHH</sub> | DRV<1:0>=HH                                                                             | 1.8                   | 3.6 | 5.4 | mA    |

| Logic High Level Output Voltage      | V <sub>OH</sub>     | I <sub>OH</sub> < I <sub>Omax</sub> source,<br>V <sub>DD</sub> =1.8 V                   | V <sub>DD</sub> – 0.6 | _   | _   | V     |

| Logic Low Level Output Voltage       | V <sub>OL</sub>     | I <sub>OL</sub> < I <sub>Omax</sub> sink,<br>V <sub>DD</sub> =1.8 V                     | —                     |     | 0.6 | V     |

#### Table 7. Absolute Maximum Ratings

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Value                       | Unit |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|--|--|--|--|--|--|

| V <sub>DD</sub> to GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -0.3, +3.6                  | V    |  |  |  |  |  |  |

| Instantaneous V <sub>RF-peak</sub> to GND on TX Output Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -0.3, +8.0                  | V    |  |  |  |  |  |  |

| Sustained V <sub>RF-peak</sub> to GND on TX Output Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -0.3, +6.5                  | V    |  |  |  |  |  |  |

| Voltage on Digital Control Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | –0.3, V <sub>DD</sub> + 0.3 | V    |  |  |  |  |  |  |

| Voltage on Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | –0.3, V <sub>DD</sub> + 0.3 | V    |  |  |  |  |  |  |

| Operating Ambient Temperature Range T <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -40 to +85                  | °C   |  |  |  |  |  |  |

| Thermal Impedance $\theta_{JA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                          | °C/W |  |  |  |  |  |  |

| Junction Temperature T <sub>J</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | +125                        | °C   |  |  |  |  |  |  |

| Storage Temperature Range T <sub>STG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -55 to +125                 | °C   |  |  |  |  |  |  |

| Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at or beyond these ratings in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Power Amplifier may be damaged if switched on without proper load or termination connected. TX matching network design will influence TX V <sub>RF-peak</sub> on TX output pin. Caution: ESD sensitive device. |                             |      |  |  |  |  |  |  |

### 1.1. Definition of Test Conditions

#### **Production Test Conditions:**

- T<sub>A</sub> = +25 °C

- V<sub>DD</sub> = +3.3 VDC

- TX output power measured at 915 MHz

- External reference signal (XOUT) = 1.0 V<sub>PP</sub> at 30 MHz, centered around 0.8 VDC

- Production test schematic (unless noted otherwise)

- All RF output levels referred to the pins of the Si4030/31/32 (not the RF module)

#### **Qualification Test Conditions:**

- T<sub>A</sub> = -40 to +85 °C

- V<sub>DD</sub> = +1.8 to +3.6 VDC

- Using 4032, 4031, or 4030 reference design or production test schematic

- All RF output levels referred to the pins of the Si4030/31/32 (not the RF module)

### 2. Functional Description

The Si4030/31/32 are ISM wireless transmitters with continuous frequency tuning over their specified bands which encompasses 240–960 MHz. The wide operating voltage range of 1.8–3.6 V and low current consumption makes the Si4030/31/32 an ideal solution for battery powered applications.

The RF carrier is generated by an integrated VCO and  $\Delta\Sigma$  Fractional-N PLL synthesizer. The synthesizer is designed to support configurable data rates, output frequency, frequency deviation, and Gaussian filtering at any frequency between 240–960 MHz. The transmit FSK data is modulated directly into the  $\Delta\Sigma$  data stream and can be shaped by a Gaussian low-pass filter to reduce unwanted spectral content.

The Si4032's PA output power can be configured between +1 and +20 dBm in 3 dB steps, while the Si4030/31's PA output power can be configured between –8 and +13 dBm in 3 dB steps. The PA is single-ended to allow for easy antenna matching and low BOM cost. The PA incorporates automatic ramp-up and ramp-down control to reduce unwanted spectral spreading. The +20 dBm power amplifier of the Si4032 can also be used to compensate for the reduced performance of a lower cost, lower performance antenna or antenna with size constraints due to a small form-factor. Competing solutions require large and expensive external PAs to achieve comparable performance.

The Si4030/31/32 is designed to work with a microcontroller, crystal, and a few external components to create a very low cost system. Voltage regulators are integrated on-chip which allows for a wide operating supply voltage range from +1.8 to +3.6 V. A standard 4-pin SPI bus is used to communicate with an external microcontroller. Three configurable general purpose I/Os are available. A complete list of the available GPIO functions is available in "AN466: Si4030/31/32 Register Descriptions."

#### 2.1. Operating Modes

The Si4030/31/32 provides several operating modes which can be used to optimize the power consumption for a given application.

Table 8 summarizes the operating modes of the Si4030/31/32. In general, any given operating mode may be classified as an active mode or a power saving mode. The table indicates which block(s) are enabled (active) in each corresponding mode. With the exception of the SHUTDOWN mode, all can be dynamically selected by sending the appropriate commands over the SPI. An "X" in any cell means that, in the given mode of operation, that block can be independently programmed to be either ON or OFF, without noticeably impacting the current consumption. The SPI circuit block includes the SPI interface hardware and the device register space. The 32 kHz OSC block includes the 32.768 kHz RC oscillator or 32.768 kHz crystal oscillator and wake-up timer. AUX (Auxiliary Blocks) includes the temperature sensor, general purpose ADC, and low-battery detector.

| Mode Name         |                                    | Circuit Blocks |                  |       |                |     |     |                  |

|-------------------|------------------------------------|----------------|------------------|-------|----------------|-----|-----|------------------|

|                   | Digital LDO                        | SPI            | 32 kHz OSC       | AUX   | 30 MHz<br>XTAL | PLL | PA  | I <sub>VDD</sub> |

| SHUTDOWN          | OFF<br>(Register contents<br>lost) | OFF            | OFF              | OFF   | OFF            | OFF | OFF | 15 nA            |

| STANDBY           | ON                                 | ON             | OFF              | OFF   | OFF            | OFF | OFF | 450 nA           |

| SLEEP             | (Register contents                 | ON             | ON               | Х     | OFF            | OFF | OFF | 1 µA             |

| SENSOR            | retained)                          | ON             | Х                | ON    | OFF            | OFF | OFF | 1 µA             |

| READY             |                                    | ON             | Х                | Х     | ON             | OFF | OFF | 800 µA           |

| TUNING            |                                    | ON             | Х                | Х     | ON             | ON  | OFF | 8.5 mA           |

| TRANSMIT          |                                    | ON             | Х                | Х     | ON             | ON  | ON  | 30 mA*           |

| *Note: Using Si40 | )30/31 at +13 dBm using r          | ecommen        | ded reference de | sign. |                | 1   | 1   |                  |

#### **Table 8. Operating Modes**

### 3. Controller Interface

#### 3.1. Serial Peripheral Interface (SPI)

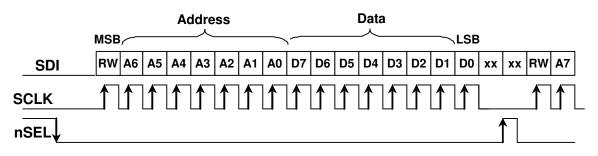

The Si4030/31/32 communicates with the host MCU over a standard 3-wire SPI interface: SCLK, SDI, and nSEL. The host MCU can read data from the device on the SDO output pin. A SPI transaction is a 16-bit sequence which consists of a Read-Write ( $\overline{R}$ /W) select bit, followed by a 7-bit address field (ADDR), and an 8-bit data field (DATA) as demonstrated in Figure 1. The 7-bit address field is used to select one of the 128, 8-bit control registers. The  $\overline{R}$ /W select bit determines whether the SPI transaction is a read or write transaction. If  $\overline{R}$ /W = 1 it signifies a WRITE transaction, while  $\overline{R}$ /W = 0 signifies a READ transaction. The contents (ADDR or DATA) are latched into the Si4030/31/32 every eight clock cycles. The timing parameters for the SPI interface are shown in Table 9. The SCLK rate is flexible with a maximum rate of 10 MHz.

Figure 1. SPI Timing

| Symbol          | Parameter              | Min (nsec) | Diagram |

|-----------------|------------------------|------------|---------|

| t <sub>CH</sub> | Clock high time        | 40         |         |

| t <sub>CL</sub> | Clock low time         | 40         |         |

| t <sub>DS</sub> | Data setup time        | 20         |         |

| t <sub>DH</sub> | Data hold time         | 20         |         |

| t <sub>DD</sub> | Output data delay time | 20         |         |

| t <sub>EN</sub> | Output enable time     | 20         |         |

| t <sub>DE</sub> | Output disable time    | 50         |         |

| t <sub>SS</sub> | Select setup time      | 20         |         |

| t <sub>SH</sub> | Select hold time       | 50         |         |

| t <sub>SW</sub> | Select high period     | 80         |         |

Table 9. Serial Interface Timing Parameters

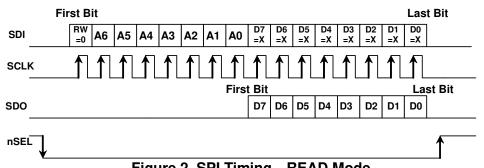

To read back data from the Si4030/31/32, the R/W bit must be set to 0 followed by the 7-bit address of the register from which to read. The 8 bit DATA field following the 7-bit ADDR field is ignored n the SDI pin when R/W = 0. The next eight negative edge transitions of the SCLK signal will clock out the contents of the selected register. The data read from the selected register will be available on the SDO output pin. The READ function is shown in Figure 2. After the READ function is completed the SDO pin will remain at either a logic 1 or logic 0 state depending on the last data bit clocked out (D0). When nSEL goes high the SDO output pin will be pulled high by internal pullup.

The SPI interface contains a burst read/write mode which allows for reading/writing sequential registers without having to re-send the SPI address. When the nSEL bit is held low while continuing to send SCLK pulses, the SPI interface will automatically increment the ADDR and read from/write to the next address. An example burst write transaction is illustrated in Figure 3 and a burst read in Figure 4. As long as nSEL is held low, input data will be latched into the Si4030/31/32 every eight SCLK cycles.

#### 3.2. Operating Mode Control

There are three primary states in the Si4030/31/32 radio state machine: SHUTDOWN, IDLE, and TX (see Figure 5). The SHUTDOWN state completely shuts down the radio to minimize current consumption. There are five different configurations/options for the IDLE state which can be selected to optimize the chip to the applications needs. "Register 07h. Operating Mode and Function Control 1" controls which operating mode/state is selected with the exception of SHUTDOWN which is controlled by SDN pin 20. The TX state may be reached automatically from any of the IDLE states by setting the txon bit in "Register 07h. Operating Mode and Function Control 1." Table 10 shows each of the operating modes with the time required to reach TX mode as well as the current consumption of each mode.

The Si4030/31/32 includes a low-power digital regulated supply (LPLDO) which is internally connected in parallel to the output of the main digital regulator (and is available externally at the VR\_DIG pin). This common digital supply voltage is connected to all digital circuit blocks including the SPI and register space. The LPLDO has extremely low quiescent current consumption but limited current supply capability; it is used only in the IDLE-STANDBY and IDLE-SLEEP modes. The main digital regulator is automatically enabled in all other modes.

Figure 5. State Machine Diagram

| State/Mode      | Response Time to TX | Current in State/Mode [µA] |

|-----------------|---------------------|----------------------------|

| Shut Down State | 16.8 ms             | 15 nA                      |

| Idle States:    |                     |                            |

| Standby Mode    | 800 µs              | 450 nA                     |

| Sleep Mode      | 800 µs              | 1 µA                       |

| Sensor Mode     | 800 µs              | 1 µA                       |

| Ready Mode      | 200 µs              | 800 µA                     |

| Tune Mode       | 200 µs              | 8.5 mA                     |

| TX State        | NA                  | Si4032:                    |

|                 |                     | 85 mA @ +20 dBm,           |

|                 |                     | Si4030/31:                 |

|                 |                     | 30 mA @ +13 dBm            |

#### Table 10. Operating Modes Response Time

#### 3.2.1. SHUTDOWN State

The SHUTDOWN state is the lowest current consumption state of the device with nominally less than 15 nA of current consumption. The SHUTDOWN state may be entered by driving the SDN pin (Pin 20) high. The SDN pin should be held low in all states except the SHUTDOWN state. In the SHUTDOWN state, the contents of the registers are lost and there is no SPI access.

When the chip is connected to the power supply, a POR will be initiated after the falling edge of SDN.

#### 3.2.2. IDLE State

There are five different modes in the IDLE state which may be selected by "Register 07h. Operating Mode and Function Control 1". All modes have a tradeoff between current consumption and response time to TX mode. This tradeoff is shown in Table 10. After the POR event, SWRESET, or exiting from the SHUTDOWN state the chip will default to the IDLE-READY mode. After a POR event the interrupt registers must be read to properly enter the SLEEP, SENSOR, or STANDBY mode and to control the 32 kHz clock correctly.

#### 3.2.2.1. STANDBY Mode

STANDBY mode has the lowest current consumption of the five IDLE states with only the LPLDO enabled to maintain the register values. In this mode the registers can be accessed in both read and write mode. The STANDBY mode can be entered by writing 0h to "Register 07h. Operating Mode and Function Control 1". If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption. Additionally, the ADC should not be selected as an input to the GPIO in this mode as it will cause excess current consumption.

#### 3.2.2.2. SLEEP Mode

In SLEEP mode the LPLDO is enabled along with the Wake-Up-Timer, which can be used to accurately wake-up the radio at specified intervals. See "7.6. Wake-Up Timer" on page 45 for more information on the Wake-Up-Timer. SLEEP mode is entered by setting enwt = 1 (40h) in "Register 07h. Operating Mode and Function Control 1". If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption. Also, the ADC should not be selected as an input to the GPIO in this mode as it will cause excess current consumption.

#### 3.2.2.3. SENSOR Mode

In SENSOR Mode either the Low Battery Detector, Temperature Sensor, or both may be enabled in addition to the LPLDO and Wake-Up-Timer. The Low Battery Detector can be enabled by setting enlbd = 1 in "Register 07h. Operating Mode and Function Control 1". See "7.4. Temperature Sensor" on page 42 and "7.5. Low Battery Detector" on page 44 for more information on these features. If an interrupt has occurred (i.e., the nIRQ pin = 0) the interrupt registers must be read to achieve the minimum current consumption.

#### 3.2.2.4. READY Mode

READY Mode is designed to give a fast transition time to TX mode with reasonable current consumption. In this mode the Crystal oscillator remains enabled reducing the time required to switch to TX mode by eliminating the crystal start-up time. READY mode is entered by setting xton = 1 in "Register 07h. Operating Mode and Function Control 1". To achieve the lowest current consumption state the crystal oscillator buffer should be disabled in "Register 62h. Crystal Oscillator Control and Test."

#### 3.2.2.5. TUNE Mode

In TUNE Mode the PLL remains enabled in addition to the other blocks enabled in the IDLE modes. This will give the fastest response to TX mode as the PLL will remain locked but it results in the highest current consumption. This mode of operation is designed for frequency hopping spread spectrum systems (FHSS). TUNE mode is entered by setting pllon = 1 in "Register 07h. Operating Mode and Function Control 1". It is not necessary to set xton to 1 for this mode, the internal state machine automatically enables the crystal oscillator.

#### 3.2.3. TX State

The TX state may be entered from any of the IDLE modes when the txon bit is set to 1 in "Register 07h. Operating Mode and Function Control 1". A built-in sequencer takes care of all the actions required to transition between states from enabling the crystal oscillator to ramping up the PA. The following sequence of events will occur automatically when going from STANDBY mode to TX mode by setting the txon bit.

- 1. Enable the main digital LDO and the Analog LDOs.

- 2. Start up crystal oscillator and wait until ready (controlled by an internal timer).

- 3. Enable PLL.

- 4. Calibrate VCO (this action is skipped when the vcocal bit is "0", default value is "1").

- 5. Wait until PLL settles to required transmit frequency (controlled by timer).

- 6. Activate power amplifier and wait until power ramping is completed (controlled by an internal timer).

- 7. Transmit packet.

Steps in this sequence may be eliminated depending on which IDLE mode the chip is configured to prior to setting the txon bit. By default, the VCO and PLL are calibrated every time the PLL is enabled.

#### 3.2.4. Device Status

| Add | R/W | Function/Description | D7     | D6     | D5       | D4       | D3      | D2 | D1     | D0     | POR Def. |

|-----|-----|----------------------|--------|--------|----------|----------|---------|----|--------|--------|----------|

| 02  | R   | Device Status        | ffovfl | ffunfl | Reserved | Reserved | freqerr |    | cps[1] | cps[0] | —        |

The operational status of the chip can be read from "Register 02h. Device Status".

#### 3.3. Interrupts

The Si4030/31/32 is capable of generating an interrupt signal when certain events occur. The chip notifies the microcontroller that an interrupt event has occurred by setting the nIRQ output pin LOW = 0. This interrupt signal will be generated when any one (or more) of the interrupt events (corresponding to the Interrupt Status bits) shown below occur. The nIRQ pin will remain low until the microcontroller reads the Interrupt Status Register(s) (Registers 03h–04h) containing the active Interrupt Status bit. The nIRQ output signal will then be reset until the next change in status is detected. The interrupts must be enabled by the corresponding enable bit in the Interrupt Enable Registers (Registers 05h–06h). All enabled interrupt bits will be cleared when the microcontroller reads the interrupt status register. If the interrupt is not enabled when the event occurs it will not trigger the nIRQ pin, but the status may still be read at anytime in the Interrupt Status registers.

| Add | R/W | Function/Descript<br>ion | D7       | D6          | D5        | D4       | D3    | D2       | D1        | D0       | POR Def. |

|-----|-----|--------------------------|----------|-------------|-----------|----------|-------|----------|-----------|----------|----------|

| 03  | R   | Interrupt Status 1       | ifferr   | itxffafull  | itxffaem  | Reserved | iext  | ipksent  | Reserved  | Reserved | —        |

| 04  | R   | Interrupt Status 2       | Reserved | Reserved    | Reserved  | Reserved | iwut  | ilbd     | ichiprdy  | ipor     | —        |

| 05  | R/W | Interrupt Enable 1       | enfferr  | entxffafull | entxffaem | Reserved | enext | enpksent | Reserved  | Reserved | 00h      |

| 06  | R/W | Interrupt Enable 2       | Reserved | Reserved    | Reserved  | Reserved | enwut | enlbd    | enchiprdy | enpor    | 01h      |

See "AN466: Si4030/31/32 Register Descriptions" for a complete list of interrupts.

#### 3.4. System Timing

The system timing for TX mode is shown in Figure 6. The figures demonstrate transitioning from STANDBY mode to TX mode through the built-in sequencer of required steps. The user only needs to program the desired mode, and the internal sequencer will properly transition the part from its current mode.

The VCO will automatically calibrate at every frequency change or power up. The PLL T0 time is to allow for bias settling of the VCO. The PLL TS time is for the settling time of the PLL, which has a default setting of 100  $\mu$ s. The total time for PLL T0, PLL CAL, and PLL TS under all conditions is 200  $\mu$ s. Under certain applications, the PLL T0 time and the PLL CAL may be skipped for faster turn-around time. Contact applications support if faster turnaround time is desired.

Figure 6. TX Timing

#### 3.5. Frequency Control

For calculating the necessary frequency register settings it is recommended that customers use Silicon Labs' Wireless Design Suite (WDS) or the EZRadioPRO Register Calculator worksheet (in Microsoft Excel) available on the product website. These methods offer a simple method to quickly determine the correct settings based on the application requirements. The following information can be used to calculated these values manually.

#### 3.5.1. Frequency Programming

In order to transmit an RF signal, the desired channel frequency,  $f_{carrier}$ , must be programmed into the Si4030/31/32. Note that this frequency is the center frequency of the desired channel. The carrier frequency is generated by a Fractional-N Synthesizer, using 10 MHz both as the reference frequency and the clock of the (3<sup>rd</sup> order)  $\Delta\Sigma$  modulator. This modulator uses modulo 64000 accumulators. This design was made to obtain the desired frequency resolution of the synthesizer. The overall division ratio of the feedback loop consist of an integer part (N) and a fractional part (F).In a generic sense, the output frequency of the synthesizer is as follows:

$$f_{OUT} = 10MHz \times (N+F)$$

The fractional part (F) is determined by three different values, Carrier Frequency (fc[15:0]), Frequency Offset (fo[8:0]), and Frequency Deviation (fd[7:0]). Due to the fine resolution and high loop bandwidth of the synthesizer, FSK modulation is applied inside the loop and is done by varying F according to the incoming data; this is discussed further in "3.5.4. Frequency Deviation" on page 24. Also, a fixed offset can be added to fine-tune the carrier frequency and counteract crystal tolerance errors. For simplicity assume that only the fc[15:0] register will determine the fractional component. The equation for selection of the carrier frequency is shown below:

$$f_{carrier} = 10MHz \times (hbsel + 1) \times (N + F)$$

$$f_{TX} = 10MHz * (hbsel + 1) * (fb[4:0] + 24 + \frac{fc[15:0]}{64000})$$

| Add | R/W | Function/Description           | D7     | D6     | D5     | D4     | D3     | D2     | D1    | D0    | POR Def. |

|-----|-----|--------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|----------|

| 73  | R/W | Frequency Offset 1             | fo[7]  | fo[6]  | fo[5]  | fo[4]  | fo[3]  | fo[2]  | fo[1] | fo[0] | 00h      |

| 74  | R/W | Frequency Offset 2             |        |        |        |        |        |        | fo[9] | fo[8] | 00h      |

| 75  | R/W | Frequency Band Select          |        | sbsel  | hbsel  | fb[4]  | fb[3]  | fb[2]  | fb[1] | fb[0] | 35h      |

| 76  | R/W | Nominal Carrier<br>Frequency 1 | fc[15] | fc[14] | fc[13] | fc[12] | fc[11] | fc[10] | fc[9] | fc[8] | BBh      |

| 77  | R/W | Nominal Carrier<br>Frequency 0 | fc[7]  | fc[6]  | fc[5]  | fc[4]  | fc[3]  | fc[2]  | fc[1] | fc[0] | 80h      |

The integer part (N) is determined by fb[4:0]. Additionally, the output frequency can be halved by connecting a  $\div 2$  divider to the output. This divider is not inside the loop and is controlled by the hbsel bit in "Register 75h. Frequency Band Select". This effectively partitions the entire 240–960 MHz frequency range into two separate bands: High Band (HB) for hbsel = 1, and Low Band (LB) for hbsel = 0. The valid range of fb[4:0] is from 0 to 23. If a higher value is written into the register, it will default to a value of 23. The integer part has a fixed offset of 24 added to it as shown in the formula above. Table 11 demonstrates the selection of fb[4:0] for the corresponding frequency band.

After selection of the fb (N) the fractional component may be solved with the following equation:

$$fc[15:0] = \left(\frac{f_{TX}}{10MHz*(hbsel+1)} - fb[4:0] - 24\right)*64000$$

fb and fc are the actual numbers stored in the corresponding registers.

| fb[4:0] Value | Ν  | Frequen       | cy Band       |

|---------------|----|---------------|---------------|

|               |    | hbsel=0       | hbsel=1       |

| 0             | 24 | 240–249.9 MHz | 480–499.9 MHz |

| 1             | 25 | 250–259.9 MHz | 500–519.9 MHz |

| 2             | 26 | 260–269.9 MHz | 520–539.9 MHz |

| 3             | 27 | 270–279.9 MHz | 540–559.9 MHz |

| 4             | 28 | 280–289.9 MHz | 560–579.9 MHz |

| 5             | 29 | 290–299.9 MHz | 580–599.9 MHz |

| 6             | 30 | 300–309.9 MHz | 600–619.9 MHz |

| 7             | 31 | 310–319.9 MHz | 620–639.9 MHz |

| 8             | 32 | 320–329.9 MHz | 640–659.9 MHz |

| 9             | 33 | 330–339.9 MHz | 660–679.9 MHz |

| 10            | 34 | 340–349.9 MHz | 680–699.9 MHz |

| 11            | 35 | 350–359.9 MHz | 700–719.9 MHz |

| 12            | 36 | 360–369.9 MHz | 720–739.9 MHz |

| 13            | 37 | 370–379.9 MHz | 740–759.9 MHz |

| 14            | 38 | 380–389.9 MHz | 760–779.9 MHz |

| 15            | 39 | 390–399.9 MHz | 780–799.9 MHz |

| 16            | 40 | 400–409.9 MHz | 800–819.9 MHz |

| 17            | 41 | 410–419.9 MHz | 820–839.9 MHz |

| 18            | 42 | 420–429.9 MHz | 840–859.9 MHz |

| 19            | 43 | 430–439.9 MHz | 860–879.9 MHz |

| 20            | 44 | 440–449.9 MHz | 880–899.9 MHz |

| 21            | 45 | 450–459.9 MHz | 900–919.9 MHz |

| 22            | 46 | 460–469.9 MHz | 920–939.9 MHz |

| 23            | 47 | 470–479.9 MHz | 940–960 MHz   |

### Table 11. Frequency Band Selection

#### 3.5.2. Easy Frequency Programming for FHSS

While Registers 73h–77h may be used to program the carrier frequency of the Si4030/31/32, it is often easier to think in terms of "channels" or "channel numbers" rather than an absolute frequency value in Hz. Also, there may be some timing-critical applications (such as for Frequency Hopping Systems) in which it is desirable to change frequency by programming a single register. Once the channel step size is set, the frequency may be changed by a single register corresponding to the channel number. A nominal frequency is first set using Registers 73h–77h, as described above. Registers 79h and 7Ah are then used to set a channel step size and channel number, relative to the nominal setting. The Frequency Hopping Step Size (fhs[7:0]) is set in increments of 10 kHz with a maximum channel step size of 2.56 MHz. The Frequency Hopping Channel Select Register then selects channels based on multiples of the step size.

$$F_{carrier} = Fnom + fhs[7:0] \times (fhch[7:0] \times 10kHz)$$

For example, if the nominal frequency is set to 900 MHz using Registers 73h–77h, the channel step size is set to 1 MHz using "Register 7Ah. Frequency Hopping Step Size," and "Register 79h. Frequency Hopping Channel Select" is set to 5d, the resulting carrier frequency would be 905 MHz. Once the nominal frequency and channel step size are programmed in the registers, it is only necessary to program the fhch[7:0] register in order to change the frequency.

| Add | R/W | Function/Description                | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      | POR Def. |

|-----|-----|-------------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|----------|

| 79  | R/W | Frequency Hopping Channel<br>Select | fhch[7] | fhch[6] | fhch[5] | fhch[4] | fhch[3] | fhch[2] | fhch[1] | fhch[0] | 00h      |

| 7A  | R/W | Frequency Hopping Step<br>Size      | fhs[7]  | fhs[6]  | fhs[5]  | fhs[4]  | fhs[3]  | fhs[2]  | fhs[1]  | fhs[0]  | 00h      |

#### 3.5.3. Automatic State Transition for Frequency Change

If registers 79h or 7Ah are changed in TX mode, the state machine will automatically transition the chip back to TUNE and change the frequency. This feature is useful to reduce the number of SPI commands required in a Frequency Hopping System. This in turn reduces microcontroller activity, reducing current consumption. The exception to this is during TX FIFO mode. If a frequency change is initiated during a TX packet, then the part will complete the current TX packet and will only change the frequency for subsequent packets.

#### 3.5.4. Frequency Deviation

The peak frequency deviation is configurable from  $\pm 0.625$  to  $\pm 320$  kHz. The Frequency Deviation ( $\Delta f$ ) is controlled by the Frequency Deviation Register (fd), address 71 and 72h, and is independent of the carrier frequency setting. When enabled, regardless of the setting of the hbsel bit (high band or low band), the resolution of the frequency deviation will remain in increments of 625 Hz. When using frequency modulation the carrier frequency will deviate from the nominal center channel carrier frequency by  $\pm \Delta f$ :

$$\Delta f = fd[8:0] \times 625Hz$$

$$fd[8:0] = \frac{\Delta f}{625Hz} \quad \Delta f = \text{peak deviation}$$

Figure 7. Frequency Deviation

The previous equation should be used to calculate the desired frequency deviation. If desired, frequency modulation may also be disabled in order to obtain an unmodulated carrier signal at the channel center frequency; see "4.1. Modulation Type" on page 27 for further details.

| Add | R/W | Function/Description      | D7       | D6       | D5       | D4       | D3    | D2    | D1        | D0        | POR Def. |

|-----|-----|---------------------------|----------|----------|----------|----------|-------|-------|-----------|-----------|----------|

| 71  | R/W | Modulation Mode Control 2 | trclk[1] | trclk[0] | dtmod[1] | dtmod[0] | eninv | fd[8] | modtyp[1] | modtyp[0] | 00h      |

| 72  | R/W | Frequency Deviation       | fd[7]    | fd[6]    | fd[5]    | fd[4]    | fd[3] | fd[2] | fd[1]     | fd[0]     | 20h      |