# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

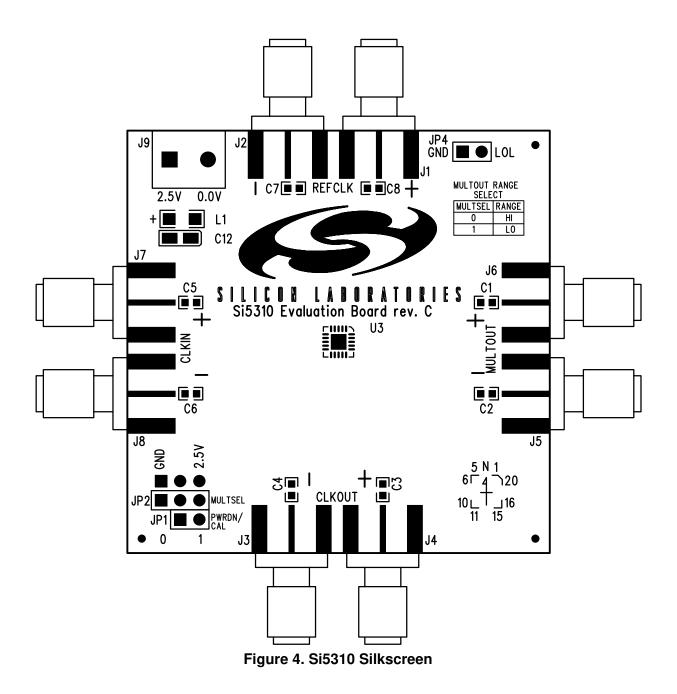

## EVALUATION BOARD FOR SI5310 PRECISION CLOCK MULTIPLIER/REGENERATOR IC

## Description

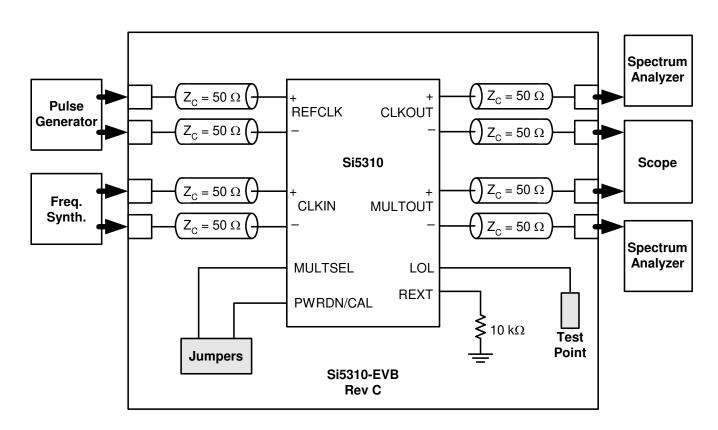

The Si5310 evaluation board provides a platform for testing and characterizing the Silicon Laboratories Si5310 precision clock multiplier/regenerator IC.

All high-speed I/Os are AC coupled to ease interfacing to industry standard test equipment.

## Features

- Single 2.5 V power supply

- Differential I/Os ac coupled

- Simple jumper configuration

## Function Block Diagram

## **Functional Description**

The evaluation board simplifies characterization of the Si5310 precision clock multiplier/regenerator IC by providing access to all of the Si5310 I/Os. Device performance can be evaluated by following the "Test Configuration" section. Specific performance metrics include jitter tolerance, jitter generation, and jitter transfer.

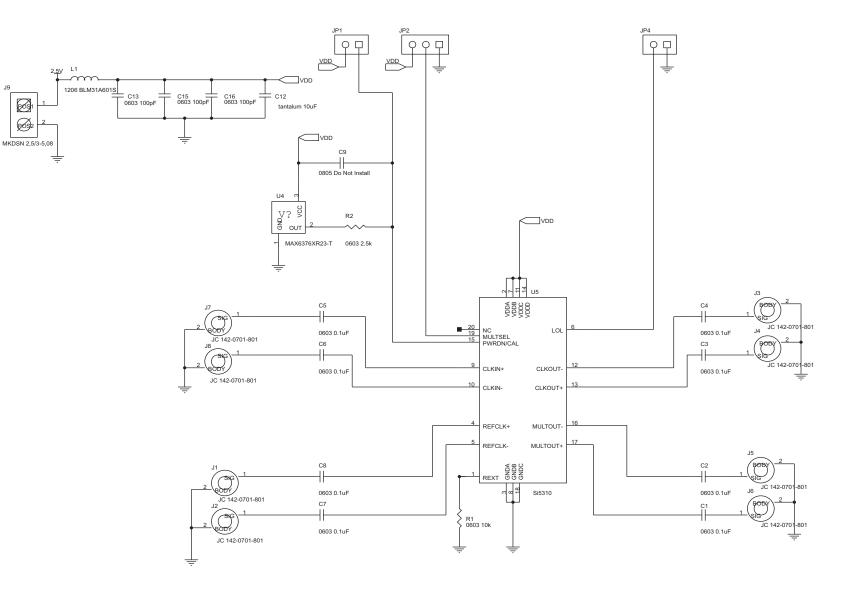

## **Power supply**

The evaluation board requires one 2.5 V supply. Supply filtering is placed on the board to filter typical system noise components; however, initial performance testing should use a linear supply capable of supplying 2.5 V  $\pm$ 5% DC.

*CAUTION*: The evaluation board is designed so that the body of the SMA jacks and GND are shorted. Care must be taken when powering the PCB at potentials other than GND at 0.0 V and VDD at 2.5 V relative to chassis GND.

## Self-Calibration

The Si5310 device provides an internal self-calibration function that optimizes the loop gain parameters within the internal DSPLL<sup>™</sup>. Self-calibration is initiated by a high-to-low transition of the PWRDN/CAL signal while a valid reference clock is supplied to the REFCLK input. On the Si5310-EVB board, a voltage detector IC is utilized to initiate self-calibration. The voltage detector drives the PWRDN/CAL signal low after the supply voltage has reached a specific voltage level. This circuit is described in Silicon Laboratories application note AN42. On the Si5310-EVB, the PWRDN/CAL signal is also accessible via a jumper located in the lower left-hand corner of the evaluation board. PWRDN/CAL is wired to the center post (signal post) between 2.5 V and GND.

#### **Device Power Down**

The Si5310 device can be powered down via the PWRDN/CAL signal. When PWRDN/CAL is driven high (2.5 V) the evaluation board will draw minimal current. On the Si5310-EVB board, the PWRDN/CAL signal may be controlled via a jumper located in the lower left-hand corner of the evaluation board. PWRDN/CAL is wired to the center post (signal post) between 2.5 V and GND.

## CLKIN, CLKOUT, MULTOUT

These high-speed I/Os are wired to the board perimeter on 30 mil (0.030 inch) 50  $\Omega$  microstrip lines to the endlaunch SMA jacks as labeled on the PCB. These I/Os are AC coupled to simplify direct connection to a wide array of standard test hardware. Because each of these signals are differential both the positive (+) and negative (-) terminals must be terminated to 50  $\Omega$ . Terminating only one side will degrade the performance of the Si5310 device. The CLKIN inputs are terminated on the die with 50  $\Omega$  resistors.

Note: The 50  $\Omega$  termination is for each terminal/side of a differential signal, thus the differential termination is actually 50  $\Omega$  + 50  $\Omega$  = 100  $\Omega$ .

## REFCLK

REFCLK is used to center the frequency of the Si5310 DSPLL so that the device can lock to the CLKIN signal. For a given CLKIN rate, there are five choices for the REFCLK frequency. These five options are all multiples of the CLKIN frequency, as indicated in Table 1. The REFCLK frequency is automatically detected by the Si5310 device, so no digital control inputs are needed for REFCLK frequency selection. REFCLK may be synchronous or asynchronous with respect to CLKIN. However, REFCLK must be within  $\pm 100$  PPM of the target CLKIN frequency multiple. REFCLK is ac coupled to the SMA jacks located on the top side of the evaluation board. The REFCLK inputs are terminated on the die with 50  $\Omega$  resistors.

**Note:** The 50  $\Omega$  termination is for each terminal/side of a differential signal, thus the differential termination is actually 50  $\Omega$  + 50  $\Omega$  = 100  $\Omega$ .

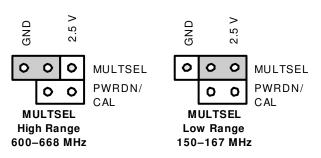

## MULTSEL

MULTSEL is a binary input to the Si5310 device that selects the frequency range for the MULTOUT clock output. The MULTOUT output frequency is a multiple of the CLKIN input frequency. The frequency for MULTOUT will be in either the 150–167 MHz frequency range or the 600–668 MHz frequency range depending on the state of the MULTSEL signal as indicated in Table 1. On the Si5310 evaluation board, MULTSEL is controlled via a jumper located in the lower left-hand corner of the board. MULTSEL is wired to the center post (signal post) between 2.5 V and GND.

The jumper configurations for MULTSEL are indicated in Figure 1.

| MULTSEL                      | CLKIN Range<br>(MHz) | REFCLK = 2 <sup>n</sup> x CLKIN<br>±100 ppm<br>(see Note 2) | CLKOUT     | MULTOUT  |

|------------------------------|----------------------|-------------------------------------------------------------|------------|----------|

| 0<br>(MULTOUT = 600–668 MHz) | 37.500–41.750        | n = -2, -1, 0, 1, or 2                                      | 1xCLKIN    | 16xCLKIN |

|                              | 75.000–83.500        | n = -3, -2, -1, 0, or 1                                     | 1xCLKIN    | 8xCLKIN  |

|                              | 150.000–167.000      | n = -4, -3, -2, -1, or 0                                    | 1xCLKIN    | 4xCLKIN  |

|                              | 300.000–334.000      | n = -5, -4, -3, -2, or -1                                   | 1xCLKIN    | 2xCLKIN  |

|                              | 600.000–668.000      | n = -6, -5, -4, -3, or -2                                   | See Note 1 | 1xCLKIN  |

| 1<br>(MULTOUT = 150–167 MHz) | 9.375–10.438         | n = 0, 1, 2, 3, or 4                                        | 1xCLKIN    | 16xCLKIN |

|                              | 18.750–20.875        | n = -1, 0, 1, 2, or 3                                       | 1xCLKIN    | 8xCLKIN  |

|                              | 37.500–41.750        | n = -2, -1, 0, 1, or 2                                      | 1xCLKIN    | 4xCLKIN  |

|                              | 75.000–83.500        | n = -3, -2, -1, 0, or 1                                     | 1xCLKIN    | 2xCLKIN  |

|                              | 150.000–167.000      | n = -4, -3, -2, -1, or 0                                    | See Note 1 | 1xCLKIN  |

Table 1. CLKIN, CLKOUT, MULTOUT, REFCLK Operating Ranges

Note:

1. The CLKOUT output is not valid for MULTOUT:CLKIN ratios of 1:1 (MULTOUT = 1 x CLKIN.)

2. The REFCLK input can be set to any one of the five CLKIN multiples indicated. The REFCLK input can be

asynchronous to the CLKIN input, but must be within ±100 ppm of the stated CLKIN multiple.

## Figure 1. MULTSEL Jumper Configurations

## Loss-of-Lock (LOL)

LOL is an indicator of the relative frequency between the REFCLK input, which is nominally a multiple of CLKIN, and an internally generated multiple of CLKIN. LOL will assert when the frequency difference is greater than ±600 PPM. In order to prevent LOL from deasserting prematurely, there is hysterisis in returning from the out of lock condition. LOL will be de-asserted (indicating a lock condition) when the frequency difference is less than ±300 PPM.

LOL is wired to a test point which is located on the

upper right-hand side of the evaluation board.

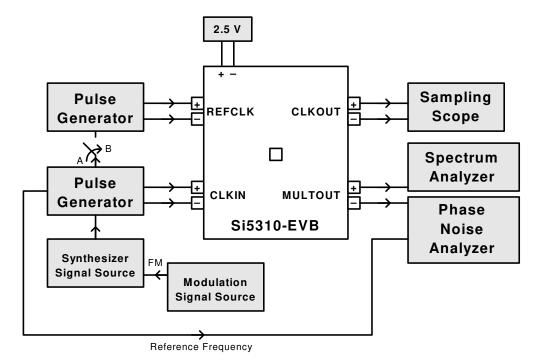

## **Test Configuration**

The characterization of clock sources typically involves measuring the output jitter or phase noise of the source. The overall output jitter is a function of the input jitter (jitter transfer) and the jitter generated (output jitter) by the internal PLL.

Jitter can be measured using several different techniques and hardware. An oscilloscope, a spectrum analyzer, and a phase-noise analyzer are three such instruments capable of measuring output jitter. A spectrum analyzer is the best choice for measuring jitter transfer.

#### **Output Jitter**

Output jitter is a measure of the output clock short-term stability. In Figure 2, either position A or B can be used when measuring this parameter.

## Oscilloscope

An oscilloscope can measure jitter from the clock edges within the trigger-to-capture bandwidth. Typically the jitter measured is expressed in picoseconds (peak-topeak and RMS) relative to the average edge position. A histogram can be used to capture the jitter distribution.

#### Spectrum Analyzer

A spectrum analyzer measures the power of the carrier source and its associated phase noise. Analysis of the offset power distribution provides the data from which jitter can be derived. Simple integration of the offset power distribution over the desired offset range and filtered amplitudes provides a RMS jitter value.

#### Phase-noise Analyzer

A phase-noise analyzer behaves similarly to a spectrum analyzer, but only provides details regarding the power offset from the carrier. Simple integration of the offset power distribution over the desired offset range and filtered amplitudes provides a RMS jitter value.

#### Jitter Transfer

Jitter transfer is the ratio of the input jitter spectrum to the output jitter spectrum. Comparing the power levels from the input jitter spectrum with the output jitter spectrum provides the jitter transfer details. To characterize this parameter, a modulation source is added to the synthesizer. The FM modulation frequency is the jitter frequency, and its relative amplitude on the output verses the input describes the amount transferred. In Figure 2, position A should be used when measuring this parameter.

Figure 2. Test Configuration for Jitter Tolerance, Transfer, and Generation

Figure 3. Si5310-EVB Schematic

S15310-EVB

Rev. 0.71

## **Bill of Materials**

| Si5310EVB Assy Rev    | / C-01 BOM                     |                            |                      |

|-----------------------|--------------------------------|----------------------------|----------------------|

| Reference             | Part Desc                      | Part Number                | Manufacturer         |

| C1,C2,C3,C4,C5,C6,    |                                |                            |                      |

| C7,C8                 | CAP, SM, 0.1uF, 0603           | C0603X7R160-104KNE         | Venkel               |

| C12                   | CAP, SM, 10 uF, TANTALUM, 3216 | TA010TCM106KAR             | Venkel               |

| C13,C15,C16           | CAP, SM, 100 pF, 16V, 0603     | C0603C0G500101KNE          | Venkel               |

| JP1,JP4               | CONNECTOR, HEADER, 2X1         | 2340-6111TN or 2380-6121TN | 3M                   |

| JP2                   | CONNECTOR, HEADER, 3X1         | 2340-6111TN or 2380-6121TN | 3M                   |

| J1,J2,J3,J4,J5,J6,J7, |                                |                            |                      |

| J8                    | CONNECTOR, SMA, SIDE MOUNT     | 901-10003                  | Amphenol             |

| J9                    | CONNECTOR, POWER, 2 POS        | 1729018                    | Phoenix Contact      |

| L1                    | RESISTOR, SM, 0 OHM, 1206      | CR1206-8W-000T             | Venkel               |

| R1                    | RESISTOR, SM, 10K, 1%, 0603    | CR0603-16W-1002FT          | Venkel               |

| R2                    | RESISTOR, SM, 2.55K, 1%, 0603  | CR0603-16W-2551FT          | Venkel               |

| U4                    | MAX6376XR23-T                  | MAX6376XR23-T              | Maxim                |

| U5                    | Si5310                         | SI5310-BM                  | Silicon Laboratories |

| PCB                   | PRINTED CIRCUIT BOARD          | Si5310-EVB PCB Rev C       | Silicon Laboratories |

| No Load               |                                |                            |                      |

| C9                    | SPARE,0805                     |                            |                      |

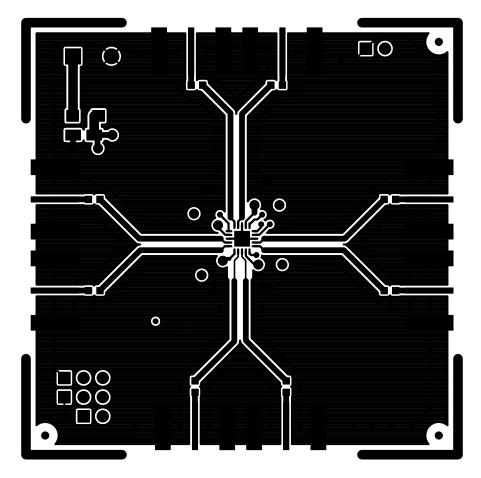

Figure 5. Si5310 Component Side

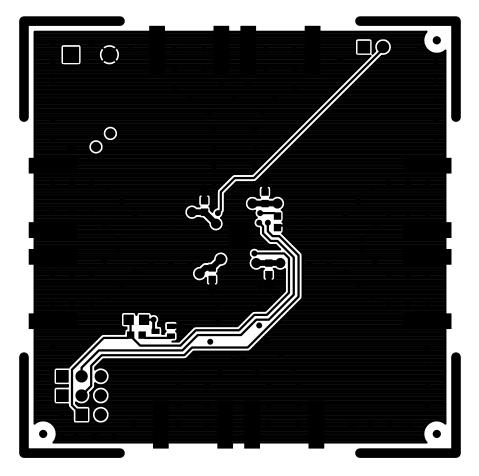

Figure 6. Si5310 Solder Side

## **Document Change List**

## Revision 0.7 to Revision 0.71

Added bill of materials.

## **Evaluation Board Assembly Revision History**

| Assembly Level | РСВ | Si5310 Device | Assembly Notes             |

|----------------|-----|---------------|----------------------------|

| B-01           | В   | В             | Assemble per BOM rev B-01. |

| C-01           | С   | С             | Assemble per BOM rev C-01. |

Notes:

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products not be used in weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com