Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# LOW-JITTER, 10-OUTPUT, ANY-FREQUENCY, ANY-OUTPUT CLOCK GENERATOR

#### **Features**

- Generates up to 10 independent output clocks

- Ultra-low jitter: <100 fs RMS typical

- MultiSynth<sup>™</sup> technology enables anyfrequency synthesis on any-output

- Highly configurable outputs compatible with LVDS, LVPECL, CML, ■ LVCMOS, HCSL, or programmable voltage

- Input frequency range:

- External crystal: 25, 48-54 MHz

- Differential clock: 10 to 750 MHz

- LVCMOS clock: 10 to 250 MHz

- Output frequency range:

- Differential: 100 Hz to 712.5 MHz

- LVCMOS: 100 Hz to 250 MHz

- Output-output skew: 20 ps typ

- Adjustable output-output delayOptional zero delay mode

- Independent glitchless on-the-fly output frequency changes

- DCO mode with frequency steps as low as 0.001 ppb

- Independent output clock supply pins: 3.3 V, 2.5 V, or 1.8 V

- Built-in power supply filtering and regulation

- Status monitoring: LOS, LOL

- Serial Interface: I<sup>2</sup>C or SPI (3-wire or 4-wire)

- User programmable (2x) non-volatile OTP memory

- ClockBuilder<sup>TM</sup> Pro software utility simplifies device configuration and assigns customer part numbers

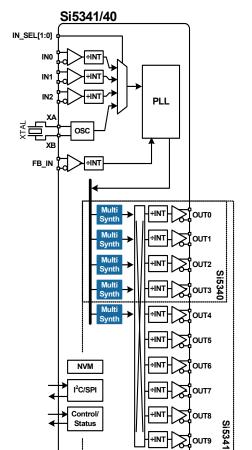

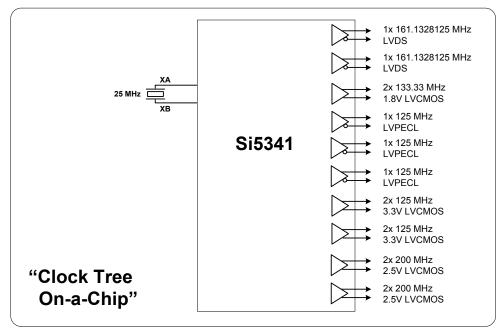

- Si5341: 4 input, 10 output, compact 9x9 mm, 64 QFN

- Si5340: 4 input, 4 output, compact 7x7 mm, 44 QFN

- Temperature range: -40 to +85 °C

- Pb-free, RoHS-6 compliant

# 9x9 mm 7x7 mm Ordering Information See Section 8.

#### **Functional Block Diagram**

#### **Device Selector Guide**

| Grade   | Max Output Frequency | Frequency Synthesis Mode |

|---------|----------------------|--------------------------|

| Si534xA | 712.5 MHz            | Integer + Fractional     |

| Si534xB | 350 MHz              | integer i i ractional    |

| Si534xC | 712.5 MHz            | Integer Only             |

| Si534xD | 350 MHz              | integer Only             |

#### **Applications**

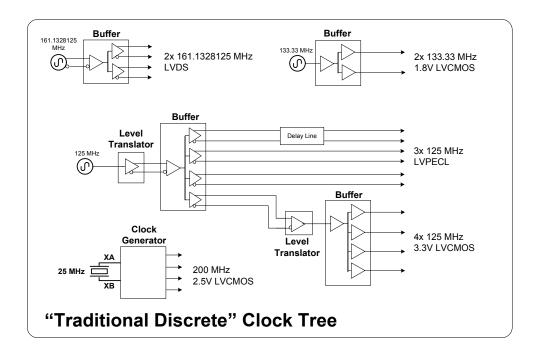

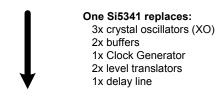

- Clock tree generation replacing XOs, buffers, signal format translators

- Any-frequency clock translation

- Clocking for FPGAs, processors, memory

- Ethernet switches/routers

- OTN framers/mappers/processors

- Test equipment & instrumentation

- Broadcast video

#### **Description**

The any-frequency, any-output Si5341/40 clock generators combine a wide-band PLL with proprietary MultiSynth fractional synthesizer technology to offer a versatile and high performance clock generator platform. This highly flexible architecture is capable of synthesizing a wide range of integer and non-integer related frequencies up to 712.5 MHz on 10 differential clock outputs while delivering sub-100 fs rms phase jitter performance with 0 ppm error. Each of the clock outputs can be assigned its own format and output voltage enabling the Si5341/40 to replace multiple clock ICs and oscillators with a single device making it a true "clock tree on a chip".

The Si5341/40 can be quickly and easily configured using ClockBuilder Pro software. Custom part numbers are automatically assigned using a ClockBuilder Pro for fast, free, and easy factory pre-programming, or the Si5341/40 can be programmed incircuit via I<sup>2</sup>C and SPI serial interfaces.

2

# TABLE OF CONTENTS

| 1. Typical Application Schematic                                                      | 4    |

|---------------------------------------------------------------------------------------|------|

| 2. Electrical Specifications                                                          | 5    |

| 3. Typical Operating Characteristics                                                  | 23   |

| 4. Detailed Block Diagrams                                                            | 26   |

| 5. Functional Description                                                             |      |

| 5.1. Power-up and Initialization                                                      | 28   |

| 5.2. Frequency Configuration                                                          | 29   |

| 5.3. Inputs                                                                           | . 29 |

| 5.4. Fault Monitoring                                                                 | 31   |

| 5.5. Outputs                                                                          | 32   |

| 5.6. Power Management                                                                 | 37   |

| 5.7. In-Circuit Programming                                                           | 37   |

| 5.8. Serial Interface                                                                 | 37   |

| 5.9. Custom Factory Preprogrammed Devices                                             | 37   |

| 5.10. Enabling Features and/or Configuration Settings Not Available in ClockBuilder P |      |

| for Factory Pre-programmed Devices                                                    | 38   |

| 6. Register Map                                                                       | 39   |

| 6.1. Addressing Scheme                                                                |      |

| 6.2. High-Level Register Map                                                          | 39   |

| 7. Pin Descriptions                                                                   | 41   |

| 8. Ordering Guide                                                                     |      |

| 9. Package Outlines                                                                   | 49   |

| 9.1. Si5341 9x9 mm 64-QFN Package Diagram                                             |      |

| 9.2. Si5340 7x7 mm 44-QFN Package Diagram                                             |      |

| 10. PCB Land Pattern                                                                  | 51   |

| 11. Top Marking                                                                       |      |

| 12. Device Errata                                                                     |      |

| Document Change List                                                                  |      |

| Contact Information                                                                   | 56   |

### 1. Typical Application Schematic

Figure 1. Using The Si5341 to Replace a Traditional Clock Tree

SILICON LARS

## 2. Electrical Specifications

**Table 1. Recommended Operating Conditions**

$(V_{DD} = 1.8 \text{ V } \pm 5\%, V_{DDA} = 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                    | Symbol            | Min  | Тур  | Max  | Units |

|------------------------------|-------------------|------|------|------|-------|

| Ambient Temperature          | T <sub>A</sub>    | -40  | 25   | 85   | °C    |

| Junction Temperature         | TJ <sub>MAX</sub> | _    | _    | 125  | °C    |

| Core Supply Voltage          | V <sub>DD</sub>   | 1.71 | 1.80 | 1.89 | V     |

|                              | V <sub>DDA</sub>  | 3.14 | 3.30 | 3.47 | V     |

| Output Driver Supply Voltage | $V_{DDO}$         | 3.14 | 3.30 | 3.47 | V     |

|                              |                   | 2.38 | 2.50 | 2.62 | V     |

|                              |                   | 1.71 | 1.80 | 1.89 | V     |

\*Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise noted.

#### **Table 2. DC Characteristics**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDO} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_{A} = -40 \text{ to } 85 \text{ °C})$

| Parameter                    | Symbol            | Test Co                                          | ndition                 | Min | Тур | Max | Units |

|------------------------------|-------------------|--------------------------------------------------|-------------------------|-----|-----|-----|-------|

| Core Supply Current          | I <sub>DD</sub>   | Si5341                                           | Note <sup>1</sup>       | _   | 100 | 150 | mA    |

|                              |                   | Si5340                                           | Note <sup>2</sup>       | _   | 85  | 130 | mA    |

|                              | I <sub>DDA</sub>  | Si5341                                           | Note <sup>1</sup>       | _   | 115 | 125 | mA    |

|                              |                   | Si5340                                           | Note <sup>2</sup>       | _   | 115 | 125 | mA    |

| Output Buffer Supply Current | I <sub>DDOx</sub> | LVPECL                                           | Output <sup>3</sup>     | _   | 21  | 25  | mA    |

|                              |                   | @ 156.                                           | 56.25 MHz               |     |     |     |       |

|                              |                   | LVDS Output <sup>3</sup>                         |                         | _   | 15  | 18  | mA    |

|                              |                   | @ 156.                                           | 25 MHz                  |     |     |     |       |

|                              |                   | 3.3 V LVCM                                       | 10S <sup>4</sup> output | _   | 21  | 25  | mA    |

|                              |                   | @ 156.                                           | 25 MHz                  |     |     |     |       |

|                              |                   | 2.5 V LVCM                                       | 10S <sup>4</sup> output | _   | 16  | 18  | mA    |

|                              |                   | @ 156.                                           | @ 156.25 MHz            |     |     |     |       |

|                              |                   | 1.8 V LVCMOS <sup>4</sup> output<br>@ 156.25 MHz |                         | _   | 12  | 13  | mA    |

|                              |                   |                                                  |                         |     |     |     |       |

| Total Power Dissipation      | P <sub>d</sub>    | Si5341                                           | Notes 1,5               | _   | 830 | 980 | mW    |

|                              |                   | Si5340                                           | Notes <sup>2,5</sup>    |     | 685 | 815 | mW    |

#### Notes:

6

- 1. Si5341 test configuration: 7 x 2.5 V LVDS outputs enabled @156.25 MHz. Excludes power in termination resistors.

- 2. Si5340 test configuration: 4 x 2.5 V LVDS outputs enabled @ 156.25 MHz. Excludes power in termination resistors.

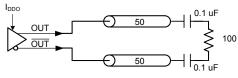

- 3. Differential outputs terminated into an ac-coupled 100  $\Omega$  load.

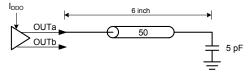

- **4.** LVCMOS outputs measured into a 6-inch 50 Ω PCB trace with 5 pF load. The LVCMOS outputs were set to OUTx\_CMOS\_DRV=3, which is the strongest driver setting. Refer to the Si5341/40 Family Reference Manual for more details on register settings.

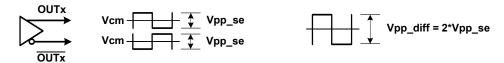

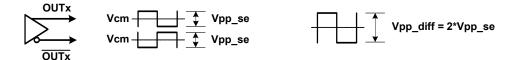

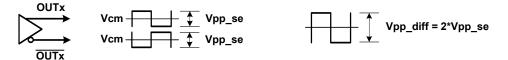

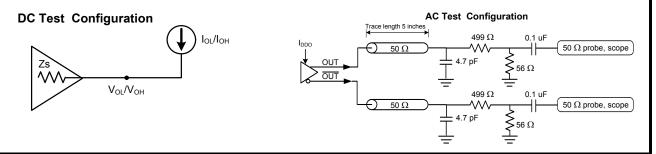

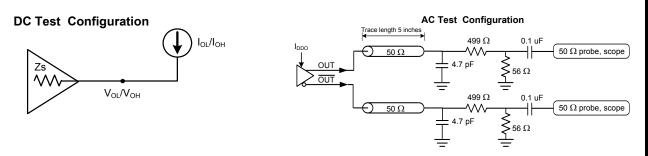

#### **Differential Output Test Configuration**

#### **LVCMOS Output Test Configuration**

**5.** Detailed power consumption for any configuration can be estimated using ClockBuilderPro when an evaluation board (EVB) is not available. All EVBs support detailed current measurements for any configuration.

#### **Table 3. Input Specifications**

$(V_{DD} = 1.8 \text{ V } \pm 5\%, V_{DDA} = 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                        | Symbol             | Test Condition                                     | Min        | Тур       | Max      | Units   |

|----------------------------------|--------------------|----------------------------------------------------|------------|-----------|----------|---------|

| Differential or Single-Ended/LVC | MOS — A            | C-Coupled (IN0/IN0, IN1/IN                         | 11, IN2/IN | N2, FB_II | N/FB_IN) |         |

| Input Frequency Range            | f <sub>IN</sub>    | Differential                                       | 10         | _         | 750      | MHz     |

|                                  |                    | Single-ended/LVCMOS                                | 10         | _         | 250      |         |

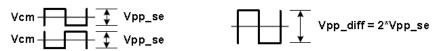

| Input Voltage Swing <sup>5</sup> | V <sub>IN</sub>    | Differential AC Coupled<br>fin < 250 MHz           | 100        | _         | 1800     | mVpp_se |

|                                  |                    | Differential AC Coupled<br>250 MHz < fin < 750 MHz | 225        | _         | 1800     | mVpp_se |

|                                  |                    | Single-ended AC Coupled fin < 250 MHz              | 100        | _         | 3600     | mVpp_se |

| Slew Rate <sup>1, 2</sup>        | SR                 |                                                    | 400        | _         | _        | V/µs    |

| Duty Cycle                       | DC                 |                                                    | 40         | _         | 60       | %       |

| Capacitance                      | C <sub>IN</sub>    |                                                    | _          | 2         | _        | pF      |

| DC-Coupled CMOS Input Buffer     | (IN0, IN1,         | IN2) <sup>4</sup>                                  |            |           |          |         |

| Input Frequency                  | f <sub>IN</sub>    |                                                    | 10         | _         | 250      | MHz     |

| Input Voltage                    | V <sub>IL</sub>    |                                                    | -0.2       | _         | 0.33     | V       |

|                                  | V <sub>IH</sub>    |                                                    | 0.49       | _         | _        | V       |

| Slew Rate <sup>1, 2</sup>        | SR                 |                                                    | 400        | _         | _        | V/µs    |

| Duty Cycle                       | DC                 | Clock Input                                        | 40         | _         | 60       | %       |

| Minimum Pulse Width              | PW                 | Pulse Input                                        | 1.6        | _         | _        | ns      |

| Input Resistance                 | R <sub>IN</sub>    |                                                    | _          | 8         | _        | kΩ      |

| Differential or Single-Ended/LVC | MOS Clo            | ck at XA/XB                                        |            |           |          | ,       |

| Input Frequency Range            | f <sub>IN</sub>    | Frequency range for best output jitter performance | 48         | _         | 200      | MHz     |

|                                  |                    |                                                    | 10         | _         | 200      | MHz     |

| Input Single-ended Voltage Swing | V <sub>IN_SE</sub> |                                                    | 365        | _         | 2000     | mVpp_se |

#### Notes:

- 1. Imposed for jitter performance.

- 2. Rise and fall times can be estimated using the following simplified equation:  $tr/tf_{80-20} = ((0.8 0.2) * V_{IN\_Vpp\_se}) / SR$ .

- 3.  $V_{DDIO}$  is determined by the IO\_VDD\_SEL bit. It is selectable as  $V_{DDA}$  or  $V_{DD}$ .

- **4.** DC-coupled CMOS Input Buffer selection is not supported in ClockBuilder Pro for new designs. For single-ended LVCMOS inputs to IN0,1,2 it is required to ac-couple into the differential input buffer.

- **5.** Voltage swing is specified as single-ended mVpp.

6. Contact Silicon Labs Technical Support for more details.

#### **Table 3. Input Specifications**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                        | Symbol               | Test Condition                           | Min | Тур | Max  | Units     |

|----------------------------------|----------------------|------------------------------------------|-----|-----|------|-----------|

| Input Differential Voltage Swing | V <sub>IN_DIFF</sub> |                                          | 365 | _   | 2500 | mVpp_diff |

| Slew rate <sup>1, 2</sup>        | SR                   | Imposed for best jitter per-<br>formance | 400 | _   | _    | V/µs      |

| Input Duty Cycle                 | DC                   |                                          | 40  | _   | 60   | %         |

#### Notes:

- 1. Imposed for jitter performance.

- 2. Rise and fall times can be estimated using the following simplified equation:  $tr/tf_{80-20} = ((0.8 0.2) * V_{IN\_Vpp\_se}) / SR$ .

- 3.  $V_{DDIO}$  is determined by the IO\_VDD\_SEL bit. It is selectable as  $V_{DDA}$  or  $V_{DD}$ .

- **4.** DC-coupled CMOS Input Buffer selection is not supported in ClockBuilder Pro for new designs. For single-ended LVCMOS inputs to IN0,1,2 it is required to ac-couple into the differential input buffer.

- 5. Voltage swing is specified as single-ended mVpp.

6. Contact Silicon Labs Technical Support for more details.

#### **Table 4. Control Input Pin Specifications**

$(V_{DD}$  = 1.8 V ±5%,  $V_{DDA}$  = 3.3 V ±5%,  $V_{DDS}$  = 3.3 V ±5%, 1.8 V ±5%,  $T_A$  = -40 to 85 °C)

| Parameter                                                                                                      | Symbol          | Test Condition                     | Min                         | Тур        | Max                     | Units       |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------|-----------------------------|------------|-------------------------|-------------|--|--|--|--|--|

| Si5341 Control Input Pi <u>ns</u> (I2C_SEL, IN_SEL[1:0], RST, OE, SYNC, A1, SCLK, A0/CS, FINC, FDEC, SDA/SDIO) |                 |                                    |                             |            |                         |             |  |  |  |  |  |

| Input Voltage                                                                                                  | V <sub>IL</sub> |                                    | _                           | _          | 0.3xV <sub>DDIO</sub> * | V           |  |  |  |  |  |

|                                                                                                                | V <sub>IH</sub> |                                    | 0.7xV <sub>DDIO</sub> *     | _          | _                       | V           |  |  |  |  |  |

| Input Capacitance                                                                                              | C <sub>IN</sub> |                                    | _                           | 2          | _                       | pF          |  |  |  |  |  |

| Input Resistance                                                                                               | R <sub>IN</sub> |                                    | _                           | 20         | _                       | kΩ          |  |  |  |  |  |

| Minimum Pulse Width                                                                                            | T <sub>PW</sub> | RST, SYNC,<br>FINC, and FDEC       | 100                         | _          | _                       | ns          |  |  |  |  |  |

| Frequency Update Rate                                                                                          | F <sub>UR</sub> | FINC and FDEC                      | _                           | _          | 1                       | MHz         |  |  |  |  |  |

| Si5340 Control Input Pins (I2C_SEL                                                                             | ., IN_SEL[1     | :0], RST, OE, A1,                  | SDA, SDI, SC                | LK, A0/    | CS, SDA/SDI             | O)          |  |  |  |  |  |

| Input Voltage                                                                                                  | $V_{IL}$        |                                    | _                           | _          | 0.3xV <sub>DDIO</sub> * | V           |  |  |  |  |  |

|                                                                                                                | V <sub>IH</sub> |                                    | 0.7xV <sub>DDIO</sub> *     | _          | _                       | V           |  |  |  |  |  |

| Input Capacitance                                                                                              | C <sub>IN</sub> |                                    | _                           | 2          | _                       | pF          |  |  |  |  |  |

| Input Resistance                                                                                               | R <sub>IN</sub> |                                    | _                           | 20         | _                       | kΩ          |  |  |  |  |  |

| Minimum Pulse Width                                                                                            | T <sub>PW</sub> | RST only                           | 100                         | _          | _                       | ns          |  |  |  |  |  |

| *Note: V <sub>DDIO</sub> is determined by the IO_VD                                                            | D_SEL bit. I    | t is selectable as V <sub>DD</sub> | A or V <sub>DD</sub> . Refe | r to the R | eference Manu           | al for more |  |  |  |  |  |

8 Rev. 1.0

details on register settings.

#### **Table 5. Differential Clock Output Specifications**

$(V_{DD} = 1.8 \ \ V \ \pm 5\%, \ V_{DDA} = 3.3 \ \ V \ \pm 5\%, \ V_{DDO} = 1.8 \ \ V \ \pm 5\%, \ 2.5 \ \ V \ \pm 5\%, \ or \ 3.3 \ \ V \ \pm 5\%, \ T_A = -40 \ to \ 85 \ ^{\circ}C)$

| Parameter                        | Symbol              | Test Coi                                           | ndition  | Min    | Тур | Max   | Units   |  |

|----------------------------------|---------------------|----------------------------------------------------|----------|--------|-----|-------|---------|--|

| Output Frequency                 | f <sub>OUT</sub>    |                                                    |          |        | _   | 712.5 | MHz     |  |

| Duty Cycle                       | DC                  | f <sub>OUT</sub> < 40                              | 00 MHz   | 48     | _   | 52    | %       |  |

|                                  |                     | 400 MHz < f <sub>OUT</sub> <<br>712.5 MHz          |          | 45     | _   | 55    | %       |  |

| Output-Output Skew               | T <sub>SK</sub>     | Outputs on san<br>Normal                           |          | _      | 20  | 50    | ps      |  |

|                                  |                     | Outputs on same Multisynth, Pow Power Mode         |          | _      | 20  | 100   | ps      |  |

| OUT-OUT Skew                     | T <sub>SK_OUT</sub> | Measured from the positive to negative output pins |          | _      | 0   | 100   | ps      |  |

| Output Amplitude <sup>1, 5</sup> |                     |                                                    | Normal I | /lode  |     |       |         |  |

|                                  | V <sub>OUT</sub>    | V <sub>DDO</sub> = 3.3 V,<br>2.5 V, or 1.8 V       | LVDS     | 350    | 470 | 550   | mVpp_se |  |

|                                  |                     | V <sub>DDO</sub> = 3.3 V<br>or 2.5 V               | LVPECL   | 660    | 810 | 1000  |         |  |

|                                  |                     |                                                    | Low Powe | r Mode |     |       |         |  |

|                                  | V <sub>OUT</sub>    | V <sub>DDO</sub> = 3.3 V,<br>2.5 V, or 1.8 V       | LVDS     | 300    | 420 | 530   | mVpp_se |  |

|                                  |                     | V <sub>DDO</sub> = 3.3 V<br>or 2.5 V               | LVPECL   | 620    | 820 | 1060  |         |  |

#### Notes:

- 1. The typical normal mode (or low power mode) LVDS maximum is 100 mV (or 80 mV) higher than the TIA/EIA-644 maximum. For normal and low-power modes, the amplitudes are programmable through register settings and can be stored in NVM. Each output driver can be programmed independently. See Appendix A of the Si5341/40 Reference Manual.

- 2. Driver output impedance depends on selected output mode (Normal, Low Power).

- 3. Measured for 156.25 MHz carrier frequency. Sinewave noise added to VDDO (1.8 V = 50 mVpp, 2.5 V/ 3.3 V = 100 mVpp) and noise spur amplitude measured.

- **4.** Measured across two adjacent outputs, both in LVDS mode, with the victim running at 155.52 MHz and the aggressor at 156.25 MHz. Refer to application note, "AN862: Optimizing Si534x Jitter Performance in Next Generation Internet Infrastructure Systems", guidance on crosstalk minimization.

- **5.** For other amplitudes see Appendix A of the Si5341/40 Reference Manual.

- **6.** See Note 4, but in this case the measurement is across two output clocks that have a single clock between them.

- 7. Same as Note 4, but the Si5340 has less crosstalk due to the spacing of adjacent outputs.

#### **Table 5. Differential Clock Output Specifications (Continued)**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDO} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                                  | Symbol                                            | Test Co                        | ndition        | Min     | Тур         | Max  | Units |  |

|--------------------------------------------|---------------------------------------------------|--------------------------------|----------------|---------|-------------|------|-------|--|

| Common Mode Voltage <sup>1</sup>           |                                                   | Normal Mode or Low Power Modes |                |         |             |      |       |  |

|                                            | $V_{CM}$                                          | V <sub>DDO</sub> = 3.3 V       | LVDS           | 1.10    | 1.25        | 1.35 | V     |  |

|                                            |                                                   |                                | LVPECL         | 1.90    | 2.05        | 2.15 |       |  |

|                                            |                                                   | V <sub>DDO</sub> = 2.5 V       | LVPECL<br>LVDS | 1.15    | 1.25        | 1.35 |       |  |

|                                            |                                                   | V <sub>DDO</sub> = 1.8 V       | Sub-LVDS       | 0.87    | 0.93        | 1.0  |       |  |

| Rise and Fall Times                        | t <sub>R</sub> /t <sub>F</sub>                    | Normal                         | Mode           | _       | 170         | 240  | ps    |  |

| (20% to 80%)                               |                                                   | Low Power Mode                 |                | _       | 300         | 430  |       |  |

| Differential Output Impedance <sup>2</sup> | Z <sub>O</sub>                                    | Normal Mode                    |                | _       | 100         | _    | Ω     |  |

|                                            |                                                   | Low Pow                        | er Mode        | _       | 650         |      | Ω     |  |

| Power Supply Noise Rejection <sup>3</sup>  | PSRR                                              |                                | No             | rmal Mo | de          | 1    |       |  |

|                                            |                                                   | 10 kHz sinusoidal noise        |                | _       | -93         | _    | dBc   |  |

|                                            |                                                   | 100 kHz sinusoidal noise       |                | _       | -93         | _    |       |  |

|                                            |                                                   | 500 kHz sinusoidal noise       |                | _       | -84         | _    |       |  |

|                                            |                                                   | 1 MHz sinusoidal noise         |                | _       | <b>–</b> 79 | _    |       |  |

|                                            |                                                   | Low Power Mode                 |                |         |             |      |       |  |

|                                            |                                                   | 10 kHz sinus                   | soidal noise   | _       | -98         | _    | dBc   |  |

|                                            | 100 kHz sinusoidal noise 500 kHz sinusoidal noise |                                | _              | -95     | _           |      |       |  |

|                                            |                                                   |                                | _              | -84     | _           |      |       |  |

|                                            |                                                   | 1 MHz sinusoidal noise         |                | _       | -76         | _    |       |  |

#### Notes:

- 1. The typical normal mode (or low power mode) LVDS maximum is 100 mV (or 80 mV) higher than the TIA/EIA-644 maximum. For normal and low-power modes, the amplitudes are programmable through register settings and can be stored in NVM. Each output driver can be programmed independently. See Appendix A of the Si5341/40 Reference Manual.

- 2. Driver output impedance depends on selected output mode (Normal, Low Power).

- 3. Measured for 156.25 MHz carrier frequency. Sinewave noise added to VDDO (1.8 V = 50 mVpp, 2.5 V/ 3.3 V = 100 mVpp) and noise spur amplitude measured.

- **4.** Measured across two adjacent outputs, both in LVDS mode, with the victim running at 155.52 MHz and the aggressor at 156.25 MHz. Refer to application note, "AN862: Optimizing Si534x Jitter Performance in Next Generation Internet Infrastructure Systems", guidance on crosstalk minimization.

- 5. For other amplitudes see Appendix A of the Si5341/40 Reference Manual.

- 6. See Note 4, but in this case the measurement is across two output clocks that have a single clock between them.

- 7. Same as Note 4, but the Si5340 has less crosstalk due to the spacing of adjacent outputs.

SILICON LARS

#### Table 5. Differential Clock Output Specifications (Continued)

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDO} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter               | Symbol | Test Condition |                   | Min | Тур         | Max | Units |

|-------------------------|--------|----------------|-------------------|-----|-------------|-----|-------|

| Output-Output Crosstalk | XTALK  | Si5341         | Note <sup>4</sup> | _   | <b>–</b> 75 | _   | dBc   |

|                         |        | Si5341         | Note <sup>6</sup> | _   | -85         | _   | dBc   |

|                         |        | Si5340         | Note <sup>7</sup> | _   | -85         | _   | dBc   |

#### Notes:

- The typical normal mode (or low power mode) LVDS maximum is 100 mV (or 80 mV) higher than the TIA/EIA-644

maximum. For normal and low-power modes, the amplitudes are programmable through register settings and can be

stored in NVM. Each output driver can be programmed independently. See Appendix A of the Si5341/40 Reference

Manual.

- 2. Driver output impedance depends on selected output mode (Normal, Low Power).

- 3. Measured for 156.25 MHz carrier frequency. Sinewave noise added to VDDO (1.8 V = 50 mVpp, 2.5 V/ 3.3 V = 100 mVpp) and noise spur amplitude measured.

- **4.** Measured across two adjacent outputs, both in LVDS mode, with the victim running at 155.52 MHz and the aggressor at 156.25 MHz. Refer to application note, "AN862: Optimizing Si534x Jitter Performance in Next Generation Internet Infrastructure Systems", guidance on crosstalk minimization.

- 5. For other amplitudes see Appendix A of the Si5341/40 Reference Manual.

- 6. See Note 4, but in this case the measurement is across two output clocks that have a single clock between them.

- 7. Same as Note 4, but the Si5340 has less crosstalk due to the spacing of adjacent outputs.

#### **Table 6. Output Status Pin Specifications**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDS} = 3.3 \text{ V} \pm 5\%, 1.8 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                          | Symbol          | <b>Test Condition</b>   | Min                            | Тур | Max                                   | Units |  |  |  |

|--------------------------------------------------------------------|-----------------|-------------------------|--------------------------------|-----|---------------------------------------|-------|--|--|--|

| Si5341 Status Output Pins (LOL, INTR), SDA/SDIO <sup>2</sup> , SDO |                 |                         |                                |     |                                       |       |  |  |  |

| Output Voltage                                                     | V <sub>OH</sub> | I <sub>OH</sub> = -2 mA | $V_{\rm DDIO}^{1} \times 0.75$ | _   | _                                     | V     |  |  |  |

|                                                                    | V <sub>OL</sub> | I <sub>OL</sub> = 2 mA  | _                              | _   | V <sub>DDIO</sub> <sup>1</sup> x 0.15 | V     |  |  |  |

| Si5340 Status Output Pins (INT                                     | R), LOL, L      | OS_XAXB, SDA            | SDIO <sup>2</sup> , SDO        |     |                                       |       |  |  |  |

| Output Voltage                                                     | V <sub>OH</sub> | I <sub>OH</sub> = -2 mA | $V_{\rm DDIO}^{1} \times 0.75$ | _   | _                                     | V     |  |  |  |

|                                                                    | V <sub>OL</sub> | I <sub>OL</sub> = 2 mA  | _                              | _   | V <sub>DDIO</sub> <sup>1</sup> x 0.15 | V     |  |  |  |

#### Notes:

- V<sub>DDIO</sub> is determined by the IO\_VDD\_SEL bit. It is selectable as V<sub>DDA</sub> or V<sub>DD</sub>. Refer to the Reference Manual for more details on register settings.

- 2. The V<sub>OH</sub> specification does not apply to the open-drain SDA/SDIO output when the serial interface is in I2C mode or is unused with I2C\_SEL pulled high. V<sub>OI</sub> remains valid in all cases.

#### **Table 7. LVCMOS Clock Output Specifications**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDO} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                              | Symbol          | Test Conditi                 | on                        | Min                | Тур  | Max  | Units |   |   |  |

|----------------------------------------|-----------------|------------------------------|---------------------------|--------------------|------|------|-------|---|---|--|

| Output Frequency                       |                 |                              |                           | 0.0001             | _    | 250  | MHz   |   |   |  |

| Duty Cycle                             | DC              | f <sub>OUT</sub> < 100 M     | 47                        | _                  | 53   | %    |       |   |   |  |

|                                        |                 | 100 MHz < f <sub>OUT</sub> < | 44                        | _                  | 55   |      |       |   |   |  |

| Output-to-Output Skew                  | T <sub>SK</sub> |                              | _                         | _                  | 100  | ps   |       |   |   |  |

| Output Voltage High <sup>1, 2, 3</sup> | V <sub>OH</sub> |                              | V <sub>DDO</sub> = 3.3 V  |                    |      |      |       |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=1              | I <sub>OH =</sub> –10 mA  | V <sub>DDO</sub> x | _    | _    | V     |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=2              | I <sub>OH =</sub> –12 mA  | 0.75               | 0.75 | _    | _     |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=3              | $I_{OH} = -17 \text{ mA}$ |                    | _    | _    |       |   |   |  |

|                                        |                 |                              | V <sub>DDO</sub> = 2.5 V  |                    |      |      |       |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=1              | $I_{OH} = -6 \text{ mA}$  | V <sub>DDO</sub> x | _    | _    | V     |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=2              | I <sub>OH =</sub> –8 mA   | 0.75               | 0.75 | 0.75 | 0.75  | _ | _ |  |

|                                        |                 | OUTx_CMOS_DRV=3              | I <sub>OH =</sub> –11 mA  |                    | _    | _    |       |   |   |  |

|                                        |                 |                              | V <sub>DDO</sub> = 1.8 V  |                    |      |      |       |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=2              | $I_{OH} = -4 \text{ mA}$  | V <sub>DDO</sub> x | _    | _    | V     |   |   |  |

|                                        |                 | OUTx_CMOS_DRV=3              | $I_{OH} = -5 \text{ mA}$  | 0.75               | _    | _    | V     |   |   |  |

#### Notes:

- 1. Driver strength is a register programmable setting and stored in NVM. Options are OUTx\_CMOS\_DRV = 1, 2, 3. Refer to the Reference Manual for more details on register settings.

- 2.  $I_{OL}/I_{OH}$  is measured at  $V_{OL}/V_{OH}$  as shown in the dc test configuration.

- 3. A series termination resistor (Rs) is recommended to help match the source impedance to a 50  $\Omega$  PCB trace. A 5 pF capacitive load is assumed. The LVCMOS outputs were set to OUTx\_CMOS\_DRV = 3.

#### **Table 7. LVCMOS Clock Output Specifications (Continued)**

$(V_{DD} = 1.8 \text{ V} \pm 5\%, V_{DDA} = 3.3 \text{ V} \pm 5\%, V_{DDO} = 1.8 \text{ V} \pm 5\%, 2.5 \text{ V} \pm 5\%, \text{ or } 3.3 \text{ V} \pm 5\%, T_{A} = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                  | Symbol          | Test Conditi             | on                      | Min | Тур | Max       | Units |  |

|------------------------------------------------------------|-----------------|--------------------------|-------------------------|-----|-----|-----------|-------|--|

| Output Voltage Low <sup>1, 2, 3</sup>                      | V <sub>OL</sub> | V <sub>DDO</sub> = 3.3 V |                         |     |     |           |       |  |

|                                                            |                 | OUTx_CMOS_DRV=1          | I <sub>OL</sub> = 10 mA | _   | _   | $V_{DDO}$ | V     |  |

|                                                            |                 | OUTx_CMOS_DRV=2          | I <sub>OL</sub> = 12 mA | _   | _   | x 0.15    |       |  |

|                                                            |                 | OUTx_CMOS_DRV=3          | I <sub>OL</sub> = 17 mA |     | _   |           |       |  |

|                                                            |                 | V <sub>DDO</sub> = 2.5 V |                         |     |     |           |       |  |

|                                                            |                 | OUTx_CMOS_DRV=1          | I <sub>OL</sub> = 6 mA  | _   | _   | $V_{DDO}$ | V     |  |

|                                                            |                 | OUTx_CMOS_DRV=2          | I <sub>OL</sub> = 8 mA  | _   | _   | x 0.15    |       |  |

|                                                            |                 | OUTx_CMOS_DRV=3          | I <sub>OL</sub> = 11 mA | _   | _   |           |       |  |

|                                                            |                 | V <sub>DDO</sub> = 1.8 V |                         |     |     |           |       |  |

|                                                            |                 | OUTx_CMOS_DRV=2          | I <sub>OL</sub> = 4 mA  | _   | _   | $V_{DDO}$ | V     |  |

|                                                            |                 | OUTx_CMOS_DRV=3          | I <sub>OL</sub> = 5 mA  | _   | _   | x 0.15    |       |  |

| LVCMOS Rise and Fall<br>Times <sup>3</sup><br>(20% to 80%) | tr/tf           | VDDO = 3.3               | _                       | 420 | 550 | ps        |       |  |

|                                                            |                 | VDDO = 2.5 V             |                         | _   | 475 | 625       | ps    |  |

| (                                                          |                 | VDDO = 1.8               | _                       | 525 | 705 | ps        |       |  |

#### Notes:

- 1. Driver strength is a register programmable setting and stored in NVM. Options are OUTx\_CMOS\_DRV = 1, 2, 3. Refer to the Reference Manual for more details on register settings.

- 2.  $I_{OL}/I_{OH}$  is measured at  $V_{OL}/V_{OH}$  as shown in the dc test configuration.

- 3. A series termination resistor (Rs) is recommended to help match the source impedance to a 50  $\Omega$  PCB trace. A 5 pF capacitive load is assumed. The LVCMOS outputs were set to OUTx\_CMOS\_DRV = 3.

#### **Table 8. Performance Characteristics**

(V<sub>DD</sub> = 1.8 V  $\pm$ 5%, V<sub>DDA</sub> = 3.3 V  $\pm$ 5%, T<sub>A</sub> = -40 to 85 °C)

| Parameter                                                  | Symbol                                                                                                                            | Test Condition                                                                    | Min  | Тур   | Max    | Units    |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|-------|--------|----------|

| V <sub>CO</sub> Frequency Range                            | F <sub>VCO</sub>                                                                                                                  |                                                                                   | 13.5 | _     | 14.256 | GHz      |

| PLL Loop Bandwidth                                         | f <sub>BW</sub>                                                                                                                   |                                                                                   | _    | 1.0   | _      | MHz      |

| Initial Start-Up Time                                      | t <sub>START</sub>                                                                                                                | Time from power-up to when the device generates clocks (Input Frequency > 48 MHz) |      | 30    | 45     | ms       |

| POR <sup>1</sup> to Serial Interface<br>Ready              | t <sub>RDY</sub>                                                                                                                  |                                                                                   | _    | _     | 15     | ms       |

| PLL Lock Time <sup>6</sup>                                 | t <sub>ACQ</sub>                                                                                                                  | f <sub>IN</sub> = 19.44 MHz                                                       | 22   | _     | 180    | ms       |

| Output Delay Adjustment                                    | t <sub>DELAY_</sub> -                                                                                                             | f <sub>VCO</sub> = 14 GHz<br>Delay is controlled by the Multi-                    | _    | 0.28  | _      | ps       |

|                                                            | t <sub>DELAY_int</sub>                                                                                                            | Synth                                                                             | _    | 71.4  | _      | ps       |

|                                                            | t <sub>RANGE</sub>                                                                                                                |                                                                                   | _    | ±9.14 | _      | ns       |

| Jitter Generation<br>Locked to External Clock <sup>2</sup> | J <sub>GEN</sub>                                                                                                                  | Integer Mode <sup>3</sup><br>12 kHz to 20 MHz                                     | _    | 0.135 | 0.175  | ps RMS   |

|                                                            |                                                                                                                                   | Fractional/DCO Mode <sup>4</sup><br>12 kHz to 20 MHz                              | _    | 0.160 | 0.205  | ps RMS   |

|                                                            | J <sub>PER</sub>                                                                                                                  | Derived from                                                                      | _    | 0.140 | _      | ps pk-pk |

|                                                            | J <sub>CC</sub>                                                                                                                   | integrated phase noise                                                            |      | 0.250 | _      | ps pk    |

|                                                            | J <sub>PER</sub>                                                                                                                  | N = 10,000 cycles                                                                 | _    | 7.3   | _      | ps pk-pk |

|                                                            | JCC Integer or Fractional Mode <sup>3</sup> Measured in the time doma Performance is limited by the noise floor of the equipment. |                                                                                   |      | 8.1   | _      | ps pk    |

#### Notes:

- 1. Measured as time from valid  $V_{DD}$  and  $V_{DD33}$  rails (90% of their value) to when the serial interface is ready to respond to commands. Measured in SPI 4-wire mode, with SCLK @ 10 MHz.

- Jitter generation test conditions f<sub>IN</sub> = 100 MHz, f<sub>OUT</sub> = 156.25 MHz LVPECL.

Integer mode assumes that the output dividers (Nn/Nd) are configured with an integer value.

- 4. Fractional and DCO modes assume that the output dividers (Nn/Nd) are configured with a fractional value and the feedback divider is integer.

- 5. Initiate a soft reset command to align the outputs to within +/- 100 ps.

- 6. PLL lock time is measured by first letting the PLL lock, then turning off the input clock, and then turning on the input clock. The time from the first edge of the input clock being re-applied until LOL de-asserts is the PLL lock time.

#### **Table 8. Performance Characteristics (Continued)**

$(V_{DD} = 1.8 \text{ V } \pm 5\%, V_{DDA} = 3.3 \text{ V } \pm 5\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter               | Symbol                                                      | Test Condition                                                                                                                             | Min | Тур   | Max   | Units    |  |  |  |

|-------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|----------|--|--|--|

| Jitter Generation       |                                                             | XTAL Frequency = 48 MHz                                                                                                                    |     |       |       |          |  |  |  |

| Locked to External XTAL | J <sub>GEN</sub> Integer Mode <sup>3</sup> 12 kHz to 20 MHz |                                                                                                                                            | _   | 0.090 | 0.150 | ps RMS   |  |  |  |

|                         |                                                             | Fractional/DCO Mode <sup>4</sup><br>12 kHz to 20 MHz                                                                                       |     | 0.120 | 0.165 | ps RMS   |  |  |  |

|                         | J <sub>PER</sub>                                            | Derived from                                                                                                                               |     | 0.150 | _     | ps pk-pk |  |  |  |

|                         | J <sub>CC</sub>                                             | integrated phase noise                                                                                                                     | _   | 0.270 | _     | ps pk    |  |  |  |

|                         | J <sub>PER</sub>                                            | N = 10, 000 cycles                                                                                                                         | _   | 7.3   | _     | ps pk-pk |  |  |  |

|                         | Jcc                                                         | Jcc Integer or Fractional Mode <sup>3,4</sup> .  Measured in the time domain.  Performance is limited by the noise floor of the equipment. |     | 7.8   | _     | ps pk    |  |  |  |

|                         |                                                             | XTAL Frequency = 25 MHz                                                                                                                    |     |       |       |          |  |  |  |

|                         | $J_{GEN}$                                                   | J <sub>GEN</sub> Integer Mode<br>12 kHz to 20 MHz                                                                                          |     | 0.125 | 0.330 | ps RMS   |  |  |  |

|                         |                                                             | Fractional<br>12 kHz to 20 MHz                                                                                                             |     | 0.170 | 0.360 | ps RMS   |  |  |  |

#### Notes:

- 1. Measured as time from valid  $V_{DD}$  and  $V_{DD33}$  rails (90% of their value) to when the serial interface is ready to respond to commands. Measured in SPI 4-wire mode, with SCLK @ 10 MHz.

- 2. Jitter generation test conditions  $f_{IN}$  = 100 MHz,  $f_{OUT}$  = 156.25 MHz LVPECL.

- 3. Integer mode assumes that the output dividers (Nn/Nd) are configured with an integer value.

- **4.** Fractional and DCO modes assume that the output dividers (Nn/Nd) are configured with a fractional value and the feedback divider is integer.

- 5. Initiate a soft reset command to align the outputs to within +/- 100 ps.

- **6.** PLL lock time is measured by first letting the PLL lock, then turning off the input clock, and then turning on the input clock. The time from the first edge of the input clock being re-applied until LOL de-asserts is the PLL lock time.

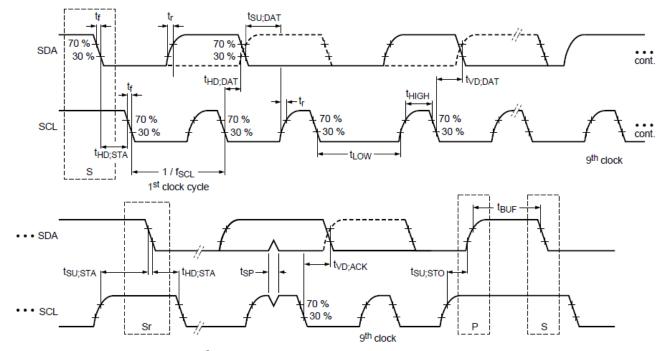

Table 9. I<sup>2</sup>C Timing Specifications (SCL,SDA)

| Parameter                                                   | Symbol              | Test Condition | Min                       | Max  | Min                   | Max | Units |

|-------------------------------------------------------------|---------------------|----------------|---------------------------|------|-----------------------|-----|-------|

|                                                             |                     |                | Standard Mode<br>100 kbps |      | Fast Mode<br>400 kbps |     |       |

| SCL Clock<br>Frequency                                      | f <sub>SCL</sub>    |                | _                         | 100  | _                     | 400 | kHz   |

| Hold Time<br>(Repeated)<br>START Condition                  | t <sub>HD:STA</sub> |                | 4.0                       | _    | 0.6                   | _   | μs    |

| Low Period of the SCL Clock                                 | t <sub>LOW</sub>    |                | 4.7                       | _    | 1.3                   | _   | μs    |

| HIGH Period of the SCL Clock                                | t <sub>HIGH</sub>   |                | 4.0                       | _    | 0.6                   | _   | μs    |

| Set-up Time for a<br>Repeated START<br>Condition            | t <sub>SU:STA</sub> |                | 4.7                       | _    | 0.6                   | _   | μs    |

| Data Hold Time                                              | t <sub>HD:DAT</sub> |                | 100                       | _    | 100                   | _   | ns    |

| Data Set-up Time                                            | t <sub>SU:DAT</sub> |                | 250                       | _    | 100                   | _   | ns    |

| Rise Time of Both<br>SDA and SCL<br>Signals                 | t <sub>r</sub>      |                | _                         | 1000 | 20                    | 300 | ns    |

| Fall Time of Both<br>SDA and SCL<br>Signals                 | t <sub>f</sub>      |                | _                         | 300  | _                     | 300 | ns    |

| Set-up Time for STOP Condition                              | t <sub>SU:STO</sub> |                | 4.0                       | _    | 0.6                   | _   | μs    |

| Bus Free Time<br>between a STOP<br>and START Con-<br>dition | t <sub>BUF</sub>    |                | 4.7                       | _    | 1.3                   | _   | μs    |

| Data Valid Time                                             | t <sub>VD:DAT</sub> |                | _                         | 3.45 | _                     | 0.9 | μs    |

| Data Valid<br>Acknowledge<br>Time                           | t <sub>VD:ACK</sub> |                | _                         | 3.45 | _                     | 0.9 | μs    |

Figure 2. I<sup>2</sup>C Serial Port Timing Standard and Fast Modes

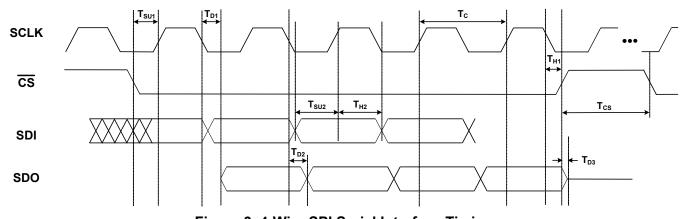

# Table 10. SPI Timing Specifications (4-Wire) ( $V_{DD}$ = 1.8 V ±5%, $V_{DDA}$ = 3.3V ±5%, $T_A$ = -40 to 85 °C)

| Parameter                            | Symbol           | Min | Тур  | Max | Units          |

|--------------------------------------|------------------|-----|------|-----|----------------|

| SCLK Frequency                       | f <sub>SPI</sub> | _   | _    | 20  | MHz            |

| SCLK Duty Cycle                      | T <sub>DC</sub>  | 40  | _    | 60  | %              |

| SCLK Period                          | $T_C$            | 50  | _    | _   | ns             |

| Delay Time, SCLK Fall to SDO Active  | T <sub>D1</sub>  | _   | 12.5 | 18  | ns             |

| Delay Time, SCLK Fall to SDO         | T <sub>D2</sub>  | _   | 10   | 15  | ns             |

| Delay Time, CS Rise to SDO Tri-State | $T_{D3}$         |     | 10   | 15  | ns             |

| Setup Time, CS to SCLK               | T <sub>SU1</sub> | 5   | _    | _   | ns             |

| Hold Time, CS to SCLK Rise           | T <sub>H1</sub>  | 5   | _    | _   | ns             |

| Setup Time, SDI to SCLK Rise         | T <sub>SU2</sub> | 5   | _    | _   | ns             |

| Hold Time, SDI to SCLK Rise          | T <sub>H2</sub>  | 5   | _    | _   | ns             |

| Delay Time Between Chip Selects (CS) | T <sub>CS</sub>  | 2   | _    | _   | T <sub>C</sub> |

Figure 3. 4-Wire SPI Serial Interface Timing

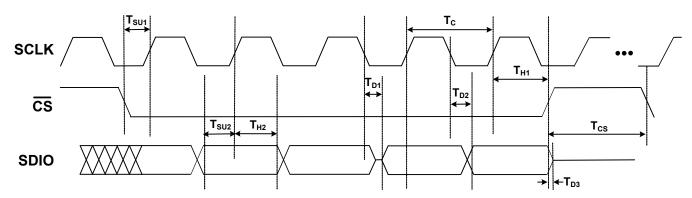

Table 11. SPI Timing Specifications (3-Wire) ( $V_{DD}$  = 1.8 V ±5%,  $V_{DDA}$  = 3.3 V ±5%,  $T_A$  = -40 to 85 °C)

| Parameter                              | Symbol           | Min | Тур  | Max | Units          |

|----------------------------------------|------------------|-----|------|-----|----------------|

| SCLK Frequency                         | f <sub>SPI</sub> | _   | _    | 20  | MHz            |

| SCLK Duty Cycle                        | T <sub>DC</sub>  | 40  | _    | 60  | %              |

| SCLK Period                            | T <sub>C</sub>   | 50  | _    | _   | ns             |

| Delay Time, SCLK Fall to SDIO Turn-on  | T <sub>D1</sub>  | _   | 12.5 | 20  | ns             |

| Delay Time, SCLK Fall to SDIO Next-bit | T <sub>D2</sub>  | _   | 10   | 15  | ns             |

| Delay Time, CS Rise to SDIO Tri-State  | T <sub>D3</sub>  | _   | 10   | 15  | ns             |

| Setup Time, CS to SCLK                 | T <sub>SU1</sub> | 5   | _    | _   | ns             |

| Hold Time, CS to SCLK Rise             | T <sub>H1</sub>  | 5   | _    | _   | ns             |

| Setup Time, SDI to SCLK Rise           | T <sub>SU2</sub> | 5   | _    | _   | ns             |

| Hold Time, SDI to SCLK Rise            | T <sub>H2</sub>  | 5   | _    | _   | ns             |

| Delay Time Between Chip Selects (CS)   | T <sub>CS</sub>  | 2   | _    | _   | T <sub>C</sub> |

Figure 4. 3-Wire SPI Serial Interface Timing

**Table 12. Crystal Specifications**

| Parameter                    | Symbol                  | Test Condition                                                  | Min         | Тур       | Max           | Units    |  |

|------------------------------|-------------------------|-----------------------------------------------------------------|-------------|-----------|---------------|----------|--|

| Crystal Frequency Range      | f <sub>XTAL_48-54</sub> | Frequency range for best jitter performance                     | 48          | _         | 54            | MHz      |  |

| Load Capacitance             | C <sub>L_48-54</sub>    |                                                                 | _           | 8         | _             | pF       |  |

| Shunt Capacitance            | C <sub>O_48-54</sub>    |                                                                 | _           | _         | 2             | pF       |  |

| Crystal Drive Level          | d <sub>L_48-54</sub>    |                                                                 | _           | _         | 200           | μW       |  |

| Equivalent Series Resistance | r <sub>ESR_48-54</sub>  | Refer to the Si5341/40 F                                        | amily Refer | ence Manu | ial to determ | ine ESR. |  |

| Crystal Frequency Range      | f <sub>XTAL_25</sub>    |                                                                 | _           | 25        | _             | MHz      |  |

| Load Capacitance             | C <sub>L_25</sub>       |                                                                 | _           | 8         | _             | pF       |  |

| Shunt Capacitance            | C <sub>O_25</sub>       |                                                                 | _           | _         | 3             | pF       |  |

| Crystal Drive Level          | d <sub>L_25</sub>       |                                                                 | _           | _         | 200           | μW       |  |

| Equivalent Series Resistance | r <sub>ESR_25</sub>     | Refer to the Si5341/40 Family Reference Manual to determine ESR |             |           |               |          |  |

#### Notes:

- The Si5341/40 is designed to work with crystals that meet the specifications in Table 12.

Refer to the Si5341/40 Family Reference Manual for recommended 48 to 54 MHz crystals.

**Table 13. Thermal Characteristics**

| Parameter                                 | Symbol            | Test Condition* | Value | Units |

|-------------------------------------------|-------------------|-----------------|-------|-------|

| Si5341 — 64QFN                            |                   |                 | 1     |       |

| Thermal Resistance<br>Junction to Ambient | $\theta_{\sf JA}$ | Still Air       | 22    | °C/W  |

|                                           |                   | Air Flow 1 m/s  | 19.4  |       |

|                                           |                   | Air Flow 2 m/s  | 18.3  |       |

| Thermal Resistance Junction to Case       | θЈС               |                 | 9.5   |       |

| Thermal Resistance                        | $\theta_{JB}$     |                 | 9.4   |       |

| Junction to Board                         | ΨЈВ               |                 | 9.3   |       |

| Thermal Resistance Junction to Top Center | ΨJT               |                 | 0.2   |       |

| Si5340-44QFN                              |                   |                 | ,     |       |

| Thermal Resistance                        | $\theta_{\sf JA}$ | Still Air       | 22.3  | °C/W  |

| Junction to Ambient                       |                   | Air Flow 1 m/s  | 19.4  |       |

|                                           |                   | Air Flow 2 m/s  | 18.4  |       |

| Thermal Resistance<br>Junction to Case    | θЈС               |                 | 10.9  |       |

| Thermal Resistance                        | $\theta_{JB}$     |                 | 9.3   |       |

| Junction to Board                         | ΨЈВ               |                 | 9.2   |       |

| Thermal Resistance Junction to Top Center | ΨЈТ               |                 | 0.23  |       |

\*Note: Based on PCB Dimension: 3" x 4.5", PCB Thickness: 1.6 mm, PCB Land/Via under GND pad: 36, Number of Cu Layers: 4

Table 14. Absolute Maximum Ratings<sup>1,2,3,4</sup>

| Parameter                                                                      | Symbol            | <b>Test Condition</b>                                                        | Value        | Units  |

|--------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|--------------|--------|

| Storage Temperature Range                                                      | T <sub>STG</sub>  |                                                                              | -55 to +150  | °C     |

| DC Supply Voltage                                                              | V <sub>DD</sub>   |                                                                              | -0.5 to 3.8  | V      |

|                                                                                | $V_{DDA}$         |                                                                              | -0.5 to 3.8  | V      |

|                                                                                | $V_{DDO}$         |                                                                              | -0.5 to 3.8  | V      |

| Input Voltage Range                                                            | V <sub>I1</sub>   | IN0-IN2, FB_IN                                                               | -0.85 to 3.8 | V      |

|                                                                                | V <sub>I2</sub>   | IN_SEL[1:0], RST, OE, SYNC, I2C_SEL, SDI, SCLK, A0/CS A1, SDA/SDIO FINC/FDEC | -0.5 to 3.8  | V      |

|                                                                                | V <sub>I3</sub>   | XA/XB                                                                        | -0.5 to 2.7  | V      |

| Latch-up Tolerance                                                             | LU                |                                                                              | JESD78 Com   | pliant |

| ESD Tolerance                                                                  | НВМ               | 100 pF, 1.5 kΩ                                                               | 2.0          | kV     |

| Junction Temperature                                                           | T <sub>JCT</sub>  |                                                                              | -55 to 150   | °C     |

| Soldering Temperature<br>(Pb-free profile) <sup>4</sup>                        | T <sub>PEAK</sub> |                                                                              | 260          | °C     |

| Soldering Temperature Time at T <sub>PEAK</sub> (Pb-free profile) <sup>4</sup> | T <sub>P</sub>    |                                                                              | 20-40        | sec    |

|                                                                                |                   |                                                                              |              |        |

#### **Notes**

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. 64-QFN and 44-QFN packages are RoHS-6 compliant.

- 3. For MSL and more packaging information, go to www.silabs.com/support/quality/pages/rohsinformation.aspx.

- 4. The device is compliant with JEDEC J-STD-020.

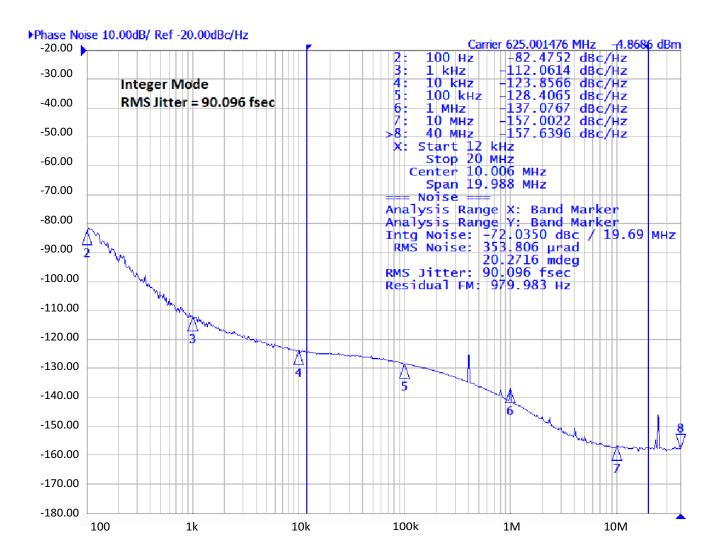

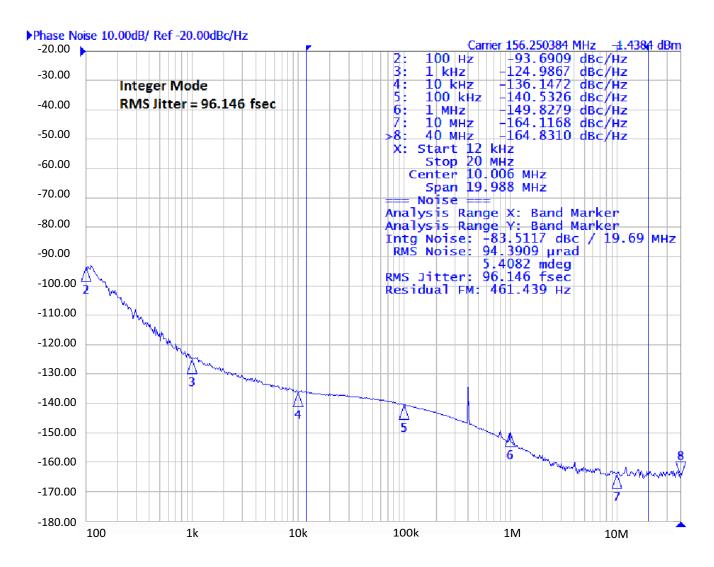

## 3. Typical Operating Characteristics

Figure 5. Integer Mode—48 MHz Crystal, 625 MHz Output (2.5 V LVDS)

Figure 6. Integer Mode—48 MHz Crystal, 156.25 MHz Output (2.5 V LVDS)

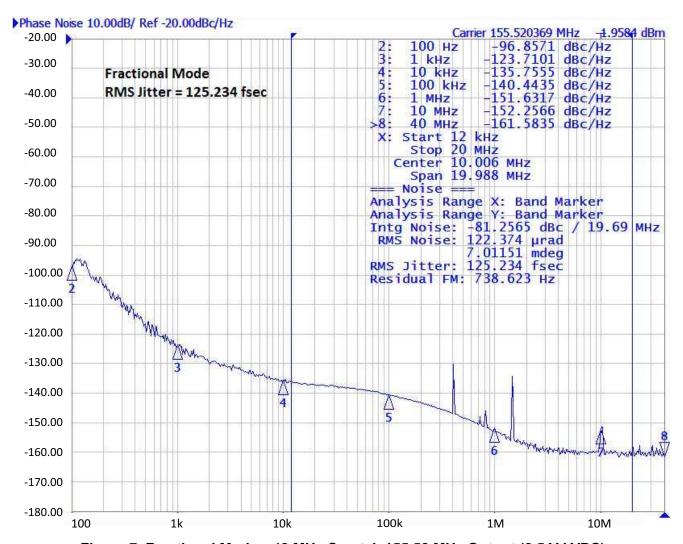

Figure 7. Fractional Mode—48 MHz Crystal, 155.52 MHz Output (2.5 V LVDS)