Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ANY-FREQUENCY PRECISION CLOCK MULTIPLIER/JITTER **ATTENUATOR**

#### **Features**

- Generates any frequency from 2 kHz Five clock outputs with selectable to 945 MHz and select frequencies to 1.4 GHz from an input frequency of 2 kHz to 710 MHz

- Ultra-low jitter clock outputs with jitter generation as low as 300 fs rms (12 kHz-20 MHz)

- Integrated loop filter with selectable loop bandwidth (4 Hz to 525 Hz)

- Meets OC-192 GR-253-CORE jitter specifications

- Four clock inputs with manual or automatically controlled hitless switching and phase build-out

- Supports holdover and freerun modes of operation

- SONET frame sync switching and regeneration

- signal format (LVPECL, LVDS, CML, CMOS)

- Support for ITU G.709 and custom FEC ratios (253/226, 239/237, 255/238, 255/237, 255/236)

- LOL, LOS, FOS alarm outputs

- Digitally-controlled output phase adjust

- I<sup>2</sup>C or SPI programmable settings

- On-chip voltage regulator for 1.8 V ±5%, 2.5 V ±10%, or 3.3 V ±10% operation

- Small size: 14 x 14 mm 100-pin **TQFP**

- Pb-free, RoHS compliant

**Ordering Information:** See page 78.

### **Applications**

- SONET/SDH OC-48/STM-16/OC-192/STM-64 line cards

- GbE/10GbE, 1/2/4/8/10G FC line cards ■

- ITU G.709 and custom FEC line cards

- Wireless repeaters/wireless backhaul

- Data converter clocking

- OTN/WDM Muxponder, MSPP, ROADM line cards

- SONET/SDH + PDH clock synthesis

- Test and measurement

- Synchronous Ethernet

- Broadcast video

#### **Description**

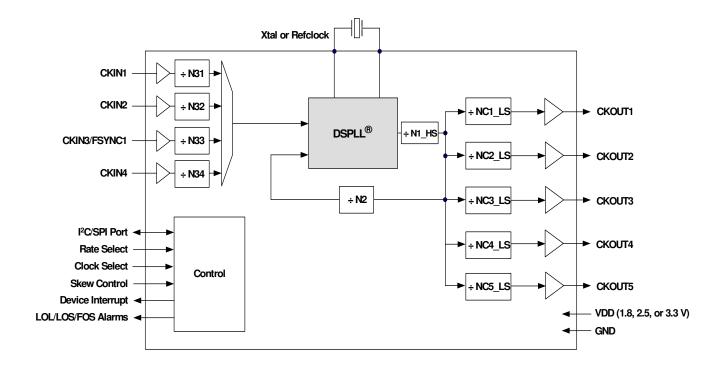

The Si5369 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps rms jitter performance. The Si5369 accepts four clock inputs ranging from 2 kHz to 710 MHz and generates five clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The device provides virtually any frequency translation combination across this operating range. The outputs are divided down separately from a common source. The Si5369 input clock frequency and clock multiplication ratio are programmable through an I<sup>2</sup>C or SPI interface. The Si5369 is based on Silicon Laboratories' third-generation DSPLL® technology, which provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5369 is ideal for providing clock multiplication and jitter attenuation in high performance timing applications.

## **Functional Block Diagram**

# TABLE OF CONTENTS

| <u>Section</u>                     | <u>Page</u> |

|------------------------------------|-------------|

| 1. Electrical Specifications       | <br>4       |

| 2. Typical Phase Noise Performance | <br>16      |

| 3. Functional Description          |             |

| 3.1. External Reference            |             |

| 3.2. Further Documentation         | <br>21      |

| 4. Register Map                    | <br>22      |

| 5. Register Descriptions           | <br>25      |

| 6. Pin Descriptions: Si5369        | <br>73      |

| 7. Ordering Guide                  |             |

| 8. Package Outline: 100-Pin TQFP   | <br>79      |

| 9. Recommended PCB Layout          | <br>80      |

| 10. Top Marking                    |             |

| Document Change List               | <br>83      |

| Contact Information                |             |

## 1. Electrical Specifications

Table 1. Recommended Operating Conditions<sup>1</sup>

| Parameter                                 | Symbol         | Test Condition             | Min  | Тур | Max  | Unit |

|-------------------------------------------|----------------|----------------------------|------|-----|------|------|

| Ambient Temperature                       | T <sub>A</sub> |                            | -40  | 25  | 85   | С    |

| Supply Voltage during<br>Normal Operation | $V_{DD}$       | 3.3 V Nominal <sup>2</sup> | 2.97 | 3.3 | 3.63 | V    |

|                                           |                | 2.5 V Nominal              | 2.25 | 2.5 | 2.75 | V    |

|                                           |                | 1.8 V Nominal              | 1.71 | 1.8 | 1.89 | V    |

#### Notes:

- **1.** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

- 2. The LVPECL and CMOS output formats draw more current than either LVDS or CML; however, there are restrictions in the allowed output format pin settings so that the maximum power dissipation for the TQFP devices is limited when they are operated at 3.3 V. When there are four enabled LVPECL or CMOS outputs, the fifth output must be disabled. When there are five enabled outputs, there can be no more than three outputs that are either LVPECL or CMOS.

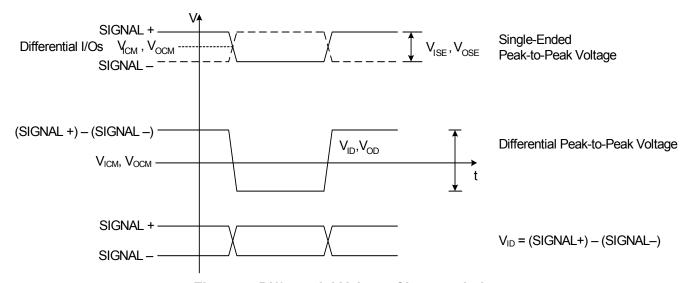

Figure 1. Differential Voltage Characteristics

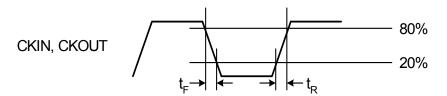

Figure 2. Rise/Fall Time Characteristics

SHIPPN LARG

**Table 2. DC Characteristics**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                   | Symbol             | Test Condition                                        | Min  | Тур | Max  | Unit            |

|---------------------------------------------|--------------------|-------------------------------------------------------|------|-----|------|-----------------|

| Supply Current <sup>1,6</sup>               | I <sub>DD</sub>    | LVPECL Format<br>622.08 MHz Out<br>All CKOUTs Enabled | _    | 394 | 435  | mA              |

|                                             |                    | LVPECL Format<br>622.08 MHz Out<br>1 CKOUT Enabled    | _    | 253 | 284  | mA              |

|                                             |                    | CMOS Format<br>19.44 MHz Out<br>All CKOUTs Enabled    | _    | 278 | 400  | mA              |

|                                             |                    | CMOS Format<br>19.44 MHz Out<br>1 CKOUT Enabled       | _    | 229 | 261  | mA              |

|                                             |                    | Disable Mode                                          | _    | 165 | _    | mA              |

| CKINn Input Pins <sup>2</sup>               |                    |                                                       |      | 1   | 1    |                 |

| Input Common Mode<br>Voltage (Input Thresh- | V <sub>ICM</sub>   | 1.8 V ± 5%                                            | 0.9  | _   | 1.4  | V               |

| old Voltage)                                |                    | 2.5 V ± 10%                                           | 1    | _   | 1.7  | V               |

|                                             |                    | 3.3 V ± 10%                                           | 1.1  | _   | 1.95 | V               |

| Input Resistance                            | CKN <sub>RIN</sub> | Single-ended                                          | 20   | 40  | 60   | kΩ              |

| Single-Ended Input<br>Voltage Swing         | $V_{ISE}$          | f <sub>CKIN</sub> < 212.5 MHz<br>See Figure 1.        | 0.2  | _   | _    | V <sub>PP</sub> |

| (See Absolute Specs)                        |                    | f <sub>CKIN</sub> > 212.5 MHz<br>See Figure 1.        | 0.25 | _   | _    | V <sub>PP</sub> |

| Differential Input<br>Voltage Swing         | $V_{ID}$           | f <sub>CKIN</sub> < 212.5 MHz<br>See Figure 1.        | 0.2  | _   | _    | V <sub>PP</sub> |

| (See Absolute Specs)                        |                    | fCKIN > 212.5 MHz<br>See Figure 1.                    | 0.25 | _   | _    | V <sub>PP</sub> |

### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- **3.** LVPECL outputs require nominal VDD ≥ 2.5 V.

- **4.** This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

- **6.** The LVPECL and CMOS output formats draw more current than either LVDS or CML; however, there are restrictions in the allowed output format pin settings so that the maximum power dissipation for the TQFP devices is limited when they are operated at 3.3 V. When there are four enabled LVPECL or CMOS outputs, the fifth output must be disabled. When there are five enabled outputs, there can be no more than three outputs that are either LVPECL or CMOS.

### **Table 2. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                         | Symbol               | Test Condition                                | Min                   | Тур                   | Max                   | Unit            |

|-----------------------------------|----------------------|-----------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------|

| Output Clocks (CKOUT              | Րn) <sup>3,5,6</sup> |                                               |                       |                       |                       |                 |

| Common Mode                       | CKO <sub>VCM</sub>   | LVPECL 100 Ω load line-to-line                | V <sub>DD</sub> –1.42 | _                     | V <sub>DD</sub> –1.25 | V               |

| Differential Output<br>Swing      | CKO <sub>VD</sub>    | LVPECL 100 Ω load line-to-line                | 1.1                   | _                     | 1.9                   | V <sub>PP</sub> |

| Single Ended Output<br>Swing      | CKO <sub>VSE</sub>   | LVPECL 100 Ω load line-to-line                | 0.5                   | _                     | 0.93                  | V <sub>PP</sub> |

| Differential Output Voltage       | CKO <sub>VD</sub>    | CML 100 Ω load line-to-line                   | 350                   | 425                   | 500                   | $mV_PP$         |

| Common Mode<br>Output Voltage     | CKO <sub>VCM</sub>   | CML 100 $\Omega$ load line-to-line            | _                     | V <sub>DD</sub> -0.36 |                       | V               |

| Differential Output Voltage       | CKO <sub>VD</sub>    | LVDS 100 $\Omega$ load line-to-line           | 500                   | 700                   | 900                   | $mV_PP$         |

|                                   |                      | Low Swing LVDS 100 $\Omega$ load line-to-line | 350                   | 425                   | 500                   | $mV_PP$         |

| Common Mode<br>Output Voltage     | CKO <sub>VCM</sub>   | LVDS 100 Ω load<br>line-to-line               | 1.125                 | 1.2                   | 1.275                 | V               |

| Differential<br>Output Resistance | CKO <sub>RD</sub>    | CML, LVPECL, LVDS                             | _                     | 200                   |                       | Ω               |

| Output Voltage Low                | CKO <sub>VOLLH</sub> | CMOS                                          | _                     | _                     | 0.4                   | V               |

| Output Voltage High               | CKO <sub>VOHLH</sub> | V <sub>DD</sub> = 1.71 V<br>CMOS              | 0.8 x V <sub>DD</sub> | _                     | _                     | V               |

### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- 4. This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

- **6.** The LVPECL and CMOS output formats draw more current than either LVDS or CML; however, there are restrictions in the allowed output format pin settings so that the maximum power dissipation for the TQFP devices is limited when they are operated at 3.3 V. When there are four enabled LVPECL or CMOS outputs, the fifth output must be disabled. When there are five enabled outputs, there can be no more than three outputs that are either LVPECL or CMOS.

**Table 2. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                                                                 | Symbol            | Test Condition                             | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------------|-------------------|--------------------------------------------|-----|------|-----|------|

| Output Drive Current (CMOS driving into                                                   | CKO <sub>IO</sub> | ICMOS[1:0] = 11<br>V <sub>DD</sub> = 1.8 V | _   | 7.5  | _   | mA   |

| CKO <sub>VOL</sub> for output low<br>or CKO <sub>VOH</sub> for output<br>high. CKOUT+ and |                   | ICMOS[1:0] = 10<br>V <sub>DD</sub> = 1.8 V | _   | 5.5  | _   | mA   |

| CKOUT- shorted externally)                                                                |                   | ICMOS[1:0] = 01<br>V <sub>DD</sub> = 1.8 V | _   | 3.5  | _   | mA   |

|                                                                                           |                   | ICMOS[1:0] = 00<br>V <sub>DD</sub> = 1.8 V | _   | 1.75 | _   | mA   |

|                                                                                           |                   | ICMOS[1:0] = 11<br>V <sub>DD</sub> = 3.3 V | _   | 32   | _   | mA   |

|                                                                                           |                   | ICMOS[1:0] = 10<br>V <sub>DD</sub> = 3.3 V | _   | 24   | _   | mA   |

|                                                                                           |                   | ICMOS[1:0] = 01<br>V <sub>DD</sub> = 3.3 V | _   | 16   | _   | mA   |

|                                                                                           |                   | ICMOS[1:0] = 00<br>V <sub>DD</sub> = 3.3 V | _   | 8    | _   | mA   |

| 2-Level LVCMOS Input                                                                      | Pins              |                                            |     |      |     | •    |

| Input Voltage Low                                                                         | $V_{IL}$          | V <sub>DD</sub> = 1.71 V                   | _   | _    | 0.5 | V    |

|                                                                                           |                   | V <sub>DD</sub> = 2.25 V                   | _   | _    | 0.7 | V    |

|                                                                                           |                   | V <sub>DD</sub> = 2.97 V                   | _   | _    | 0.8 | V    |

| Input Voltage High                                                                        | V <sub>IH</sub>   | V <sub>DD</sub> = 1.89 V                   | 1.4 | _    | _   | V    |

|                                                                                           |                   | V <sub>DD</sub> = 2.25 V                   | 1.8 | _    | _   | V    |

|                                                                                           |                   | V <sub>DD</sub> = 3.63 V                   | 2.5 | _    | _   | V    |

#### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- **4.** This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

- **6.** The LVPECL and CMOS output formats draw more current than either LVDS or CML; however, there are restrictions in the allowed output format pin settings so that the maximum power dissipation for the TQFP devices is limited when they are operated at 3.3 V. When there are four enabled LVPECL or CMOS outputs, the fifth output must be disabled. When there are five enabled outputs, there can be no more than three outputs that are either LVPECL or CMOS.

### **Table 2. DC Characteristics (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                       | Symbol           | Test Condition                         | Min                       | Тур | Max                    | Unit |

|---------------------------------|------------------|----------------------------------------|---------------------------|-----|------------------------|------|

| 3-Level Input Pins <sup>4</sup> |                  |                                        |                           |     | •                      |      |

| Input Voltage Low               | V <sub>ILL</sub> |                                        | _                         | _   | 0.15 x V <sub>DD</sub> | V    |

| Input Voltage Mid               | V <sub>IMM</sub> |                                        | 0.45 x<br>V <sub>DD</sub> | _   | 0.55 x V <sub>DD</sub> | V    |

| Input Voltage High              | V <sub>IHH</sub> |                                        | 0.85 x<br>V <sub>DD</sub> |     | _                      | V    |

| Input Low Current               | I <sub>ILL</sub> | See Note 4                             | -20                       | _   | _                      | μA   |

| Input Mid Current               | I <sub>IMM</sub> | See Note 4                             | -2                        | _   | +2                     | μA   |

| Input High Current              | Інн              | See Note 4                             | _                         | _   | 20                     | μΑ   |

| LVCMOS Output Pins              | 1                |                                        |                           |     |                        |      |

| Output Voltage Low              | V <sub>OL</sub>  | IO = 2 mA<br>V <sub>DD</sub> = 1.71 V  | _                         | _   | 0.4                    | V    |

| Output Voltage Low              |                  | IO = 2 mA<br>V <sub>DD</sub> = 2.97 V  | _                         | _   | 0.4                    | V    |

| Output Voltage High             | V <sub>OH</sub>  | IO = -2 mA<br>V <sub>DD</sub> = 1.71 V | V <sub>DD</sub> -0.4      | _   | _                      | V    |

| Output Voltage High             |                  | IO = -2 mA<br>V <sub>DD</sub> = 2.97 V | V <sub>DD</sub> -0.4      | _   | _                      | V    |

#### Notes:

- 1. Current draw is independent of supply voltage

- 2. No under- or overshoot is allowed.

- 3. LVPECL outputs require nominal VDD ≥ 2.5 V.

- **4.** This is the amount of leakage that the 3-Level inputs can tolerate from an external driver. See Si53xx Family Reference Manual for more details.

- **5.** LVPECL, CML, LVDS and low-swing LVDS measured with Fo = 622.08 MHz.

- **6.** The LVPECL and CMOS output formats draw more current than either LVDS or CML; however, there are restrictions in the allowed output format pin settings so that the maximum power dissipation for the TQFP devices is limited when they are operated at 3.3 V. When there are four enabled LVPECL or CMOS outputs, the fifth output must be disabled. When there are five enabled outputs, there can be no more than three outputs that are either LVPECL or CMOS.

**Table 3. AC Specifications**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                            | Symbol               | Test Condition                                                                              | Min   | Тур | Max   | Unit            |

|------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|-------|-----|-------|-----------------|

| Single-Ended Referer                                 | nce Clock Inp        | ut Pin XA (XB with cap to G                                                                 | ND)   |     |       |                 |

| Input Resistance                                     | XA <sub>RIN</sub>    | RATE[1:0] = LM, MH,<br>ac coupled                                                           | _     | 12  | _     | kΩ              |

| Input Voltage Swing                                  | XA <sub>VPP</sub>    | RATE[1:0] = LM, MH,<br>ac coupled                                                           | 0.5   | _   | 1.2   | V <sub>PP</sub> |

| Differential Reference                               | Clock Input          | Pins (XA/XB)                                                                                |       |     |       |                 |

| Input Voltage Swing                                  | XA/XB <sub>VPP</sub> | RATE[1:0] = LM, MH                                                                          | 0.5   | _   | 2.4   | V <sub>PP</sub> |

| CKINn Input Pins                                     | ı                    |                                                                                             |       |     |       |                 |

| Input Frequency                                      | CKN <sub>F</sub>     |                                                                                             | 0.002 | _   | 710   | MHz             |

| Input Duty Cycle<br>(Minimum Pulse<br>Width)         | CKN <sub>DC</sub>    | Whichever is smaller (i.e., the 40% / 60% limitation applies only to high frequency clocks) | 40    | _   | 60    | %               |

|                                                      |                      |                                                                                             | 2     | _   | _     | ns              |

| Input Capacitance                                    | CKN <sub>CIN</sub>   |                                                                                             | _     | _   | 3     | pF              |

| Input Rise/Fall Time                                 | CKN <sub>TRF</sub>   | 20–80%<br>See Figure 2                                                                      | _     | _   | 11    | ns              |

| CKOUTn Output Pins                                   |                      |                                                                                             |       |     |       |                 |

| (See ordering section for                            | or speed grade       | e vs frequency limits)                                                                      |       |     | T     |                 |

| Output Frequency<br>(Output not config-              | CKO <sub>F</sub>     | N1 ≥ 6                                                                                      | 0.002 | _   | 945   | MHz             |

| ured for CMOS or<br>Disabled)                        |                      | N1 = 5                                                                                      | 970   | _   | 1134  | MHz             |

| Diadology                                            |                      | N1 = 4                                                                                      | 1.213 | _   | 1.4   | GHz             |

| Maximum Output<br>Frequency in CMOS<br>Format        | CKO <sub>F</sub>     |                                                                                             | _     | _   | 212.5 | MHz             |

| Output Rise/Fall<br>(20–80 %) @<br>622.08 MHz output | CKO <sub>TRF</sub>   | Output not configured for CMOS or Disabled See Figure 2                                     | _     | 230 | 350   | ps              |

### Notes:

- 1. Input to output phase skew after an ICAL is not controlled and can assume any value.

- 2. Lock and settle time performance is dependent on the frequency plan and the XAXB reference frequency. Please visit the Silicon Labs Technical Support web page at: <a href="https://www.silabs.com/support/pages/contacttechnicalsupport.aspx">https://www.silabs.com/support/pages/contacttechnicalsupport.aspx</a> to submit a technical support request regarding the lock time of your frequency plan.

**Table 3. AC Specifications (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V } \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                          | Symbol              | Test Condition                                                                                                                         | Min | Тур | Max      | Unit              |

|----------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|-------------------|

| Output Rise/Fall<br>(20–80%) @<br>212.5 MHz output | CKO <sub>TRF</sub>  | CMOS Output<br>V <sub>DD</sub> = 1.71<br>C <sub>LOAD</sub> = 5 pF                                                                      | _   | _   | 8        | ns                |

| Output Rise/Fall<br>(20–80%) @<br>212.5 MHz output | CKO <sub>TRF</sub>  | CMOS Output $V_{DD} = 2.97$ $C_{LOAD} = 5 pF$                                                                                          | _   | _   | 2        | ns                |

| Output Duty Cycle<br>Uncertainty @<br>622.08 MHz   | CKO <sub>DC</sub>   | 100 Ω Load<br>Line-to-Line<br>Measured at 50% Point<br>(Not for CMOS)                                                                  | _   | _   | ±40      | ps                |

| LVCMOS Input Pins                                  |                     |                                                                                                                                        |     |     |          |                   |

| Minimum Reset Pulse<br>Width                       | t <sub>RSTMN</sub>  |                                                                                                                                        | 1   | _   |          | μs                |

| Reset to Microprocessor Access Ready               | t <sub>READY</sub>  |                                                                                                                                        | _   | _   | 10       | ms                |

| Input Capacitance                                  | $C_in$              |                                                                                                                                        | _   | _   | 3        | pF                |

| LVCMOS Output Pins                                 |                     |                                                                                                                                        |     |     |          |                   |

| Rise/Fall Times                                    | t <sub>RF</sub>     | C <sub>LOAD</sub> = 20pf<br>See Figure 2                                                                                               | _   | 25  | _        | ns                |

| LOSn Trigger Window                                | LOS <sub>TRIG</sub> | From last CKINn ↑ to ↓ Internal detection of LOSn N3 ≠ 1                                                                               | _   | _   | 4.5 x N3 | T <sub>CKIN</sub> |

| Time to Clear LOL after LOS Cleared                | t <sub>CLRLOL</sub> | ↓LOS to ↓LOL<br>Fold = Fnew<br>Stable Xa/XB reference                                                                                  | _   | 10  | _        | ms                |

| Device Skew                                        |                     |                                                                                                                                        |     |     |          |                   |

| Output Clock Skew                                  | t <sub>SKEW</sub>   | ↑ of CKOUTn to ↑ of CKOUT_m, CKOUTn and CKOUT_m at same frequency and signal format  PHASEOFFSET = 0  CKOUT_ALWAYS_ON = 1  SQ_ICAL = 1 | _   | _   | 100      | ps                |

#### Notes

- 1. Input to output phase skew after an ICAL is not controlled and can assume any value.

- 2. Lock and settle time performance is dependent on the frequency plan and the XAXB reference frequency. Please visit the Silicon Labs Technical Support web page at: https://www.silabs.com/support/pages/contacttechnicalsupport.aspx to submit a technical support request regarding the lock time of your frequency plan.

SHIPPIN LAB

**Table 3. AC Specifications (Continued)**

$(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, T_A = -40 \text{ to } 85 \text{ °C})$

| Parameter                                              | Symbol              | Test Condition                                                | Min         | Тур         | Max | Unit     |

|--------------------------------------------------------|---------------------|---------------------------------------------------------------|-------------|-------------|-----|----------|

| Phase Change due to Temperature Variation <sup>1</sup> | t <sub>TEMP</sub>   | Max phase changes from<br>-40 to +85 °C                       | _           | 300         | 500 | ps       |

| PLL Performance                                        |                     |                                                               |             |             |     | •        |

| (fin = fout = 622.08 MF                                | lz; BW = 7 Hz       | z; LVPECL, XAXB = 114.285                                     | MHz)        |             |     |          |

| Lock Time <sup>2</sup>                                 | t <sub>LOCKMP</sub> | Start of ICAL to ↓ of LOL                                     | 1           | 0.8         | 1.0 | s        |

| Settle Time <sup>2</sup>                               | t <sub>SETTLE</sub> | Start of ICAL to F <sub>OUT</sub> within 5 ppm of final value |             | 4.2         | 5.0 | S        |

| Output Clock Phase<br>Change                           | t <sub>P_STEP</sub> | After clock switch f3 ≥ 128 kHz                               | _           | 200         | _   | ps       |

| Closed Loop Jitter<br>Peaking                          | $J_{PK}$            |                                                               | _           | 0.05        | 0.1 | dB       |

| Jitter Tolerance                                       | J <sub>TOL</sub>    | Jitter Frequency ≥ Loop<br>Bandwidth                          | 5000/BW     | _           | _   | ns pk-pk |

| Phase Noise<br>fout = 622.08 MHz                       |                     | 100 Hz Offset                                                 | _           | -95         | _   | dBc/Hz   |

| 10dt - 022.00 Wii i2                                   |                     | 1 kHz Offset                                                  | _           | -110        | _   | dBc/Hz   |

|                                                        | CKO <sub>PN</sub>   | 10 kHz Offset                                                 | _           | -117        | _   | dBc/Hz   |

|                                                        |                     | 100 kHz Offset                                                | <del></del> | -118        | _   | dBc/Hz   |

|                                                        |                     | 1 MHz Offset                                                  | _           | -131        | _   | dBc/Hz   |

| Spurious Noise                                         | SP <sub>SPUR</sub>  | Max spur @ n x F3<br>(n ≥ 1, n x F3 < 100 MHz)                | _           | <b>–</b> 67 | _   | dBc      |

#### Notes:

- 1. Input to output phase skew after an ICAL is not controlled and can assume any value.

- 2. Lock and settle time performance is dependent on the frequency plan and the XAXB reference frequency. Please visit the Silicon Labs Technical Support web page at: <a href="https://www.silabs.com/support/pages/contacttechnicalsupport.aspx">https://www.silabs.com/support/pages/contacttechnicalsupport.aspx</a> to submit a technical support request regarding the lock time of your frequency plan.

# Si5369

Table 4. Microprocessor Control ( $V_{DD}$  = 1.8 ± 5%, 2.5 ±10%, or 3.3 V ±10%,  $T_A$  = -40 to 85 °C)

| Parameter                             | Symbol              | Test Condition                              | Min                    | Тур | Max                    | Unit |  |

|---------------------------------------|---------------------|---------------------------------------------|------------------------|-----|------------------------|------|--|

| I <sup>2</sup> C Bus Lines (SDA, SCL) |                     |                                             |                        |     |                        |      |  |

| Input Voltage Low                     | VIL <sub>I2C</sub>  |                                             | _                      | _   | 0.25 x V <sub>DD</sub> | V    |  |

| Input Voltage High                    | VIH <sub>I2C</sub>  |                                             | 0.7 x V <sub>DD</sub>  | _   | $V_{DD}$               | V    |  |

| Hysteresis of Schmitt trigger inputs  | VHYS <sub>I2C</sub> | V <sub>DD</sub> = 1.8 V                     | 0.1 x V <sub>DD</sub>  | _   | _                      | V    |  |

| inggor inpute                         |                     | V <sub>DD</sub> = 2.5 or 3.3 V              | 0.05 x V <sub>DD</sub> | _   | _                      | V    |  |

| Output Voltage Low                    | VOL <sub>I2C</sub>  | V <sub>DD</sub> = 1.8 V<br>IO = 3 mA        | _                      | _   | 0.2 x V <sub>DD</sub>  | V    |  |

|                                       |                     | V <sub>DD</sub> = 2.5 or 3.3 V<br>IO = 3 mA | _                      | _   | 0.4                    | V    |  |

Table 4. Microprocessor Control (Continued)  $(V_{DD} = 1.8 \pm 5\%, 2.5 \pm 10\%, \text{ or } 3.3 \text{ V} \pm 10\%, \text{ T}_{A} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                               | Symbol           | Test Condition | Min      | Тур | Max         | Unit |

|-----------------------------------------|------------------|----------------|----------|-----|-------------|------|

| SPI Specifications                      | ,                |                | •        |     |             | 1    |

| Duty Cycle, SCLK                        | t <sub>DC</sub>  | SCLK = 10 MHz  | 40       | _   | 60          | %    |

| Cycle Time, SCLK                        | t <sub>c</sub>   |                | 100      | _   | <del></del> | ns   |

| Rise Time, SCLK                         | t <sub>r</sub>   | 20–80%         | <u> </u> | _   | 25          | ns   |

| Fall Time, SCLK                         | t <sub>f</sub>   | 20–80%         | <u> </u> | _   | 25          | ns   |

| Low Time, SCLK                          | t <sub>lsc</sub> | 20–20%         | 30       | _   | <del></del> | ns   |

| High Time, SCLK                         | t <sub>hsc</sub> | 80–80%         | 30       | _   | <del></del> | ns   |

| Delay Time, SCLK Fall to SDO Active     | t <sub>d1</sub>  |                | _        | _   | 25          | ns   |

| Delay Time, SCLK Fall to SDO Transition | t <sub>d2</sub>  |                | _        | _   | 25          | ns   |

| Delay Time, SS Rise<br>to SDO Tri-state | t <sub>d3</sub>  |                | _        | _   | 25          | ns   |

| Setup Time, SS to<br>SCLK Fall          | t <sub>su1</sub> |                | 25       | _   | _           | ns   |

| Hold Time, SS to<br>SCLK Rise           | t <sub>h1</sub>  |                | 20       | _   | _           | ns   |

| Setup Time, SDI to<br>SCLK Rise         | t <sub>su2</sub> |                | 25       | _   | _           | ns   |

| Hold Time, SDI to<br>SCLK Rise          | t <sub>h2</sub>  |                | 20       | _   | _           | ns   |

| Delay Time between<br>Slave Selects     | t <sub>cs</sub>  |                | 25       | _   | _           | ns   |

**Table 5. Jitter Generation**

| Parameter            | Symbol | Test Condition        | on <sup>*</sup>          | Min | Тур | Max | GR-253-       | Unit              |

|----------------------|--------|-----------------------|--------------------------|-----|-----|-----|---------------|-------------------|

|                      |        | Measurement<br>Filter | DSPLL<br>BW <sup>2</sup> |     |     |     | Specification |                   |

| Jitter Gen<br>OC-192 | JGEN   | 0.02-80 MHz           | 120 Hz                   |     | 4.2 | _   | 30            | ps <sub>PP</sub>  |

|                      |        |                       |                          |     | .27 | _   | N/A           | ps <sub>rms</sub> |

|                      |        | 4–80 MHz              | 120 Hz                   |     | 3.7 | _   | 10            | ps <sub>PP</sub>  |

|                      |        |                       |                          | _   | .14 | _   | N/A           | ps <sub>rms</sub> |

|                      |        | 0.05–80 MHz           | 120 Hz                   | _   | 4.4 | _   | 10            | ps <sub>PP</sub>  |

|                      |        |                       |                          | _   | .26 | _   | 1.0           | ps <sub>rms</sub> |

| Jitter Gen<br>OC-48  | JGEN   | 0.12–20 MHz           | 120 Hz                   | _   | 3.5 | _   | 40.2          | ps <sub>PP</sub>  |

|                      |        |                       |                          | _   | .27 | _   | 4.02          | ps <sub>rms</sub> |

\*Note: Test conditions:

1. fIN = fOUT = 622.08 MHz

2. Clock input: LVPECL

3. Clock output: LVPECL

4. PLL bandwidth: 120 Hz

5. 114.285 MHz 3rd OT crystal used as XA/XB input

- 6.  $V_{DD} = 2.5 V$

- 7.  $T_A = 85 \, ^{\circ}C$

- 8. Jitter integration bands include low-pass (-20 dB/dec) and high-pas (-60 dB/dec) roll-offs per Telecordia GR-253-

## **Table 6. Thermal Characteristics**

$(V_{DD}$  = 1.8 ±5%, 2.5 ±10%, or 3.3 V ±10%,  $T_A$  = -40 to 85 °C)

| Parameter                              | Symbol            | Test Condition | Value | Unit |

|----------------------------------------|-------------------|----------------|-------|------|

| Thermal Resistance Junction to Ambient | $\theta_{\sf JA}$ | Still Air      | 31    | C°/W |

## **Table 7. Absolute Maximum Ratings\***

| Parameter                                                             | Symbol             | Test Condition | Min              | Тур | Max                  | Unit |  |

|-----------------------------------------------------------------------|--------------------|----------------|------------------|-----|----------------------|------|--|

| DC Supply Voltage                                                     | $V_{DD}$           |                | -0.5             | _   | 3.8                  | V    |  |

| LVCMOS Input Voltage                                                  | $V_{DIG}$          |                | -0.3             | _   | V <sub>DD</sub> +0.3 | V    |  |

| CKINn Voltage Level Limits                                            | CKN <sub>VIN</sub> |                | 0                | _   | $V_{DD}$             | V    |  |

| XA/XB Voltage Level Limits                                            | XA <sub>VIN</sub>  |                | 0                | _   | 1.2                  | V    |  |

| Operating Junction Temperature                                        | T <sub>JCT</sub>   |                | <b>–</b> 55      | _   | 150                  | °C   |  |

| Storage Temperature Range                                             | T <sub>STG</sub>   |                | <b>–</b> 55      | _   | 150                  | °C   |  |

| ESD HBM Tolerance<br>(100 pF, 1.5 kΩ); All pins except<br>CKIN+/CKIN– |                    |                | 2                | _   | _                    | kV   |  |

| ESD MM Tolerance; All pins except CKIN+/CKIN-                         |                    |                | 150              | _   | _                    | V    |  |

| ESD HBM Tolerance<br>(100 pF, 1.5 kΩ); CKIN+/CKIN-                    |                    |                | 700              | _   | _                    | V    |  |

| ESD MM Tolerance;<br>CKIN+/CKIN-                                      |                    |                | 100              | _   | _                    | V    |  |

| Latch-up Tolerance                                                    |                    |                | JESD78 Compliant |     |                      |      |  |

\*Note: Permanent device damage may occur if the Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operation sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

# 2. Typical Phase Noise Performance

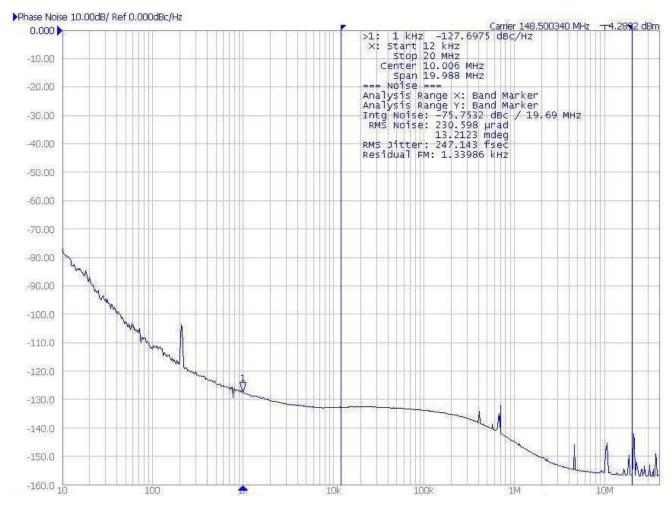

Figure 3. Broadcast Video\*

\*Note: Phase noise plot RMS jitter value used brick wall integration.

| Jitter Bandwidth                | Jitter (peak-peak) | Jitter (RMS) |  |  |  |

|---------------------------------|--------------------|--------------|--|--|--|

| 10 Hz to 20 MHz                 | 5.24 ps            | 484          |  |  |  |

| Note: Number of samples: 8.91E9 |                    |              |  |  |  |

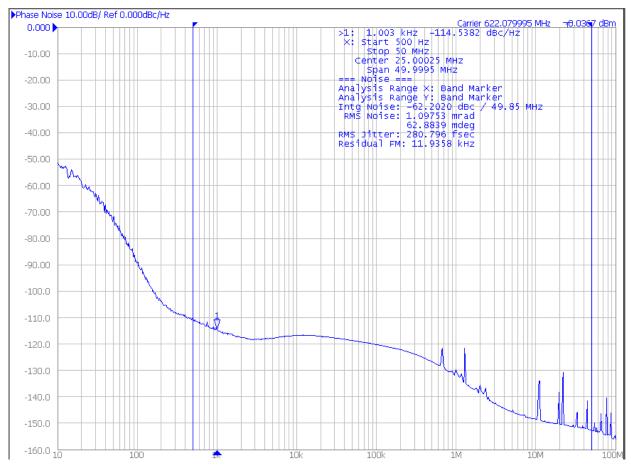

Figure 4. OTN/SONET/SDH Phase Noise\*

\*Note: Phase noise plot RMS jitter value uses brick wall integration.

| Jitter Bandwidth                | Jitter, RMS |

|---------------------------------|-------------|

| SONET_OC48, 12 kHz to 20 MHz    | 266 fs      |

| SONET_OC192_A, 20 kHz to 80 MHz | 283 fs      |

| SONET_OC192_B, 4 MHz to 80 MHz  | 155 fs      |

| SONET_OC192_C, 50 kHz to 80 MHz | 275 fs      |

| Brick Wall_800 Hz to 80 MHz     | 287 fs      |

|                                 | *           |

**Note:** Jitter integration bands include low-pass (–20 dB/Dec) and hi-pass (–60 dB/Dec) roll-offs per Telecordia GR-253-CORE.

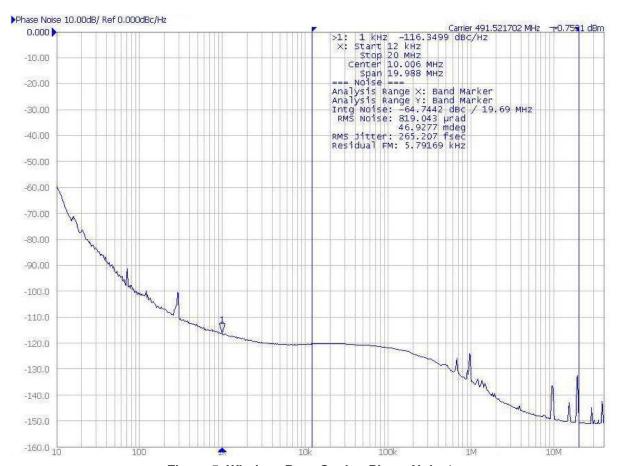

Figure 5. Wireless Base Station Phase Noise\*

\*Note: Phase noise plot RMS jitter value uses brick wall integration.

| Jitter Bandwidth                | Jitter (peak-peak) | Jitter (RMS) |  |  |  |

|---------------------------------|--------------------|--------------|--|--|--|

| 10 Hz to 20 MHz                 | 7.28 ps            | 581          |  |  |  |

| Note: Number of samples: 8.91E9 |                    |              |  |  |  |

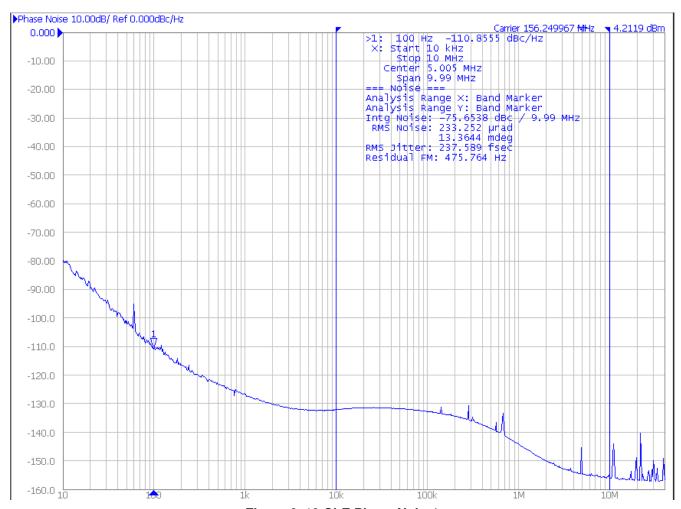

Figure 6. 10 GbE Phase Noise\*

\*Note: Phase noise plot RMS jitter value uses brick wall integration.

| Jitter Bandwidth | Jitter (RMS) |

|------------------|--------------|

| 10 kHz to 10 MHz | 238 fs       |

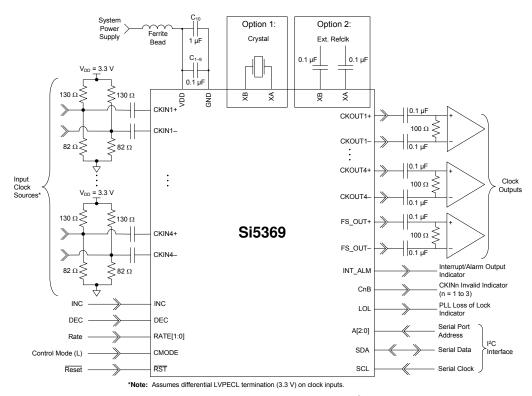

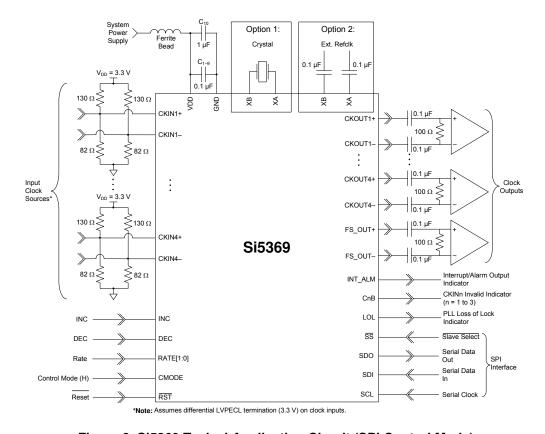

Figure 7. Si5369 Typical Application Circuit (I<sup>2</sup>C Control Mode)

Figure 8. Si5369 Typical Application Circuit (SPI Control Mode)

## 3. Functional Description

The Si5369 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps rms jitter performance. The Si5369 accepts four clock inputs ranging from 2 kHz to 710 MHz and generates five clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The device provides virtually any frequency translation combination across this operating range. Independent dividers are available for every input clock and output clock, so the Si5369 can accept input clocks at different frequencies and it can generate output clocks at different frequencies. The Si5369 input clock frequency and clock multiplication ratio are programmable through an I<sup>2</sup>C or SPI interface. Optionally, the fifth clock output can be configured as a 2 to 512 kHz SONET/SDH frame synchronization output that is phase aligned with one of the high-speed output clocks. Silicon Laboratories offers a PC-based software utility, DSPLLsim, that can be used to determine the optimum PLL divider settings for a given input frequency/clock multiplication ratio combination that minimizes phase noise and power consumption. This can be downloaded http://www.silabs.com/timing (click on Documentation).

The Si5369 is based on Silicon Laboratories' 3rd-generation DSPLL® technology, which provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need for external VCXO and loop filter components. The Si5369 PLL loop bandwidth is digitally programmable and supports a range from 4 to 525 Hz. The DSPLLsim software utility can be used to calculate valid loop bandwidth settings for a given input clock frequency/clock multiplication ratio.

The Si5369 supports hitless switching between input clocks in compliance with GR-253-CORE and GR-1244-CORE that greatly minimizes the propagation of phase transients to the clock outputs during an input clock transition (<200 ps typ). Manual, automatic revertive and non-revertive input clock switching options are available. The Si5369 monitors the four input clocks for loss-ofsignal and provides a LOS alarm when it detects missing pulses on any of the four input clocks. The device monitors the lock status of the PLL. The lock detect algorithm works by continuously monitoring the phase of the input clock in relation to the phase of the feedback clock. The Si5369 monitors the frequency of CKIN1, CKIN2, CKIN3, and CKIN4 with respect to a selected reference frequency and generates a frequency offset alarm (FOS) if the threshold is exceeded. This FOS feature is available for SONET applications in which both the monitored frequency on CKIN1, CKIN3, and CKIN4 and the reference frequency are integer multiples of 19.44 MHz. Both Stratum 3/3E and SONET Minimum Clock (SMC) FOS thresholds are supported.

The Si5369 provides a digital hold capability that allows the device to continue generation of a stable output clock when the selected input reference is lost. During digital hold, the DSPLL generates an output frequency based on a historical average that existed a fixed amount of time before the error event occurred, eliminating the effects of phase and frequency transients that may occur immediately preceding digital hold.

The Si5369 has five differential clock outputs. The electrical format of the clock outputs is programmable to support LVPECL, LVDS, CML, or CMOS loads, If not required, unused clock outputs can be powered down to minimize power consumption. The phase difference between the selected input clock and the output clocks is adjustable in 200 ps increments for system skew control. In addition, the phase of one output clock may be adjusted in relation to the phase of the other output clock. The resolution varies from 800 ps to 2.2 ns depending on the PLL divider settings. Consult the DSPLLsim configuration software to determine the phase offset resolution for a given input clock/clock multiplication ratio combination. For system-level debugging, a bypass mode is available which drives the output clock directly from the input clock, bypassing the internal DSPLL. The device is powered by a single 1.8, 2.5, or 3.3 V supply.

#### 3.1. External Reference

An external clock or a low-cost 114.285 MHz 3rd overtone crystal is typically used as part of a fixed-frequency oscillator within the DSPLL. This external reference is required for the device to operate. Silicon Laboratories recommends using a high-quality crystal. Specific recommendations may be found in the Family Reference Manual. An external clock from a high-quality OCXO or TCXO can also be used as a reference for the device.

If there is a need to use a reference oscillator instead of a crystal, Silicon Labs does not recommend using MEMS based oscillators. Instead, Silicon Labs recommends the Si530EB121M109DG, which is a very low jitter/wander, LVPECL, 2.5 V crystal oscillator. The very low loop BW of the Si5369 means that it can be susceptible to XAXB reference sources that have high wander. Experience has shown that in spite of having low jitter, some MEMs oscillators have high wander, and these devices should be avoided. Contact Silicon Labs for details.

In digital hold, the DSPLL remains locked to this external reference. Any changes in the frequency of this reference when the DSPLL is in digital hold, will be tracked by the output of the device. Note that crystals can have temperature sensitivities.

#### 3.2. Further Documentation

Consult the Silicon Laboratories Any-Frequency Precision Clock Family Reference Manual (FRM) for detailed information about the Si5369. Additional design support is available from Silicon Laboratories through your distributor.

Silicon Laboratories has developed a PC-based software utility called DSPLLsim to simplify device configuration, frequency planning, and loop bandwidth selection. The FRM and this utility can be downloaded from <a href="http://www.silabs.com/timing">http://www.silabs.com/timing</a>; click on Documentation.

# 4. Register Map

All register bits that are not defined in this map should always be written with the specified Reset Values. The writing to these bits of values other than the specified Reset Values may result in undefined device behavior. Registers not listed, such as Register 64, should never be written to.

| Register | D7             | D6           | D5                      | D4                | D3                | D2                | D1                | D0            |

|----------|----------------|--------------|-------------------------|-------------------|-------------------|-------------------|-------------------|---------------|

| 0        |                | FREE_RUN     | CKOUT_<br>ALWAYS_<br>ON |                   |                   |                   | BYPASS_<br>REG    |               |

| 1        | CK_PRI         | OR4 [1:0]    | CK_PRIC                 | OR3 [1:0]         | CK_PRI            | OR2 [1:0]         | CK_PRI            | OR1 [1:0]     |

| 2        |                | BWSEL_I      | REG [3:0]               |                   |                   |                   |                   |               |

| 3        | CKSEL_         | REG [1:0]    | DHOLD                   | SQ_ICAL           |                   |                   |                   |               |

| 4        | AUTOSEL        | _REG [1:0]   |                         |                   | ı                 | HIST_DEL [4:0     | ]                 |               |

| 5        | ICMO           | S [1:0]      | SF                      | OUT2_REG [2       | 2:0]              | SF                | OUT1_REG [2       | 2:0]          |

| 6        |                |              | SF                      | OUT4_REG [2       | 2:0]              | SF                | OUT3_REG [2       | 2:0]          |

| 7        |                |              | SF                      | OUT5_REG [2       | 2:0]              | F                 | OSREFSEL [2       | :0]           |

| 8        | HLOG           | _4 [1:0]     | HLOG_                   | _3 [1:0]          | HLOG_             | _2 [1:0]          | HLOG              | _1 [1:0]      |

| 9        |                | ŀ            | HIST_AVG [4:0           | ]                 |                   |                   | HLOG              | _5 [1:0]      |

| 10       |                |              | DSBL5_<br>REG           |                   | DSBL4_<br>REG     | DSBL3_<br>REG     | DSBL2_<br>REG     | DSBL1_<br>REG |

| 11       |                |              |                         |                   | PD_CK4            | PD_CK3            | PD_CK2            | PD_CK1        |

| 19       | FOS_EN         | FOS_TI       | HR [1:0]                | VALTIME [1:0]     |                   | LOCKT [2:0]       |                   |               |

| 20       |                |              | ALR-<br>MOUT_PIN        | CK3_BAD_<br>PIN   | CK2_BAD_<br>PIN   | CK1_BAD_<br>PIN   | LOL_PIN           | INT_PIN       |

| 21       |                |              |                         | CK4_ACT-<br>V_PIN | CK3_ACT-<br>V_PIN | CK2_ACT-<br>V_PIN | CK1_ACT-<br>V_PIN | CKSEL_PIN     |

| 22       |                |              |                         |                   | CK_ACTV_<br>POL   | CK_BAD_<br>POL    | LOL_POL           | INT_POL       |

| 23       |                |              |                         | LOS4_MSK          | LOS3_MSK          | LOS2_MSK          | LOS1_MSK          | LOSX_MSK      |

| 24       |                |              |                         | FOS4_MSK          | FOS3_MSK          | FOS2_MSK          | FOS1_MSK          | LOL_MSK       |

| 25       | N1_HS [2:0]    |              |                         |                   |                   | NC1_LS            | S [19:16]         |               |

| 26       | NC1_LS [15:8]  |              |                         |                   |                   |                   |                   |               |

| 27       | NC1_LS [7:0]   |              |                         |                   |                   |                   |                   |               |

| 28       | NC2_LS [19:16] |              |                         |                   |                   |                   |                   |               |

| 29       | NC2_LS [15:8]  |              |                         |                   |                   |                   |                   |               |

| 30       |                | NC2_LS [7:0] |                         |                   |                   |                   |                   |               |

| 31       |                |              |                         |                   |                   | NC3_LS            | S [19:16]         |               |

| Register | D7                                                                 | D6                | D5 | D4           | D3                | D2                | D1                | D0       |

|----------|--------------------------------------------------------------------|-------------------|----|--------------|-------------------|-------------------|-------------------|----------|

| 32       | NC3_LS [15:8]                                                      |                   |    |              |                   |                   |                   |          |

| 33       |                                                                    | NC3_LS [7:0]      |    |              |                   |                   |                   |          |

| 34       |                                                                    |                   |    |              |                   | NC4_LS            | S [19:16]         |          |

| 35       |                                                                    |                   |    | NC4_L        | S [15:8]          |                   |                   |          |

| 36       |                                                                    |                   |    | NC4_L        | S [7:0]           |                   |                   |          |

| 37       |                                                                    | NC5_LS [19:16]    |    |              |                   |                   |                   |          |

| 38       |                                                                    |                   |    |              | S [15:8]          |                   |                   |          |

| 39       |                                                                    |                   |    | NC5_L        | S [7:0]           |                   |                   |          |

| 40       | N2_HS [2:0]                                                        |                   |    |              |                   | N2_LS             | [19:16]           |          |

| 41       |                                                                    |                   |    | N2_LS        | S [15:8]          |                   |                   |          |

| 42       |                                                                    |                   |    | N2_LS        | S [7:0]           |                   |                   |          |

| 43       |                                                                    |                   |    |              |                   |                   | N31_ [18:16]      |          |

| 44       |                                                                    |                   |    | N31_         | [15:8]            |                   |                   |          |

| 45       |                                                                    | N31_ [7:0]        |    |              |                   |                   |                   |          |

| 46       |                                                                    |                   |    |              |                   |                   | N32_ [18:16]      |          |

| 47       |                                                                    | N31_ [15:8]       |    |              |                   |                   |                   |          |

| 48       |                                                                    |                   |    | N32_         | _[7:0]            |                   |                   |          |

| 49       |                                                                    |                   |    |              |                   |                   | N33_[18:16]       |          |

| 50       |                                                                    |                   |    | N33_         | [15:8]            |                   |                   |          |

| 51       |                                                                    |                   |    |              | _[7:0]            |                   |                   |          |

| 52       |                                                                    |                   |    |              |                   |                   | N34_[18:16]       |          |

| 53       |                                                                    |                   |    | N34          | <br>[15:8]        |                   |                   |          |

| 54       |                                                                    |                   |    |              | _[7:0]            |                   |                   |          |

| 55       |                                                                    |                   | С  | LKIN2RATE_[2 |                   | С                 | LKIN1RATE[2:      | 01       |

| 56       | CLKIN4RATE_[2:0] CLKIN3RATE[2:0]  CLKIN4RATE_[2:0] CLKIN3RATE[2:0] |                   |    |              |                   |                   |                   |          |

| 128      |                                                                    |                   |    |              | CK4_ACT-<br>V_REG | CK3_ACT-<br>V_REG | CK2_ACT-<br>V_REG | CK1_ACT  |

| 129      |                                                                    |                   |    | LOS4_INT     | LOS3_INT          | LOS2_INT          | LOS1_INT          | LOSX_INT |

| 130      |                                                                    | DIGHOLD-<br>VALID |    | FOS4_INT     | FOS3_INT          | FOS2_INT          | FOS1_INT          | LOL_INT  |

| 131      |                                                                    |                   |    | LOS4_FLG     | LOS3_FLG          | LOS2_FLG          | LOS1_FLG          | LOSX_FL0 |

# Si5369

| Register | D7                     | D6                | D5               | D4               | D3               | D2               | D1               | D0               |  |

|----------|------------------------|-------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|

| 132      |                        |                   | FOS4_FLG         | FOS3_FLG         | FOS2_FLG         | FOS1_FLG         | LOL_FLG          |                  |  |

| 134      |                        | PARTNUM_RO [11:4] |                  |                  |                  |                  |                  |                  |  |

| 135      |                        | PARTNUN           | /_RO [3:0]       |                  |                  | REVID_           | RO [3:0]         |                  |  |

| 136      | RST_REG                | ICAL              |                  |                  |                  |                  |                  |                  |  |

| 137      |                        |                   |                  |                  |                  |                  |                  | FASTLOCK         |  |

| 138      |                        |                   |                  |                  | LOS4_EN<br>[1:1] | LOS3_EN<br>[1:1] | LOS2_EN<br>[1:1] | LOS1_EN<br>[1:1] |  |

| 139      | LOS4_EN<br>[0:0]       | LOS3_EN<br>[0:0]  | LOS2_EN<br>[0:0] | LOS1_EN<br>[0:0] | FOS4_EN          | FOS3_EN          | FOS2_EN          | FOS1_EN          |  |

| 140      |                        |                   |                  | INDEPENDEN       | ITSKEW1 [7:0]    |                  |                  |                  |  |

| 141      | INDEPENDENTSKEW2 [7:0] |                   |                  |                  |                  |                  |                  |                  |  |

| 142      | INDEPENDENTSKEW3 [7:0] |                   |                  |                  |                  |                  |                  |                  |  |

| 143      | INDEPENDENTSKEW4 [7:0] |                   |                  |                  |                  |                  |                  |                  |  |

| 144      |                        |                   |                  | INDEPENDEN       | ITSKEW5 [7:0]    |                  |                  |                  |  |

# 5. Register Descriptions

## Register 0.

| Bit  | D7 | D6       | D5              | D4 | D3 | D2 | D1         | D0 |

|------|----|----------|-----------------|----|----|----|------------|----|

| Name |    | FREE_RUN | CKOUT_ALWAYS_ON |    |    |    | BYPASS_REG |    |

| Туре | R  | R/W      | R/W             | R  | R  | R  | R/W        | R  |

Reset value = 0001 0100

| Bit | Name            | Function                                                                                                                                                                                                                                                                                                          |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Reserved        |                                                                                                                                                                                                                                                                                                                   |

| 6   | FREE_RUN        | Free Run. Internal to the device, route XA/XB to CKIN2. This allows the device to lock to its external reference.  0: Disable Free Run  1: Enable                                                                                                                                                                 |

| 5   | CKOUT_ALWAYS_ON | CKOUT Always On. This will bypass the SQ_ICAL function. Output will be available even if SQ_ICAL is on and ICAL is not complete or successful. See Table 8.  0: Squelch output until part is calibrated (ICAL).  1: Provide an output. Note: The frequency may be significantly off until the part is calibrated. |

| 4:2 | Reserved        |                                                                                                                                                                                                                                                                                                                   |

| 1   | BYPASS_REG      | Bypass Register. This bit enables or disables the PLL bypass mode. Use is only valid when the part is in digital hold or before the first ICAL.  0: Normal operation  1: Bypass mode. Selected input clock is connected to CKOUT buffers, bypassing PLL.                                                          |

| 0   | Reserved        |                                                                                                                                                                                                                                                                                                                   |