Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Si8630/31/35 Data Sheet

## Low-Power Triple-Channel Digital Isolators

Silicon Lab's family of ultra-low-power digital isolators are CMOS devices offering substantial data rate, propagation delay, power, size, reliability, and external BOM advantages over legacy isolation technologies. The operating parameters of these products remain stable across wide temperature ranges and throughout device service life for ease of design and highly uniform performance. All device versions have Schmitt trigger inputs for high noise immunity and only require VDD bypass capacitors.

Data rates up to 150 Mbps are supported, and all devices achieve propagation delays of less than 10 ns. Enable inputs provide a single point control for enabling and disabling output drive. Ordering options include a choice of isolation ratings (2.5, 3.75 and 5 kV) and a selectable fail-safe operating mode to control the default output state during power loss. All products are safety certified by UL, CSA, VDE, and CQC, and products in wide-body packages support reinforced insulation withstanding up to 5 kV<sub>RMS</sub>.

## **Applications**

- · Industrial automation systems

- · Medical electronics

- · Hybrid electric vehicles

- · Isolated switch mode supplies

- · Isolated ADC, DAC

- · Motor control

- Power inverters

- · Communications systems

## Safety Regulatory Approvals

- · UL 1577 recognized

- Up to 5000 V<sub>RMS</sub> for 1 minute

- CSA component notice 5A approval

- IEC 60950-1, 61010-1, 60601-1 (reinforced insulation)

- · VDE certification conformity

- Si863xxT options certified to reinforced VDE 0884-10

- All other options certified to IEC 60747-5-5 and reinforced 60950-1

- · CQC certification approval

- GB4943.1

#### **KEY FEATURES**

- · High-speed operation

- DC to 150 Mbps

- · No start-up initialization required

- Wide Operating Supply Voltage2.5–5.5 V

- Up to 5000 V<sub>RMS</sub> isolation

- Reinforced VDE 0884-10, 10 kV surgecapable (Si863xxT)

- · 60-year life at rated working voltage

- · High electromagnetic immunity

- · Ultra low power (typical)

#### 5 V Operation

- 1.6 mA per channel at 1 Mbps

- 5.5 mA per channel at 100 Mbps

#### 2.5 V Operation

- 1.5 mA per channel at 1 Mbps

- 3.5 mA per channel at 100 Mbps

- Tri-state outputs with ENABLE

- · Schmitt trigger inputs

- Selectable fail-safe mode

- Default high or low output (ordering option)

- Precise timing (typical)

- 10 ns propagation delay

- 1.5 ns pulse width distortion

- 0.5 ns channel-channel skew

- 2 ns propagation delay skew

- 5 ns minimum pulse width

- Transient Immunity 50 kV/µs

- AEC-Q100 qualification

- Wide temperature range

- -40 to 125 °C

- · RoHS-compliant packages

- SOIC-16 wide body

- SOIC-16 narrow body

## 1. Ordering Guide

Table 1.1. Ordering Guide for Valid OPNs<sup>1, 2</sup>

| Ordering Part Number (OPN)   | Number of<br>Inputs<br>VDD1 Side | Number of<br>Inputs<br>VDD2 Side | Max Data<br>Rate<br>(Mbps) | Default<br>Output<br>State | Isolation<br>Rating<br>(kVrms) | Temp Range (°C) | Package    |

|------------------------------|----------------------------------|----------------------------------|----------------------------|----------------------------|--------------------------------|-----------------|------------|

| Si8630BB-B-IS                | 3                                | 0                                | 150                        | Low                        | 2.5                            | –40 to +125 °C  | WB SOIC-16 |

| Si8630BB-B-IS1               | 3                                | 0                                | 150                        | Low                        | 2.5                            | –40 to +125 °C  | NB SOIC-16 |

| Si8630BC-B-IS1               | 3                                | 0                                | 150                        | Low                        | 3.75                           | –40 to +125 °C  | NB SOIC-16 |

| Si8630EC-B-IS1               | 3                                | 0                                | 150                        | High                       | 3.75                           | –40 to +125 °C  | NB SOIC-16 |

| Si8630BD-B-IS                | 3                                | 0                                | 150                        | Low                        | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Si8630ED-B-IS                | 3                                | 0                                | 150                        | High                       | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Si8631BB-B-IS                | 2                                | 1                                | 150                        | Low                        | 2.5                            | –40 to +125 °C  | WB SOIC-16 |

| Si8631BB-B-IS1               | 2                                | 1                                | 150                        | Low                        | 2.5                            | –40 to +125 °C  | NB SOIC-16 |

| Si8631BC-B-IS1               | 2                                | 1                                | 150                        | Low                        | 3.75                           | –40 to +125 °C  | NB SOIC-16 |

| Si8631EC-B-IS1               | 2                                | 1                                | 150                        | High                       | 3.75                           | –40 to +125 °C  | NB SOIC-16 |

| Si8631BD-B-IS                | 2                                | 1                                | 150                        | Low                        | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Si8631ED-B-IS                | 2                                | 1                                | 150                        | High                       | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Si8635BB-B-IS                | 3                                | 0                                | 150                        | Low                        | 2.5                            | –40 to +125 °C  | WB SOIC-16 |

| Si8635BC-B-IS1               | 3                                | 0                                | 150                        | Low                        | 3.75                           | –40 to +125 °C  | NB SOIC-16 |

| Si8635BD-B-IS                | 3                                | 0                                | 150                        | Low                        | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Product Options with Reinfor | ced VDE 088                      | 4-10 Rating v                    | with 10 kV Su              | rge Capabil                | ity                            |                 |            |

| Si8630BT-IS                  | 3                                | 0                                | 150                        | Low                        | 5.0                            | -40 to +125 °C  | WB SOIC-16 |

| Si8630ET-IS                  | 3                                | 0                                | 150                        | High                       | 5.0                            | -40 to +125 °C  | WB SOIC-16 |

| Si8631BT-IS                  | 2                                | 1                                | 150                        | Low                        | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Si8631ET-IS                  | 2                                | 1                                | 150                        | High                       | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

| Si8635BT-IS                  | 3                                | 0                                | 150                        | Low                        | 5.0                            | -40 to +125 °C  | WB SOIC-16 |

| Si8635ET-IS                  | 3                                | 0                                | 150                        | High                       | 5.0                            | –40 to +125 °C  | WB SOIC-16 |

- 1. All packages are RoHS-compliant with peak reflow temperatures of 260 °C according to the JEDEC industry standard classifications and peak solder temperatures.

- 2. "Si" and "SI" are used interchangeably.

- 3. An "R" at the end of the part number denotes tape and reel packaging option.

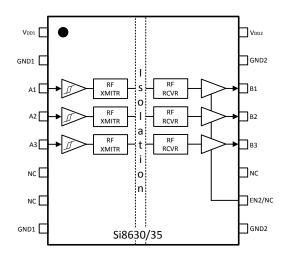

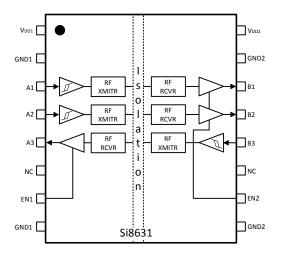

## 2. System Overview

## 2.1 Theory of Operation

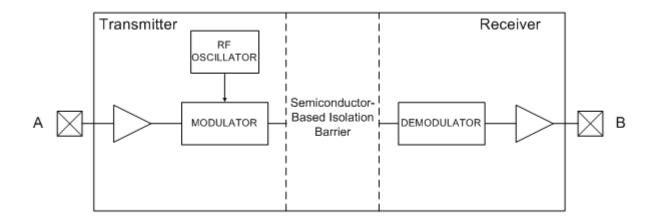

The operation of an Si863x channel is analogous to that of an opto coupler, except an RF carrier is modulated instead of light. This simple architecture provides a robust isolated data path and requires no special considerations or initialization at start-up. A simplified block diagram for a single Si863x channel is shown in the figure below.

Figure 2.1. Simplified Channel Diagram

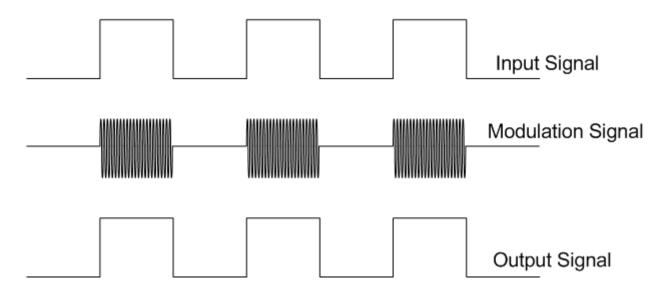

A channel consists of an RF Transmitter and RF Receiver separated by a semiconductor-based isolation barrier. Referring to the transmitter, input A modulates the carrier provided by an RF oscillator using on/off keying. The Receiver contains a demodulator that decodes the input state according to its RF energy content and applies the result to output B via the output driver. This RF on/off keying scheme is superior to pulse code schemes as it provides best-in-class noise immunity, low power consumption, and improved immunity to magnetic fields. See the following figure for more details.

Figure 2.2. Modulation Scheme

## 2.2 Eye Diagram

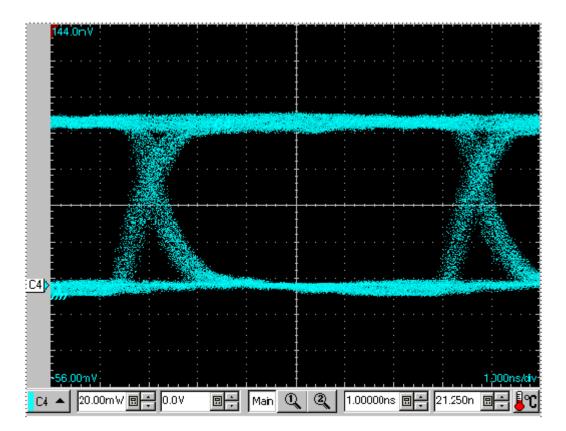

The figure below illustrates an eye diagram taken on an Si8630. For the data source, the test used an Anritsu (MP1763C) Pulse Pattern Generator set to 1000 ns/div. The output of the generator's clock and data from an Si8630 were captured on an oscilloscope. The results illustrate that data integrity was maintained even at the high data rate of 150 Mbps. The results also show that 2 ns pulse width distortion and 350 ps peak jitter were exhibited.

Figure 2.3. Eye Diagram

## 3. Device Operation

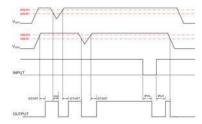

Device behavior during start-up, normal operation, and shutdown is shown in Figure 3.1 Device Behavior during Normal Operation on page 6, where UVLO+ and UVLO- are the respective positive-going and negative-going thresholds. Refer to the following tables to determine outputs when power supply (VDD) is not present and for logic conditions when enable pins are used.

Table 3.1. Si86xx Logic Operation

| V <sub>I</sub> Input <sup>1, 2</sup> | EN Input <sup>1, 2, 3, 4</sup> | VDDI State <sup>1, 5, 6</sup> | VDDO State <sup>1, 5, 6</sup> | V <sub>O</sub> Output <sup>1, 2</sup> | Comments                                                                                                                                                                                                                                               |

|--------------------------------------|--------------------------------|-------------------------------|-------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Н                                    | H or NC                        | Р                             | Р                             | Н                                     | Enabled, normal operation.                                                                                                                                                                                                                             |

| L                                    | H or NC                        | Р                             | Р                             | L                                     |                                                                                                                                                                                                                                                        |

| X <sup>7</sup>                       | L                              | Р                             | Р                             | Hi-Z <sup>8</sup>                     | Disabled.                                                                                                                                                                                                                                              |

| X <sup>7</sup>                       | H or NC                        | UP                            | Р                             | L <sup>9</sup>                        | Upon transition of VDDI from unpowered to powered, $V_O$ returns to the same state as $V_I$ in less than 1 $\mu$ s.                                                                                                                                    |

| X <sup>7</sup>                       | L                              | UP                            | Р                             | Hi-Z <sup>8</sup>                     | Disabled.                                                                                                                                                                                                                                              |

| X <sup>7</sup>                       | X <sup>7</sup>                 | Р                             | UP                            | Undetermined                          | Upon transition of VDDO from unpowered to powered, VO returns to the same state as $V_I$ within 1 $\mu$ s, if EN is in either the H or NC state. Upon transition of VDDO from unpowered to powered, $V_O$ returns to Hi-Z within 1 $\mu$ s if EN is L. |

#### Note

- 1. VDDI and VDDO are the input and output power supplies. V<sub>I</sub> and V<sub>O</sub> are the respective input and output terminals. EN is the enable control input located on the same output side.

- 2. X = not applicable; H = Logic High; L = Logic Low; Hi-Z = High Impedance.

- 3. It is recommended that the enable inputs be connected to an external logic high or low level when the Si86xx is operating in noisy environments.

- 4. No Connect (NC) replaces EN1 on Si8630/35. No Connect replaces EN2 on the Si8635. No Connects are not internally connected and can be left floating, tied to VDD, or tied to GND.

- 5. "Powered" state (P) is defined as 2.5 V < VDD < 5.5 V.

- 6. "Unpowered" state (UP) is defined as VDD = 0 V.

- 7. Note that an I/O can power the die for a given side through an internal diode if its source has adequate current.

- 8. When using the enable pin (EN) function, the output pin state is driven into a high-impedance state when the EN pin is disabled (EN = 0).

- 9. See Ordering Guide for details. This is the selectable fail-safe operating mode (ordering option). Some devices have default output state = H, and some have default output state = L, depending on the ordering part number (OPN). For default high devices, the data channels have pull-ups on inputs/outputs. For default low devices, the data channels have pull-downs on inputs/outputs.

Table 3.2. Enable Input Truth

| Part Number | EN1 <sup>1, 2</sup> | EN2 <sup>1, 2</sup> | Operation                                                                 |

|-------------|---------------------|---------------------|---------------------------------------------------------------------------|

| Si8630      | _                   | Н                   | Outputs B1, B2, B3 are enabled and follow input state.                    |

|             | <del></del>         | L                   | Outputs B1, B2, B3 are disabled and in high impedance state. <sup>3</sup> |

| Si8631      | Н                   | Х                   | Output A3 enabled and follows the input state.                            |

|             | L                   | Х                   | Output A3 disabled and in high impedance state. <sup>3</sup>              |

|             | Х                   | Н                   | Outputs B1, B2 are enabled and follow the input state.                    |

|             | Х                   | L                   | Outputs B1, B2 are disabled and in high impedance state. <sup>3</sup>     |

| Si8635      | _                   | _                   | Outputs B1, B2, B3 are enabled and follow the input state.                |

- 1. Enable inputs EN1 and EN2 can be used for multiplexing, for clock sync, or other output control. These inputs are internally pulled-up to local VDD allowing them to be connected to an external logic level (high or low) or left floating. To minimize noise coupling, do not connect circuit traces to EN1 or EN2 if they are left floating. If EN1, EN2 are unused, it is recommended they be connected to an external logic level, especially if the Si86xx is operating in a noisy environment.

- 2. X = not applicable; H = Logic High; L = Logic Low.

- 3. When using the enable pin (EN) function, the output pin state is driven into a high-impedance state when the EN pin is disabled (EN = 0).

#### 3.1 Device Startup

Outputs are held low during powerup until VDD is above the UVLO threshold for time period tSTART. Following this, the outputs follow the states of inputs.

#### 3.2 Undervoltage Lockout

Undervoltage Lockout (UVLO) is provided to prevent erroneous operation during device startup and shutdown or when VDD is below its specified operating circuits range. Both Side A and Side B each have their own undervoltage lockout monitors. Each side can enter or exit UVLO independently. For example, Side A unconditionally enters UVLO when  $V_{DD1}$  falls below  $V_{DD1(UVLO-)}$  and exits UVLO when  $V_{DD1}$  rises above  $V_{DD1(UVLO+)}$ . Side B operates the same as Side A with respect to its  $V_{DD2}$  supply.

Figure 3.1. Device Behavior during Normal Operation

#### 3.3 Layout Recommendations

To ensure safety in the end-user application, high-voltage circuits (i.e., circuits with  $>30 \text{ V}_{AC}$ ) must be physically separated from the safety extra-low-voltage circuits (SELV is a circuit with  $<30 \text{ V}_{AC}$ ) by a certain distance (creepage/clearance). If a component, such as a digital isolator, straddles this isolation barrier, it must meet those creepage/clearance requirements and also provide a sufficiently large high-voltage breakdown protection rating (commonly referred to as working voltage protection). Table 4.6 Insulation and Safety-Related Specifications on page 19 and Table 4.8 IEC 60747-5-5 Insulation Characteristics for Si86xxxx  $^1$  on page 20 detail the working voltage and creepage/clearance capabilities of the Si86xx. These tables also detail the component standards (UL1577, IEC60747, CSA 5A), which are readily accepted by certification bodies to provide proof for end-system specifications requirements. Refer to the end-system specification (61010-1, 60950-1, 60601-1, etc.) requirements before starting any design that uses a digital isolator.

## 3.3.1 Supply Bypass

The Si863x family requires a 0.1  $\mu$ F bypass capacitor between  $V_{DD1}$  and GND1 and  $V_{DD2}$  and GND2. The capacitor should be placed as close as possible to the package. To enhance the robustness of a design, the user may also include resistors (50–300  $\Omega$ ) in series with the inputs and outputs if the system is excessively noisy.

## 3.3.2 Output Pin Termination

The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ ,  $\pm$ 40%, which is a combination of the value of the onchip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled impedance PCB traces.

## 3.4 Fail-Safe Operating Mode

Si86xx devices feature a selectable (by ordering option) mode whereby the default output state (when the input supply is unpowered) can either be a logic high or logic low when the output supply is powered. See Table 3.1 Si86xx Logic Operation on page 4 and 1. Ordering Guide for more information.

## 3.5 Typical Performance Characteristis

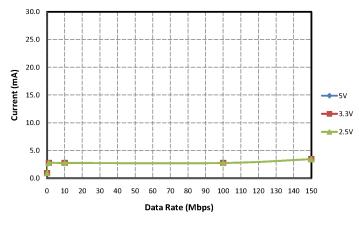

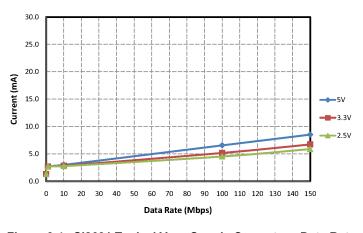

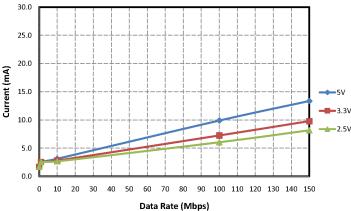

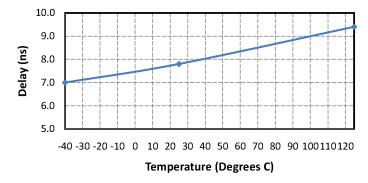

The typical performance characteristics depicted in the following diagrams are for information purposes only. Refer to 4. Electrical Specifications for actual specification limits.

30.0 25.0 20.0 15.0 10.0 0 10 20 30 40 50 60 70 80 90 100 110 120 130 140 150 Data Rate (Mbps)

Figure 3.2. Si8630/35 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation

Figure 3.3. Si8630/35 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation (15 pF Load)

Figure 3.4. Si8631 Typical V<sub>DD1</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation

Figure 3.5. Si8631 Typical V<sub>DD2</sub> Supply Current vs. Data Rate 5, 3.3, and 2.5 V Operation (15 pF Load)

Figure 3.6. Propagation Delay vs. Temperature (5.0 V Data)

# 4. Electrical Specifications

**Table 4.1. Recommended Operating Conditions**

| Parameter                                  | Symbol           | Min | Тур | Max              | Unit |

|--------------------------------------------|------------------|-----|-----|------------------|------|

| Ambient Operating Temperature <sup>1</sup> | T <sub>A</sub>   | -40 | 25  | 125 <sup>1</sup> | °C   |

| Supply Voltage                             | V <sub>DD1</sub> | 2.5 | _   | 5.5              | V    |

|                                            | V <sub>DD2</sub> | 2.5 | _   | 5.5              | V    |

Table 4.2. Electrical Characteristics <sup>1</sup>

| Parameter                               | Symbol                              | Test Condition                              | Min                                       | Тур  | Max   | Unit |

|-----------------------------------------|-------------------------------------|---------------------------------------------|-------------------------------------------|------|-------|------|

| VDD Undervoltage Threshold              | VDD <sub>UV+</sub>                  | V <sub>DD1</sub> , V <sub>DD2</sub> rising  | 1.95                                      | 2.24 | 2.375 | V    |

| VDD Undervoltage Threshold              | VDD <sub>UV</sub>                   | V <sub>DD1</sub> , V <sub>DD2</sub> falling | 1.88                                      | 2.16 | 2.325 | V    |

| VDD Undervoltage Hysteresis             | VDD <sub>HYS</sub>                  |                                             | 50                                        | 70   | 95    | mV   |

| Positive-Going Input Threshold          | VT+                                 | All inputs rising                           | 1.4                                       | 1.67 | 1.9   | V    |

| Negative-Going Input Threshold          | VT-                                 | All inputs falling                          | 1.0                                       | 1.23 | 1.4   | V    |

| Input Hysteresis                        | V <sub>HYS</sub>                    |                                             | 0.38                                      | 0.44 | 0.50  | V    |

| High Level Input Voltage                | V <sub>IH</sub>                     |                                             | 2.0                                       | _    | _     | V    |

| Low Level Input Voltage                 | V <sub>IL</sub>                     |                                             | _                                         | _    | 0.8   | V    |

| High Level Output Voltage               | V <sub>OH</sub>                     | loh = –4 mA                                 | V <sub>DD1</sub> , V <sub>DD2</sub> – 0.4 | 4.8  | _     | V    |

| Low Level Output Voltage                | V <sub>OL</sub>                     | IoI = 4 mA                                  | _                                         | 0.2  | 0.4   | V    |

| Input Leakage Current                   |                                     |                                             |                                           |      |       |      |

| Si863xxA/B/C/D                          | ΙL                                  |                                             | _                                         | _    | ±10   | μΑ   |

| Si863xxT                                |                                     |                                             | _                                         | _    | ±15   |      |

| Output Impedance <sup>2</sup>           | Z <sub>O</sub>                      |                                             | _                                         | 50   | _     | Ω    |

| Enable Input Current                    |                                     |                                             |                                           |      |       |      |

| Si863xxA/B/C/D                          | I <sub>ENH</sub> , I <sub>ENL</sub> | $V_{ENx} = V_{IH}$ or $V_{IL}$              | _                                         | 2.0  | _     | μΑ   |

| Si863xxT                                |                                     |                                             | _                                         | 10.0 | _     |      |

| DC Supply Current (All Inputs 0 V or at | Supply)                             |                                             |                                           |      |       |      |

| Si8630Bx, Ex, Si8635Bx                  |                                     |                                             |                                           |      |       |      |

| $V_{DD1}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 0.9  | 1.6   |      |

| $V_{DD2}$                               |                                     | $V_1 = 0(Bx), 1(Ex)$                        | _                                         | 1.9  | 3.0   | mA   |

| $V_{DD1}$                               |                                     | $V_1 = 1(Bx), 0(Ex)$                        | _                                         | 4.6  | 7.4   |      |

| $V_{DD2}$                               |                                     | $V_1 = 1(Bx), 0(Ex)$                        | _                                         | 1.9  | 3.0   |      |

<sup>1.</sup> The maximum ambient temperature is dependent on data frequency, output loading, number of operating channels, and supply voltage.

| Parameter                              | Symbol                              | Test Condition                                        | Min    | Тур  | Max  | Unit |

|----------------------------------------|-------------------------------------|-------------------------------------------------------|--------|------|------|------|

| Si8631Bx, Ex                           |                                     |                                                       |        |      |      |      |

| V <sub>DD1</sub>                       |                                     | $V_I = 0(Bx), 1(Ex)$                                  | _      | 1.3  | 2.1  |      |

| $V_{DD2}$                              |                                     | $V_1 = 0(Bx), 1(Ex)$                                  | _      | 1.7  | 2.7  | mA   |

| V <sub>DD1</sub>                       |                                     | $V_1 = 1(Bx), 0(Ex)$                                  | _      | 3.9  | 5.9  |      |

| $V_{DD2}$                              |                                     | $V_1 = 1(Bx), 0(Ex)$                                  | _      | 3.0  | 4.5  |      |

| 1 Mbps Supply Current (All Inputs = 50 | 0 kHz Squar                         | e Wave, CI = 15 pF on All Outp                        | uts)   |      |      |      |

| Si8630Bx, Ex, Si8635Bx                 |                                     |                                                       |        |      |      |      |

| V <sub>DD1</sub>                       |                                     |                                                       | _      | 2.8  | 3.9  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 2.2  | 3.1  |      |

| Si8631Bx, Ex                           |                                     |                                                       |        |      |      |      |

| V <sub>DD1</sub>                       |                                     |                                                       | _      | 2.7  | 3.8  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 2.6  | 3.6  |      |

| 10 Mbps Supply Current (All Inputs = 5 | MHz Square                          | Wave, CI = 15 pF on All Outpu                         | uts)   |      |      |      |

| Si8630Bx, Ex, Si8635Bx                 |                                     |                                                       |        |      |      |      |

| V <sub>DD1</sub>                       |                                     |                                                       | _      | 2.8  | 3.9  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 3.1  | 4.3  |      |

| Si8631Bx, Ex                           |                                     |                                                       |        |      |      |      |

| V <sub>DD1</sub>                       |                                     |                                                       | _      | 3.0  | 4.2  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 3.1  | 4.4  |      |

| 100 Mbps Supply Current (All Inputs =  | 50 MHz Squa                         | are Wave, CI = 15 pF on All Ou                        | tputs) |      |      |      |

| Si8630Bx, Ex, Si8635Bx                 |                                     |                                                       |        |      |      |      |

| $V_{DD1}$                              |                                     |                                                       | _      | 2.8  | 3.9  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 13.2 | 17.8 |      |

| Si8631Bx, Ex                           |                                     |                                                       |        |      |      |      |

| $V_{DD1}$                              |                                     |                                                       | _      | 6.6  | 8.8  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 9.9  | 13.4 |      |

| Timing Characteristics                 |                                     |                                                       |        |      |      |      |

| Si863xBx, Ex                           |                                     |                                                       |        |      |      |      |

| Maximum Data Rate                      |                                     |                                                       | 0      | _    | 150  | Mbps |

| Minimum Pulse Width                    |                                     |                                                       | _      | _    | 5.0  | ns   |

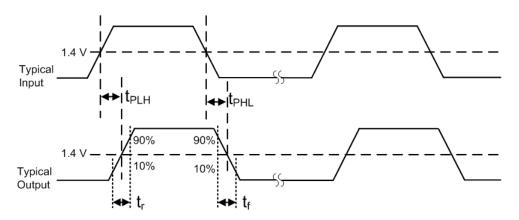

| Propagation Delay                      | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 4.2 Propagation<br>Delay Timing on page 11 | 5.0    | 8.0  | 13   | ns   |

| Pulse Width Distortion                 | PWD                                 | See Figure 4.2 Propagation                            | _      | 0.2  | 4.5  | ne   |

| tPLH - tPHL                            | FVVD                                | Delay Timing on page 11                               |        | 0.2  | 4.0  | ns   |

| Propagation Delay Skew <sup>3</sup>    | t <sub>PSK(P-P)</sub>               |                                                       | _      | 2.0  | 4.5  | ns   |

| Channel-Channel Skew                   | t <sub>PSK</sub>                    |                                                       | _      | 0.4  | 2.5  | ns   |

| Parameter                                | Symbol               | Test Condition                                                   | Min | Тур | Max | Unit  |

|------------------------------------------|----------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| All Models                               |                      |                                                                  |     |     |     |       |

|                                          |                      | C <sub>L</sub> = 15 pF                                           |     |     |     |       |

| Output Rise Time                         | t <sub>r</sub>       | See Figure 4.2 Propagation<br>Delay Timing on page 11            | _   | 2.5 | 4.0 | ns    |

|                                          |                      | C <sub>L</sub> = 15 pF                                           |     |     |     |       |

| Output Fall Time                         | t <sub>f</sub>       | See Figure 4.2 Propagation<br>Delay Timing on page 11            | _   | 2.5 | 4.0 | ns    |

| Peak Eye Diagram Jitter                  | t <sub>JIT(PK)</sub> | See Figure 2.3 Eye Diagram on page 3                             | _   | 350 | _   | ps    |

|                                          |                      | $V_I = V_{DD}$ or 0 V                                            |     |     |     |       |

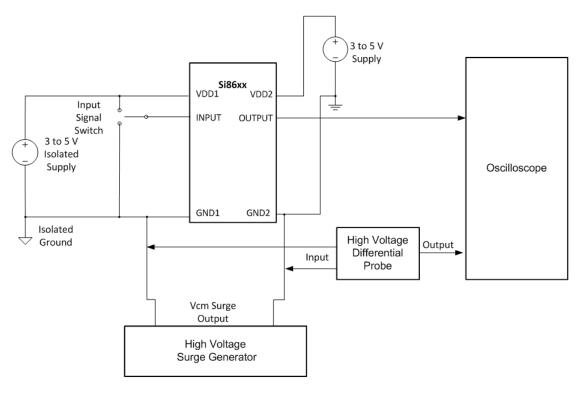

| Common Mode Transient Immunity           | 01.471               | V <sub>CM</sub> = 1500 V                                         |     |     |     | 12.4  |

| Si86xxxB/C/D                             | CMTI                 | See Figure 4.3 Common-<br>Mode Transient Immunity Test           | 35  | 50  | _   | kV/μs |

| Si86xxxT                                 |                      | Circuit on page 11                                               | 60  | 100 | _   |       |

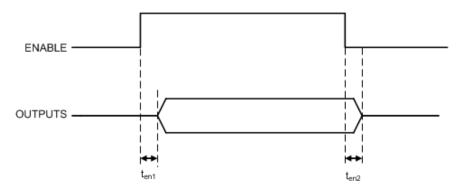

| Enable to Data Valid                     | t <sub>en1</sub>     | See Figure 4.1 ENABLE Timing Diagram on page 11                  | _   | 6.0 | 11  | ns    |

| Enable to Data Tri-State                 | t <sub>en2</sub>     | See Figure 4.1 ENABLE Timing Diagram on page 11                  | _   | 8.0 | 12  | ns    |

| Input power loss to valid default output | t <sub>SD</sub>      | See Figure 3.1 Device Behavior during Normal Operation on page 6 | _   | 8.0 | 12  | ns    |

| Start-up Time <sup>4</sup>               | t <sub>SU</sub>      |                                                                  | _   | 15  | 40  | μs    |

- 1.  $V_{DD1}$  = 5 V ±10%;  $V_{DD2}$  = 5 V ±10%,  $T_A$  = -40 to 125 °C

- 2. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ , ±40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled-impedance PCB traces.

- 3. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

- 4. Start-up time is the time period from the application of power to the appearance of valid data at the output.

Figure 4.1. ENABLE Timing Diagram

Figure 4.2. Propagation Delay Timing

Figure 4.3. Common-Mode Transient Immunity Test Circuit

Table 4.3. Electrical Characteristics <sup>1</sup>

| Parameter                               | Symbol                              | Test Condition                              | Min                                       | Тур  | Max   | Unit |

|-----------------------------------------|-------------------------------------|---------------------------------------------|-------------------------------------------|------|-------|------|

| VDD Undervoltage Threshold              | VDD <sub>UV+</sub>                  | V <sub>DD1</sub> , V <sub>DD2</sub> rising  | 1.95                                      | 2.24 | 2.375 | V    |

| VDD Undervoltage Threshold              | VDD <sub>UV</sub> _                 | V <sub>DD1</sub> , V <sub>DD2</sub> falling | 1.88                                      | 2.16 | 2.325 | V    |

| VDD Undervoltage Hysteresis             | VDD <sub>HYS</sub>                  |                                             | 50                                        | 70   | 95    | mV   |

| Positive-Going Input Threshold          | VT+                                 | All inputs rising                           | 1.4                                       | 1.67 | 1.9   | V    |

| Negative-Going Input Threshold          | VT-                                 | All inputs falling                          | 1.0                                       | 1.23 | 1.4   | V    |

| Input Hysteresis                        | V <sub>HYS</sub>                    |                                             | 0.38                                      | 0.44 | 0.50  | V    |

| High Level Input Voltage                | V <sub>IH</sub>                     |                                             | 2.0                                       | _    | _     | V    |

| Low Level Input Voltage                 | V <sub>IL</sub>                     |                                             | _                                         | _    | 0.8   | V    |

| High Level Output Voltage               | V <sub>OH</sub>                     | loh = –4 mA                                 | V <sub>DD1</sub> , V <sub>DD2</sub> – 0.4 | 3.1  | _     | V    |

| Low Level Output Voltage                | V <sub>OL</sub>                     | IoI = 4 mA                                  | _                                         | 0.2  | 0.4   | V    |

| Input Leakage Current                   |                                     |                                             |                                           |      |       |      |

| Si863xxA/B/C/D                          | IL                                  |                                             | _                                         | _    | ±10   | μA   |

| Si863xxT                                |                                     |                                             | _                                         | _    | ±15   |      |

| Output Impedance <sup>2</sup>           | Z <sub>O</sub>                      |                                             | _                                         | 50   | _     | Ω    |

| Enable Input Current                    |                                     |                                             |                                           |      |       |      |

| Si863xxA/B/C/D                          | I <sub>ENH</sub> , I <sub>ENL</sub> | $V_{ENx} = V_{IH}$ or $V_{IL}$              | _                                         | 2.0  | _     | μA   |

| Si863xxT                                |                                     |                                             | _                                         | 10.0 | _     |      |

| DC Supply Current (All Inputs 0 V or at | Supply)                             |                                             |                                           |      | 1     |      |

| Si8630Bx, Ex, Si8635Bx                  |                                     |                                             |                                           |      |       |      |

| $V_{DD1}$                               |                                     | $V_1 = 0(Bx), 1(Ex)$                        | _                                         | 0.9  | 1.6   |      |

| $V_{DD2}$                               |                                     | $V_1 = 0(Bx), 1(Ex)$                        | _                                         | 1.9  | 3.0   | mA   |

| $V_{DD1}$                               |                                     | $V_{I} = 1(Bx), 0(Ex)$                      | _                                         | 4.6  | 7.4   |      |

| $V_{DD2}$                               |                                     | $V_I = 1(Bx), 0(Ex)$                        | _                                         | 1.9  | 3.0   |      |

| Si8631Bx, Ex                            |                                     |                                             |                                           |      |       |      |

| $V_{DD1}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 1.3  | 2.1   |      |

| $V_{DD2}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 1.7  | 2.7   | mA   |

| V <sub>DD1</sub>                        |                                     | $V_1 = 1(Bx), 0(Ex)$                        | _                                         | 3.9  | 5.9   |      |

| $V_{DD2}$                               |                                     | $V_1 = 1(Bx), 0(Ex)$                        | _                                         | 3.0  | 4.5   |      |

| 1 Mbps Supply Current (All Inputs = 50  | ⊥<br>0 kHz Square                   |                                             | outs)                                     |      |       |      |

| Si8630Bx, Ex, Si8635Bx                  |                                     | · ·                                         |                                           |      |       |      |

| V <sub>DD1</sub>                        |                                     |                                             | _                                         | 2.8  | 3.9   | mA   |

| $V_{DD2}$                               |                                     |                                             |                                           | 2.2  | 3.1   |      |

| Parameter                              | Symbol                              | Test Condition                                        | Min    | Тур | Max  | Unit |

|----------------------------------------|-------------------------------------|-------------------------------------------------------|--------|-----|------|------|

| Si8631Bx, Ex                           |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                              |                                     |                                                       | _      | 2.7 | 3.8  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 2.6 | 3.6  |      |

| 10 Mbps Supply Current (All Inputs = 5 | MHz Square                          | ·<br>• Wave, CI = 15 pF on All Outpo                  | uts)   |     |      |      |

| Si8630Bx, Ex, Si8635Bx                 |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                              |                                     |                                                       | _      | 2.8 | 3.9  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 2.6 | 3.6  |      |

| Si8631Bx, Ex                           |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                              |                                     |                                                       | _      | 2.8 | 4.0  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 2.6 | 3.9  |      |

| 100 Mbps Supply Current (All Inputs =  | 50 MHz Squ                          | are Wave, CI = 15 pF on All Ou                        | tputs) |     |      |      |

| Si8630Bx, Ex, Si8635Bx                 |                                     |                                                       |        |     |      |      |

| V <sub>DD1</sub>                       |                                     |                                                       | _      | 2.8 | 3.9  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 9.3 | 12.5 |      |

| Si8631Bx, Ex                           |                                     |                                                       |        |     |      |      |

| V <sub>DD1</sub>                       |                                     |                                                       | _      | 5.2 | 7.0  | mA   |

| $V_{DD2}$                              |                                     |                                                       | _      | 7.3 | 9.8  |      |

| Timing Characteristics                 | 1                                   |                                                       | I      |     |      |      |

| Si863xBx, Ex                           |                                     |                                                       |        |     |      |      |

| Maximum Data Rate                      |                                     |                                                       | 0      | _   | 150  | Mbps |

| Minimum Pulse Width                    |                                     |                                                       | _      | _   | 5.0  | ns   |

| Propagation Delay                      | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 4.2 Propagation<br>Delay Timing on page 11 | 5.0    | 8.0 | 13   | ns   |

| Pulse Width Distortion                 | PWD                                 | See Figure 4.2 Propagation                            |        | 0.2 | 4.5  | ns   |

| tPLH - tPHL                            | T WB                                | Delay Timing on page 11                               |        | 0.2 | 7.0  | 113  |

| Propagation Delay Skew <sup>3</sup>    | t <sub>PSK(P-P)</sub>               |                                                       | _      | 2.0 | 4.5  | ns   |

| Channel-Channel Skew                   | t <sub>PSK</sub>                    |                                                       | _      | 0.4 | 2.5  | ns   |

| All Models                             |                                     |                                                       |        |     |      |      |

|                                        |                                     | C <sub>L</sub> = 15 pF                                |        |     |      |      |

| Output Rise Time                       | t <sub>r</sub>                      | See Figure 4.2 Propagation<br>Delay Timing on page 11 | _      | 2.5 | 4.0  | ns   |

|                                        |                                     | C <sub>L</sub> = 15 pF                                |        |     |      |      |

| Output Fall Time                       | t <sub>f</sub>                      | See Figure 4.2 Propagation<br>Delay Timing on page 11 |        | 2.5 | 4.0  | ns   |

| Peak Eye Diagram Jitter                | t <sub>JIT(PK)</sub>                | See Figure 2.3 Eye Diagram on page 3                  | _      | 350 | _    | ps   |

| Parameter                                | Symbol           | Test Condition                                                   | Min | Тур | Max | Unit  |

|------------------------------------------|------------------|------------------------------------------------------------------|-----|-----|-----|-------|

|                                          |                  | $V_I = V_{DD}$ or 0 V                                            |     |     |     |       |

| Common Mode Transient Immunity           | CMTI             | V <sub>CM</sub> = 1500 V                                         |     |     |     | kV/µs |

| Si86xxxB/C/D                             | OWITE            | See Figure 4.3 Common-<br>Mode Transient Immunity Test           | 35  | 50  | _   | κνημο |

| Si86xxxT                                 |                  | Circuit on page 11                                               | 60  | 100 | _   |       |

| Enable to Data Valid                     | t <sub>en1</sub> | See Figure 4.1 ENABLE Timing Diagram on page 11                  | _   | 6.0 | 11  | ns    |

| Enable to Data Tri-State                 | t <sub>en2</sub> | See Figure 4.1 ENABLE Timing Diagram on page 11                  | _   | 8.0 | 12  | ns    |

| Input power loss to valid default output | t <sub>SD</sub>  | See Figure 3.1 Device Behavior during Normal Operation on page 6 | _   | 8.0 | 12  | ns    |

| Start-up Time <sup>4</sup>               | t <sub>SU</sub>  |                                                                  | _   | 15  | 40  | μs    |

- 1.  $V_{DD1}$  = 3.3 V ±10%;  $V_{DD2}$  = 3.3 V ±10%,  $T_A$  = -40 to 125 °C

- 2. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ ,  $\pm$ 40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled-impedance PCB traces.

- 3. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

- 4. Start-up time is the time period from the application of power to the appearance of valid data at the output.

Table 4.4. Electrical Characteristics <sup>1</sup>

| Parameter                               | Symbol                              | Test Condition                              | Min                                       | Тур  | Max   | Unit |

|-----------------------------------------|-------------------------------------|---------------------------------------------|-------------------------------------------|------|-------|------|

| VDD Undervoltage Threshold              | VDD <sub>UV+</sub>                  | V <sub>DD1</sub> , V <sub>DD2</sub> rising  | 1.95                                      | 2.24 | 2.375 | V    |

| VDD Undervoltage Threshold              | VDD <sub>UV</sub> _                 | V <sub>DD1</sub> , V <sub>DD2</sub> falling | 1.88                                      | 2.16 | 2.325 | V    |

| VDD Undervoltage Hysteresis             | VDD <sub>HYS</sub>                  |                                             | 50                                        | 70   | 95    | mV   |

| Positive-Going Input Threshold          | VT+                                 | All inputs rising                           | 1.4                                       | 1.67 | 1.9   | V    |

| Negative-Going Input Threshold          | VT-                                 | All inputs falling                          | 1.0                                       | 1.23 | 1.4   | V    |

| Input Hysteresis                        | V <sub>HYS</sub>                    |                                             | 0.38                                      | 0.44 | 0.50  | V    |

| High Level Input Voltage                | V <sub>IH</sub>                     |                                             | 2.0                                       | _    | _     | V    |

| Low Level Input Voltage                 | V <sub>IL</sub>                     |                                             | _                                         | _    | 0.8   | V    |

| High Level Output Voltage               | V <sub>OH</sub>                     | loh = –4 mA                                 | V <sub>DD1</sub> , V <sub>DD2</sub> – 0.4 | 2.3  | _     | V    |

| Low Level Output Voltage                | V <sub>OL</sub>                     | IoI = 4 mA                                  | _                                         | 0.2  | 0.4   | V    |

| Input Leakage Current                   |                                     |                                             |                                           |      |       |      |

| Si863xxA/B/C/D                          | IL                                  |                                             | _                                         | _    | ±10   | μΑ   |

| Si863xxT                                |                                     |                                             | _                                         | _    | ±15   |      |

| Output Impedance <sup>2</sup>           | Z <sub>O</sub>                      |                                             | _                                         | 50   | _     | Ω    |

| Enable Input Current                    |                                     |                                             |                                           |      |       |      |

| Si863xxA/B/C/D                          | I <sub>ENH</sub> , I <sub>ENL</sub> | $V_{ENx} = V_{IH}$ or $V_{IL}$              | _                                         | 2.0  | _     | μΑ   |

| Si863xxT                                |                                     |                                             | _                                         | 10.0 | _     |      |

| DC Supply Current (All Inputs 0 V or at | Supply)                             |                                             | '                                         |      |       |      |

| Si8630Bx, Ex, Si8635Bx                  |                                     |                                             |                                           |      |       |      |

| $V_{DD1}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 0.9  | 1.6   |      |

| $V_{DD2}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 1.9  | 3.0   | mA   |

| $V_{DD1}$                               |                                     | $V_{I} = 1(Bx), 0(Ex)$                      | _                                         | 4.6  | 7.4   |      |

| $V_{DD2}$                               |                                     | $V_{I} = 1(Bx), 0(Ex)$                      | _                                         | 1.9  | 3.0   |      |

| Si8631Bx, Ex                            |                                     |                                             |                                           |      |       |      |

| $V_{DD1}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 1.3  | 2.1   |      |

| $V_{DD2}$                               |                                     | $V_I = 0(Bx), 1(Ex)$                        | _                                         | 1.7  | 2.7   | mA   |

| V <sub>DD1</sub>                        |                                     | $V_1 = 1(Bx), 0(Ex)$                        | _                                         | 3.9  | 5.9   |      |

| $V_{DD2}$                               |                                     | $V_1 = 1(Bx), 0(Ex)$                        | _                                         | 3.0  | 4.5   |      |

| 1 Mbps Supply Current (All Inputs = 50  | ⊥<br>0 kHz Square                   |                                             | outs)                                     | -    |       |      |

| Si8630Bx, Ex, Si8635Bx                  |                                     | · ·                                         |                                           |      |       |      |

| V <sub>DD1</sub>                        |                                     |                                             | _                                         | 2.8  | 3.9   | mA   |

| $V_{DD2}$                               |                                     |                                             |                                           | 2.2  | 3.1   |      |

| Parameter                           | Symbol                              | Test Condition                                        | Min    | Тур | Max  | Unit |

|-------------------------------------|-------------------------------------|-------------------------------------------------------|--------|-----|------|------|

| Si8631Bx, Ex                        |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                           |                                     |                                                       | _      | 2.7 | 3.8  | mA   |

| $V_{DD2}$                           |                                     |                                                       | _      | 2.6 | 3.6  |      |

| 10 Mbps Supply Current (All Input   | ts = 5 MHz Square                   | • Wave, CI = 15 pF on All Outpu                       | uts)   |     |      |      |

| Si8630Bx, Ex, Si8635Bx              |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                           |                                     |                                                       | _      | 2.8 | 3.9  | mA   |

| $V_{DD2}$                           |                                     |                                                       | _      | 2.4 | 3.3  |      |

| Si8631Bx, Ex                        |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                           |                                     |                                                       | _      | 2.8 | 3.9  | mA   |

| $V_{\mathrm{DD2}}$                  |                                     |                                                       | _      | 2.7 | 3.7  |      |

| 100 Mbps Supply Current (All Inpu   | uts = 50 MHz Squa                   | are Wave, CI = 15 pF on All Ou                        | tputs) |     |      |      |

| Si8630Bx, Ex, Si8635Bx              |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                           |                                     |                                                       | _      | 2.8 | 3.9  | mA   |

| $V_{\mathrm{DD2}}$                  |                                     |                                                       | _      | 7.5 | 10.1 |      |

| Si8631Bx, Ex                        |                                     |                                                       |        |     |      |      |

| $V_{DD1}$                           |                                     |                                                       | _      | 4.5 | 6.1  | mA   |

| $V_{\mathrm{DD2}}$                  |                                     |                                                       | _      | 6.1 | 8.2  |      |

| Timing Characteristics              |                                     | l .                                                   |        |     |      |      |

| Si863xBx, Ex                        |                                     |                                                       |        |     |      |      |

| Maximum Data Rate                   |                                     |                                                       | 0      | _   | 150  | Mbps |

| Minimum Pulse Width                 |                                     |                                                       | _      | _   | 5.0  | ns   |

| Propagation Delay                   | t <sub>PHL</sub> , t <sub>PLH</sub> | See Figure 4.2 Propagation<br>Delay Timing on page 11 | 5.0    | 8.0 | 14   | ns   |

| Pulse Width Distortion              | PWD                                 | See Figure 4.2 Propagation                            |        | 0.2 | 5.0  | ne   |

| tPLH -tPHL                          | FVVD                                | Delay Timing on page 11                               | _      | 0.2 | 5.0  | ns   |

| Propagation Delay Skew <sup>3</sup> | t <sub>PSK(P-P)</sub>               |                                                       | _      | 2.0 | 5.0  | ns   |

| Channel-Channel Skew                | t <sub>PSK</sub>                    |                                                       | _      | 0.4 | 2.5  | ns   |

| All Models                          |                                     |                                                       |        |     |      |      |

|                                     |                                     | C <sub>L</sub> = 15 pF                                |        |     |      |      |

| Output Rise Time                    | t <sub>r</sub>                      | See Figure 4.2 Propagation<br>Delay Timing on page 11 | _      | 2.5 | 4.0  | ns   |

|                                     |                                     | C <sub>L</sub> = 15 pF                                |        |     |      |      |

| Output Fall Time                    | t <sub>f</sub>                      | See Figure 4.2 Propagation<br>Delay Timing on page 11 | _      | 2.5 | 4.0  | ns   |

| Peak Eye Diagram Jitter             | t <sub>JIT(PK)</sub>                | See Figure 2.3 Eye Diagram on page 3                  | _      | 350 | _    | ps   |

| Parameter                                | Symbol           | Test Condition                                                   | Min | Тур | Max | Unit  |

|------------------------------------------|------------------|------------------------------------------------------------------|-----|-----|-----|-------|

|                                          |                  | V <sub>I</sub> = V <sub>DD</sub> or 0 V                          |     |     |     |       |

| Common Mode Transient Immunity           | CMTI             | V <sub>CM</sub> = 1500 V                                         |     |     |     | kV/µs |

| Si86xxxB/C/D                             | OWITE            | See Figure 4.3 Common-<br>Mode Transient Immunity Test           | 35  | 50  | _   | κνημο |

| Si86xxxT                                 |                  | Circuit on page 11                                               | 60  | 100 | _   |       |

| Enable to Data Valid                     | t <sub>en1</sub> | See Figure 4.1 ENABLE Timing Diagram on page 11                  | _   | 6.0 | 11  | ns    |

| Enable to Data Tri-State                 | t <sub>en2</sub> | See Figure 4.1 ENABLE Timing Diagram on page 11                  | _   | 8.0 | 12  | ns    |

| Input power loss to valid default output | t <sub>SD</sub>  | See Figure 3.1 Device Behavior during Normal Operation on page 6 | _   | 8.0 | 12  | ns    |

| Start-up Time <sup>4</sup>               | t <sub>SU</sub>  |                                                                  | _   | 15  | 40  | μs    |

- 1.  $V_{DD1}$  = 2.5 V ±5%;  $V_{DD2}$  = 2.5 V ±5%,  $T_A$  = -40 to 125 °C

- 2. The nominal output impedance of an isolator driver channel is approximately 50  $\Omega$ ,  $\pm$ 40%, which is a combination of the value of the on-chip series termination resistor and channel resistance of the output driver FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately terminated with controlled-impedance PCB traces.

- 3. t<sub>PSK(P-P)</sub> is the magnitude of the difference in propagation delay times measured between different units operating at the same supply voltages, load, and ambient temperature.

- 4. Start-up time is the time period from the application of power to the appearance of valid data at the output.

## Table 4.5. Regulatory Information 1, 2, 3, 4

## For All Product Options Except Si863xxT

#### **CSA**

The Si863x is certified under CSA Component Acceptance Notice 5A. For more details, see File 232873.

61010-1: Up to 600  $V_{RMS}$  reinforced insulation working voltage; up to 600  $V_{RMS}$  basic insulation working voltage.

60950-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

60601-1: Up to 125 V<sub>RMS</sub> reinforced insulation working voltage; up to 380 V<sub>RMS</sub> basic insulation working voltage.

#### **VDE**

The Si863x is certified according to IEC 60747-5-5. For more details, see File 5006301-4880-0001.

60747-5-5: Up to 1200 Vpeak for basic insulation working voltage.

60950-1: Up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

#### UL

The Si863x is certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 5000 V<sub>RMS</sub> isolation voltage for basic protection.

#### CQC

The Si863x is certified under GB4943.1-2011. For more details, see certificates CQC13001096110 and CQC13001096239.

Rated up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

## For All Si863xxT Product Options

## CSA

Certified under CSA Component Acceptance Notice 5A. For more details, see File 232873.

60950-1: Up to 600  $V_{RMS}$  reinforced insulation working voltage; up to 1000  $V_{RMS}$  basic insulation working voltage.

#### **VDE**

Certified according to VDE 0884-10.

#### UL

Certified under UL1577 component recognition program. For more details, see File E257455.

Rated up to 5000 V<sub>RMS</sub> isolation voltage for basic protection.

## CQC

Certified under GB4943.1-2011

Rated up to 600 V<sub>RMS</sub> reinforced insulation working voltage; up to 1000 V<sub>RMS</sub> basic insulation working voltage.

- 1. Regulatory Certifications apply to 2.5 kV<sub>RMS</sub> rated devices, which are production tested to 3.0 kV<sub>RMS</sub> for 1 s.

- 2. Regulatory Certifications apply to 3.75 kV<sub>RMS</sub> rated devices, which are production tested to 4.5 kV<sub>RMS</sub> for 1 s.

- 3. Regulatory Certifications apply to 5.0 kV $_{RMS}$  rated devices, which are production tested to 6.0 kV $_{RMS}$  for 1 s.

- 4. For more information, see 1. Ordering Guide.

Table 4.6. Insulation and Safety-Related Specifications

| Parameter                                | Symbol          | Test Condition | Value            |                  | Unit             |

|------------------------------------------|-----------------|----------------|------------------|------------------|------------------|

|                                          |                 |                | WB SOIC-16       | NB SOIC-16       |                  |

| Nominal Air Gap (Clearance) <sup>1</sup> | L(IO1)          |                | 8.0              | 4.9              | mm               |

| Nominal External Tracking <sup>1</sup>   | L(IO2)          |                | 8.0              | 4.01             | mm               |

| Minimum Internal Gap                     |                 |                | 0.014            | 0.014            | mm               |

| (Internal Clearance)                     |                 |                |                  |                  |                  |

| Tracking Resistance                      | PTI             | IEC60112       | 600              | 600              | V <sub>RMS</sub> |

| (Proof Tracking Index)                   |                 |                |                  |                  |                  |

| Erosion Depth                            | ED              |                | 0.019            | 0.019            | mm               |

| Resistance (Input-Output) <sup>2</sup>   | R <sub>IO</sub> |                | 10 <sup>12</sup> | 10 <sup>12</sup> | Ω                |

| Capacitance (Input-Output) <sup>2</sup>  | C <sub>IO</sub> | f = 1 MHz      | 2.0              | 2.0              | pF               |

| Input Capacitance 3                      | C <sub>I</sub>  |                | 4.0              | 4.0              | pF               |

- 1. The values in this table correspond to the nominal creepage and clearance values. VDE certifies the clearance and creepage limits as 4.7 mm minimum for the NB SOIC-16 package and 8.5 mm minimum for the WB SOIC-16 package. UL does not impose a clearance and creepage minimum for component-level certifications. CSA certifies the clearance and creepage limits as 3.9 mm minimum for the NB SOIC-16 and 7.6 mm minimum for the WB SOIC-16 package.

- 2. To determine resistance and capacitance, the Si86xx is converted into a 2-terminal device. Pins 1–8 are shorted together to form the first terminal and pins 9–16 are shorted together to form the second terminal. The parameters are then measured between these two terminals.

- 3. Measured from input pin to ground.

Table 4.7. IEC 60664-1 Ratings

| Parameter                   | Test Conditions                             | Specif     | Specification |  |  |  |

|-----------------------------|---------------------------------------------|------------|---------------|--|--|--|

|                             |                                             | WB SOIC-16 | NB SOIC-16    |  |  |  |

| Basic Isolation Group       | Material Group                              | I          | 1             |  |  |  |

| Installation Classification | Rated Mains Voltages ≤ 150 V <sub>RMS</sub> | I-IV       | I-IV          |  |  |  |

|                             | Rated Mains Voltages ≤ 300 V <sub>RMS</sub> | I-IV       | 1-111         |  |  |  |

|                             | Rated Mains Voltages ≤ 400 V <sub>RMS</sub> | 1-111      | 1-11          |  |  |  |

|                             | Rated Mains Voltages ≤ 600 V <sub>RMS</sub> | I-III      | 1-11          |  |  |  |

Table 4.8. IEC 60747-5-5 Insulation Characteristics for Si86xxxx <sup>1</sup>

| Parameter Symbol                                                  |                | Test Condition                                          | Charac           | Unit             |       |

|-------------------------------------------------------------------|----------------|---------------------------------------------------------|------------------|------------------|-------|

|                                                                   |                |                                                         | WB SOIC-16       | NB SOIC-16       |       |

| Maximum Working<br>Insulation Voltage                             | $V_{IORM}$     |                                                         | 1200             | 630              | Vpeak |

| Input to Output Test                                              | $V_{PR}$       | Method b1                                               | 2250             | 1182             | Vpeak |

| Voltage                                                           |                | (V <sub>IORM</sub> x 1.875 = VPR, 100%                  |                  |                  |       |

|                                                                   |                | Production Test, t <sub>m</sub> = 1 sec,                |                  |                  |       |

|                                                                   |                | Partial Discharge < 5 pC)                               |                  |                  |       |

| Transient Overvolt-<br>age                                        | $V_{IOTM}$     | t = 60 sec                                              | 6000             | 6000             | Vpeak |

|                                                                   |                | Tested per IEC 60065 with surge voltage of 1.2 μs/50 μs |                  |                  |       |

| Surge Voltage                                                     | $V_{IOSM}$     | Si863xxT tested with magnitude 6250 V x 1.6 = 10 kV     | 6250             | _                | Vpeak |

|                                                                   |                | Si863xxB/C/D tested with 4000 V                         | 4000             | 4000             |       |

| Pollution Degree                                                  |                |                                                         | 2                | 2                |       |

| (DIN VDE 0110, Ta-<br>ble 1)                                      |                |                                                         |                  |                  |       |

| Insulation Resistance at T <sub>S</sub> , V <sub>IO</sub> = 500 V | R <sub>S</sub> |                                                         | >10 <sup>9</sup> | >10 <sup>9</sup> | Ω     |

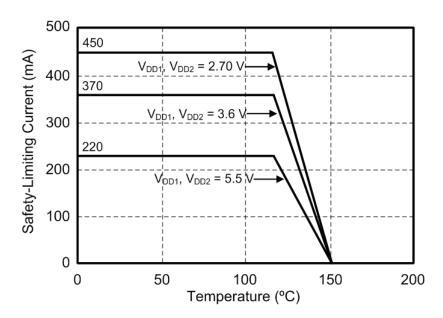

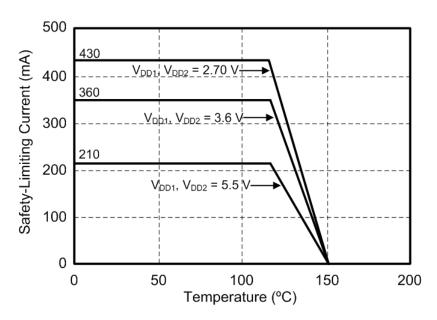

Table 4.9. IEC Safety Limiting Values <sup>1</sup>

| Parameter                               | Symbol         | Test Condition                                                          | Max        |            | Unit |

|-----------------------------------------|----------------|-------------------------------------------------------------------------|------------|------------|------|

|                                         |                |                                                                         | WB SOIC-16 | NB SOIC-16 |      |

| Case Temperature                        | T <sub>S</sub> |                                                                         | 150        | 150        | °C   |

| Safety Input, Output, or Supply Current | I <sub>S</sub> | $\theta_{JA}$ = 100 °C/W (WB SOIC-16)                                   | 220        | 210        | mA   |

|                                         |                | 105 °C/W (NB SOIC-16)                                                   |            |            |      |

|                                         |                | V <sub>I</sub> = 5.5 V, T <sub>J</sub> = 150 °C, T <sub>A</sub> = 25 °C |            |            |      |

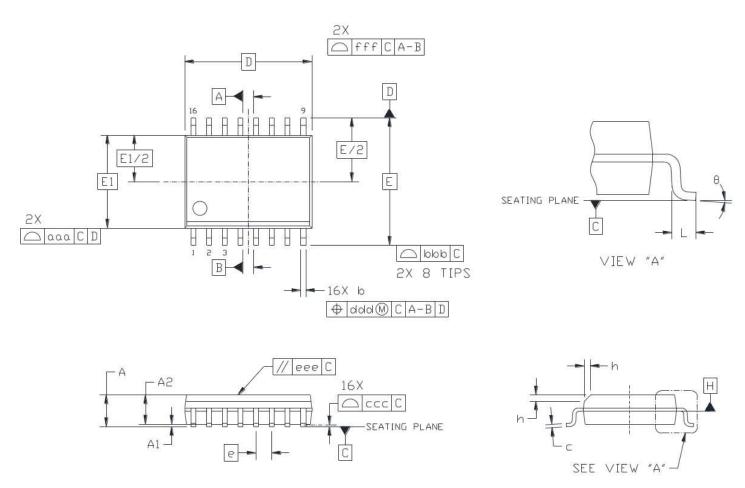

| Device Power Dissipation <sup>2</sup>   | P <sub>D</sub> |                                                                         | 275        | 275        | mW   |