# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Unipolar 2-Phase Stepper Motor Driver ICs SLA7070MS Series Data Sheet

March, 2018 Rev.1.6

# **Table of Contents**

| 1.   | General Description                           | .2 |

|------|-----------------------------------------------|----|

| 2.   | Features and Benefits                         | .2 |

| 3.   | Part Numbers and Functional Characteristics   | .3 |

| 4.   | Specifications                                | .4 |

| 5.   | Power Derating Chart                          | .8 |

| 6.   | Package Outline Drawing                       | .9 |

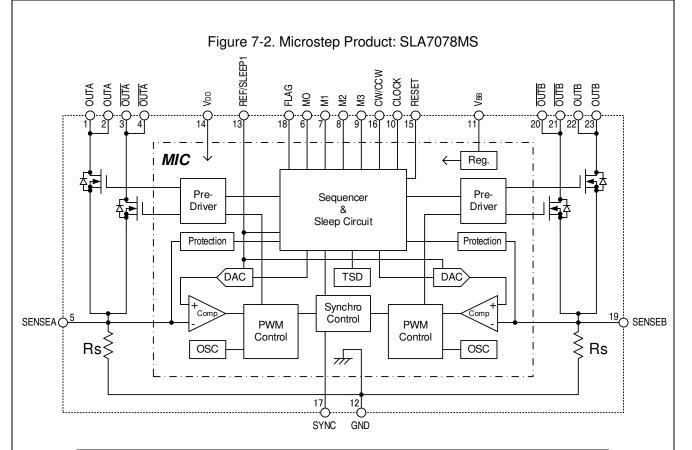

| 7.   | Functional Block Diagrams and Pin Assignments | 10 |

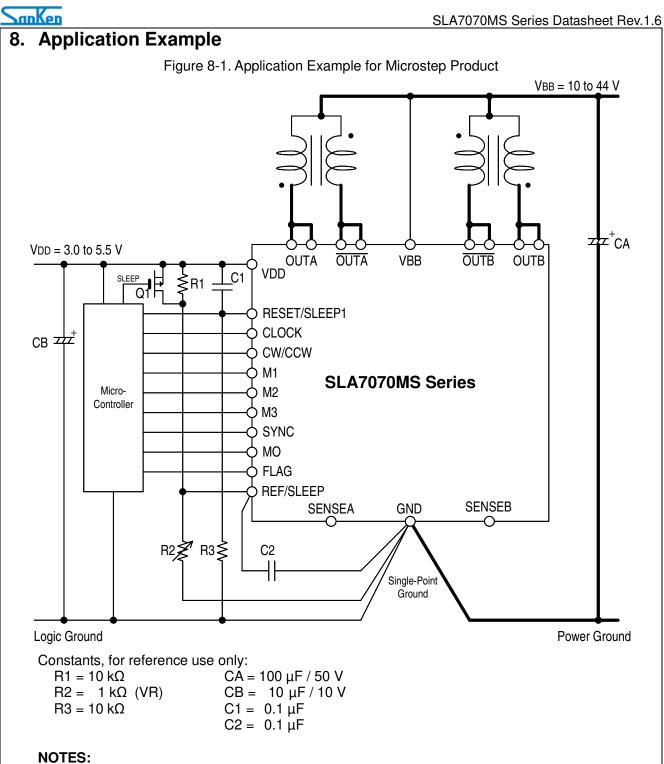

| 8.   | Application Example                           | 12 |

| 9.   | Truth Tables                                  | 13 |

| 10.  | Logic Input Pins                              | 14 |

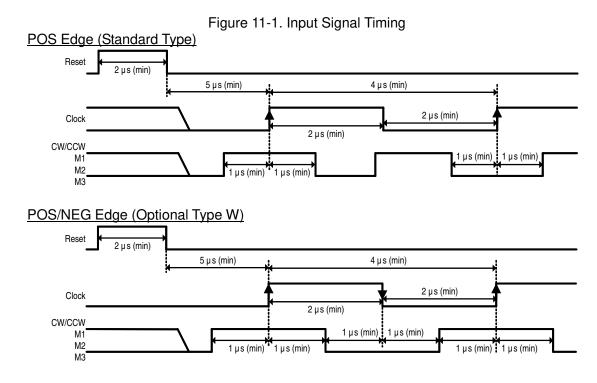

| 11.  | Logic Input Timing                            | 15 |

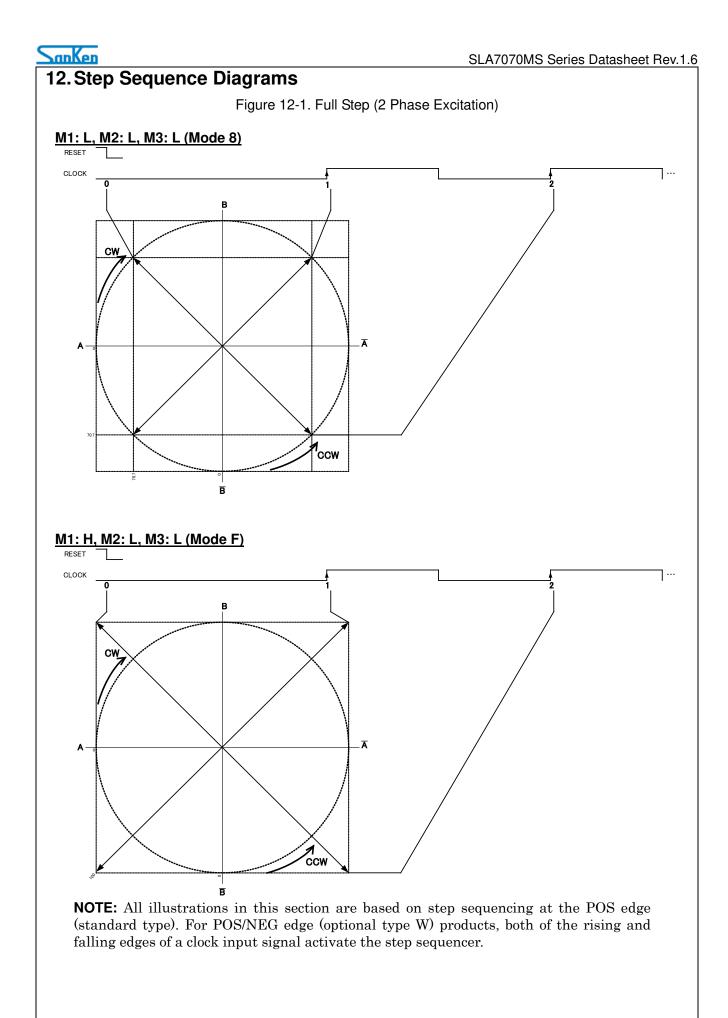

| 12.  | Step Sequence Diagrams                        | 16 |

| 13.  | Individual Circuit Descriptions               | 22 |

| 14.  | Functional Descriptions                       | 24 |

| 15.  | Application Information                       | 31 |

| 16.  | Thermal Design Information                    | 36 |

| 17.  | Characteristics Data                          | 38 |

| Impo | rtant Notes                                   | 39 |

# 1. General Description

SanKen

This document describes summary of the SLA7070MS series.

# 2. Features and Benefits

- (1) Main power supply voltages,  $V_{BB}$ : 46 V (max.), 10 to 44 V normal operating range

- (2) Logic supply voltages,  $V_{DD}$ : 3.0 to 5.5 V

- (3) Maximum output currents, Io(max): 2.0 A, 3.0 A

- (4) Clock-in stepping control (built-in sequencer)

- (5) Full-, half-, and microstep products are available

→ Microstepping options are capable of full-, half-, quarter-, eighth-, and sixteenth-stepping

- (6) Built-in "sense resistor" detects motor current

- (7) All variants are pin-compatible for enhanced design flexibility

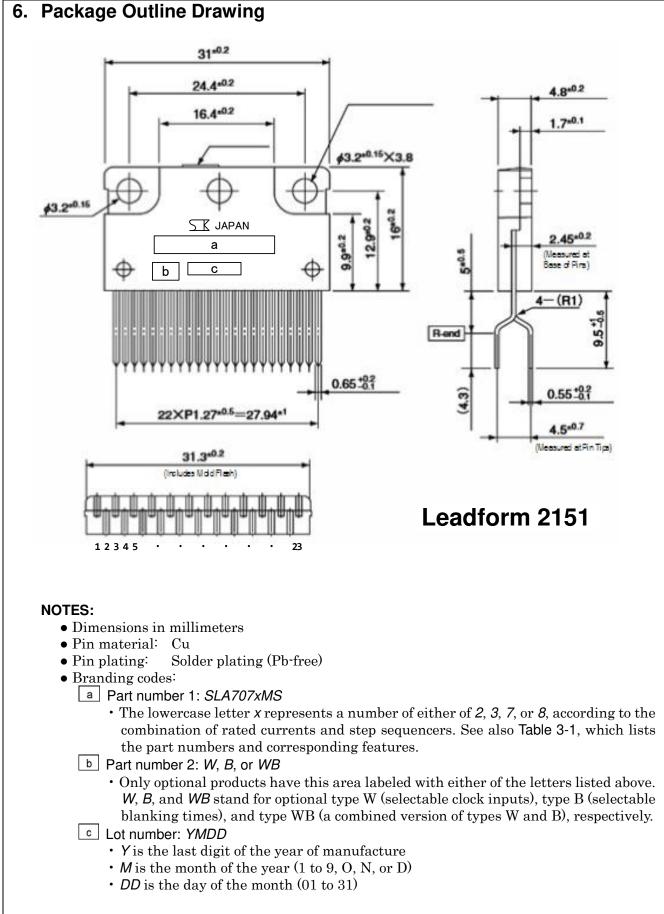

- (8) ZIP type 23-pin molded package (SLA package)

- (9) Self-excitation PWM current control with fixed OFF-time

- → For microstepping variants, OFF-time adjusted automatically by step reference current ratio (3 levels)

- (10) Built-in synchronous rectifying circuit reduces power dissipation at PWM-OFF

- (11) Synchronous PWM chopping function prevents motor noise in the Hold mode

- (12) The Sleep mode to reduce IC input current in stand-by state

- (13) Built-in protection circuitry against motor coil opens/shorts and thermal shutdown protection

- (14) The following are the product variants and optional features available:

- Blanking Time

- Full/Half step products:

- Microstep product:

- $3.2 \ \mu s$  (standard),  $5.2 \ \mu s$  (optional type B)  $1.7 \ \mu s$  (standard),  $3.2 \ \mu s$  (optional type B)

- Input Clock Edge

- Standard type:

- Optional type W:

- POS (positive) edge POS/NEG (positive and negative) edge

**NOTE:** The optional types listed above, "type B" and "type W", are abbreviated and referred to "B" and "W" as the letters for product branding codes, respectively. These terms and abbreviations are also used throughout this document. See also Section 6 for more details.

# 3. Part Numbers and Functional Characteristics

Table 3-1 provides the product variants available in the SLA7070MS series.

| Table       |                |               |               | 00            |  |

|-------------|----------------|---------------|---------------|---------------|--|

|             |                | aracteristics |               |               |  |

|             |                |               | Rated Current |               |  |

|             | Seque          | ncer          | (Maximum Se   | etting Value) |  |

| Part Number | Full/Half Step | Microstep     | 2.0 A         | 3.0 A         |  |

| SLA7072MS   | Х              |               | Х             |               |  |

| SLA7073MS   | X              |               |               | X             |  |

| SLA7078MS   |                | Х             |               | X             |  |

| Table 3-1 Part Nu | mbers and Functiona   | I Charactoristics |

|-------------------|-----------------------|-------------------|

|                   | inders and i uncliona |                   |

In addition, the following functional options are available in the SLA7070MS series: • Blanking Time

• Full/Half step products:

anKen

3.2 μs (standard), 5.2 μs (optional type B)

1.7 μs (standard), 3.2 μs (optional type B)

- Microstep product:Input Clock Edge

- POS (positive) edge

- Standard type:Optional type W:

POS/NEG (positive and negative) edge

**NOTE:** The optional types listed above, "type B" and "type W", are abbreviated and referred to "B" and "W" as the letters for product branding codes, respectively. These terms and abbreviations are also used throughout this document. See also Section 6 for more details.

# 4. Specifications

|                               | 1                |                               | Unle | ess specifically not   | ted, T <sub>A</sub> = 25 °C |

|-------------------------------|------------------|-------------------------------|------|------------------------|-----------------------------|

| Characteristic                | Symbol           | Rating                        | Unit | Rema                   | rks                         |

| Load (Motor Supply) Voltage   | V <sub>M</sub>   | 46                            | V    |                        |                             |

| Main Power Supply Voltage     | V <sub>BB</sub>  | 46                            | V    |                        |                             |

| Supply Voltage                | V                | 6                             | V    | Power supply           | to DC                       |

| Supply Voltage                | V <sub>DD</sub>  | 7                             | V    | ≤1 µs (5% dut          | y)                          |

|                               |                  | 2.0                           | Α    | SLA7072MS              | Control                     |

| Output Current                | I <sub>O</sub>   | 3.0                           | Α    | SLA7073MS<br>SLA7078MS | current<br>value            |

| Logic Input Voltage           | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |                        |                             |

| REF Input Voltage             | V <sub>REF</sub> | -0.3 to V <sub>DD</sub> + 0.3 | V    |                        |                             |

| Sense Voltage                 | V <sub>RS</sub>  | ±1                            | V    |                        |                             |

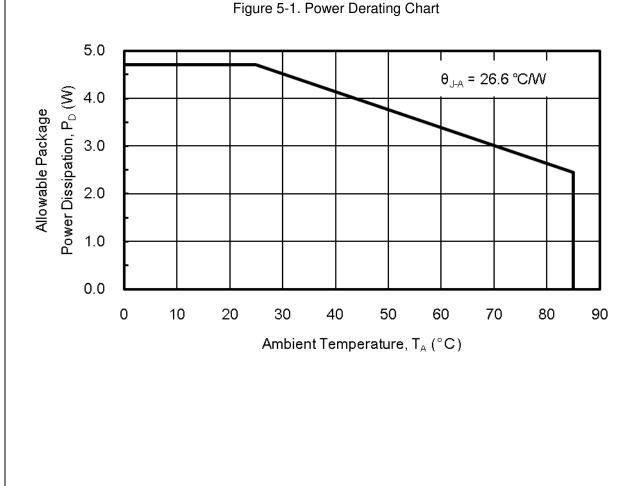

| Allowable Power Dissipation   | PD               | 4.7                           | W    | Without heats          | ink                         |

| Junction Temperature          | TJ               | 150                           | °C   |                        |                             |

| Operating Ambient Temperature | T <sub>A</sub>   | -20 to 85                     | °C   |                        |                             |

| Storage Temperature           | T <sub>stg</sub> | -30 to 150                    | °C   |                        |                             |

Table 4-1. Absolute Maximum Ratings

NOTE: Output current ratings may be limited by duty cycles, ambient temperatures, and heat sinking conditions. Do not exceed the maximum output currents and the maximum junction temperature (T<sub>J</sub>) given above, under any conditions of use.

| Table 4-2. | Recommended | Operating | Conditions |

|------------|-------------|-----------|------------|

|            |             |           | Liniaga an |

| Tabl                        | e 4-2. Rec      | ommendeo       | d Operating | •    | ons<br>ss specifically noted. $T_A = 25 \ ^{\circ}C$                                              |

|-----------------------------|-----------------|----------------|-------------|------|---------------------------------------------------------------------------------------------------|

|                             |                 | Standard Value |             |      |                                                                                                   |

| Characteristic              | Symbol          | Min.           | Max.        | Unit | Remarks                                                                                           |

| Load (Motor Supply) Voltage | V <sub>M</sub>  |                | 44          | V    |                                                                                                   |

| Main Power Supply Voltage   | V <sub>BB</sub> | 10             | 44          | V    |                                                                                                   |

| Logic Supply Voltage        | V <sub>DD</sub> | 3.0            | 5.5         | v    | Surge voltage at VDD pin<br>should be less than ±0.5<br>V to avoid malfunctioning<br>in operation |

| Case Temperature            | T <sub>C</sub>  |                | 90          | °C   | Measured at Pin 12 (lead portion), without heatsink                                               |

**NOTE:** As the motor supply voltage,  $V_M$ , becomes higher, it also approaches the breakdown voltage of the OUTx pins (100 V min.); and breakdown will be more likely to happen. Even if one of the OUTx pins breaks down (due to surge noise or other factors), the SLA7070MS series will recognize it as abnormality (coil open) and will run appropriate protection functions. Therefore, a thorough evaluation is recommended.

|                                                                       | Ia                 |                            |                  | aracteristic ly noted, $T_A$ |      | C, $V_{BB} = 24$ V, and $V_{DD} = 5$ V                           |

|-----------------------------------------------------------------------|--------------------|----------------------------|------------------|------------------------------|------|------------------------------------------------------------------|

|                                                                       |                    |                            | Rating           |                              |      |                                                                  |

| Characteristic                                                        | Symbol             | Min.                       | Тур.             | Max.                         | Unit | Conditions                                                       |

| Main Power Supply                                                     | I <sub>BB</sub>    |                            |                  | 15                           | mA   | Normal mode                                                      |

| Current                                                               | I <sub>BBS</sub>   |                            |                  | 100                          | μA   | Sleep1, Sleep2                                                   |

| Logic Power Current                                                   | I <sub>DD</sub>    |                            |                  | 5                            | mA   |                                                                  |

| MOSFET Breakdown<br>Voltage                                           | V <sub>DSS</sub>   | 100                        |                  |                              | V    | $V_{BB} = 44V, I_D = 1 \text{ mA}$                               |

| Maximum Response<br>Frequency                                         | f <sub>clk</sub>   | 250                        |                  |                              | kHz  | Clock duty cycle = 50%                                           |

| Logic Input Voltage                                                   | V <sub>IL</sub>    |                            |                  | 0.25 ×<br>V <sub>DD</sub>    | V    |                                                                  |

|                                                                       | V <sub>IH</sub>    | 0.75 ×<br>V <sub>DD</sub>  |                  |                              | V    |                                                                  |

| Logic Input Current                                                   | IL                 |                            | ±1               |                              | μΑ   |                                                                  |

| Logic input ourient                                                   | I <sub>IH</sub>    |                            | ±1               |                              | μA   |                                                                  |

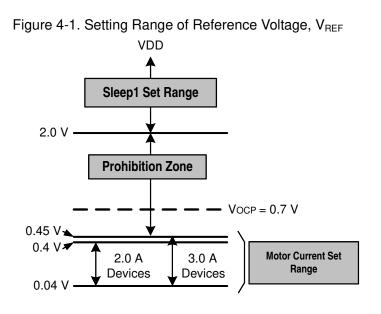

| REF Input Voltage                                                     | V <sub>REF</sub>   | 0.04                       |                  | <b>→</b>                     | V    | Table 4-5, Figure 4-1                                            |

|                                                                       | V <sub>REFS</sub>  | 2.0                        |                  | V <sub>DD</sub>              | V    | Output OFF, Sleep1 <sup>1)</sup>                                 |

| REF Input Current                                                     | I <sub>REF</sub>   |                            | ±10              |                              | μΑ   |                                                                  |

| SENSE Detection<br>Voltage                                            | V <sub>SENSE</sub> | V <sub>REF</sub> –<br>0.03 | V <sub>REF</sub> | V <sub>REF</sub> + 0.03      | V    | V <sub>REF</sub> = 0 to1.5 V,<br>Step reference ratio: 100%      |

| Sleep-Enable Recovery<br>Time                                         | t <sub>SE</sub>    | 100                        |                  |                              | μs   | Sleep1, Sleep2                                                   |

| Switching Time                                                        | t <sub>con</sub>   |                            | 2.0              |                              | μs   | Clock $\rightarrow$ Output ON                                    |

| Switching fille                                                       | t <sub>coff</sub>  |                            | 1.5              |                              | μs   | Clock $\rightarrow$ Output OFF                                   |

| Overcurrent Detection<br>Voltage <sup>2)</sup>                        | V <sub>CCP</sub>   | 0.65                       | 0.7              | 0.75                         | V    | Motor coils shorted                                              |

| Overeurrent Detection                                                 |                    |                            | 2.3              |                              | A    | 1.0 A and 1.5 A devices                                          |

| Overcurrent Detection<br>Current (V <sub>OCP</sub> / R <sub>S</sub> ) | ICCP               |                            | 3.5              |                              | A    | 2.0 A devices                                                    |

|                                                                       |                    |                            | 4.6              |                              | Α    | 3.0 A devices                                                    |

| Load Disconnection<br>Undetected Time                                 | t <sub>opp</sub>   |                            | 2                |                              | μs   | From PWM-OFF                                                     |

| Overheat Protection<br>Temperature                                    | T <sub>tsd</sub>   |                            | 140              |                              | °C   | Measured at back of device<br>case (after heat has<br>saturated) |

|                                                                       | V <sub>FlagL</sub> |                            |                  | 1.25                         | V    | I <sub>FlagL</sub> = 1.25 mA                                     |

| FLAG Output Voltage                                                   | V <sub>FlagH</sub> | V <sub>DD</sub> –<br>1.25  |                  |                              | V    | I <sub>FlagH</sub> = −1.25 mA                                    |

| FLAG Output Current                                                   | I <sub>FlagL</sub> |                            |                  | 1.25                         | mA   |                                                                  |

|                                                                       | I <sub>FlagH</sub> | -1.25                      |                  |                              | mA   |                                                                  |

Table 4-3. Electrical Characteristics 1

**NOTE:** Unless specifically noted, negative current is defined as output current flow from a specified pin. <sup>1)</sup> In a state of: IBBS, output OFF, and sequencer <u>enabled</u>. <sup>2)</sup> Protection circuit operates when  $V_{SENSE} \ge V_{OCP}$ .

#### Table 4-4. Electrical Characteristics 2 (Varying with Step Sequence)

(1) Full-/Half-step products: SLA7072MS, SLA7073MS

|                             |                      | mess spec                 |                                       | $100, T_A =$                   | <u>23 0,</u> | $V_{BB} = 24$ V, and $V_{DD} = 5$                                                                    |

|-----------------------------|----------------------|---------------------------|---------------------------------------|--------------------------------|--------------|------------------------------------------------------------------------------------------------------|

| Characteristic              | Symbol               | Min.                      | Rating<br>Typ.                        | Max.                           | Unit         | Conditions                                                                                           |

| Step Reference Current      | Mode F               | 101111.                   | 100                                   | IVIAN.                         | %            | V ~V 100%                                                                                            |

| Ratio                       | Mode 1<br>Mode 8     |                           | 70                                    |                                | %            | $V_{\text{REF}} \approx V_{\text{SENSE}} = 100\%,$<br>$V_{\text{REF}} = 0 \text{ to } 1.0 \text{ V}$ |

|                             |                      |                           | 3.2                                   |                                | μs           | Standard type<br>(w/o branding codes)                                                                |

| Minimum PWM ON-Time         | t <sub>on(min)</sub> |                           | 5.2                                   |                                | μs           | Optional type B<br>(w/ branding codes)                                                               |

| PWM OFF-Time                | t <sub>off</sub>     |                           | 12                                    |                                | μs           | <b>_</b>                                                                                             |

| (2) Microstep product: SLA7 |                      | iless speci<br>Min.       | <u>fically note</u><br>Rating<br>Typ. | ed, T <sub>A</sub> = 2<br>Max. | 25 °C, V     | $V_{BB} = 24$ V, and VDD = 5<br>Conditions                                                           |

|                             | Mode F               |                           | 100                                   | IVIAN.                         | %            |                                                                                                      |

|                             | Mode F               |                           | 98.1                                  |                                | %            |                                                                                                      |

|                             | Mode D               |                           | 95.7                                  |                                | %            | r.                                                                                                   |

|                             | Mode C               |                           | 92.4                                  |                                | %            |                                                                                                      |

|                             | Mode B               |                           | 88.2                                  |                                | %            |                                                                                                      |

|                             | Mode A               |                           | 83.1                                  |                                | %            |                                                                                                      |

|                             | Mode 9               |                           | 77.3                                  |                                | %            |                                                                                                      |

| Step Reference Current      | Mode 8               |                           | 70.7                                  |                                | %            | $V_{\text{REF}} \approx V_{\text{SENSE}} = 100\%,$                                                   |

| Ratio                       | Mode 7               |                           | 63.4                                  |                                | %            | V <sub>REF</sub> = 0 to 1.0 V                                                                        |

|                             | Mode 6               |                           | 55.5                                  |                                | %            |                                                                                                      |

|                             | Mode 5               |                           | 47.1                                  |                                | %            |                                                                                                      |

|                             | Mode 4               |                           | 38.2                                  |                                | %            |                                                                                                      |

|                             | Mode 3               |                           | 29                                    |                                | %            |                                                                                                      |

|                             | Mode 2               |                           | 19.5                                  |                                | %            |                                                                                                      |

|                             | Mode 1               |                           | 9.8                                   |                                | %            |                                                                                                      |

|                             | V <sub>MOL</sub>     |                           |                                       | 1.25                           | V            | I <sub>MOL</sub> = 1.25 mA                                                                           |

| MO Output Voltage           | V <sub>MOH</sub>     | V <sub>DD</sub> –<br>1.25 |                                       |                                | V            | I <sub>MOH</sub> = −1.25 mA                                                                          |

| MO Output Current           | I <sub>MOL</sub>     |                           |                                       | 1.25                           | mA           |                                                                                                      |

|                             | I <sub>MOH</sub>     | -1.25                     |                                       |                                | mA           |                                                                                                      |

| Minimum PWM ON-Time         | t <sub>on(min)</sub> |                           | 1.7                                   |                                | μs           | Standard type<br>(w/o branding codes)                                                                |

|                             | •on(min)             |                           | 3.2                                   |                                | μs           | Optional type B<br>(w/ branding codes)                                                               |

|                             | t <sub>off 1</sub>   |                           | 12                                    |                                | μs           | Mode 8 to Mode F                                                                                     |

| PWM OFF-time                | t <sub>off 2</sub>   |                           | 9                                     |                                | μs           | Mode 4 to Mode 7                                                                                     |

|                             | t <sub>off 3</sub>   |                           | 7                                     |                                | μs           | Mode 1 to Mode 3                                                                                     |

### Table 4-5. Electrical Characteristics 3 (Varying with Output Current Range)

(1)  $I_0 = 2.0 A$

| ( ) <u>-</u>                                 |                     | Unless sp | ecifically r | noted, T <sub>A</sub> : | = 25 °C | , $V_{BB} = 24$ V, and $V_{DD} = 5$ V |

|----------------------------------------------|---------------------|-----------|--------------|-------------------------|---------|---------------------------------------|

| Characteristic                               | Cumbal              |           | Rating       |                         |         | Conditiono                            |

| Characteristic                               | Symbol              | Min.      | Тур.         | Max.                    | Unit    | Conditions                            |

| Output MOSFET ON-Voltage                     | R <sub>DS(on)</sub> |           | 0.25         | 0.4                     | Ω       | I <sub>D</sub> = 2.0 A                |

| Output MOSFET Body<br>Diodes Forward Voltage | V <sub>F</sub>      |           | 0.95         | 1.2                     | V       | I <sub>F</sub> = 2.0 A                |

| Sense Resistor <sup>1)</sup>                 | Rs                  | 0.199     | 0.205        | 0.211                   | Ω       | Tolerance: ±3%                        |

| REF Input Voltage                            | V <sub>REF</sub>    | 0.04      |              | 0.4                     | V       | Within specified current limit        |

<sup>1)</sup> Includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

(2)  $I_0 = 3.0 \text{ A}$

Unless specifically noted,  $T_A = 25 \text{ °C}$ ,  $V_{BB} = 24 \text{ V}$ , and  $V_{DD} = 5 \text{ V}$

| Characteristic                               | Symbol              |       | Rating |       | Unit | Conditions                     |

|----------------------------------------------|---------------------|-------|--------|-------|------|--------------------------------|

| Characteristic                               | Symbol              | Min.  | Тур.   | Max.  | Unit | Conditions                     |

| Output MOSFET<br>ON-Resistance               | R <sub>DS(on)</sub> |       | 0.18   | 0.24  | Ω    | I <sub>D</sub> = 3.0 A         |

| Output MOSFET Body<br>Diodes Forward Voltage | V <sub>F</sub>      |       | 0.95   | 2.1   | V    | I <sub>F</sub> = 3.0 A         |

| Sense Resistor <sup>1)</sup>                 | R <sub>S</sub>      | 0.150 | 0.155  | 0.160 | Ω    | Tolerance: ±3%                 |

| REF Input Voltage                            | V <sub>REF</sub>    | 0.04  |        | 0.45  | V    | Within specified current limit |

<sup>1)</sup> Includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

**NOTE:** Extra attentions should be paid to the changeover between the motor current specification range and the Sleep1 set range. Vocp falls on the "prohibition zone" threshold. If the changeover takes too long, OCP operation will start when  $V_{SENSE} > V_{OCP}$ .

# 5. Power Derating Chart

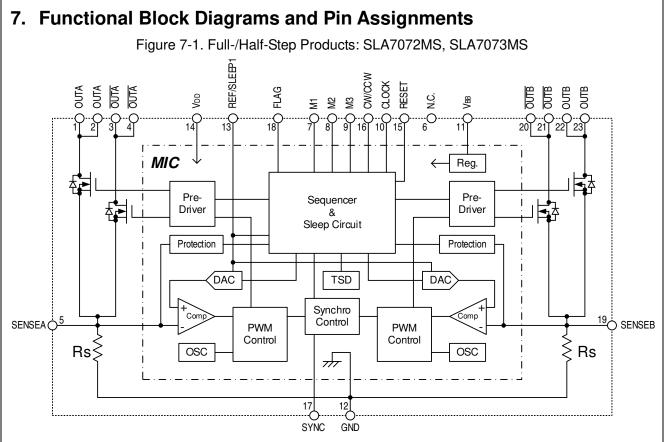

| Pin No. | Symbol          | Function                                   |  |  |  |

|---------|-----------------|--------------------------------------------|--|--|--|

| 1       |                 |                                            |  |  |  |

| 2       | OUTA            | Phase A output                             |  |  |  |

| 3       | OUTA            | Phase A output                             |  |  |  |

| 4       | OUTA            |                                            |  |  |  |

| 5       | SENSEA          | Phase A current sensing                    |  |  |  |

| 6       | NC              | No connection                              |  |  |  |

| 7       | M1              |                                            |  |  |  |

| 8       | M2              | Input for excitation mode & Sleep2 setting |  |  |  |

| 9       | M3              |                                            |  |  |  |

| 10      | CLOCK           | Step clock input                           |  |  |  |

| 11      | V <sub>BB</sub> | Main power supply voltage (for motor)      |  |  |  |

| 12      | GND             | Ground                                     |  |  |  |

| 13      | REF/SLEEP1      | Input for control current / Sleep1 setting |  |  |  |

| 14      | V <sub>DD</sub> | Power supply to logic                      |  |  |  |

| 15      | RESET           | Reset input for internal logic             |  |  |  |

| 16      | CW/CCW          | Forward / reverse input                    |  |  |  |

| 17      | SYNC            | Synchronous PMW control switch input       |  |  |  |

| 18      | FLAG            | Output from protection circuit monitor     |  |  |  |

| 19      | SENSEB          | Phase B current sensing                    |  |  |  |

| 20      | OUTB            |                                            |  |  |  |

| 21      | OUTB            | Phase B output                             |  |  |  |

| 22      |                 | Dhace D evitevit                           |  |  |  |

| 23      | OUTB            | Phase B output                             |  |  |  |

| Pin No. | Symbol          | Function                                      |  |  |  |  |

|---------|-----------------|-----------------------------------------------|--|--|--|--|

| 1       | OUTA            | Phase A output                                |  |  |  |  |

| 2       | OUTA            | Filase A oulput                               |  |  |  |  |

| 3       | OUTA            | Phase A output                                |  |  |  |  |

| 4       | UUIA            | Filase A oulput                               |  |  |  |  |

| 5       | SENSEA          | Phase A current sensing                       |  |  |  |  |

| 6       | MO              | Output from 2-phase excitation status monitor |  |  |  |  |

| 7       | M1              |                                               |  |  |  |  |

| 8       | M2              | Input for excitation mode & Sleep2 setting    |  |  |  |  |

| 9       | M3              |                                               |  |  |  |  |

| 10      | CLOCK           | Step clock input                              |  |  |  |  |

| 11      | V <sub>BB</sub> | Main power supply voltage (for motor)         |  |  |  |  |

| 12      | GND             | Ground                                        |  |  |  |  |

| 13      | REF/SLEEP1      | Input for control current / Sleep1 setting    |  |  |  |  |

| 14      | V <sub>DD</sub> | Power supply to logic                         |  |  |  |  |

| 15      | RESET           | Reset input for internal logic                |  |  |  |  |

| 16      | CW/CCW          | Forward / reverse input                       |  |  |  |  |

| 17      | SYNC            | Synchronous PMW control switch input          |  |  |  |  |

| 18      | FLAG            | Output from protection circuit monitor for    |  |  |  |  |

| 10      | I LAG           | detecting coil opens/shorts                   |  |  |  |  |

| 19      | SENSEB          | Phase B current sensing                       |  |  |  |  |

| 20      | OUTB            | Phase B output                                |  |  |  |  |

| 21      |                 |                                               |  |  |  |  |

| 22      | OUTB            | Phase P output                                |  |  |  |  |

| 23      | OUTB            | Phase B output                                |  |  |  |  |

- Take precautions to avoid noise on the V<sub>DD</sub> line; noise levels greater than 0.5 V on the V<sub>DD</sub> line may cause device malfunction. Noise can be reduced by separating the logic ground and the power ground on a PCB from the GND pin (Pin 12).

- Unused logic input pins (CW/CCW, M1, M2, M3, RESET, and SYNC) <u>must be pulled up or</u> <u>down to VDD or ground.</u> If those unused pins are left open, the device may malfunction.

- Unused logic output pins (MO, FLAG) <u>must be kept open</u>.

#### SanKen

### 9. Truth Tables

#### (1) Common Input Pins

Table 9-1 shows the truth table for the input pins common to both full-/half-stepping and microstepping products available in the SLA7070MS series.

|            |                                          |                      | Clock      |                   |

|------------|------------------------------------------|----------------------|------------|-------------------|

|            |                                          |                      | POS Edge   | POS/NEG Edge      |

| Pin Name   | Low Level                                | High Level           | (Standard) | (Optional Type W) |

| RESET      | Normal operation                         | Logic reset          |            | —                 |

| CW/CCW     | Forward (CW)                             | Reverse (CCW)        |            |                   |

| M1         |                                          |                      |            |                   |

| M2         | Commutation (Slee                        | ep2 is not included) |            |                   |

| M3         |                                          |                      |            |                   |

| REF/SLEEP1 | Normal operation Sleep1 function         |                      |            |                   |

| OVNO       | Non-sync PWM<br>control Sync PWM control |                      |            |                   |

| SYNC       |                                          |                      |            |                   |

#### Table 9-1.Truth Table for Common Input Pins

The Reset function is asynchronous. If an input on the RESET pin is high, the internal logic circuit is reset. At this point, if the REF/SLEEP1 pin stays low, outputs turn on at the starting point of excitation. Note that a signal on the RESET pin cannot control an output disable command.

Voltage across the REF/SLEEP1 pin controls PWM currents and the Sleep1 function.

- When  $V_{REF} \le 1.5$  V (low level), the REF/SLEEP1 pin functions as the reference voltage input for normal operation.

- When  $V_{REF} \ge 2.0 V$  (high level), the REF/SLEEP1 pin disables all outputs. This is the Sleep1 mode that disables the internal linear circuitry and minimizes the main power supply current, IBB. Although much of the internal circuitry is disabled, the logic circuit is still active. If an input signal on the CLOCK pin is asserted, the internal sequencer/translator circuit reacts and sets a step starting point for the next operation.

The Sleep2 function operates in the same way as the Sleep1 function does, except that the internal logic circuit enters the Hold mode. Therefore, in the Sleep2 mode, the internal sequencer/translator circuit is not activated even if a step command signal occurs on the CLOCK input pin.

The Sync function runs only at "2-phase excitation timing." If this function is used at other than the 2-phase excitation timing, an overall balance might collapse because PWM OFF-times and setting currents are different in each of phase A and phase B control scenario. (If this function is used at a point of 1-phase excitation, it does not react as the Sync function does. But there is no problem.) The 2-phase excitation timing is a point where the step reference current ratio of both phases A and B is either of Mode 8 or F.

#### (2) Commutation/Sleep2 Function Setting

Table 9-2 provides the logic for the pins (M1, M2, and M3) which set commutation.

| Funct | tion (Pin N | Name) |                          |                              |

|-------|-------------|-------|--------------------------|------------------------------|

| M1    | M2          | M3    | Full/Half Step           | Microstep                    |

| L     | L           | L     | Full step (Mode 8 fixed) | Full step (Mode 8 fixed)     |

| Н     | L           | L     | Full step (Mode F fixed) | Full step (Mode F fixed)     |

| L     | Н           | L     | Half step (1-2 Phase)    | Half step (1-2 Phase)        |

| Н     | Н           | L     | Half step (Mode F fixed) | Half step (Mode F fixed)     |

| L     | L           | Н     |                          | Quarter step (W1-2 Phase)    |

| Н     | L           | Н     | Clear of typetion        | Eighth step (2W1-2 Phase)    |

| L     | H           | Н     | Sleep2 function          | Sixteenth step (4W1-2 Phase) |

| Н     | H           | Н     |                          | Sleep2 function              |

| Table 9-2. | Truth Table for | Commutation/Sleep     | 2 Functions |

|------------|-----------------|-----------------------|-------------|

|            | indin idolo ioi | oonninatation, oloopi |             |

NOTE: The Sleep2 function disables outputs and reduces the driver supply current (IBB) in the same way as the Sleep1 function does. However, unlike the Sleep1 function, the logic circuitry is put into a "standby" state in the Sleep2 function. Therefore, the sequencer/translator is not activated even if a step command signal occurs on the CLOCK input pin. When awaking from the Sleep2 mode, a delay of 100 µs or longer before sending a clock pulse is recommended.

#### (3) Monitor Output Pins

The SLA7070MS series provides two device status monitor outputs:

- MO pin (microstepping product only) Step sequence

- FLAG pin Protection feature operation

Table 9-3 shows the logic for the monitor output pins.

| Table 9-3. Truth Table for Monitor Output Pins |                                      |                              |  |  |

|------------------------------------------------|--------------------------------------|------------------------------|--|--|

| Pin Name                                       | Low Level                            | High Level                   |  |  |

| МО                                             | Other than 2-phase excitation timing | 2-phase excitation timing    |  |  |

| FLAG                                           | Normal operation                     | Protection circuit operation |  |  |

**NOTE:** The outputs turn off at the point where the protection circuit starts operating. To release the protection state, cycle the logic supply voltage, VDD.

# **10. Logic Input Pins**

The low pass filter (LPF) incorporated with the logic input pins (CLOCK, RESET, CW/CCW, M1, M2, M3, and SYNC) improves noise rejection.

The logic inputs are CMOS input compatible; therefore, they are in a high impedance state. Note that the IC should be used at a fixed input level, either low or high.

If there is a possibility that signals from the microcontroller are in high impedance, add a pull-up/-down resistor. Since outputs from the logic input pins, which function as output ON/OFF controllers, may result in abnormal oscillation, leading to MOSFET breakdown as the worst-case scenario.

# 11. Logic Input Timing

#### (1) Clock Signal

SanKen

a. A low-to-high transition (rising, or POS edge) or a low-to-high then high-to-low transition (rising and falling, or POS/NEG edge) on the CLOCK input signal advances the sequencer/translator. Clock pulse width should be set at 2 µs or longer in both positive and negative polarities. Therefore, clock response frequency is set to 250 kHz.

#### b. Clock Edge Timing

With regard to the input logic of the CW/CCW, M1, M2, and M3 pins, a 1 µs delay should occur both before and after a pulse edge, as setup and hold times (see Figure 11-1). The sequencer logic circuitry might malfunction if the logic polarity is changed during these setup and hold times.

**NOTE:** When awaking from the Sleep1 or Sleep2 mode, a delay of <u> $100 \ \mu s \ or \ longer$ </u> before sending a clock pulse is recommended.

#### (2) Reset Signal

a. Reset Signal Pulse Width

Reset pulse width is equivalent to the hold time of a high level input. It should be 2  $\mu s$  or longer, same as the clock pulse width.

b. Reset Release and Clock Input Timing

When the timing of a reset release (falling edge) and a clock edge is simultaneous, the internal logic might result in an unexpected operation. Therefore, a greater than 5  $\mu$ s delay is required between the falling edge of the RESET input signal and the next rising edge of the CLOCK input signal (see Figure 11-1).

(3) Logic Level Change

Logic level inputs on CW/CCW, M1, M2, and M3 set the translator step direction (CW/CCW) and step mode (M1, M2, and M3; see also Table 9-2, the commutation truth table). Changes to those inputs do not take effect until the rising edge of an input signal on the CLOCK pin. However, depending on the type and state of a motor, there may be errors in motor operation such as step-out. A thorough evaluation on the changes of sequence should be carried out.

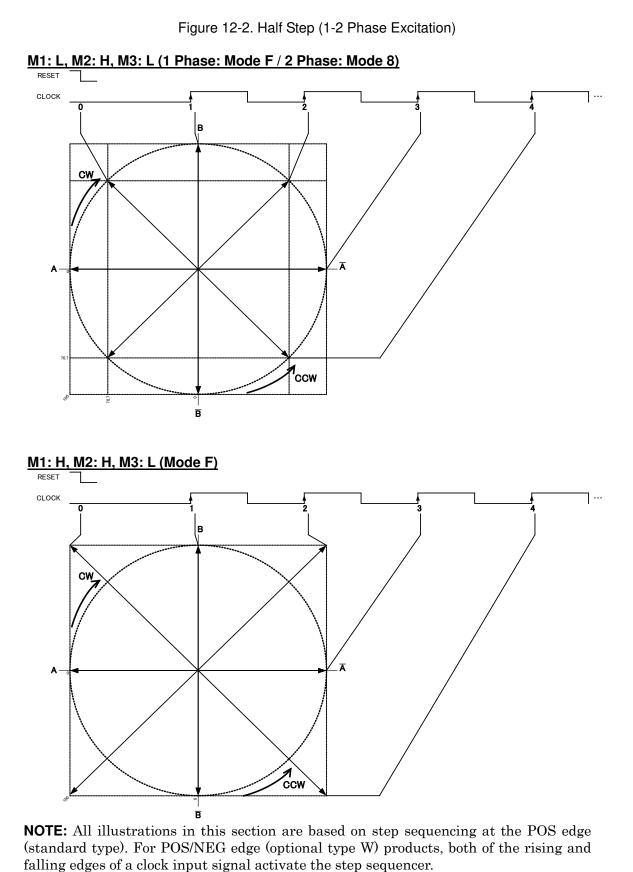

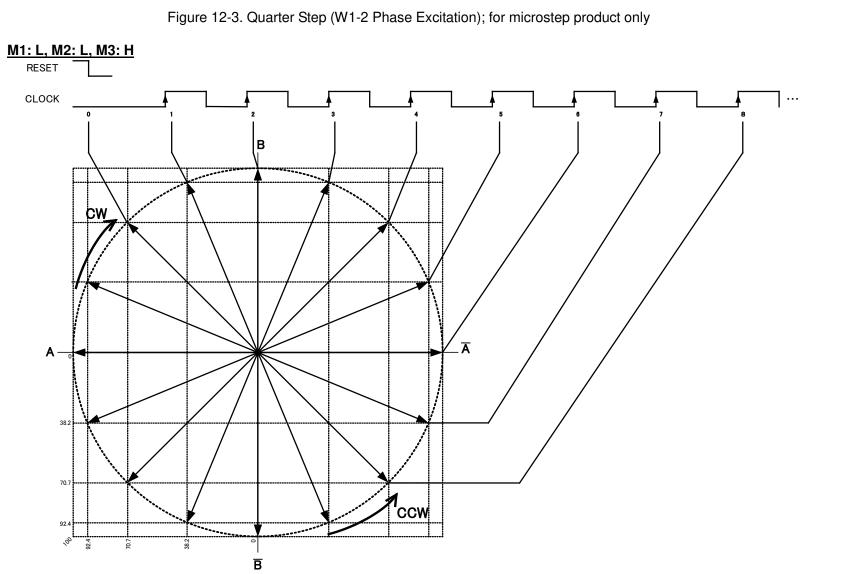

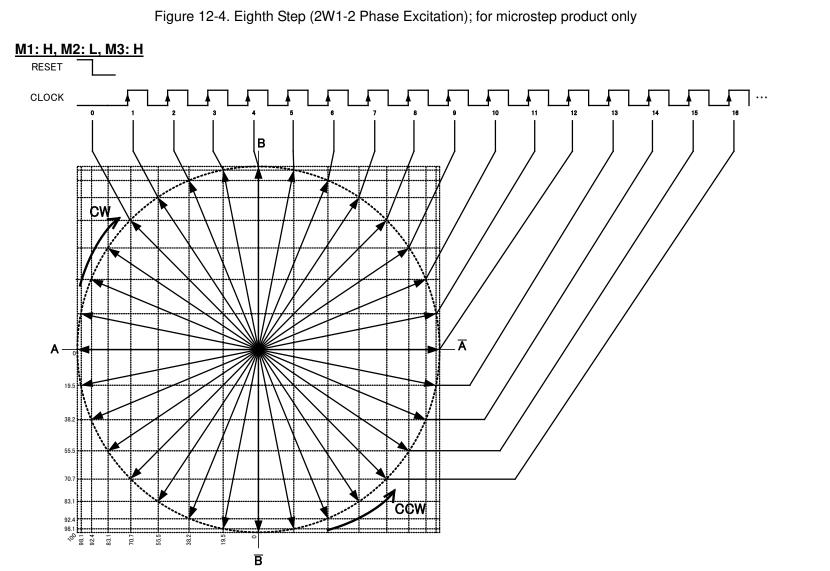

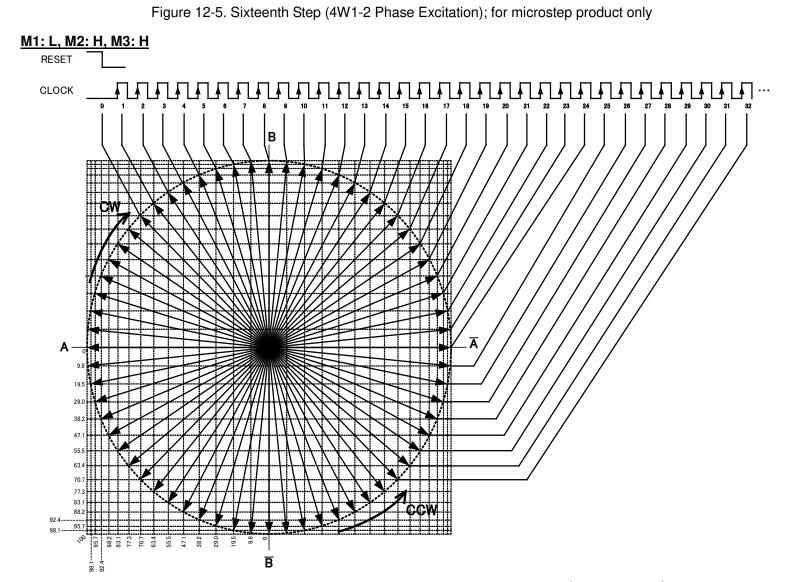

**NOTE:** All illustrations in this section are based on step sequencing at the POS edge (standard type). For POS/NEG edge (optional type W) products, both of the rising and falling edges of a clock input signal activate the step sequencer.

**NOTE:** All illustrations in this section are based on step sequencing at the POS edge (standard type). For POS/NEG edge (optional type W) products, both of the rising and falling edges of a clock input signal activate the step sequencer.

SanKen

**NOTE:** All illustrations in this section are based on step sequencing at the POS edge (standard type). For POS/NEG edge (optional type W) products, both of the rising and falling edges of a clock input signal activate the step sequencer.

Sanken Electric Co., Ltd.

#### Excitation Change Sequence

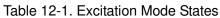

The change of excitation modes is determined by the settings of the excitation pins (M1, M2, and M3) before and after a step signal. Table 12-1 shows each excitation mode state setting.

|           | Internal Sequence State <sup>1)</sup> Step Sequencing <sup>2)</sup> |        |          |                                           |        |        |            |             |            |                     |                     |

|-----------|---------------------------------------------------------------------|--------|----------|-------------------------------------------|--------|--------|------------|-------------|------------|---------------------|---------------------|

| Direction | Phase A Phase B                                                     |        |          | 2 Phase (Full Stap) 1.2 Phase (Half Stap) |        |        | W1-2 Phase | 2W1-2 4W1-2 |            |                     |                     |

|           | PWM                                                                 | Mode   | PWM      | Mode                                      | Mode 8 | Mode F | Mode 8/F   | Mode F      | (1/4 Step) | Phase<br>(1/8 Step) | Phase<br>(1/16 Step |

|           | Α                                                                   | 8      | В        | 8                                         | Х      | ХХ     | Х          | ХХ          | Х          | X                   | Х                   |

|           | А                                                                   | 7      | В        | 9                                         |        |        |            |             |            |                     | Х                   |

|           | Α                                                                   | 6      | В        | A                                         |        |        |            |             |            | Х                   | Х                   |

|           | A                                                                   | 5      | В        | B                                         |        |        |            |             | ~          | V                   | X                   |

|           | A                                                                   | 4      | B        | C<br>D                                    |        |        |            |             | Х          | Х                   | X                   |

|           | A                                                                   | 2      | B        | E                                         |        |        |            |             | 1 1        | Х                   | X                   |

|           | A                                                                   | 1      | B        | F                                         |        |        |            |             | 1          | ~                   | X                   |

|           | -                                                                   | -      | В        | F                                         |        |        | Х          | Х           | Х          | Х                   | Х                   |

|           | /A                                                                  | 1      | В        | F                                         |        |        |            |             | 1          |                     | Х                   |

|           | /A                                                                  | 2      | В        | Е                                         |        |        |            |             |            | Х                   | Х                   |

|           | /A                                                                  | 3      | В        | D                                         |        |        |            |             |            |                     | Х                   |

| CCW       | /A                                                                  | 4      | В        | С                                         |        |        |            |             | Х          | Х                   | Х                   |

|           | /A                                                                  | 5      | B        | B                                         |        |        |            |             |            | v                   | X                   |

| Ť         | /A<br>/A                                                            | 6<br>7 | B        | A<br>9                                    |        |        |            |             | 1 1        | Х                   | X                   |

|           | /A                                                                  | 8      | B        | 8                                         | Х      | ХХ     | Х          | ХХ          | Х          | Х                   | X                   |

|           | /A                                                                  | 9      | B        | 7                                         |        |        |            |             |            |                     | X                   |

|           | /A                                                                  | A      | В        | 6                                         |        |        |            |             |            | Х                   | Х                   |

|           | /A                                                                  | В      | В        | 5                                         |        |        |            |             |            |                     | Х                   |

|           | /A                                                                  | С      | В        | 4                                         |        |        |            |             | Х          | Х                   | Х                   |

|           | /A                                                                  | D      | В        | 3                                         |        |        |            |             |            | V                   | Х                   |

|           | /A                                                                  | E<br>F | B        | 2                                         |        |        |            |             |            | Х                   | X                   |

|           | /A<br>/A                                                            | F      | B<br>-   | -                                         |        |        | Х          | Х           | Х          | Х                   | X                   |

|           | /A<br>/A                                                            | F      | /B       | 1                                         |        |        | ~          | ^           | ~          | ~                   | X                   |

|           | /A                                                                  | E      | /B       | 2                                         |        |        |            |             |            | Х                   | X                   |

|           | /A                                                                  | D      | /B       | 3                                         |        |        |            |             |            |                     | Х                   |

|           | /A                                                                  | С      | /B       | 4                                         |        |        |            |             | Х          | Х                   | Х                   |

|           | /A                                                                  | В      | /B       | 5                                         |        |        |            |             |            |                     | Х                   |

|           | /A                                                                  | A      | /B       | 6                                         |        |        |            |             |            | Х                   | Х                   |

|           | /A                                                                  | 9      | /B       | 7                                         | v      | ~~~    | v          | ~~          | ~          | v                   | X                   |

|           | /A<br>/A                                                            | 8      | /B<br>/B | 8<br>9                                    | Х      | XX     | Х          | XX          | Х          | Х                   | X                   |

|           | /A<br>/A                                                            | 6      | /B       | A                                         |        |        |            |             |            | Х                   | X                   |

|           | /A                                                                  | 5      | /B       | B                                         |        |        |            |             |            |                     | Х                   |

|           | /A                                                                  | 4      | /B       | С                                         |        |        |            |             | Х          | Х                   | Х                   |

|           | /A                                                                  | 3      | /B       | D                                         |        |        |            |             |            |                     | Х                   |

|           | /A                                                                  | 2      | /B       | Е                                         |        |        |            |             |            | Х                   | Х                   |

|           | /A                                                                  | 1      | /B       | F                                         |        |        | v          | V           | × ×        | V                   | Х                   |

|           | A                                                                   | - 1    | /B<br>/B | F                                         |        |        | Х          | Х           | Х          | Х                   | X                   |

|           | A                                                                   | 2      | /в<br>/В | E                                         |        |        |            |             | +          | Х                   | X                   |

|           | A                                                                   | 3      | /B       | D                                         |        |        |            |             | 1 1        | ~                   | X                   |

|           | A                                                                   | 4      | /B       | C                                         |        |        |            |             | Х          | Х                   | X                   |

|           | Α                                                                   | 5      | /B       | В                                         |        |        |            |             |            |                     | Х                   |

|           | Α                                                                   | 6      | /B       | Α                                         |        |        |            |             |            | Х                   | Х                   |

|           | A                                                                   | 7      | /B       | 9                                         | V      | ~~~    |            | ~~~         |            | V                   | X                   |

|           | A                                                                   | 8      | /B<br>/B | 8                                         | Х      | XX     | Х          | XX          | Х          | Х                   | X                   |

| •         | A                                                                   | 9<br>A | /B<br>/B | 76                                        |        |        |            |             |            | Х                   | X                   |

| CW        | A                                                                   | B      | /B       | 5                                         |        |        |            |             |            | Λ                   | X                   |

|           | A                                                                   | C      | /B       | 4                                         |        |        |            |             | Х          | Х                   | X                   |

|           | Α                                                                   | D      | /B       | 3                                         |        |        |            |             |            |                     | Х                   |

|           | А                                                                   | Е      | /B       | 2                                         |        |        |            |             |            | Х                   | Х                   |

|           | А                                                                   | F      | /B       | 1                                         |        |        |            |             |            |                     | Х                   |

|           | A                                                                   | F      | •        | -                                         |        |        | Х          | Х           | Х          | Х                   | Х                   |

|           | A                                                                   | F      | В        | 1                                         |        |        |            |             |            | v                   | X                   |

|           | A                                                                   | E<br>D | B        | 2                                         |        |        |            |             | +          | Х                   | X                   |

|           | A                                                                   | C      | B        | 3                                         |        |        | -          |             | Х          | Х                   | X                   |

|           | A                                                                   | B      | B        | 5                                         |        |        |            |             | ^          | ~                   | X                   |

|           | A                                                                   | A      | B        | 6                                         |        |        |            |             |            | Х                   | X                   |

|           | А                                                                   | 9      | В        | 7                                         |        |        |            |             | 1          |                     | Х                   |

<sup>1)</sup> Each mode is defined accordingly to the SLA7070M series.

<sup>2)</sup> XX indicates that sequence state is Mode 8; but step reference current ratio is Mode F. Mode F has a step reference current ratio of 100%, and a PWM OFF-time of 12 µs.

# **13. Individual Circuit Descriptions**

#### (1) Monolithic IC (MIC)

Sequencer Logic

A single clock strategy is employed for step timing. An input on the CW/CCW pin determines the direction of motor rotation. Excitation mode is controlled by the combination of the M1, M2, and M3 input logic levels. See Section 9 for truth tables, and Section 11 for input timings.

#### • DAC (D-to-A Converter)

DACs that generate the reference voltage for controlling current. In microstep sequencing, the current at each step is set by the values of a sense resistor ( $R_s$ ), a reference voltage ( $V_{REF}$ ), the output voltage of the DACs, controlled by the output of the sequencer/translator circuit. For the step reference current ratios, see the electrical characteristics tables given in Section 4.

#### • PWM Control

Circuits that allow self-excitation PWM current controlling with a fixed OFF-time are used in this series. Each built-in oscillator (OSC) determines an OFF-time and a blanking time for proper PWM operation. The operation mechanism of the PWM control circuitry is identical to that of the SLA7070M family. For more detailed functional descriptions, see Section 14.

#### Synchronous Control

A synchronous chopping circuit that prevents occasional motor noise during a hold state which normally results from the asynchronous PWM operation of both motor phases. When the SYNC input pin is set to logic high, the circuit sends a timing signal that simultaneously turns off the chopping of phases A and B.

This function adopts the same operation mechanism applied to the SLA7070M series. Therefore, the use of the synchronous control during normal stepping is not recommended because, it produces less motor torque or may cause motor vibration due to staircase current.

The use of the synchronous control when the motor is not in operation is only allowed in 2-phase excitation timing, because the differences in current control values and PWM OFF-times between phases A and B exist at other excitation timings; otherwise, these two phases may not be synchronized or may be greatly disrupted in their current control values.

#### • Regulator Circuit

An integrated regulator circuit is used for powering the output MOSFET gate drive circuit (pre-driver) and other internal linear circuits.

#### • Protection Circuit

Built-in protection circuits against motor coil opens or shorts are provided. This protection is activated by sensing the voltage across internal sense resistors, R<sub>S</sub>. Therefore, an overcurrent condition cannot be detected which results from the OUTx pins or SENSEx pins, or both, shorting to GND. The protection against motor coil opens is available only during PWM operation; therefore, it does not work at constant voltage driving, when the motor is rotating at a high speed.

The operation of the protection circuit disables all outputs. To come out of the Protection mode, cycle the logic supply,  $V_{DD}$ . For more details, see the next section.

#### • TSD Circuit

A TSD circuit that protects a driver by shifting an output to the Disable mode is incorporated. When the temperature of the product control IC (MIC) rises and becomes higher than its threshold, the circuit starts operating. To reset the function, perform the same steps as described in the Protection Circuit description.

#### (2) Output MOSFET Chip

The type of MOSFET chips to be mounted varies according to which of the two different output current ratings has been selected. For specifications, see Table 4-5.

| Rated Current<br>(A) | Resistance<br>(ΩTyp.) |  |

|----------------------|-----------------------|--|

| 2.0                  | 0.25                  |  |

| 3.0                  | 0.18                  |  |

**NOTE:** Each resistance shown above includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

#### (3) Sense Resistor

Sense resistors are incorporated in this series to detect motor current. The resistance of these varies according to which of the two different output current ratings has been selected. For specifications, see Table 4-5.

| Rated Current<br>(A) | Resistance<br>(ΩTyp.) |  |  |

|----------------------|-----------------------|--|--|

| 2.0                  | 0.205                 |  |  |

| 3.0                  | 0.155                 |  |  |

**NOTE:** Each resistance shown above includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

# **14. Functional Descriptions**

SanKen

(1) PWM Current Control

[1] Blanking Time

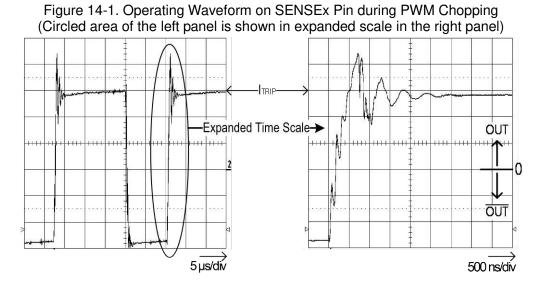

An actual operating waveform on the SENSEx pin when driving a motor is shown in Figure 14-1.

Immediately after a PWM turns off, ringing (or spike) noise on the SENSEx pin is observed for a period of a few microseconds. Ringing noise can be generated by various causes, such as capacitance between motor coils or inappropriate motor wiring.

Each pair of outputs is controlled by a fixed OFF-time PWM current-control circuit that limits the load current to a target value, ITRIP. Initially, an output is enabled and then currents flow through the motor winding and the current sense resistors. When the voltage across the current sense resistors equals the DAC output voltage,  $V_{TRIP}$ , the current sense comparator resets a PWM latch. This turns off the driver for the fixed OFF-time, during which the load inductance causes the current to recirculate for the OFF-time period. Therefore, if the ringing noise on the current sense resistor(s) equals and surpasses  $V_{TRIP}$ , the PWM turns off (i.e., a hunting phenomenon).

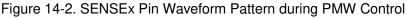

To prevent this phenomenon, a blanking time is set to override signals from the current sense comparator for a certain period immediately after the PWM turns on (Figure 14-2).

#### [2] Blanking Time and Hunting Phenomenon

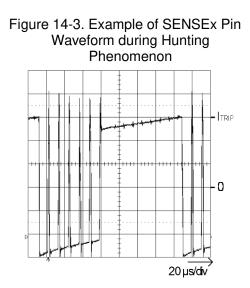

Although current control can be improved by shortening a blanking time, the degree of margin to a ringing noise decreases simultaneously. For this reason, when a motor is driven by the device, a hunting phenomenon may occur. Figure 14-3 shows an example of the waveform pattern when the phenomenon occurs.

In order to overcome this problem, Sanken has released a new option, "type B", which offers a longer blanking time. Having the longer blanking time, the optional type B can improve problems such as torque reduction and huge motor noise that are occasionally found during the hunting phenomenon.

#### [3] Blanking Time Difference

Table 14-1 shows characteristic differences between two blanking times, shorter and longer blanking periods.

This comparison is based on the case where drive conditions, such as a motor, motor power supply voltage, REF input voltage, and circuit constant were kept the same while only the indicated parameters were changed.

| Table 14-1. Onaracteristic Companson of Difference in Dianking Time          |                    |         |  |  |  |

|------------------------------------------------------------------------------|--------------------|---------|--|--|--|

| Parameter                                                                    | Better Performance |         |  |  |  |

| Internal blanking time                                                       | Short              | Long    |  |  |  |

| Minimum PWM ON-time                                                          | Small 🗲            |         |  |  |  |

| Ringing noise suppression                                                    |                    | → Large |  |  |  |

| Minimum coil current                                                         | Small 🗲            |         |  |  |  |

| Coil current waveform<br>distortion at a high rotation<br>(mainly microstep) |                    | → Large |  |  |  |

Table 14-1. Characteristic Comparison of Difference in Blanking Time

Brief descriptions for each parameter are as follows:

• Minimum PWM ON-time, t<sub>ON(min)</sub>

This series has a blanking time that is effectively selected and fixed by the PWM control. Therefore, even if an application attempts to shorten its ON-time for limiting currents, it would not go below the fixed blanking time. Minimum PWM ON-time refers to the time when an output is on during this blanking time period, that is, when an output MOSFET is actually turned on. In other words, a blanking time determines a minimum ON-time ("Small" in Table 14-1).

Minimum Coil Current

This refers to the coil current when the PWM control is performed during a minimum PWM ON-time. In other words, the device with a shorter blanking time can reduce more coil current.

Coil Current Waveform Distortion during High-Velocity Revolution

While a microstep drive is active, the  $I_{TRIP}$  value changes to a predetermined value in accordance with a clock input. The  $I_{TRIP}$  value (internal reference voltage splitting ratio) is then set up to be a sine wave. Because the PWM control of motor coil current is set according to the  $I_{TRIP}$  value, (the envelope of) the motor coil current will also be controlled to be sine wave-like.