# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## SMC128CF SMC01GCF SMC08GCF

128-Mbyte, 1-Gbyte, 8-Gbyte, 3.3/5 V supply, CompactFlash™ card

#### Preliminary Data

## **Features**

- Custom-designed, highly-integrated memory controller

- Fully compliant with CompactFlash<sup>TM</sup> specification 3.0

- Fully compatible with PCMCIA specification 2.1

- PC Card ATA interface supported

- True IDE mode compatible

- Up to PIO mode 6 supported

- Up to 4 multi-word DMA supported

- Hardware RS-ECC (4 symbols in a 512byte sector)

- Up to mode 4 UDMA

- Small form factor

- 36.4 mm x 42.8 mm x 3.3 mm

- Low-power CMOS technology

- 3.3 V / 5 V power supply

- Power saving mode (with automatic wake-up)

- Hot swappable

- Flash memory power-down logic and write protect control

- Power loss protection

| Table 1. Device summary |                  |                     |                         |  |  |  |  |  |  |

|-------------------------|------------------|---------------------|-------------------------|--|--|--|--|--|--|

| Reference               | Root part number | Package form factor | Operating voltage range |  |  |  |  |  |  |

|                         | SMC128CF         |                     |                         |  |  |  |  |  |  |

| SMCxxxCF                | SMC01GCF         | CF type I           | 3.3 V + 10%, 5 V + 10%  |  |  |  |  |  |  |

|                         | SMC08GCF         |                     |                         |  |  |  |  |  |  |

change without notice.

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to

1/29

- High performance

- Up to 66 Mbyte/s transfer rate

- Sustained write performance (host to card): 18.3 Mbyte/s

- Sustained read performance (host to card: 41.8 Mbyte/s)

- Available densities (formatted) 128 Mbytes, 1 Gbyte and 8 Gbytes

- Operating system support

- Standard software drivers operation

## Contents

| 1  | Description                                                          |

|----|----------------------------------------------------------------------|

| 2  | Capacity specification7                                              |

| 3  | Card physical                                                        |

|    | 3.1 Physical description                                             |

| 4  | Electrical interface9                                                |

|    | 4.1 Electrical description                                           |

|    | 4.2 Electrical specification 17                                      |

|    | 4.3 Current measurement 17                                           |

|    | 4.4 Additional requirements for CompactFlash advanced timing mode 18 |

| 5  | Command interface 19                                                 |

| 6  | Card configuration                                                   |

| 7  | Host configuration requirements 20                                   |

| 8  | Software interface                                                   |

| 9  | CF-ATA registers                                                     |

| 10 | CF-ATA command description 20                                        |

| 11 | CIS information (typical) 21                                         |

| 12 | Package mechanical                                                   |

| 13 | Ordering information                                                 |

| 14 | Revision history                                                     |

## List of tables

| Table 1.  | Device summary               |

|-----------|------------------------------|

| Table 2.  | System performance           |

| Table 3.  | Current consumption          |

| Table 4.  | Environmental specifications |

| Table 5.  | Physical dimensions          |

| Table 6.  | CF capacity specification    |

| Table 7.  | Pin assignment and pin type  |

| Table 8.  | Signals description          |

| Table 9.  | Absolute maximum conditions  |

| Table 10. | Input power                  |

| Table 11. | Input leakage current        |

| Table 12. | Input characteristics        |

| Table 13. | Output drive type            |

| Table 14. | Output drive characteristics |

| Table 15. | Ordering information scheme  |

| Table 16. | Document revision history    |

## List of figures

| Figure 1. | CompactFlash memory card block diagram      | . 8 |

|-----------|---------------------------------------------|-----|

| Figure 2. | Type I CompactFlash memory card dimensions. | 26  |

## 1 Description

The CompactFlash is a small form factor non-volatile memory card which provides high capacity data storage. Its aim is to capture, retain and transport data, audio and images, facilitating the transfer of all types of digital information between a large variety of digital systems.

The card operates in three basic modes:

- PCMCIA I/O mode

- PCMCIA memory mode

- True IDE mode

The CompactFlash also supports advanced timing modes. Advanced timing modes are PCMCIA style I/O modes that are 100 ns or faster, PCMCIA memory modes that are 100 ns or faster, true IDE PIO up to mode 6, multi-word DMA up to mode 4, and UDMA up to mode 4.

It conforms to the PC card specification when operating in the PCMCIA I/O mode, and in the PCMCIA memory mode (personal computer memory card international association standard, JEIDA in Japan), and to the ATA specification when operating in true IDE mode. CompactFlash cards can be used with passive adapters in a PC-card type II or type III socket.

The card has an internal intelligent controller which manages interface protocols, data storage and retrieval as well as hardware RS-code error correction code (ECC), defect handling, diagnostics and clock control. Once the card has been configured by the host, it behaves as a standard ATA (IDE) disk drive. The hardware RS-code ECC allows to detect and correct 4 bytes per 512 bytes.

The specification has been realized and approved by the CompactFlash association (CFA). This non-proprietary specification enables users to develop CF products that function correctly and are compatible with future CF design.

The system highlights are shown in Table 2, Table 3, Table 4, Table 5, and Table 6.

#### **Related documentation**

- PCMCIA PC card standard, 1995

- PCMCIA PC card ATA specification, 1995

- AT attachment interface document, american national standards institute, X3.221-1994

- CF+ and CompactFlash specification revision 3.0.

#### Table 2.System performance

| System performanc          | e     | Мах                        | Unit    |

|----------------------------|-------|----------------------------|---------|

| Sleep to write             |       | 0.022                      | ms      |

| Sleep to read              |       | 0.070                      | ms      |

| Power-up to ready          |       | 493                        | ms      |

| Data transfer rate (burst) |       | 66 (440X) <sup>(1)</sup>   | Mbyte/s |

| Sustained read             |       | 41.8 (278X) <sup>(1)</sup> | Mbyte/s |

| Sustained write            |       | 18.3 (122X) <sup>(1)</sup> | Mbyte/s |

| Command to DRQ             | Read  | 33.7                       |         |

|                            | Write | 8.5                        | μs      |

440X, 278X and 122X, speed grade markings where 1X = 150 Kbytes/s. All values are measured for an ambient temperature of 25 °C. They refer to the 1-Gbyte CompactFlash card in PIO mode 6, cycle time 80 ns, File size = 20 Mbytes sequential; sector count = 256.

#### Table 3.Current consumption<sup>(1)</sup>

| Current consumption (typ) | 3.3 V | 5 V | Unit |

|---------------------------|-------|-----|------|

| Read                      | 32    | 44  | mA   |

| Write                     | 79    | 83  | mA   |

| Standby                   | 0.5   | 0.5 | mA   |

| Sleep mode                | 0.5   | 0.5 | mA   |

1. All values are typical at 25 °C and nominal supply voltage and refer to 1-Gbyte CompactFlash card, operating in PIO mode.

#### Table 4.Environmental specifications

| Environmental specifications | Operating    | Non-operating                   |  |  |

|------------------------------|--------------|---------------------------------|--|--|

| Temperature                  | –40 to 85 °C | –50 to 100 °C                   |  |  |

| Humidity (non-condensing)    | N/A          | 85% RH, at 85 °C                |  |  |

| Salt water spray             | N/A          | 3% NaCl at 35 °C <sup>(1)</sup> |  |  |

| Vibration (peak -to-peak)    | N/A          | 30Gmax.                         |  |  |

| Shock                        | N/A          | 3,000Gmax.                      |  |  |

1. MIL STD METHOD 1009.

#### Table 5. Physical dimensions

| Physical din  | Unit |    |

|---------------|------|----|

| Width         | 42.8 | mm |

| Height        | 36.4 | mm |

| Thickness     | 3.3  | mm |

| Weight (typ.) | 10   | g  |

## 2 Capacity specification

*Table 6* shows the specific capacity for the various CF models and the default number of heads, sector/tracks and cylinders.

| Root part<br>number | Capacity   | Default_cylinders | Default_<br>heads | Default_sectors<br>_track | Sectors_card | Addressable<br>capacity (byte) |

|---------------------|------------|-------------------|-------------------|---------------------------|--------------|--------------------------------|

| SMC128CF            | 128 Mbytes | 994               | 8                 | 32                        | 254,464      | 130,285,568                    |

| SMC01GCF            | 1 Gbyte    | 1,991             | 16                | 63                        | 2,006,928    | 1,003,464,000                  |

| SMC08GCF            | 8 Gbytes   | 15,949            | 16                | 63                        | 16,055,424   | 8,231,215,104                  |

Table 6.CF capacity specification

## 3 Card physical

## 3.1 Physical description

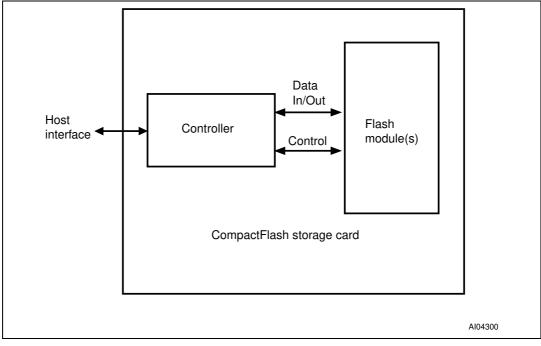

The CompactFlash memory card contains a single chip controller and flash memory module(s). The controller interfaces with a host system allowing data to be written to and read from the flash memory module(s). *Figure 1* shows the block diagram of the CompactFlash memory card.

The card is offered in a type I package with a 50-pin connector consisting of two rows of 25 female contacts on 50 mil (1.27 mm) centers. *Figure 2* shows type I card dimensions.

Figure 1. CompactFlash memory card block diagram

## 4 Electrical interface

### 4.1 Electrical description

The CompactFlash memory card operates in three basic modes:

- PC card ATA using I/O mode

- PC card ATA using memory mode

- True IDE mode, which is compatible with most disk drives.

The signal/pin assignments are listed in *Table 7* Low active signals have a '-' prefix. Pin types are input, output or input/output.

The configuration of the card is controlled using the standard PCMCIA configuration registers starting at address 200h in the attribute memory space of the memory card.

*Table 8* describes the I/O signals. Inputs are signals sourced from the host while outputs are signals sourced from the card. The signals are described for each of the three operating modes.

All outputs from the card are totem pole except the data bus signals that are bi-directional tri-state. Refer to the *Section 4.2: Electrical specification* for definitions of input and output type.

| Pin              | PC card memory mode |             |                 | PC card I/O mode |             |                 | True IDE mode      |             |                 |

|------------------|---------------------|-------------|-----------------|------------------|-------------|-----------------|--------------------|-------------|-----------------|

| num              | Signal<br>name      | Pin<br>type | In, Out<br>type | Signal<br>name   | Pin<br>type | In, Out<br>type | Signal<br>name     | Pin<br>type | In, Out<br>type |

| 1                | GND                 |             | Ground          | GND              |             | Ground          | GND                |             | Ground          |

| 2                | D03                 | I/O         | I1Z,OZ3         | D03              | I/O         | I1Z,OZ3         | D03                | I/O         | I1Z,OZ3         |

| 3                | D04                 | I/O         | I1Z,OZ3         | D04              | I/O         | I1Z,OZ3         | D04                | I/O         | I1Z,OZ3         |

| 4                | D05                 | I/O         | I1Z,OZ3         | D05              | I/O         | I1Z,OZ3         | D05                | I/O         | I1Z,OZ3         |

| 5                | D06                 | I/O         | I1Z,OZ3         | D06              | I/O         | I1Z,OZ3         | D06                | I/O         | I1Z,OZ3         |

| 6                | D07                 | I/O         | I1Z,OZ3         | D07              | I/O         | I1Z,OZ3         | D07                | I/O         | I1Z,OZ3         |

| 7                | –CE1                | I           | I3U             | –CE1             | I           | I3U             | -CS0               | I           | I3Z             |

| 8                | A10                 | I           | I1Z             | A10              | I           | I1Z             | A10 <sup>(2)</sup> | I           | I1Z             |

| 9 <sup>(1)</sup> | –OE                 | I           | I3U             | –OE              | I           | I3U             | -ATASEL            | I           | I3U             |

| 10               | A09                 | I           | l1Z             | A09              | I           | l1Z             | A09 <sup>(2)</sup> | I           | l1Z             |

| 11               | A08                 | I           | l1Z             | A08              | I           | l1Z             | A08 <sup>(2)</sup> | I           | l1Z             |

| 12               | A07                 | Ι           | l1Z             | A07              | Ι           | l1Z             | A07 <sup>(2)</sup> | I           | l1Z             |

| 13               | V <sub>CC</sub>     |             | Power           | V <sub>CC</sub>  |             | Power           | V <sub>CC</sub>    |             | Power           |

| 14               | A06                 | I           | I1Z             | A06              | I           | l1Z             | A06 <sup>(2)</sup> | I           | l1Z             |

| 15               | A05                 | I           | l1Z             | A05              | I           | l1Z             | A05 <sup>(2)</sup> | I           | l1Z             |

| 16               | A04                 | Ι           | l1Z             | A04              | I           | l1Z             | A04 <sup>(2)</sup> | I           | l1Z             |

Table 7.Pin assignment and pin type

| Di         | PC card memory mode     |             |                 | PC ca                | rd I/O r    | node            | True IDE mode                |             |                 |

|------------|-------------------------|-------------|-----------------|----------------------|-------------|-----------------|------------------------------|-------------|-----------------|

| Pin<br>num | Signal<br>name          | Pin<br>type | In, Out<br>type | Signal<br>name       | Pin<br>type | In, Out<br>type | Signal<br>name               | Pin<br>type | In, Out<br>type |

| 17         | A03                     | I           | l1Z             | A03                  | I           | l1Z             | A03 <sup>(2)</sup>           | I           | l1Z             |

| 18         | A02                     | I           | l1Z             | A02                  | I           | l1Z             | A02                          | I           | l1Z             |

| 19         | A01                     | I           | l1Z             | A01                  | I           | l1Z             | A01                          | I           | l1Z             |

| 20         | A00                     | I           | l1Z             | A00                  | I           | I1Z             | A00                          | I           | l1Z             |

| 21         | D00                     | I/O         | I1Z,OZ3         | D00                  | I/O         | I1Z,OZ3         | D00                          | I/O         | I1Z,OZ3         |

| 22         | D01                     | I/O         | I1Z,OZ3         | D01                  | I/O         | I1Z,OZ3         | D01                          | I/O         | I1Z,OZ3         |

| 23         | D02                     | I/O         | I1Z,OZ3         | D02                  | I/O         | I1Z,OZ3         | D02                          | I/O         | I1Z,OZ3         |

| 24         | WP                      | 0           | OT3             | -IOIS16              | 0           | OT3             | -IOIS16                      | 0           | ON3             |

| 25         | –CD2                    | 0           | Ground          | –CD2                 | 0           | Ground          | –CD2                         | 0           | Ground          |

| 26         | –CD1                    | 0           | Ground          | –CD1                 | 0           | Ground          | –CD1                         | 0           | Ground          |

| 27         | D11 <sup>(3)</sup>      | I/O         | I1Z,OZ3         | D11 <sup>(3)</sup>   | I/O         | I1Z,OZ3         | D11 <sup>(3)</sup>           | I/O         | I1Z,OZ3         |

| 28         | D12 <sup>(3)</sup>      | I/O         | I1Z,OZ3         | D12 <sup>(3)</sup>   | I/O         | I1Z,OZ3         | D12 <sup>(3)</sup>           | I/O         | I1Z,OZ3         |

| 29         | D13 <sup>(3)</sup>      | I/O         | I1Z,OZ3         | D13 <sup>(3)</sup>   | I/O         | I1Z,OZ3         | D13 <sup>(3)</sup>           | I/O         | I1Z,OZ3         |

| 30         | D14 <sup>(3)</sup>      | I/O         | I1Z,OZ3         | D14 <sup>(3)</sup>   | I/O         | I1Z,OZ3         | D14 <sup>(3)</sup>           | I/O         | I1Z,OZ3         |

| 31         | D15 <sup>(3)</sup>      | I/O         | I1Z,OZ3         | D15 <sup>(3)</sup>   | I/O         | I1Z,OZ3         | D15 <sup>(3)</sup>           | I/O         | I1Z,OZ3         |

| 32         | -CE2 <sup>(3)</sup>     | I           | I3U             | -CE2 <sup>(3)</sup>  | I           | ISU             | -CS1 <sup>(3)</sup>          | I           | I3Z             |

| 33         | –VS1                    | 0           | Ground          | –VS1                 | 0           | Ground          | –VS1                         | 0           | Ground          |

| 34         | –IORD                   | I           | I3U             | -IORD                | I           | I3U             | -IORD<br>HSTROBE<br>-HDMARDY | I           | 13Z             |

| 35         | –IOWR                   | I           | I3U             | –IOWR                | I           | I3U             | -IOWR<br>STOP                | I           | I3Z             |

| 36         | –WE                     | I           | I3U             | –WE                  | I           | I3U             | -WE <sup>(4)</sup>           | I           | I3U             |

| 37         | READY                   | 0           | OT1             | -IREQ                | 0           | OT1             | INTRQ                        | 0           | OZ1             |

| 38         | V <sub>CC</sub>         |             | Power           | V <sub>CC</sub>      |             | Power           | V <sub>CC</sub>              |             | Power           |

| 39         | -CSEL <sup>(5)(3)</sup> | I           | I2Z             | -CSEL <sup>(5)</sup> | I           | I2Z             | -CSEL <sup>(5)</sup>         | I           | I2U             |

| 40         | -VS2                    | 0           | OPEN            | -VS2                 | 0           | OPEN            | -VS2                         | 0           | OPEN            |

| 41         | RESET                   | I           | I2Z             | RESET                | I           | I2Z             | -RESET                       | I           | I2Z             |

| 42         | –WAIT                   | 0           | OT1             | -WAIT                | 0           | OT1             | IORDY<br>DDMARDY<br>DSTROBE  | 0           | ON1             |

| 43         | -INPACK                 | 0           | OT1             | -INPACK              | 0           | OT1             | DMARQ                        | 0           | OZ1             |

| 44         | –REG                    | I           | I3U             | –REG                 | I           | ISU             | -DMACK <sup>(6)</sup>        | I           | I3U             |

| 45         | BVD2                    | I/O         | I1U,OT1         | -SPKR                | I/O         | I1U,OT1         | -DASP                        | I/O         | I1U,ON1         |

Table 7.

Pin assignment and pin type (continued)

| Pin<br>num | PC card memory mode |             |                 | PC card I/O mode   |             |                 | True IDE mode      |             |                 |

|------------|---------------------|-------------|-----------------|--------------------|-------------|-----------------|--------------------|-------------|-----------------|

|            | Signal<br>name      | Pin<br>type | In, Out<br>type | Signal<br>name     | Pin<br>type | In, Out<br>type | Signal<br>name     | Pin<br>type | In, Out<br>type |

| 46         | BVD1                | I/O         | I1U,OT1         | -STSCHG            | I/O         | I1U,OT1         | -PDIAG             | I/O         | I1U,ON1         |

| 47         | D08 <sup>(3)</sup>  | I/O         | I1Z,OZ3         | D08 <sup>(3)</sup> | I/O         | I1Z,OZ3         | D08 <sup>(3)</sup> | I/O         | I1Z,OZ3         |

| 48         | D09 <sup>(3)</sup>  | I/O         | I1Z,OZ3         | D09 <sup>(3)</sup> | I/O         | I1Z,OZ3         | D09 <sup>(3)</sup> | I/O         | I1Z,OZ3         |

| 49         | D10 <sup>(3)</sup>  | I/O         | I1Z,OZ3         | D10 <sup>(3)</sup> | I/O         | I1Z,OZ3         | D10 <sup>(3)</sup> | I/O         | I1Z,OZ3         |

| 50         | GND                 |             | Ground          | GND                |             | Ground          | GND                |             | Ground          |

#### Table 7. Pin assignment and pin type (continued)

1. For True IDE mode, pin 9 is grounded.

2. The signal should be grounded by the host.

3. These signals are required only for 16-bit accesses and not required when installed in 8-bit systems. Devices should allow for 3-state signals not to consume current.

4. The signal should be tied to  $V_{\mbox{\scriptsize CC}}$  by the host.

5. The -CSEL signal is ignored by the card in PC card modes. However, because it is not pulled up on the card in these modes it should not be left floating by the host in PC card modes. In these modes, the pin is normally connected by the host to PC card A25 or grounded by the host.

6. When the device does not operate in DMA mode, the signal should be held High or tied to  $V_{CC}$  by the host. To ensure proper operation with older hosts when DMA mode is disabled, the card should ignore the –DMACK signal.

| Table 8. Signals description | ١ |

|------------------------------|---|

|------------------------------|---|

| Signal name                        | Dir. | Pin                      | Description                                                                                                                                                                                        |    |    |    |       |        |                                                                                                                                        |

|------------------------------------|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| A10 to A0<br>(PC card memory mode) |      | 8,10,11,12,              | Used (with –REG) to select: the I/O port address registers, the memory mapped port address registers, a byte in the card information structure and its configuration control and status registers. |    |    |    |       |        |                                                                                                                                        |

| A10 to A0<br>(PC card I/O mode)    |      | 14,15,16,17,<br>18,19,20 | Same as PC card memory mode                                                                                                                                                                        |    |    |    |       |        |                                                                                                                                        |

| A2 to A0<br>(True IDE mode)        |      |                          | Only A2 to A0 are used to select the one of eight registers in the task file, the remaining lines should be grounded.                                                                              |    |    |    |       |        |                                                                                                                                        |

| BVD1<br>(PC card memory mode)      |      |                          | The battery voltage status of the card, as no battery is required it is asserted High.                                                                                                             |    |    |    |       |        |                                                                                                                                        |

| –STSCHG<br>(PC card I/O mode)      | I/O  | 46                       | 46                                                                                                                                                                                                 | 46 | 46 | 46 | /O 46 | I/O 46 | Alerts the host to changes in the ready and write protect states. Its use is controlled by the card configuration and status register. |

| –PDIAG<br>(True IDE mode)          | ]    |                          | The Pass Diagnostic signal in the master/slave handshake protocol.                                                                                                                                 |    |    |    |       |        |                                                                                                                                        |

| BVD2<br>(PC card memory mode)      |      |                          | The battery voltage status of the card, as no battery is required it is asserted High.                                                                                                             |    |    |    |       |        |                                                                                                                                        |

| –SPKR<br>(PC card I/O mode)        | I/O  | 45                       | The Binary Audio output from the card. It is asserted High as audio functions are not supported.                                                                                                   |    |    |    |       |        |                                                                                                                                        |

| –DASP<br>(True IDE mode)           | ]    |                          | This input/output is the Disk Active/Slave Present signal in the master/slave handshake protocol.                                                                                                  |    |    |    |       |        |                                                                                                                                        |

| Signal name                      | Dir. | Pin                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D15-D00<br>(PC card memory mode) |      | Carry the data, commands and status information<br>the host and the controller. D00 is the LSB of the e<br>31,30,29,28, of the word. D08 is the LSB of the odd byte of the w |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D15-D00<br>(PC card I/O mode)    | I/O  | 27,49,48,47,<br>6,5,4,3,2,<br>23,22,21                                                                                                                                       | Same as PC card memory mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D15-D00<br>(True IDE mode)       |      |                                                                                                                                                                              | All task file operations occur in byte mode on D00 to D07 while all data transfers are 16 bits using D00 to D15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GND<br>(PC card memory mode)     |      |                                                                                                                                                                              | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GND<br>(PC card I/O mode)        |      | 1,50                                                                                                                                                                         | Same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GND<br>(True IDE mode)           |      |                                                                                                                                                                              | Same for all modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| –INPACK<br>(PC card memory mode) |      |                                                                                                                                                                              | Not used, should not be connected to the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| –INPACK<br>(PC card I/O mode)    |      |                                                                                                                                                                              | The input acknowledge is asserted when the card is selected and responding to an I/O read cycle at the current address on the bus. It is used by the host to control the enable of any input data buffers between the card and CPU.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DMARQ<br>(True IDE mode)         | 0    | 43                                                                                                                                                                           | The DMARQ input signal is used to request a DMA data<br>transfer between the host and the card. It is asserted to<br>notify that the card is ready to transfer data to or from the<br>host. For multi-word DMA transfers, the direction of data<br>transfer is controlled by -IORD and -IOWR.<br>DMARQ is used in conjunction with –DMACK to perform<br>handshaking: the card waits until –DMACK has been<br>asserted by the host to de-assert DMARQ, and re-assert it<br>again if there is still data to be transferred.<br>DMARQ is not driven when the card is not selected.<br>If the host does not support DMA mode, DMARQ should be<br>left unconnected. |

| Signal name                                                      | Dir. | Pin                                                               | Description                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------|------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| –IORD<br>(PC card memory mode)                                   |      |                                                                   | Not used.                                                                                                                                                                                                                                                                                                |

| -IORD<br>(PC card I/O mode)                                      |      | I/O read strobe generated by the host. It gates I/O date the bus. |                                                                                                                                                                                                                                                                                                          |

| –IORD<br>(True IDE mode - except<br>Ultra DMA Protocol Active)   |      |                                                                   | In True IDE mode, while Ultra DMA mode is not active, this signal has the same function as in PC Card I/O mode.                                                                                                                                                                                          |

| -HDMARDY<br>(True IDE mode - in Ultra<br>DMA Protocol DMA Read)  |      | 34                                                                | In True IDE mode when Ultra DMA mode DMA Read is active, this signal is asserted by the host to indicate that the host is read to receive Ultra DMA data-in bursts. The host may negate -HDMARDY to pause an Ultra DMA transfer.                                                                         |

| –HSTROBE<br>(True IDE mode - in Ultra<br>DMA Protocol DMA Write) |      |                                                                   | In True IDE mode when Ultra DMA mode DMA Write is<br>active, this signal is the data out strobe generated by the<br>host. Both the rising and falling edge of HSTROBE cause<br>data to be latched by the device. The host may stop<br>generating HSTROBE edges to pause an Ultra DMA data-<br>out burst. |

| –CD1, –CD2<br>(PC card memory mode)                              |      |                                                                   | These are connected to ground on the card. They are used<br>by the host to determine that the card is fully inserted into its<br>socket.                                                                                                                                                                 |

| –CD1, –CD2<br>(PC card I/O mode)                                 | 0    | 26,25                                                             | Same for all modes.                                                                                                                                                                                                                                                                                      |

| –CD1, –CD2<br>(True IDE mode)                                    |      |                                                                   | Same for all modes.                                                                                                                                                                                                                                                                                      |

| -CE1, -CE2<br>(PC card memory mode)                              |      |                                                                   | Used to select the card and to indicate whether a byte or a word operation is being performed. –CE2 accesses the odd Byte, –CE1 accesses the even byte or the odd byte depending on A0 and –CE2. A multiplexing scheme based on A0, –CE1, –CE2 allows 8-bit hosts to access all data on D0 to D7.        |

| –CE1, –CE2<br>(PC card I/O mode)                                 | 1    | 7,32                                                              | Same as PC card memory mode.                                                                                                                                                                                                                                                                             |

| –CS0, –CS1<br>(True IDE mode)                                    |      |                                                                   | -CS0 is the chip select for the task file registers, while -CS1<br>selects the alternate status register and the device control<br>register.<br>When -DMACK is asserted, -CS0 and -CS1 must be de-<br>asserted and data width is 16 bits.                                                                |

| –CSEL<br>(PC card memory mode)                                   |      |                                                                   | Not used.                                                                                                                                                                                                                                                                                                |

| -CSEL<br>(PC card I/O mode)                                      | I    | 39                                                                | Not used.                                                                                                                                                                                                                                                                                                |

| –CSEL<br>(True IDE mode)                                         |      |                                                                   | This internally pulled up signal is used to configure the card<br>as a master or slave. When grounded it is configured as a<br>master, when open it is configured as a slave.                                                                                                                            |

| Signal name                                                    | Dir. | Pin | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------------------------------------------------------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| –IOWR<br>(PC card memory mode)                                 |      |     | Not used.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| –IOWR<br>(PC card I/O mode)                                    |      |     | The I/O write strobe pulse is used to clock I/O data on the bus into the card controller registers. Clocking occurs on the rising edge.                                                                                                                                                                                                                                                                                      |  |  |

| -IOWR<br>(True IDE mode - except<br>Ultra DMA Protocol Active) | I    | 35  | In True IDE mode, while Ultra DMA mode protocol is not<br>active, this signal has the same function as in PC Card I/O<br>mode.<br>When Ultra DMA mode protocol is supported, this signal<br>must be negated before entering Ultra DMA mode protocol.                                                                                                                                                                         |  |  |

| –STOP<br>(True IDE mode - Ultra DMA<br>Protocol Active)        |      |     | In True IDE mode, while Ultra DMA mode protocol is active,<br>the assertion of this signal causes the termination of the<br>Ultra DMA burst.                                                                                                                                                                                                                                                                                 |  |  |

| –OE<br>(PC card memory mode)                                   |      |     | This is an Output Enable strobe generated by the host interface. It reads data and the CIS and configuration registers.                                                                                                                                                                                                                                                                                                      |  |  |

| –OE<br>(PC card I/O mode)                                      | I    | 9   | Reads the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| –ATASEL<br>(True IDE mode)                                     |      |     | This input signal must be driven Low to enable true IDE mode.                                                                                                                                                                                                                                                                                                                                                                |  |  |

| READY<br>(PC card memory mode)                                 | 0    | 37  | Indicates whether the card is busy (Low), or ready to accept<br>a new data transfer operation (High). The host socket must<br>provide a pull-up resistor. At power-up and reset, the Ready<br>signal is held Low until the commands are completed. No<br>access should be made during this time. The Ready signal<br>is held High whenever the card has been powered up with<br>Reset continuously disconnected or asserted. |  |  |

| –IREQ<br>(PC card I/O mode)                                    |      |     | Interrupt request. It is strobed Low to generate a pulse mode interrupt or held Low for a level mode interrupt.                                                                                                                                                                                                                                                                                                              |  |  |

| INTRQ<br>(True IDE mode)                                       |      |     | Active High interrupt request to the host.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| -REG<br>(PC card memory mode)                                  |      |     | Used to distinguish between common memory and register (attribute) memory accesses. High for common memory, Low for attribute memory.                                                                                                                                                                                                                                                                                        |  |  |

| –REG<br>(PC card I/O mode)                                     |      |     | Must be Low during I/O cycles when the I/O address is on the bus.                                                                                                                                                                                                                                                                                                                                                            |  |  |

|                                                                | I    | 44  | The –DMACK input signal is used to acknowledge DMA transfers. It is asserted by the host in response to DMARQ to initiate the transfer.                                                                                                                                                                                                                                                                                      |  |  |

| –DMACK<br>(True IDE mode)                                      |      |     | When DMA mode is disabled, the card should ignore the -DMACK signal.<br>If the host does not support DMA mode, but only True IDE                                                                                                                                                                                                                                                                                             |  |  |

|                                                                |      |     | mode, this signal should be driven High or tied to V <sub>CC</sub> by the host.                                                                                                                                                                                                                                                                                                                                              |  |  |

| Signal name                                           | Dir. | Pin   | Description                                                                                                                                                                                                                                                                                                 |  |

|-------------------------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RESET<br>(PC card memory mode)                        |      |       | Resets the card (active High). The card is reset at power-up only if this pin is left High or unconnected.                                                                                                                                                                                                  |  |

| RESET<br>(PC card I/O mode)                           | I    | 41    | Same as PC card memory mode.                                                                                                                                                                                                                                                                                |  |

| -RESET<br>(True IDE mode)                             |      |       | Hardware reset from the host (active Low).                                                                                                                                                                                                                                                                  |  |

| V <sub>CC</sub><br>(PC card memory mode)              |      |       | +5 V, +3.3 V power.                                                                                                                                                                                                                                                                                         |  |

| V <sub>CC</sub><br>(PC card I/O mode)                 |      | 13,38 | Same for all modes.                                                                                                                                                                                                                                                                                         |  |

| V <sub>CC</sub><br>(True IDE mode)                    |      |       | Same for all modes.                                                                                                                                                                                                                                                                                         |  |

| –VS1, –VS2<br>(PC card memory mode)                   |      |       | Voltage sense signals.–VS1 is grounded so that the CIS can be read at 3.3 volts and –VS2 is reserved by PCMCIA for a secondary voltage.                                                                                                                                                                     |  |

| –VS1, –VS2<br>(PC card I/O mode)                      | 0    | 33,40 | Same for all modes.                                                                                                                                                                                                                                                                                         |  |

| –VS1, –VS2<br>(True IDE mode)                         |      |       | Same for all modes.                                                                                                                                                                                                                                                                                         |  |

| -WAIT<br>(PC card memory mode)                        |      |       | Numonyx CF does not assert the WAIT (IORDY) signal                                                                                                                                                                                                                                                          |  |

| -WAIT<br>(PC card I/O mode)                           |      |       | Numbryx CF does not assert the WAT (ICFDT) signal                                                                                                                                                                                                                                                           |  |

| IORDY<br>(True IDE mode - except<br>Ultra DMA mode)   |      |       | In True IDE mode, except in Ultra DMA mode, this output signal may be used as IORDY.                                                                                                                                                                                                                        |  |

| -DDMARDY<br>(True IDE mode – Ultra<br>DMA Write mode) | 0    | 42    | In True IDE mode, when Ultra DMA mode DMA Write is<br>active, this signal is asserted by the host to indicate that the<br>device is read to receive Ultra DMA data-in bursts.<br>The device may negate -DDMARDY to pause an Ultra DMA<br>transfer.                                                          |  |

| DSTROBE<br>(True IDE mode – Ultra<br>DMA Read mode)   |      |       | In True IDE mode, when Ultra DMA mode DMA Write is<br>active, this signal is the data out strobe generated by the<br>device. Both the rising and falling edge of DSTROBE cause<br>data to be latched by the host. The device may stop<br>generating DSTROBE edges to pause an Ultra DMA data-<br>out burst. |  |

Table 8.

Signals description (continued)

| Signal name                   | Dir. | Pin                                                   | Description                                                                                                                                 |  |  |  |

|-------------------------------|------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -WE<br>(PC card memory mode)  |      |                                                       | Driven by the host to strobe memory write data to the registers.                                                                            |  |  |  |

| -WE<br>(PC card I/O mode)     | I    | I 36 Used for writing to the configuration registers. |                                                                                                                                             |  |  |  |

| –WE<br>(True IDE mode)        |      |                                                       | Not used, should be connected to $V_{CC}$ by the host.                                                                                      |  |  |  |

| WP<br>(PC card memory mode)   |      |                                                       | No write protect switch available. It is held Low after the completion of the reset initialization sequence.                                |  |  |  |

| –IOIS16<br>(PC card I/O mode) | о    | 24                                                    | Used for the 16-bit port (–IOIS16) function. Low indicates that a 16-bit or odd byte only operation can be performed at the addressed port. |  |  |  |

| –IOCS16<br>(True IDE mode)    |      |                                                       | Asserted Low when the card is expecting a word data transfer cycle.                                                                         |  |  |  |

### 4.2 Electrical specification

*Table 9* defines the DC characteristics for the CompactFlash memory card. Unless otherwise stated, conditions are:

- $V_{CC} = 5 V \pm 10\%$

- $V_{CC} = 3.3 \text{ V} \pm 10\%$

- -40 °C to 85 °C.

*Table 10* shows that the card operates correctly in both the voltage ranges and that the current requirements must not exceed the maximum limit shown.

#### Table 9. Absolute maximum conditions

| Parameter                                              | Symbol          | Conditions                  |

|--------------------------------------------------------|-----------------|-----------------------------|

| Input power                                            | V <sub>CC</sub> | - 0.3 V to 6.5 V            |

| Voltage on any pin except $V_{CC}$ with respect to GND | V               | $-$ 0.5 V to V_{CC} + 0.5 V |

#### Table 10. Input power

| Voltage        | Maximum average RMS current | Measurement conditions |

|----------------|-----------------------------|------------------------|

| $3.3~V\pm10\%$ | 75                          | – 40 + 85 °C           |

| $5~V\pm10\%$   | 100                         | − 40 + 85 °C           |

### 4.3 Current measurement

The current is measured by connecting an amp meter in series with the  $V_{CC}$  supply. The meter should be set to the 2A scale range, and have a fast current probe with an RC filter with a time constant of 0.1 ms. Current measurements are taken while looping on a data transfer command with a sector count of 128. Current consumption values for both read and write commands are not to exceed the maximum average RMS current specified in *Table 10. Table 11* shows the input leakage current, *Table 12* the input characteristics, *Table 13* the output drive type and *Table 14* the output drive characteristics.

| Туре | Parameter             | Symbol | Conditions                                                 | Min | Тур | Max | Units |

|------|-----------------------|--------|------------------------------------------------------------|-----|-----|-----|-------|

| lxZ  | Input leakage current | IL     | V <sub>IH</sub> = V <sub>CC</sub><br>V <sub>IL</sub> = GND | - 2 |     | 2   | μΑ    |

| IxU  | Pull up resistor      | RPU1   | $V_{CC} = 5.0 V$                                           | 50  |     | 500 | kΩ    |

| IxD  | Pull down resistor    | RPD1   | $V_{CC} = 5.0 V$                                           | 50  |     | 500 | kΩ    |

Table 11.

Input leakage current<sup>(1)</sup>

1. x refers to the characteristics described in *Table 12*. For example, I1U indicates a pull up resistor with a type 1 input characteristic.

| Type Parameter | Symbol                  | Min             | Тур | Max                     | Min | Тур | Max   | Units |   |

|----------------|-------------------------|-----------------|-----|-------------------------|-----|-----|-------|-------|---|

| Туре           | Farameter               | Symbol          | v   | V <sub>CC</sub> = 3.3 V |     | v   | Units |       |   |

| 4              | Input voltage           | V <sub>IH</sub> | 2.4 |                         |     | 3.3 |       |       | v |

| 1              | CMOS                    | V <sub>IL</sub> |     |                         | 0.6 |     |       | 0.8   | v |

| 2              | Input voltage           | V <sub>IH</sub> | 1.5 |                         |     | 2.0 |       |       | v |

| 2              | CMOS                    | V <sub>IL</sub> |     |                         | 0.6 |     |       | 0.8   | v |

|                | Input voltage           | V <sub>TH</sub> |     | 1.8                     |     |     | 2.8   |       |   |

| 3              | CMOS<br>Schmitt Trigger | V <sub>TL</sub> |     | 1.0                     |     |     | 2.0   |       | V |

Table 12.Input characteristics

Table 13.Output drive type<sup>(1)</sup>

| Туре | Output type           | Valid conditions                  |

|------|-----------------------|-----------------------------------|

| OTx  | Totempole             | I <sub>OH</sub> & I <sub>OL</sub> |

| OZx  | Tri-state N-P channel | I <sub>OH</sub> & I <sub>OL</sub> |

| OPx  | P-channel only        | l <sub>OH</sub> only              |

| ONx  | N-channel only        | l <sub>OL</sub> only              |

1. x refers to the characteristics described in *Table 14*. For example, OT3 refers to totem pole output with a type 3 output drive characteristic.

|--|

| Туре | Parameter                    | Symbol          | Conditions              | Min              | Тур | Max         | Units |

|------|------------------------------|-----------------|-------------------------|------------------|-----|-------------|-------|

| 1    | Output voltage               | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA | $V_{CC} - 0.8 V$ |     |             | v     |

|      |                              | V <sub>OL</sub> | I <sub>OL</sub> = 4 mA  |                  |     | Gnd + 0.4 V | v     |

| 2    | Output voltage               | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA | $V_{CC} - 0.8 V$ |     |             | V     |

|      |                              | V <sub>OL</sub> | I <sub>OL</sub> = 4 mA  |                  |     | Gnd + 0.4 V |       |

| 3    | Output voltage               | V <sub>OH</sub> | I <sub>OH</sub> = -4 mA | $V_{CC} - 0.8 V$ |     |             | V     |

|      |                              | V <sub>OL</sub> | I <sub>OL</sub> = 4 mA  |                  |     | Gnd + 0.4 V |       |

| х    | Tri-state<br>leakage current | I <sub>OZ</sub> | $V_{OL} = Gnd$          | -10              |     | 10          |       |

|      |                              |                 | $V_{OH} = V_{CC}$       |                  |     | 10          | μA    |

# 4.4 Additional requirements for CompactFlash advanced timing mode

When operating in a CompactFlash advanced timing mode, the following conditions must be respected:

- Only one CompactFlash card must be connected to the CompactFlash bus

- The load capacitance (cable included) for all signals must be lower than 40 pF

- The cable length must be lower than 0.15 m (6 inches). The cable length is measured from the card connector to the host controller. 0.46 m (18 inches) cables are not supported.

## 5 Command interface

There are two types of bus cycles and timing sequences that occur in the PCMCIA type interface, direct mapped I/O transfer and memory access. Three types of bus cycles are also available in true IDE interface type: PIO transfer, multi-word DMA transfer and Ultra DMA transfer.

Refer to CF specification 3.0 for details about read and write timing parameters and relative timing diagrams.

In order to set the card mode, the -OE (-ATASEL) signal must be set and kept stable before applying V<sub>CC</sub> until the reset phase is completed. To place the card in memory mode or I/O mode, -OE(-ATASEL) must be driven High, while it must be driven Low to place the card in true IDE mode.

## 6 Card configuration

Refer to paragraph 4.4 of CF specification 3.0.

## 7 Host configuration requirements

The CompactFlash advanced timing modes include PCMCIA-style I/O modes that are faster than the original 250 ns cycle time (see *Section 1: Description*).

Before configuring the card interface for the I/O mode, the host must ensure that all the cards connected to a given electrical interface support I/O transfers faster than 250 ns.

These modes must be used in the conditions described in *Section 4.4: Additional requirements for CompactFlash advanced timing mode*. In particular, the host can be connected to one card only. Consequently, the host must not configure a card to operate in an CompactFlash advanced timing mode if two cards are sharing the same I/O lines in master/slave operation, or if it is connected to the card through a cable which length exceeds 0.15 m.

The load presented to the host by cards supporting Ultra DMA is more controlled than that presented by other CompactFlash cards. Therefore, the use of a card that does not support Ultra DMA in a master/slave arrangement with a Ultra DMA card can affect the critical timing of the Ultra DMA transfers. The host shall not configure a card into Ultra DMA mode when a card not supporting Ultra DMA is also present on the same interface.

When the use of two cards on an interface is otherwise permitted, the host may use any mode that is supported by both cards, but to achieve maximum performance it should use its highest performance mode that is also supported by both cards.

## 8 Software interface

Refer to section 6.1 of CF specification version 3.0.

## 9 CF-ATA registers

Refer to section 6.1.5 of CF specification version 3.0.

## 10 CF-ATA command description

Refer to section 6.2 of CF specification version 3.0.

-----

## 11 CIS information (typical)

```

0000: Code 01, link 04

DF 79 01 FF

-----

Tuple CISTPL_DEVICE (01), length 4 (04)

_

Device type is FUNCSPEC

_

Extended speed byte used

Device speed is 80ns

_

Write protect switch is not in control

_

Device size is 2K bytes

_

_____

000C: Code 1C, link 05

02 DF 79 01 FF

_____

Tuple CISTPL_DEVICE_OC (1C), length 5 (05)

_

Device conditions: V_{CC} = 3.3V

_

Device type is FUNCSPEC

_

Extended speed byte used

_

Device speed is 80ns

_

Write protect switch is not in control

_

Device size is 2K bytes

_

_____

001A: Code 18, link 02

DF 01

-----

Tuple CISTPL_JEDEC_C (18), length 2 (02)

_

Device 0 JEDEC id: Manufacturer DF, ID 01

_

_____

0022: Code 20, link 04

0A 00 00 00

-----

Tuple CISTPL_MANFID (20), length 4 (04)

_

Manufacturer # 0x000A hardware rev 0.00

_

_____

002E: Code 15, link 12

04 01 53 54 4D 00 53 54 4D 2D x x x x 42 00

00 FF

```

Tuple CISTPL\_VERS\_1 (15), length 18 (12) \_ Major version 4, minor version 1 \_ Product Information: Manufacturer: 'Numonyx', Product name: 'Numonyx-xxxxB' \_\_\_\_\_ 0056: Code 21, link 02 04 01 -----Tuple CISTPL FUNCID (21), length 2 (02) \_ Function code 04 (Fixed Disk), system init 01 \_ 005E: Code 22, link 02 01 01 -----Tuple CISTPL FUNCE (22), length 2 (02) \_ This is a PC Card ATA Disk \_ 0066: Code 22, link 03 02 OC OF -----\_ Tuple CISTPL FUNCE (22), length 3 (03) V<sub>PP</sub> is not required This is a silicon device \_ Identify Drive Model/Serial Number is guaranteed unique \_ Low-Power Modes supported: Sleep Standby Idle Drive automatically minimizes power \_ All modes include 3F7 or 377 \_ Index bit is not supported \_ -IOIS16 is unspecified in Twin configurations \_ -----0070: Code 1A, link 05 01 03 00 02 OF \_\_\_\_\_ Tuple CISTPL\_CONFIG (1A), length 5 (05) \_ Last valid configuration index is 3 \_ Configuration Register Base Address is 200 \_ - Configuration Registers Present: Configuration Option Register at 200 Card Configuration and Status Register at 202 - Pin Replacement Register at 204 - Socket and Copy Register at 206

```

-----

007E: Code 1B, link 08

C0 C0 A1 01 55 08 00 20

-----

Tuple CISTPL_CFTABLE_ENTRY (1B), length 8 (08)

_

Configuration Table Index is 00 (default)

_

Interface type is Memory

BVDs not active, WP not active, RdyBsy active

_

Wait signal support required

V_{CC} Power Description: Nom V = 5.0 V

map 2048 bytes of memory to Card address 0

_

Miscellaneous Features: Max Twins 0, -Audio, -ReadOnly, +PowerDown

_

-----

0092: Code 1B, link 06

00 01 21 B5 1E 4D

_____

Tuple CISTPL CFTABLE ENTRY (1B), length 6 (06)

_

Configuration Table Index is 00

_

V<sub>CC</sub> Power Description: Nom V = 3.30 V, Peak I = 45.0 mA

_

00A2: Code 1B, link 0A

C1 41 99 01 55 64 F0 FF FF 20

-----

Tuple CISTPL CFTABLE ENTRY (1B), length 10 (0A)

_

Configuration Table Index is 01 (default)

Interface type is I/O

_

BVDs not active, WP not active, RdyBsy active

_

Wait signal support not required

V_{CC} Power Description: Nom V = 5.0 V

_

Decode 4 I/O lines, bus size 8 or 16

_

IRQ may be shared, pulse and level mode interrupts are supported

Interrupts in mask FFFF are supported

_

Miscellaneous Features: Max Twins 0, -Audio, -ReadOnly, +PowerDown

_

-----

00BA: Code 1B, link 06

01 01 21 B5 1E 4D

_____

Tuple CISTPL CFTABLE ENTRY (1B), length 6 (06)

Configuration Table Index is 01

V_{CC} Power Description: Nom V = 3.30 V,

```

Peak I = 45.0 mA

```

_____

00CA: Code 1B, link 0F

C2 41 99 01 55 EA 61 F0 01 07 F6 03 01 EE 20

-----

Tuple CISTPL CFTABLE ENTRY (1B), length 15 (0F)

_

Configuration Table Index is 02 (default)

_

Interface type is I/O

BVDs not active, WP not active, RdyBsy active

_

Wait signal support not required

_

V<sub>CC</sub> Power Description:

Nom V = 5.0 V

Decode 10 I/O lines, bus size 8 or 16

I/O block at 01F0, length 8

I/O block at 03F6, length 2

IRQ may be shared, pulse and level mode interrupts are supported

_

Only IRQ14 is supported

Miscellaneous Features: Max Twins 0, -Audio, -ReadOnly, +PowerDown

_

-----

00EC: Code 1B, link 06

02 01 21 B5 1E 4D

-----

Tuple CISTPL CFTABLE ENTRY (1B), length 6 (06)

_

Configuration Table Index is 02

_

V_{CC} Power Description: Nom V = 3.30 V, Peak I = 45.0 mA

_

_____

00FC: Code 1B, link 0F

C3 41 99 01 55 EA 61 70 01 07 76 03 01 EE 20

-----

Tuple CISTPL CFTABLE ENTRY (1B), length 15 (0F)

_

Configuration Table Index is 03 (default)

_

Interface type is I/O

BVDs not active, WP not active, RdyBsy active

_

Wait signal support not required

_

V_{CC} Power Description: Nom V = 5.0 V

Decode 10 I/O lines, bus size 8 or 16

I/O block at 0170, length 8

_

I/O block at 0376, length 2

_

IRQ may be shared, pulse and level mode interrupts are supported

_

_

Only IRQ14 is supported

```

- Miscellaneous Features: Max Twins 0, -Audio, -ReadOnly, +PowerDown

```

-----

011E: Code 1B, link 06

03 01 21 B5 1E 4D

-----

Tuple CISTPL_CFTABLE_ENTRY (1B), length 6 (06)

_

Configuration Table Index is 03

_

- V<sub>CC</sub> Power Description: Nom V = 3.30 V, Peak I = 45.0 mA

_____

012E: Code 14, link 00

-----

Tuple CISTPL_NO_LINK (14), length 0 (00)

—

-----

0134: Code FF

-----

Tuple CISTPL_END (FF)

_

```