Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

September 2010 Rev. 2.0.0

### **GENERAL DESCRIPTION**

The SP2996B voltage regulator is designed to convert voltage supplies ranging from 1.6V to 6V into a desired output voltage which is adjusted by an external resistor divider.

The regulator is capable of sourcing or sinking up to 2A of Continuous current while regulating an output voltage to within 20mV. The SP2996B provides an excellent voltage source for active termination schemes of high speed transmission lines such as those seen in high speed memory buses and distributed backplane designs when used in conjunction with series termination resistors. The voltage output of the regulator can be used as a termination voltage for DDR SDRAM, and it meets the JEDEC SSTL-2 and SSTL-3 specifications. Current limits in both sourcing and sinking mode, plus on-chip thermal shutdown make the circuit tolerant of output fault conditions.

### **APPLICATIONS**

- DDR Memory Termination

- Active Bus Termination

- Supply Splitter

### **FEATURES**

- Capable of Sourcing and sinking 2A Continuous Current

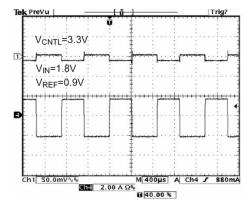

- Supports both DDR1 (1.25 $V_{TT}$ ) and DDR2 (0.9 $V_{TT}$ ) Requirements

- Low Output Voltage Offset, ± 20mV

- Thermal and Current Limit Protection

- Integrated Power MOSFETs

- Generates Termination for SSTL-2

- High Accuracy Output at Full Load

- Adjustable V<sub>OUT</sub> by External Resistors

- Minimal External Components

- Available in 8-Pin NSOIC Package

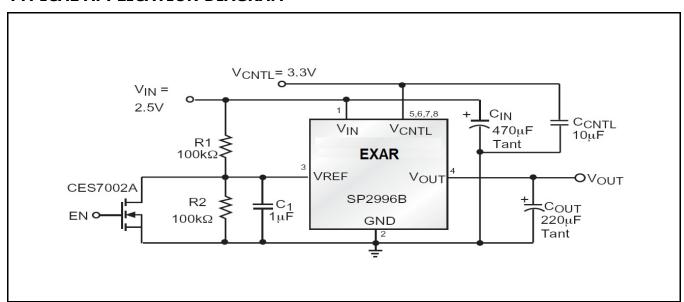

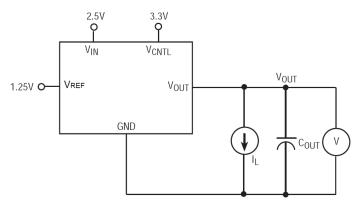

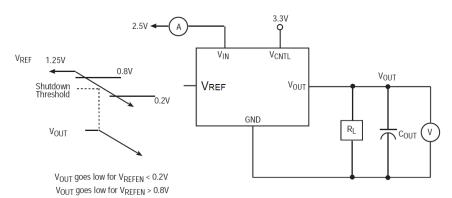

### TYPICAL APPLICATION DIAGRAM

Fig. 1: SP2996B Application Diagram

### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Supply Voltage             | 0.3V to 7.0V   |

|----------------------------|----------------|

| Junction Temperature Range | 40°C to +125°C |

| Storage Temperature        | 65°C to 150°C  |

### **OPERATING RATINGS**

| Operating Temperature Range      | 40°C to +85°C |

|----------------------------------|---------------|

| Thermal Resistance $\theta_{JA}$ | 160°C/W       |

| Thermal Resistance $\theta_{JC}$ | 40°C/W        |

### **ELECTRICAL SPECIFICATIONS**

Specifications with standard type are for an Operating Ambient Temperature of  $T_A = 25^{\circ}\text{C}$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_A = 25^{\circ}\text{C}$ , and are provided for reference purposes only. Unless otherwise indicated,  $V_{IN} = 2.5\text{V}$ ,  $V_{CNTL} = 3.3\text{V}$ ,  $V_{REF} = 0.5\text{xV}_{IN}$ ,  $C_{OUT} = 10\mu\text{F}$  (ceramic),  $T_A = 25^{\circ}\text{C}$ .

| Parameter                                                  | Min. | Тур.      | Max. | Units | Conditions                                                                                     |

|------------------------------------------------------------|------|-----------|------|-------|------------------------------------------------------------------------------------------------|

| Input Voltage Range (DDR 1/2) $V_{\text{IN}}$              | 1.6  | 2.5/1.8   |      | V     | (note 4) Keep V <sub>CNTL</sub> ≥V <sub>IN</sub> on operation power on and power off sequences |

| Input Voltage Range (DDR 1/2)<br>V <sub>CNTL</sub>         | 3.0  | 3.3       | 3.6  | V     | (note 4)<br>I <sub>OUT</sub> = 0mA                                                             |

| Output Voltage V <sub>OUT</sub>                            |      | $V_{REF}$ |      | V     | $I_{OUT} = 0mA$                                                                                |

| Output Offset Voltage Vos                                  | -20  |           | +20  | mV    | No load                                                                                        |

| Load Regulation (DDR 1/2) AV                               |      | 10        | 25   | mV    | $I_{OUT} = 0.1 \text{mA to } +2 \text{A}$                                                      |

| Load Regulation (DDR 1/2) $\Delta V_{LOR}$                 |      | 10        | 25   | mV    | $I_{OUT} = 0.1$ mA to -2A                                                                      |

| Quiescent Current I <sub>Q</sub>                           |      | 8         | 30   | μΑ    | $V_{REF} < 0.2V$ , $V_{OUT} = OFF$                                                             |

| Operating Current of $V_{\text{CNTL}}$ , $I_{\text{CNTL}}$ |      | 3         | 10   | mA    | No load                                                                                        |

| Bias Current of V <sub>REF</sub>                           |      |           | 1    | μA    | $V_{REF} = 1.25V$                                                                              |

| Current Limit I <sub>IL</sub>                              | 2.2  | 3         | 4.5  | Α     | (note 3)                                                                                       |

| Thermal Protection                                         |      |           |      |       |                                                                                                |

| Thermal Shutdown Temperature $T_{\text{SD}}$               | 125  | 150       |      | °C    | (note 4) $3.3V \le V_{CNTL} \le 5V$ , guaranteed by design                                     |

| Thermal Shutdown Hysteresis                                |      | 30        |      | °C    | Guaranteed by design                                                                           |

| Shutdown Specifications                                    |      |           |      |       |                                                                                                |

| Shutdown Threshold VTRIGGER                                | 0.8  |           |      | V     | Output ON $V_{REF} = 0V \rightarrow 1.25V$                                                     |

| SHULUOWH HITESHOID VTRIGGER                                |      |           | 0.2  |       | Output OFF $V_{REF} = 1.25V \rightarrow 0V$                                                    |

Note 1:  $V_{OS}$  offset is the voltage measurement defined as  $V_{OUT}$  subtracted from  $V_{REF}$ .

Note 2: Load regulation is measured at constant junction temperature, using pulse testing with a low ON time.

Note 3: Current limit is measured by pulsing a short time.

Note 4: In order to safely operate your system,  $V_{CNTL}$  must be  $> V_{IN}$ .

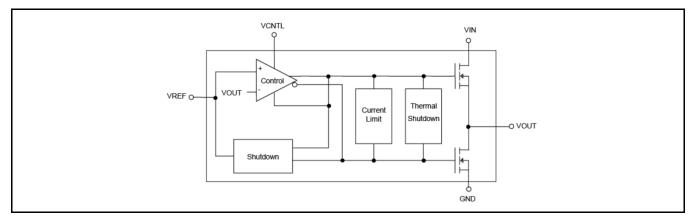

### **BLOCK DIAGRAM**

Fig. 2: SP2996B Block Diagram

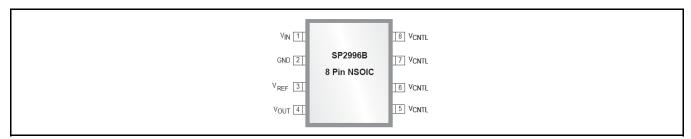

### **PIN ASSIGNMENT**

Fig. 3: SP2996B Pin Assignment

### **PIN DESCRIPTION**

| Name             | Pin Number | Description                                                                                                     |  |  |  |

|------------------|------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| $V_{IN}$         | 1          | Power Input Voltage                                                                                             |  |  |  |

| GND              | 2          | Ground Signal                                                                                                   |  |  |  |

| $V_{REF}$        | 3          | Reference Input Voltage. This input can also be used as an enable signal. Refer to typical application circuit. |  |  |  |

| V <sub>OUT</sub> | 4          | Output Voltage                                                                                                  |  |  |  |

| $V_{CNTL}$       | 5          |                                                                                                                 |  |  |  |

| $V_{CNTL}$       | 6          | Voltage for the driver circuit and all analog blocks                                                            |  |  |  |

| $V_{CNTL}$       | 7          | Voltage for the driver circuit and all analog blocks                                                            |  |  |  |

| $V_{CNTL}$       | 8          |                                                                                                                 |  |  |  |

### **ORDERING INFORMATION**

| Part Number    | Temperature<br>Range        | Marking                | Package | Packing<br>Quantity | Note 1    | Note 2 |

|----------------|-----------------------------|------------------------|---------|---------------------|-----------|--------|

| SP2996BEN-L    | -40°C≤T <sub>A</sub> ≤+85°C | SP2996BE<br>YYWWL<br>X | SOIC-8  | Bulk                | Lead Free |        |

| SP2996BEN-L/TR | -40°C≤T <sub>A</sub> ≤+85°C | SP2996BE<br>YYWWL<br>X | SOIC-8  | 2.5K/Tape & Reel    | Lead Free |        |

<sup>&</sup>quot;YY" = Year - "WW" = Work Week - "L" = Lead Free Indicator - "X" = Lot Number; when applicable.

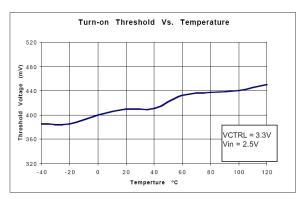

### TYPICAL PERFORMANCE CHARACTERISTICS

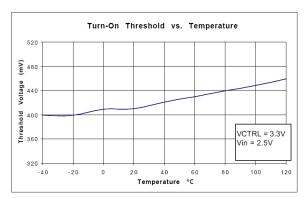

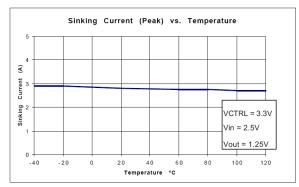

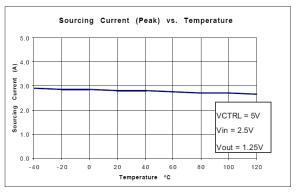

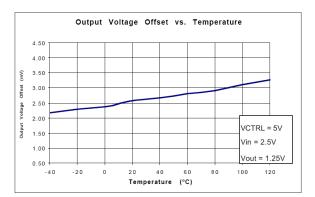

All data taken at  $V_{IN}$  = 2.5V,  $V_{CNTL}$  = 3.3V,  $V_{REF}$  = 0.5x $V_{IN}$ ,  $C_{OUT}$  = 10 $\mu F$  (ceramic),  $T_A$ = 25°C, unless otherwise specified -Schematic and BOM from Application Information section of this datasheet.

Fig. 4: Turn-on Threshold vs Temperature

2 Amp DDR Bus Termination Regulator

Fig. 5: Turn-on Threshold vs Temperature

Fig. 6: Sinking Current (Peak) vs Temperature

Fig. 7: Sourcing Current (Peak) vs Temperature

Fig. 8: Output Offset Voltage vs Temperature

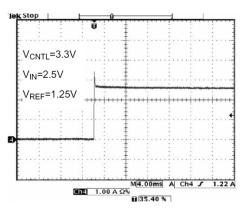

Fig. 9: Output Short Circuit (Sinking)

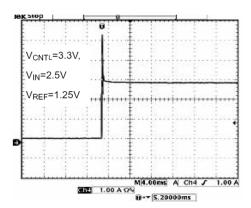

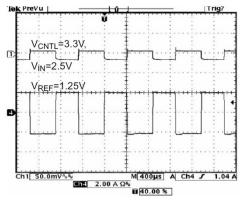

Fig. 11: Transient Response @ 1.25V<sub>™</sub>/2A

Fig. 10: Output Short Circuit (Sourcing)

Fig. 12: Transient Response @  $1.25V_{TT}/2A$

### **APPLICATION INFORMATION**

### **INTERNAL PARASITIC DIODE**

Avoid forward-biasing the internal parasitic diode,  $V_{\text{OUT}}$  to  $V_{\text{CNTL}}$ , and  $V_{\text{OUT}}$  to  $V_{\text{IN}}$ . Positive voltage should not be applied to the output if  $V_{\text{IN}}$  and  $V_{\text{CNTL}}$  are not present.

# CONSIDERATIONS FOR DESIGNING, RESISTANCE OF VOLTAGE DIVIDER

When the reference voltage is programmed below 0.2V the pulldown capability of the internal NMOS transistor is limited. It is recommened to place a filter capacitor from  $V_{\text{REF}}$  to ground in order to reduce sensitivity to

noise and improve power up characteristics (soft start).

### **LAYOUT CONSIDERATIONS**

The SP2996B is offered in the NSOIC-8 package, resulting in attention needing to be paid to dissipating heat effectively when it operates in high current. In order to prevent maximum junction temperature from being exceeded, suitable copper area is necessary. The large copper area at VCNTL pins is available, and by taking advantage of this, much heat dissipation is attained. Use vias to direct heat into the bottom layer as the layout examples show below. All capacitors should be placed as close as possible to relative pins.

### **TEST CIRCUITS**

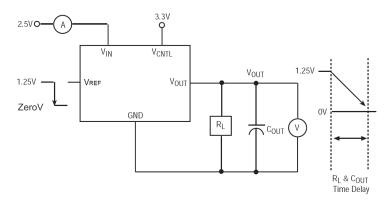

### **Testing Output Voltage Tolerance ∆VLOAD**

### Testing Current in Shutdown Mode I<sub>SHDN</sub>

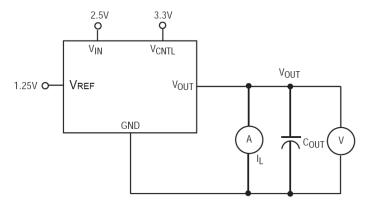

# Testing Current Limit for High Side $I_{\text{LIMIT}}$

# Testing Current Limit for Low Side $I_{\text{Limit}}$

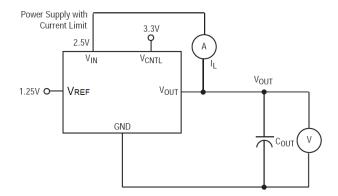

# Testing $V_{\text{REF}}$ Pin Shutdown Threshold $V_{\text{TRIGGER}}$

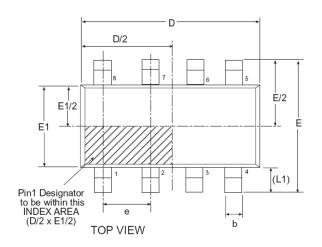

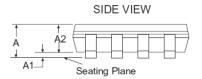

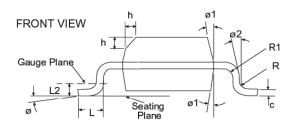

## **PACKAGE SPECIFICATION**

## **8-PIN NSOIC**

| 8 Pin NSOIC JEDEC MS                            |      |                                |      | S-012                                                           | Variation      | AA    |

|-------------------------------------------------|------|--------------------------------|------|-----------------------------------------------------------------|----------------|-------|

| SYMBOL                                          |      | sions in Milli<br>rolling Dime |      | Dimensions in Inches<br>Conversion Factor:<br>1 Inch = 25.40 mm |                |       |

|                                                 | MIN  | NOM                            | MAX  | MIN                                                             | NOM            | MAX   |

| Α                                               | 1.35 | -                              | 1.75 | 0.053                                                           | -              | 0.069 |

| A1                                              | 0.10 | -                              | 0.25 | 0.004                                                           | -              | 0.010 |

| A2                                              | 1.25 | ı                              | 1.65 | 0.049                                                           | ı              | 0.065 |

| b                                               | 0.31 | 1                              | 0.51 | 0.012                                                           | -              | 0.020 |

| С                                               | 0.17 | -                              | 0.25 | 0.007                                                           | -              | 0.010 |

| E                                               |      | 6.00 BSC                       |      | 0.236 BSC                                                       |                |       |

| E1                                              |      | 3.90 BSC                       |      | 0.154 BSC                                                       |                |       |

| е                                               |      | 1.27 BSC                       |      | 0.050 BSC                                                       |                |       |

| h                                               | 0.25 |                                | 0.50 | 0.010                                                           | -              | 0.020 |

| L                                               | 0.40 | -                              | 1.27 | 0.016                                                           | -              | 0.050 |

| L1                                              |      | 1.04 REF                       |      | 0.041 REF                                                       |                |       |

| L2                                              |      | 0.25 BSC                       |      | 0.010 BSC                                                       |                |       |

| R                                               | 0.07 | -                              | -    | 0.003                                                           | -              | -     |

| R1                                              | 0.07 | -                              | -    | 0.003                                                           | -              | -     |

| ø                                               | 00   | -                              | 80   | 00                                                              | -              | 80    |

| ø1                                              | 50   | -                              | 15°  | 50                                                              | -              | 15°   |

| ø2                                              | 00   | -                              | -    | 00                                                              | -              | -     |

| D                                               |      | 4.90 BSC                       |      | 0.193 BSC                                                       |                |       |

| SIPEX Pkg Signoff Date/Rev: JL Aug16-05 / Rev A |      |                                |      | J                                                               | L Aug16-05 / F | Rev A |

### **REVISION HISTORY**

| Revision | Date | Description                                                                                              |

|----------|------|----------------------------------------------------------------------------------------------------------|

| 2.0.0    |      | Reformat of data sheet Corrected $V_{\text{CTRL}}$ vs $V_{\text{CNTL}}$ and $V_{\text{REF}}$ annotations |

|          |      |                                                                                                          |

|          |      |                                                                                                          |

|          |      |                                                                                                          |

|          |      |                                                                                                          |

### FOR FURTHER ASSISTANCE

Email: customersupport@exar.com

Exar Technical Documentation: http://www.exar.com/TechDoc/default.aspx?

### **EXAR CORPORATION**

### **HEADQUARTERS AND SALES OFFICES**

48720 Kato Road

Fremont, CA 94538 - USA

Tel.: +1 (510) 668-7000

Fax: +1 (510) 668-7030

www.exar.com

### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.