# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Quad RS-485/RS-422 Line Receivers

- RS-485 or RS-422 Applications

- Quad Differential Line Receivers

- Tri-state Output Control

- 120ns Typical Receiver Propagation Delays

- –7V to +12V Common Mode Input Range

- 1mA Supply Current

- Single +5V Supply Operation

- Pin Compatible with SN75173, SN75175, LTC488 and LTC489

#### **DESCRIPTION...**

#### Now available in Lead Free

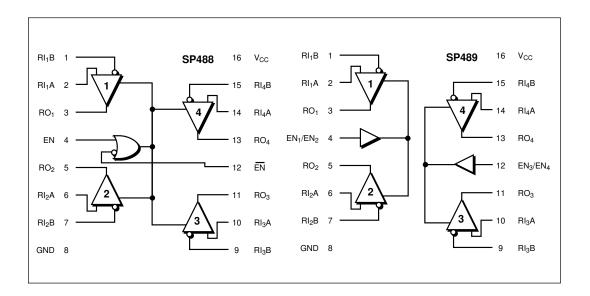

The **SP488** and **SP489** are low–power quad differential line receivers meeting RS-485 and RS-422 standards. The **SP488** features a common receiver enable control; the **SP489** provides independent receiver enable controls for each pair of receivers. Both feature tri–state outputs and wide common–mode input range. The receivers have a fail–safe feature which forces a logic "1" output when receiver inputs are left floating. Both are available in 16–pin plastic DIP and SOIC packages.

#### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| V <sub>cc</sub>                      | +7V                              |

|--------------------------------------|----------------------------------|

| Input Voltages                       |                                  |

| Logic                                | –0.5V to (V <sub>cc</sub> +0.5V) |

| Receiver                             | ±14V                             |

| Receiver Output Voltage              | 0.5V to (V <sub>cc</sub> +0.5V)  |

| Input Currents                       |                                  |

| Logic                                | ±25mA                            |

| Storage Temperature                  | 65°C to +150°C                   |

| Power Dissipation                    |                                  |

| Plastic DIP                          | 375mW                            |

| (derate 7mW/°C above +70°C)          |                                  |

| Small Outline                        | 375mW                            |

| (derate 7mW/°C above +70°C)          |                                  |

| Lead Temperature (soldering, 10 sec) |                                  |

#### SPECIFICATIONS

$V_{_{CC}}$  = 5V±5%; typicals at 25°C;  $T_{_{MIN}} \leq T_{_A} \leq T_{_{MAX}}$  unless otherwise noted.

| PARAMETER                                                                                               | MIN.                           | TYP.                                 | MAX.                 | UNIT                      | CONDITIONS                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|----------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC CHARACTERISTICS<br>Digital Inputs<br>Voltage                                                         |                                |                                      |                      |                           | $EN, \overline{EN}, EN_1/EN_2, EN_3/EN_4$                                                                                                                                                |

| VL<br>VIL<br>Input Current                                                                              | 2.0                            |                                      | 0.8<br>±2            | Volts<br>Volts<br>μΑ      | $0V \le V_{IN} \le V_{CC}$                                                                                                                                                               |

| <b>RECEIVER INPUTS</b><br>Input Resistance<br>Differential Input Threshold<br>Input Current (A, B)      | ance 12<br>aput Threshold –0.2 |                                      | +0.2<br>+1.0<br>-0.8 | kOhm<br>Volts<br>mA<br>mA | $\begin{array}{l} -7V \leq V_{_{CM}} \leq 12V \\ -7V \leq V_{_{CM}} \leq 12V \\ V_{_{CC}} = 0V \mbox{ or } 5.25V; \mbox{ I}_{_{IN2}} \\ V_{_{IN}} = +12V \\ V_{_{IN}} = -7V \end{array}$ |

| Maximum Data Rate                                                                                       | 10                             |                                      | 0.0                  | Mbps                      | • in = 7.•                                                                                                                                                                               |

| RECEIVER OUTPUTS<br>Output Voltage<br>V <sub>OH</sub><br>V <sub>OL</sub><br>High Impedance Output Curre | 3.5<br>ent                     |                                      | 0.4<br>±1            | V<br>V<br>μA              | $I_{O} = -4mA; V_{ID} = +0.2V$<br>$I_{O} = +4mA; V_{ID} = -0.2V$<br>$V_{CC} = maximum; 0.4V \le V_{O} \le 2.4V$                                                                          |

| POWER REQUIREMENTS<br>Supply Voltage<br>Supply Current                                                  | 4.75                           | 5.00<br>1                            | 5.25<br>5            | Volts<br>mA               | No load                                                                                                                                                                                  |

| ENVIRONMENTAL AND ME<br>Operating Temperature<br>C<br>E<br>Storage Temperature<br>Package<br>S<br>T     | 0<br>40<br>65<br>16-           | <b>AL</b><br>pin Plastic<br>6-pin SO |                      | ပံုသိ                     |                                                                                                                                                                                          |

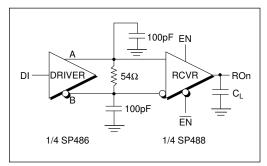

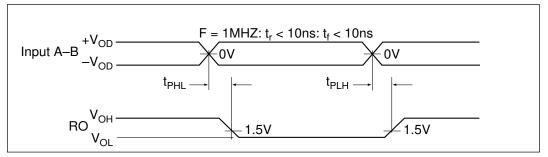

Figure 1. Timing Test Circuit

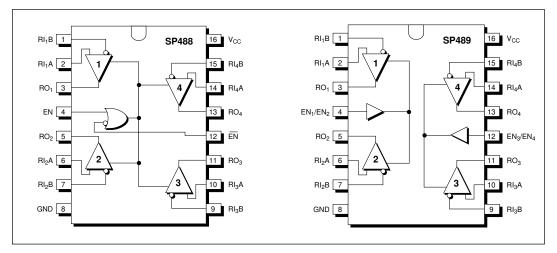

#### **SP488 PINOUT**

Pin 1 — RI<sub>1</sub>B — Receiver 1 input B.

Pin 2 —  $RI_1A$  Receiver 1 input A.

Pin 3 — RO<sub>1</sub> — Receiver 1 Output — If Receiver 1 output is enabled, if  $RI_1A > RI_1B$  by 200mV, Receiver output is high. If Receiver 1 output is enabled, and if  $RI_1A < RI_1B$  by 200mV, Receiver 1 output is low.

Pin 4 — EN — Receiver Output Enable. Please refer to SP488 *Truth Table (1)*.

Pin 5 — RO<sub>2</sub> — Receiver 2 Output — If Receiver 2 output is enabled, if  $RI_2A > RI_2B$  by 200mV, Receiver 2 output is high. If Receiver 2 output is enabled, and if  $RI_2A < RI_2B$  by 200mV, Receiver 2 output is low.

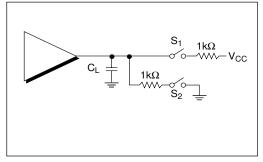

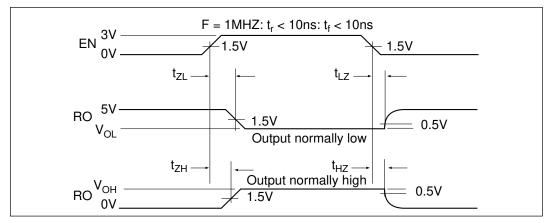

Figure 2. Enable/Disable Timing Test Circuit

Pin 6 —  $RI_2A$  — Receiver 2 input A.

Pin 7 — RI<sub>2</sub>B — Receiver 2 input B.

Pin 8 — GND — Digital Ground.

Pin 9 —  $RI_3B$  — Receiver 3 input B.

Pin  $10 - RI_3A$  - Receiver 3 input A.

Pin 11 — RO<sub>3</sub> — Receiver 3 Output — If Receiver 3 output is enabled, if  $RI_3A > RI_3B$  by 200mV, Receiver 3 output is high. If Receiver 3 output is enabled, and if  $RI_3A < RI_3B$  by 200mV, Receiver 3 output is low.

Pin 12 —  $\overline{EN}$  — Receiver Output Enable. Please refer to SP488 Truth Table (1).

#### PINOUT

Pin 13 — RO<sub>4</sub> — Receiver 4 Output — If Receiver 4 output is enabled, if  $RI_4A > RI_4B$  by 200mV, Receiver 4 output is high. If Receiver 4 output is enabled, and if  $RI_4A < RI_4B$  by 200mV, Receiver 4 output is low.

Pin 14 —  $RI_4A$  — Receiver 4 input A.

Pin 15 —  $RI_AB$  — Receiver 4 input B.

Pin 16 — Supply Voltage  $V_{cc}$  — 4.75V  $\leq V_{cc} \leq$  5.25V.

#### SP489 PINOUT

Pin 1 —  $RI_1B$  — Receiver 1 input B.

Pin 2 —  $RI_1A$  — Receiver 1 input A.

Pin 3 — RO<sub>1</sub> — Receiver 1 Output — If Receiver 1 output is enabled, if  $RI_{1A} > RI_1B$  by 200mV, Receiver output is high. If Receiver 1 output is enabled, and if  $RI_1A < RI_1B$  by 200mV, Receiver 1 output is low.

Pin 4 — EN1/EN2 — Receiver 1 and 2 Output Enable. Please refer to SP489 *Truth Table (2)*.

Pin 5 — RO<sub>2</sub> — Receiver 2 Output — If Receiver 2 output is enabled, if  $RI_2A > RI_2B$  by 200mV, Receiver 2 output is high. If Receiver 2 output is enabled, and if  $RI_2A < RI_2B$  by 200mV, Receiver 2 output is low.

Pin 6 —  $RI_2A$  — Receiver 2 input A.

Pin 7 —  $RI_2B$  — Receiver 2 input B.

Pin 8 — GND — Digital Ground.

| DIFFERENTIAL                    | ENA    | BLES   | OUTPUT |

|---------------------------------|--------|--------|--------|

| A – B                           | EN     | EN     | RO     |

| $V_{\text{ID}} \ge 0.2V$        | H<br>X | X<br>L | ΤT     |

| -0.2V < V <sub>ID</sub> < +0.2V | H<br>X | X<br>L | X<br>X |

| $V_{ID} \leq 0.2V$              | H<br>X | X<br>L | L<br>L |

| х                               | L      | н      | Hi–Z   |

Table 1. SP488 Truth Table

Pin 9 —  $RI_3B$  — Receiver 3 input B.

Pin 10 —  $RI_3A$  — Receiver 3 input A.

Pin 11 — RO<sub>3</sub> — Receiver 3 Output — If Receiver 3 output is enabled, if  $RI_3A > RI_3B$  by 200mV, Receiver 3 output is high. If Receiver 3 output is enabled, and if  $RI_3A < RI_3B$  by 200mV, Receiver 3 output is low.

Pin 12 — EN3/EN4 — Receiver 3 and 4 Output Enable. Please refer to SP489 Truth Table (2).

Pin 13 — RO<sub>4</sub> — Receiver 4 Output — If Receiver 4 output is enabled, if  $RI_4A > RI_4B$  by 200mV, Receiver 4 output is high. If Receiver 4 output is enabled, and if  $RI_4A < RI_4B$  by 200mV, Receiver 4 output is low.

Pin 14 —  $RI_4A$  — Receiver 4 input A.

Pin 15 —  $RI_AB$  — Receiver 4 input B.

Pin 16 — Supply Voltage  $V_{cc}$  — 4.75V  $\leq V_{cc} \leq$  5.25V.

#### FEATURES...

The **SP488** and **SP489** are low–power quad differential line receivers meeting RS-485 and RS-422 standards. The **SP488** features active high and active low common receiver enable controls; the **SP489** provides independent, active high receiver enable controls for each pair of receivers. Both feature tri–state outputs and a -7V to +12V common–mode input range permitting a  $\pm$ 7V ground difference between devices on the communications bus. The **SP488/ 489** are equipped with a fail–safe feature which forces a logic high at the receiver output when the input is left floating. Data rates up to 10Mbps are supported. Both are available in 16-pin plastic DIP and SOIC packages.

| DIFFERENTIAL             | ENABLES            | OUTPUT |  |

|--------------------------|--------------------|--------|--|

| A – B                    | EN1/EN2 or EN3/EN4 | RO     |  |

| $V_{ID} \ge 0.2V$        | н                  | Н      |  |

| $-0.2V < V_{ID} < +0.2V$ | н                  | х      |  |

| $V_{ID} \le 0.2V$        | н                  | L      |  |

| Х                        | L                  | Hi–Z   |  |

Table 2. SP489 Truth Table

#### **AC PARAMETERS**

$V_{_{CC}}$  = 5V±5%; typicals at 25°C; 0°C  $\leq$   $T_{_A}$   $\leq$  +70°C unless otherwise noted.

| PARAMETER                            | MIN.            | TYP. | MAX. | UNIT | CONDITIONS                                    |

|--------------------------------------|-----------------|------|------|------|-----------------------------------------------|

| PROPAGATION DELAY                    |                 |      |      |      |                                               |

| Receiver Input to Output             |                 |      |      |      | C <sub>1</sub> = 15pF; <i>Figure 1, 3</i>     |

| Low to HIGH (tPLH)                   |                 | 120  | 250  | ns   |                                               |

| High to LOW (tPH,)                   |                 | 120  | 250  | ns   |                                               |

| Differential Receiver Skew (ts       | <sub>кр</sub> ) | 13   |      | ns   |                                               |

| Receiver Rise Time (t <sub>R</sub> ) |                 |      |      |      | 10% to 90%                                    |

| SP488                                |                 | 30   | 70   | ns   |                                               |

| SP489                                |                 | 30   | 70   | ns   |                                               |

| Receiver Fall Time (t <sub>F</sub> ) |                 |      |      |      | 90% to 10%                                    |

| SP488                                |                 | 20   | 40   | ns   |                                               |

| SP489                                |                 | 20   | 40   | ns   |                                               |

| RECEIVER ENABLE                      |                 |      |      |      |                                               |

| To Output HIGH                       |                 | 70   | 150  | ns   | C <sub>1</sub> = 15pF; <i>Figures 2 and 4</i> |

|                                      |                 |      |      |      | (S2 closed)                                   |

| To Output LOW                        |                 | 80   | 200  | ns   | CL = 15pF; <i>Figures 2 and 4</i>             |

|                                      |                 |      |      |      | (S1 closed)                                   |

| RECEIVER DISABLE                     |                 |      |      |      |                                               |

| From Output LOW                      |                 | 70   | 150  | ns   | CL = 15pF; <i>Figures 2 and 4</i>             |

|                                      |                 |      |      |      | (S1 closed)                                   |

| From Output HIGH                     |                 | 70   | 150  | ns   | CL = 15pF; Figures 2 and 4                    |

|                                      |                 |      |      |      | (S2 closed)                                   |

| Í                                    |                 |      |      |      |                                               |

Figure 3. Receiver Propagation Delays

Figure 4. Receiver Enable/Disable Timing

#### **ORDERING INFORMATION**

| Quad RS485 Rece | eivers:                       |                   |               |                      |

|-----------------|-------------------------------|-------------------|---------------|----------------------|

| Model           | Enable/Disable                | Temp              | erature Range | Package              |

| SP488CS         | Common; active Low and A      | ctive High 0°C to | o +70°C       | .16-pin Plastic DIP  |

| SP488CT         | Common; active Low and A      | ctive High 0°C to | o +70°C       | 16–pin SOIC          |

| SP488ES         | Common; active Low and A      | ctive High40°C    | C to +85°C    | . 16-pin Plastic DIP |

| SP488ET         | Common; active Low and A      | ctive High40°C    | C to +85°C    | 16–pin SOIC          |

| SP489CS         | One per driver pair; active H | High0°C to        | o +70°C       | .16-pin Plastic DIP  |

| SP489CT         | One per driver pair; active H | High0°C to        | o +70°C       | 16–pin SOIC          |

| SP489ES         | One per driver pair; active H | ligh−40°C         | C to +85°C    | . 16-pin Plastic DIP |

| SP489ET         | One per driver pair; active I | High40°C          | C to +85°C    | 16–pin SOIC          |

|                 |                               |                   |               |                      |

Now available in Lead Free. To order ad "-L" to the part number. Example: SP488/TR= Normal, SP488TR-L = Lead Free

Sipex Corporation

Headquarters and Sales Office 22 Linnell Circle Billerica, MA 01821 TEL: (978) 667-8700 FAX: (978) 670-9001 e-mail: sales@sipex.com

Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.