# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

REV. 1.0.1

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

FEBRUARY 2014

## **GENERAL DESCRIPTION**

The SP510E is a highly integrated physical layer solution that is configurable to support multiple serial standards. It incorporates eight drivers and eight receivers (8TX/8RX), configurable for either differential (V.11 or V.35) or single ended (V.28 and V.10) signaling.

SP510E enables a Serial Communications Controller to implement a variety of serial port types including V.24, V.25, V.36, EIA-530, EIA-530-A, X.21, RS-232. The device architecture is designed to support the data and clock signals used in HDLC or SDLC serial ports as either DTE or DCE.

Operating configuration is programmable in system using the mode-select pins. The V.11 and V.35 modes include internal bus termination that may be switched in or out using the TERM\_OFF pin.

The SP510E is ideal for space constrained applications. It requires only a single 5V supply for full operation. The V<sub>L</sub> pin determines the receiver output voltage (V<sub>OH</sub>, down to 1.65V), for interfacing with lower voltage CPUs and FPGAs. For single supply operation at 5V the V<sub>L</sub> pin will be connected to V<sub>CC</sub>.

Fully compliant V.28 and V.10 driver output voltages are generated using the onboard charge pump. Special power sequencing is not required during system startup. Charge pump outputs are internally regulated to minimize power consumption. The SP510E requires only four  $1\mu$ F capacitors for complete functionality. The device may be put into a low power shutdown mode when not in active use.

All receivers have fail-safe protection to put outputs into an output-high state when inputs are open, shorted, or terminated but idle.

#### FEATURES

- Up to 52Mbps Differential Transmission Rates

- ±15kV HBM ESD Tolerance for Analog I/O Pins

- Integrated Termination Resistors for V.11/V.35

- Eight Drivers and Eight Receivers (8TX/8RX)

- Adjustable Logic Level Pin V<sub>L</sub> (Down to 1.65V)

- Software Selectable Protocols with 3-Bit Word:

- RS-232 (V.28)

- EIA-530 (V.10 & V.11)

- EIA-530A (V.10 & V.11)

- X.21 (V.11)

- RS-449/V.36

- Internal Line or Digital Loopback Testing

- Adheres to NET1/NET2 and TBR2 Requirements

- Easy Flow-Through Pinout

- Single +5V Supply Voltage

- Individual Driver/Receiver Enable/Disable Controls

- Operates in DTE or DCE Mode

- Pin Compatible Upgrade for SP509, SP508

#### TYPICAL APPLICATIONS

- Data Communication Networks

- Telecommunication Equipment

- Secured Data Communication

- CSU and DSU

- Data Routers

- Network Switches

- WAN Access Equipment

- VoIP-PBX Gateways

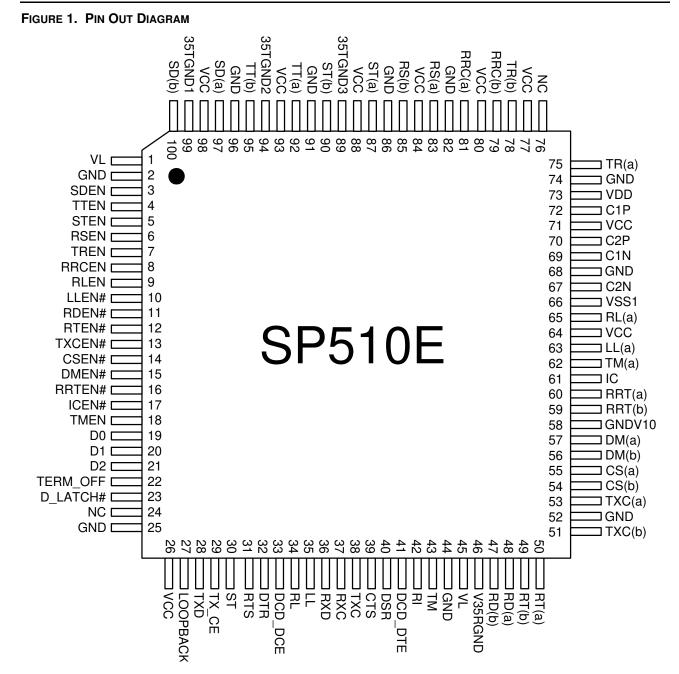

| PART NUMBER | PACKAGE      | OPERATING TEMPERATURE RANGE | DEVICE STATUS |

|-------------|--------------|-----------------------------|---------------|

| SP510EEF-L  | 100-pin LQFP | -40°C to +85°C              | Active        |

| SP510ECF-L  | 100-pin LQFP | 0°C to +70°C                | Active        |

#### **ORDERING INFORMATION**

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

#### ABSOLUTE MAXIMUM RATINGS

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Supply Voltage V <sub>CC</sub>                                                                                                                                              | +7.0V                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Logic-Interface Voltage (VL)                                                                                                                                                | $V_L \le V_{CC}$                  |

| Receiver DC Input Voltage                                                                                                                                                   | ±15.5V                            |

| Input Voltage at TTL Input Pins                                                                                                                                             | -0.3V to (V <sub>CC</sub> + 0.5V) |

| Driver Output Voltage (from Ground)                                                                                                                                         | -7.5V to +12.5V                   |

| Short Circuit Duration, TxOUT to GND                                                                                                                                        | Continuous                        |

| Storage Temperature Range                                                                                                                                                   | -65°C to +150°C                   |

| Lead Temperature (soldering, 10s)                                                                                                                                           | +300°C                            |

| Continuous Power Dissipation at $T_{AMB} = +70^{\circ}C$<br>100-Pin LQFP<br>(derate 19mW/°C above +70°C)<br>$\theta_{JA} = 52.7^{\circ}C/W, \ \theta_{JC} = 6.5^{\circ}C/W$ | 1520mW                            |

## **ESD PROTECTION**

| TX Output & RX Input Pins | ±15 | kV | Human Body Model |

|---------------------------|-----|----|------------------|

| All Other Pins            | ±2  | kV | Human Body Model |

## TABLE 1: DC ELECTRICAL CHARACTERISTICS

| PARAMETERS                               | Symbol            | TEST CONDITIONS                                     | ΜιΝ                                         | Түр   | Мах                 | Unit |

|------------------------------------------|-------------------|-----------------------------------------------------|---------------------------------------------|-------|---------------------|------|

| V <sub>CC</sub> Supply Voltage           | V <sub>CC</sub>   |                                                     | 4.75                                        |       | 5.25                | V    |

| Logic Interface Voltage                  | VL                | $V_L \le V_{CC}$                                    | 1.65                                        |       | 5.25                | V    |

| I <sub>CC</sub> Supply Current           | I <sub>CC</sub>   |                                                     |                                             |       | 300                 | mA   |

| I <sub>CC</sub> Shutdown                 | I <sub>CCSD</sub> |                                                     |                                             | 200   |                     | μA   |

| DRIVER INPUT AND LOGIC INPUT PI          | NS                |                                                     |                                             |       |                     |      |

| Logic Input High                         | V <sub>IH</sub>   |                                                     | 1.6                                         |       |                     | V    |

| Logic Input Low                          | V <sub>IL</sub>   |                                                     |                                             |       | 0.4                 | V    |

| RECEIVER OUTPUTS                         |                   |                                                     |                                             |       |                     |      |

| Receiver Logic Output Low                | V <sub>OL</sub>   | I <sub>OUT</sub> = -3.2 mA                          |                                             |       | 0.4                 | V    |

| Receiver Logic Output High               | V <sub>OH</sub>   | I <sub>OUT</sub> = 1 mA                             | I <sub>OUT</sub> = 1 mA V <sub>L</sub> -0.3 |       | V <sub>L</sub> +0.3 | V    |

| Receiver Output<br>Short-Circuit Current | I <sub>OSS</sub>  | $0V < V_O < V_{CC}$ ±2                              |                                             | ±20   | ±60                 | mA   |

| Receiver Output<br>Leakage Current       | I <sub>OZ</sub>   | Receivers disabled<br>0.4V < V <sub>O</sub> < 5.25V |                                             | ±0.05 | ±1                  | μA   |

| V.28 / RS-232 Drivers                    |                   |                                                     | 1                                           | I     |                     |      |

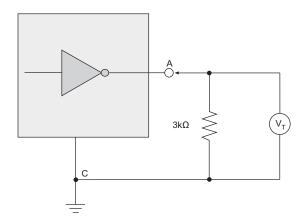

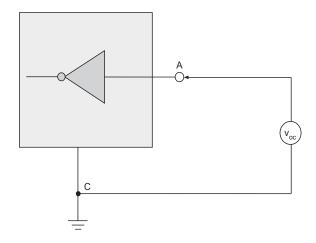

|                                          | V <sub>T</sub>    | Output load = $3k\Omega$ to GND<br>Figure 3         | ±5                                          | ±6    | ±15                 | V    |

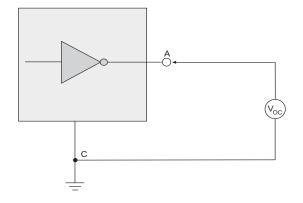

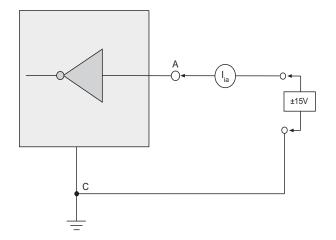

| Output Voltage Swing                     | V <sub>OC</sub>   | Open Circuit Output<br>Figure 2                     |                                             |       | ±15                 | V    |

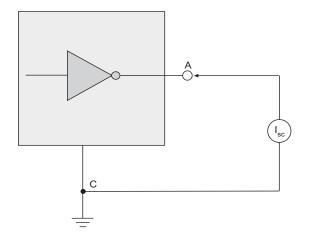

| Short Circuit Current                    | I <sub>SC</sub>   | V <sub>OUT</sub> = 0V, Figure 5                     |                                             |       | ±100                | mA   |

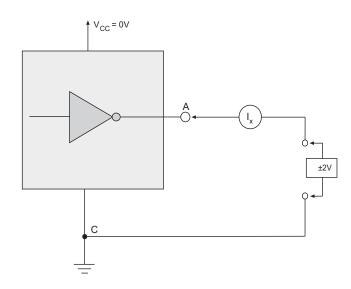

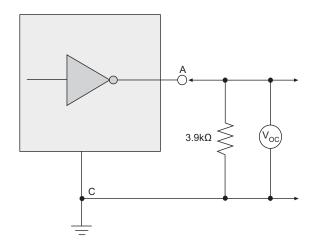

| Power-Off Impedance                      |                   | Figure 6                                            | 300                                         | 10M   |                     | Ω    |

| V.28 / RS-232 Receivers                  |                   |                                                     |                                             |       |                     |      |

| Input Voltage Range                      |                   |                                                     | -15                                         |       | 15                  | V    |

| Input Threshold Low                      |                   |                                                     | 0.8                                         | 1.2   |                     | V    |

| Input Threshold High                     |                   |                                                     |                                             | 1.7   | 3                   | V    |

| Input Hysteresis                         |                   |                                                     |                                             | 500   |                     | mV   |

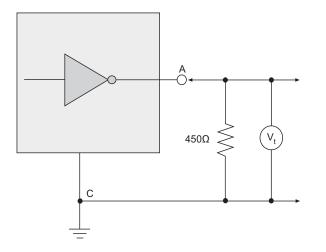

| Input Resistance                         |                   | Figure 8                                            | 3                                           | 5     | 7                   | kΩ   |

| Open Circuit Bias                        | V <sub>OC</sub>   | Figure 9                                            |                                             |       | ±2                  | V    |

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

A New Direction in Mixed-Signal REV. 1.0.1

| PARAMETERS                     | SYMBOL                             | TEST CONDITIONS            | Min                | Түр | Мах    | Unit     |

|--------------------------------|------------------------------------|----------------------------|--------------------|-----|--------|----------|

|                                |                                    |                            |                    |     |        | <u> </u> |

| V.10 / RS-423 DRIVERS          |                                    |                            |                    |     |        |          |

| Open Circuit Voltage           | V <sub>OC</sub>                    | Figure 10                  | ±4                 |     | ±6     | V        |

| Test Terminated Voltage        | V <sub>T</sub>                     | Figure 11                  | 0.9V <sub>OC</sub> |     |        | V        |

| Short Circuit Current          | I <sub>SC</sub>                    | Figure 12                  |                    |     | ±150   | mA       |

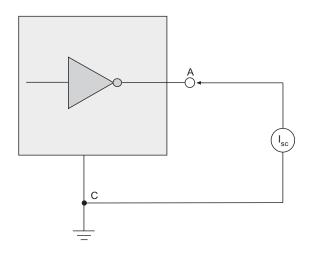

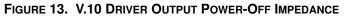

| Power-Off Current              |                                    | Figure 13                  |                    |     | ±100   | μA       |

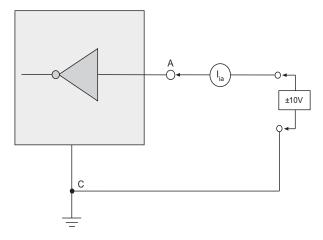

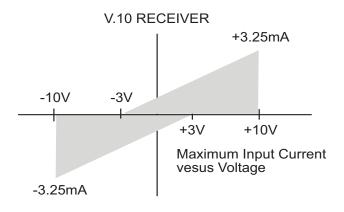

| V.10 / RS-423 Receivers        |                                    |                            |                    |     |        |          |

| Input Current                  | I <sub>IA</sub>                    | Figure 15 and Figure 16    | -3.25              |     | +3.25  | mA       |

| Input Impedance                |                                    |                            | 4                  | 15  |        | kΩ       |

| Sensitivity                    |                                    |                            |                    |     | ±0.2   | V        |

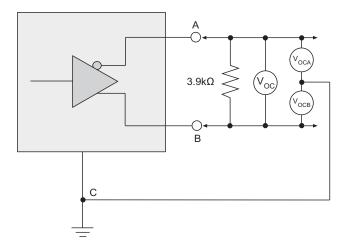

| V.11 / RS-422 Drivers          |                                    |                            |                    |     |        |          |

| Open Circuit Voltage           | V <sub>OCA</sub> ,V <sub>OCB</sub> | Figure 17                  |                    |     | ±6     | V        |

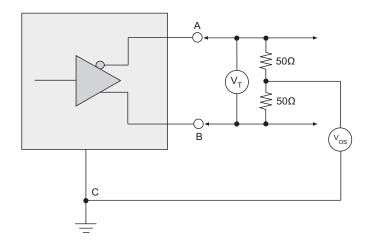

| Test Terminated Voltage        | V <sub>T</sub>                     | Figure 18                  | ±2                 |     |        | V        |

| Balance                        | $\Delta V_T$                       | Figure 18                  |                    |     | ±0.4   | V        |

| Driver DC Offset               | V <sub>OS</sub>                    | Figure 18                  |                    |     | 3      | V        |

| Offset Balance                 | $\Delta V_{OS}$                    | Figure 18                  |                    |     | ±0.4   | V        |

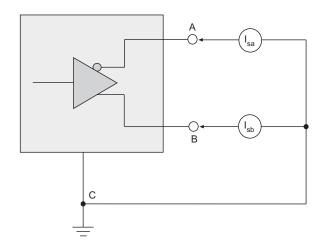

| Short Circuit Output Current   | I <sub>SA,</sub> I <sub>SB</sub>   | Figure 19                  |                    |     | ±150   | mA       |

| Power-Off Current              |                                    | Figure 20                  |                    |     | ±100   | μΑ       |

| V.11 / RS-422 Receivers        |                                    |                            |                    |     |        |          |

| Receiver Input Range           | V <sub>CM</sub>                    |                            | -7                 |     | +7     | V        |

| Input Current                  | I <sub>IA,</sub> I <sub>IB</sub>   | Figure 21 and Figure 23    |                    |     | ±3.25  | mV       |

| Input Current with Termination | I <sub>IA,</sub> I <sub>IB</sub>   | Figure 24 and Figure 25    |                    |     | ±60.75 | mA       |

| Receiver Input Impedance       | R <sub>IN</sub>                    | $-10V \le V_{CM} \le +10V$ | 4                  | 15  |        | kΩ       |

| Receiver Sensitivity           | V <sub>TH</sub>                    |                            |                    |     | ±0.2   | V        |

| Receiver Input Hysteresis      | ΔV <sub>TH</sub>                   | V <sub>CM</sub> = 0 V      |                    | 15  |        | mV       |

4

A New Direction in Mixed-Signal REV. 1.0.1

ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

**SP510E**

| PARAMETERS                        | SYMBOL          | TEST CONDITIONS                                      | Min                 | Түр  | Мах                 | Unit |

|-----------------------------------|-----------------|------------------------------------------------------|---------------------|------|---------------------|------|

| V.35 DRIVERS (ALL VALUES MEASURED | WITH TERM       | _OFF = '0')                                          |                     |      |                     |      |

| Test Terminated Voltage           | V <sub>T</sub>  | Figure 26                                            | ±0.44               |      | ±0.66               | V    |

| Offset                            | V <sub>OS</sub> | Figure 26                                            |                     |      | ±0.6                | V    |

| Output Overshoot                  |                 | Figure 26,<br>V <sub>ST</sub> = Steady State Voltage | -0.2V <sub>ST</sub> |      | +0.2V <sub>ST</sub> | V    |

| Source Impedance                  |                 | Figure 29<br>$Z_S = V_2 / V_1 \times 50\Omega$       | 50                  |      | 150                 | Ω    |

| Short Circuit Impedance           |                 | Figure 28                                            | 135                 |      | 165                 | Ω    |

| V.35 RECEIVERS (ALL VALUES MEASUF |                 | :M_OFF = '0')                                        | 1                   |      |                     |      |

| Sensitivity                       |                 |                                                      |                     | ±100 | ±200                | mV   |

| Source Impedance                  |                 | Figure 30<br>$Z_S = V_2 / V_1 \times 50\Omega$       | 90                  |      | 110                 | Ω    |

| Short-Circuit Impedance           |                 | Figure 31                                            | 135                 |      | 165                 | Ω    |

| TRANSCEIVER LEAKAGE CURRENT       |                 |                                                      |                     |      |                     |      |

| Driver Output Tri-state Current   |                 | Drivers disabled, Figure 32                          |                     | 500  |                     | μA   |

|                                   |                 | Tx and Rx Disabled,                                  |                     |      |                     |      |

## TABLE 2: AC TIMING CHARACTERISTICS

## TIMING CHARACTERISTICS

| PARAMETERS                                             | Symbol                                | TEST CONDITIONS                                               | Min | Түр | ΜΑΧ | Unit |

|--------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| V.28 / RS-232 DRIVER                                   |                                       |                                                               |     |     |     |      |

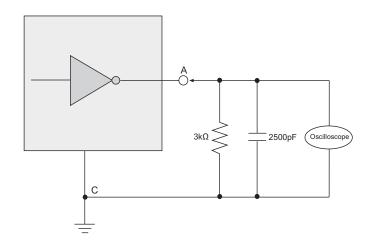

| Maximum Transmission Rate                              |                                       | Figure 7                                                      | 250 |     |     | kbps |

| Driver Propagation Delay                               | t <sub>DPHL</sub> , t <sub>DPLH</sub> |                                                               | 0.5 | 1   | 5   | μs   |

| Driver Transition Time                                 |                                       | +3V to -3V, Figure 7                                          | 0.2 |     | 1.5 | μs   |

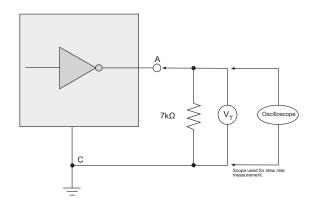

| Instantaneous Slew Rate                                |                                       | +3V to -3V, Figure 4                                          | 4   |     | 30  | V/µs |

| Driver Skew                                            |                                       | t <sub>DPHL</sub> - t <sub>DPLH</sub><br>at zero crossing     |     | 100 | 800 | ns   |

| Driver Channel to Channel Skew                         |                                       |                                                               |     | 20  |     | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low   | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 40 |     |     | 2   | μs   |

| Driver Output Enable Time<br>Tri-state to Output High  | t <sub>DZH</sub>                      | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 34 and Figure 40 |     |     | 2   | μs   |

| Driver Output Disable Time<br>Output Low to Tri-state  | t <sub>DLZ</sub>                      | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 34 and Figure 40  |     |     | 2   | μs   |

| Driver Output Disable Time<br>Output High to Tri-state | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 40  |     |     | 2   | μs   |

#### V.28 / RS-232 RECEIVER

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub> | R_IN to R_OUT, $C_L = 15 \text{ pF}$                          | 50 | 100 | 500 | ns |

|----------------------------------------------------------|-------------------------------------|---------------------------------------------------------------|----|-----|-----|----|

| Receiver Skew                                            |                                     | t <sub>PHL</sub> - t <sub>PLH</sub>   at 1.5V                 |    | 50  |     | ns |

| Receiver Channel to Channel Skew                         |                                     |                                                               |    | 20  |     | ns |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>     | C <sub>L</sub> = 15 pF                                        |    | 15  |     | ns |

| Receiver Output Enable Time<br>Tri-state to Output Low   | t <sub>ZL</sub>                     | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 35 and Figure 40 |    |     | 2   | μs |

| Receiver Output Enable Time<br>Tri-state to Output High  | t <sub>ZH</sub>                     | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 40 |    |     | 2   | μs |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                     | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 40  |    |     | 2   | μs |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                     | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 40  |    |     | 2   | μs |

| Charge Pump Rise Time                                    |                                     | Shutdown to operational                                       |    |     | 2   | ms |

A New Direction in Mixed-Signal REV. 1.0.1

ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

**SP510E**

#### -----

| TIMING CHARACTERISTICS<br>$V_{CC} = +4.75$ to 5.25V, C1-C4 = 1µF; | $T_{AAB} = T_{ABA}$ to                |                                                               | values are a | t Taxan = - | +25°C |      |

|-------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|--------------|-------------|-------|------|

|                                                                   |                                       | TEST CONDITIONS                                               |              | Түр         | MAX   | Unit |

| V.10 / RS-423 DRIVER                                              |                                       |                                                               |              |             |       |      |

| Maximum Transmission Rate                                         |                                       |                                                               | 250          |             |       | kbps |

| Driver Propagation Delay                                          | t <sub>DPHL</sub> , t <sub>DPLH</sub> |                                                               | 30           | 150         | 500   | ns   |

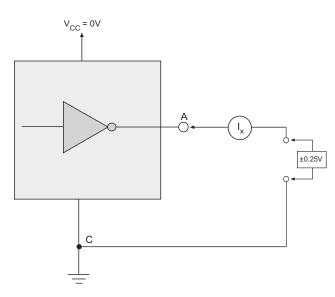

| Driver Rise / Fall Time                                           | t <sub>DR</sub> , t <sub>DF</sub>     | 10% to 90%, Figure 14                                         |              |             | 500   | ns   |

| Driver Skew                                                       |                                       | t <sub>DPHL</sub> - t <sub>DPLH</sub>  <br>at zero crossing   |              |             | 100   | ns   |

| Driver Channel to Channel Skew                                    |                                       |                                                               |              | 5           |       | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low              | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 40 |              |             | 2     | μs   |

| Driver Output Enable Time<br>Tri-state to Output High             | t <sub>DZH</sub>                      | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 34 and Figure 40 |              |             | 2     | μs   |

| Driver Output Disable Time<br>Output Low to Tri-state             | t <sub>DLZ</sub>                      | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 34 and Figure 40  |              |             | 2     | μs   |

| Driver Output Disable Time<br>Output High to Tri-state            | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 40  |              |             | 2     | μs   |

| V.10 / RS-423 RECEIVER                                            |                                       |                                                               |              |             |       |      |

| Receiver Propagation Delay                                        | t <sub>PHL</sub> , t <sub>PLH</sub>   |                                                               |              | 100         | 500   | ns   |

| Receiver Output Rise / Fall Time                                  | t <sub>R</sub> , t <sub>F</sub>       | C <sub>L</sub> = 15 pF                                        |              | 15          |       | ns   |

| Receiver Skew                                                     |                                       | ∣t <sub>PHL</sub> - t <sub>PLH</sub> ∣ at 1.5V                |              | 5           |       | ns   |

| Receiver Channel to Channel Skew                                  |                                       |                                                               |              | 5           |       | ns   |

| Receiver Output Enable Time<br>Tri-state to Output Low            | t <sub>ZL</sub>                       | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 35 and Figure 40 |              |             | 2     | μs   |

| Receiver Output Enable Time<br>Tri-state to Output High           | t <sub>ZH</sub>                       | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 40 |              |             | 2     | μs   |

| Receiver Output Disable Time<br>Output Low to Tri-state           | t <sub>LZ</sub>                       | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 40  |              |             | 2     | μs   |

| Receiver Output Disable Time<br>Output High to Tri-state          | t <sub>HZ</sub>                       | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 40  |              |             | 2     | μs   |

REV. 1.0.1

| TIMING CHARACTERISTICS                                   |                                       |                                                                        |     |     |     |      |

|----------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| $V_{CC} = +4.75$ to 5.25V, C1-C4 = 1µF;                  |                                       |                                                                        |     | 1   | 1   |      |

| PARAMETERS                                               | SYMBOL                                | TEST CONDITIONS                                                        | Min | Түр | Мах | Unit |

| HIGH SPEED V.11 / RS-422 (DRIVERS                        | 1, 2 & 3)                             |                                                                        |     |     |     |      |

| Maximum Bit Rate                                         |                                       |                                                                        | 52  |     |     | Mbps |

| Driver Rise and Fall Time                                | t <sub>DR</sub> , t <sub>DF</sub>     | 10-90%<br>Figure 22 and Figure 36                                      |     |     | 6   | ns   |

| Driver Propagation Delay Time                            | t <sub>DPHL</sub> , t <sub>DPLH</sub> | C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 36                      |     | 20  | 50  | ns   |

| Driver Skew                                              |                                       | $ t_{DPHL} - t_{DPLH}  C_L = 50 \text{ pF}$<br>Figure 33 and Figure 36 |     |     | 3.8 | ns   |

| Driver Channel to Channel Skew                           |                                       |                                                                        |     | 2   |     | ns   |

| Driver Output Enable Time<br>Tri-state to Output Low     | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 37          |     |     | 100 | ns   |

| Driver Output Enable Time<br>Tri-state to Output High    | t <sub>DZH</sub>                      | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 34 and Figure 37          |     |     | 100 | ns   |

| Driver Output Disable Time<br>Output Low to Tri-state    | t <sub>DLZ</sub>                      | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 34 and Figure 37           |     |     | 100 | ns   |

| Driver Output Disable Time<br>Output High to Tri-state   | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 37           |     |     | 100 | ns   |

| HIGH SPEED V.11 / RS-422 (RECEIVER                       | as 1, 2 & 3)                          |                                                                        |     |     |     |      |

| Receiver Output Rise / Fall Time                         | t <sub>R</sub> , t <sub>F</sub>       | C <sub>L</sub> = 50 pF                                                 |     |     | 6   | ns   |

| Receiver Propagation Delay                               | t <sub>PHL</sub> , t <sub>PLH</sub>   | C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 38                      |     | 20  | 50  | ns   |

| Receiver Skew                                            |                                       | $ t_{PHL} - t_{PLH}  C_L = 50 \text{ pF}$<br>Figure 33 and Figure 38   |     |     | 3.8 | ns   |

| Receiver Channel to Channel Skew                         |                                       |                                                                        |     | 2   |     | ns   |

| Receiver Output Enable Time<br>Tri-state to Output Low   | t <sub>ZL</sub>                       | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 35 and Figure 39          |     |     | 100 | ns   |

| Receiver Output Enable Time<br>Tri-state to Output High  | t <sub>ZH</sub>                       | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 39          |     |     | 100 | ns   |

| Receiver Output Disable Time<br>Output Low to Tri-state  | t <sub>LZ</sub>                       | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 39           |     |     | 100 | ns   |

| Receiver Output Disable Time<br>Output High to Tri-state | t <sub>HZ</sub>                       | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 39           |     |     | 100 | ns   |

#### TIMING CHARACTERISTICS V<sub>CC</sub> = +4.75 to 5.25V, C1-C4 = 1µF; T<sub>AMB</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless noted. Typical values are at T<sub>AMB</sub> = +25°C. PARAMETERS SYMBOL TEST CONDITIONS ΜιΝ Түр MAX UNIT V.11 / RS-422 HANDSHAKE SIGNALS (DRIVERS 4, 5 & 6) Figure 33 10 Mbps Maximum Bit Rate 2 Figure 22 and Figure 36 10 Driver Rise and Fall Time ns t<sub>DR</sub>, t<sub>DF</sub> $C_{I} = 50 \, pF$ Driver Propagation Delay Time 20 t<sub>DPHL</sub>, t<sub>DPLH</sub> 50 ns Figure 33 and Figure 36 10 ns $|t_{DPHL} - t_{DPLH}|, C_L = 50 \text{ pF}$ Driver Skew Figure 33 and Figure 36 2 Driver Channel to Channel Skew ns Driver Output Enable Time $C_L = 100 \text{ pF}, S1 \text{ closed}$ t<sub>DZL</sub> 100 ns Tri-state to Output Low Figure 34 and Figure 37 C<sub>L</sub> = 100 pF, S2 closed **Driver Output Enable Time** 100 t<sub>DZH</sub> ns Tri-state to Output High Figure 34 and Figure 37 $C_I = 15 \text{ pF}, S1 \text{ closed}$ **Driver Output Disable Time** 100 t<sub>DLZ</sub> ns Output Low to Tri-state Figure 34 and Figure 37 C<sub>I</sub> = 15 pF, S2 closed Driver Output Disable Time 100 t<sub>DHZ</sub> ns Output High to Tri-state Figure 34 and Figure 37 V.11 / RS-422 HANDSHAKE SIGNALS (RECEIVERS 4, 5 & 6) $C_{I} = 50 \, pF$ 20 Receiver Output Rise / Fall Time t<sub>R</sub>, t<sub>F</sub> ns $C_{I} = 50 \, pF$ **Receiver Propagation Delay** t<sub>PHL</sub>, t<sub>PLH</sub> 20 50 ns Figure 33 and Figure 38 $|t_{PHL} - t_{PLH}| C_L = 50 \text{ pF}$ **Receiver Skew** 10 ns Figure 33 and Figure 38 Receiver Channel to Channel Skew 2 ns $C_I = 100 \text{ pF}, S1 \text{ closed}$ Receiver Output Enable Time 100 t<sub>ZL</sub> ns Tri-state to Output Low Figure 35 and Figure 39 $C_L = 100 \text{ pF}$ , S2 closed **Receiver Output Enable Time** 100 ns t<sub>ZH</sub> Tri-state to Output High Figure 35 and Figure 39 $C_{I} = 15 \text{ pF}, S1 \text{ closed}$ **Receiver Output Disable Time** t<sub>LZ</sub> 100 ns Output Low to Tri-state Figure 35 and Figure 39 $C_L = 15 \text{ pF}, S2 \text{ closed}$ **Receiver Output Disable Time** t<sub>HZ</sub> 100 ns Output High to Tri-state Figure 35 and Figure 39

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

REV. 1.0.1

| <b>TIMING CHARACTERISTICS</b><br>$V_{CC} = +4.75$ to 5.25V, C1-C4 = 1µF; T <sub>AMB</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> , unless noted. Typical values are at T <sub>AMB</sub> = +25°C. |                                       |                                                                        |     |     |     |      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------|-----|-----|-----|------|--|

| PARAMETERS                                                                                                                                                                                       |                                       | Test Conditions                                                        | Min | Түр | Max | Unit |  |

| V.35 (DRIVERS 1, 2 & 3)                                                                                                                                                                          |                                       |                                                                        | L   |     |     |      |  |

| Maximum Bit Rate                                                                                                                                                                                 |                                       | f <sub>MAX</sub> = 20 MHz, Figure 33                                   | 40  |     |     | Mbps |  |

| Driver Rise and Fall Time                                                                                                                                                                        | t <sub>DR</sub> , t <sub>DF</sub>     | Figure 29                                                              |     |     | 10  | ns   |  |

| Driver Propagation Delay Time                                                                                                                                                                    | t <sub>DPHL</sub> , t <sub>DPLH</sub> | C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 36                      |     | 25  | 50  | ns   |  |

| Driver Skew                                                                                                                                                                                      |                                       | $ t_{DPHL} - t_{DPLH}  C_L = 50 \text{ pF}$<br>Figure 33 and Figure 36 |     | 2   | 5   | ns   |  |

| Driver Channel to Channel Skew                                                                                                                                                                   |                                       |                                                                        |     | 2   |     | ns   |  |

| Driver Output Enable Time<br>Tri-state to Output Low                                                                                                                                             | t <sub>DZL</sub>                      | C <sub>L</sub> = 100 pF, S1 closed<br>Figure 34 and Figure 37          |     |     | 200 | ns   |  |

| Driver Output Enable Time<br>Tri-state to Output High                                                                                                                                            | t <sub>DZH</sub>                      | $C_L = 100 \text{ pF}$ , S2 closed<br>Figure 34 and Figure 37          |     |     | 200 | ns   |  |

| Driver Output Disable Time<br>Output Low to Tri-state                                                                                                                                            | t <sub>DLZ</sub>                      | $C_L = 15 \text{ pF}$ , S1 closed<br>Figure 34 and Figure 37           |     |     | 200 | ns   |  |

| Driver Output Disable Time<br>Output High to Tri-state                                                                                                                                           | t <sub>DHZ</sub>                      | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 34 and Figure 37           |     |     | 200 | ns   |  |

| V.35 (Receivers 1, 2 & 3)                                                                                                                                                                        |                                       |                                                                        |     |     |     |      |  |

| Receiver Propagation Delay                                                                                                                                                                       | t <sub>PHL</sub> , t <sub>PLH</sub>   | C <sub>L</sub> = 50 pF<br>Figure 33 and Figure 38                      |     | 30  | 50  | ns   |  |

| Receiver Skew                                                                                                                                                                                    |                                       | $ t_{PHL} - t_{PLH}  C_L = 50 \text{ pF}$<br>Figure 33 and Figure 38   |     |     | 5   | ns   |  |

| Receiver Channel to Channel Skew                                                                                                                                                                 |                                       |                                                                        |     | 2   |     | ns   |  |

| Receiver Output Enable Time<br>Tri-state to Output Low                                                                                                                                           | t <sub>ZL</sub>                       | $C_L = 100 \text{ pF}$ , S1 closed<br>Figure 35 and Figure 39          |     |     | 200 | ns   |  |

| Receiver Output Enable Time<br>Tri-state to Output High                                                                                                                                          | t <sub>zH</sub>                       | C <sub>L</sub> = 100 pF, S2 closed<br>Figure 35 and Figure 39          |     |     | 200 | ns   |  |

| Receiver Output Disable Time<br>Output Low to Tri-state                                                                                                                                          | t <sub>LZ</sub>                       | C <sub>L</sub> = 15 pF, S1 closed<br>Figure 35 and Figure 39           |     |     | 200 | ns   |  |

| Receiver Output Disable Time<br>Output High to Tri-state                                                                                                                                         | t <sub>HZ</sub>                       | C <sub>L</sub> = 15 pF, S2 closed<br>Figure 35 and Figure 39           |     |     | 200 | ns   |  |

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

#### **TABLE 3: PIN DESCRIPTIONS BY FUNCTION**

| PIN NAME          | PIN NUMBER | I/O |     | DESCRIPTION                                                            |

|-------------------|------------|-----|-----|------------------------------------------------------------------------|

| DIFFERENTIAL DRIV | ERS        |     |     |                                                                        |

| TxD               | 28         | I   | TTL | TxD Driver Input                                                       |

| SD(b) / SD(a)     | 100, 97    | 0   | TTL | Differential Transmit data non-inverting (b) and inverting (a) outputs |

| V35TGND1          | 99         | I   |     | SD Termination Reference                                               |

| SDEN              | 3          | I   | TTL | TxD Driver Enable                                                      |

| TxCE              | 29         | I   | TTL | TxCE Driver Input                                                      |

| TT(b) / TT(a)     | 95, 92     | 0   | TTL | Differential TxCE non-inverting (b) and inverting (a) outputs          |

| V35TGND2          | 94         | I   |     | TT Termination Reference                                               |

| TTEN              | 4          | I   | TTL | TxCE Driver Enable                                                     |

| ST                | 30         | l   | TTL | ST Driver Input                                                        |

| ST(b) / ST(a)     | 90, 87     | 0   | TTL | Differential ST non-inverting (b) and inverting (a) outputs            |

| V35TGND3          | 89         | I   |     | ST Termination Reference                                               |

| STEN              | 5          | I   | TTL | ST Driver Enable                                                       |

| RTS               | 31         | l   | TTL | RTS Driver Input                                                       |

| RS(b) / RS(a)     | 85, 83     | 0   | TTL | Differential RTS non-inverting (b) and inverting (a) outputs           |

| RSEN              | 6          | I   | TTL | RTS Driver Enable                                                      |

| DTR               | 32         | I   | TTL | DTR Driver Input                                                       |

| TR(b) / TR(a)     | 78, 75     | 0   | TTL | Differential DTR non-inverting (b) and inverting (a) outputs           |

| TREN              | 7          | I   | TTL | DTR Driver Enable                                                      |

| DCD_DCE           | 33         | l   | TTL | DCD_DCE Driver Input                                                   |

| RRC(b) / RRC(a)   | 79, 81     | 0   | TTL | Differential DCD non-inverting (b) and inverting (a) outputs           |

| RRCEN             | 8          | I   | TTL | DCD Driver Enable                                                      |

| SINGLE ENDED DRIV | /ERS       |     |     |                                                                        |

| RL                | 34         | I   | TTL | RL Driver Input                                                        |

| RL(a)             | 65         | 0   | TTL | RL Driver Output                                                       |

| RLEN              | 9          | I   | TTL | RL Driver Enable                                                       |

| LL                | 35         | I   | TTL | LL Driver Input                                                        |

| LL(a)             | 63         | 0   | TTL | LL Driver Output                                                       |

| LLEN#             | 10         | I   | TTL | LL Driver Enable, active low                                           |

REV. 1.0.1

|                                   | SP510E    |

|-----------------------------------|-----------|

| ULTRA HIGH SPEED MULTIPROTOCOL TR | ANSCEIVER |

| PIN NAME          | PIN NUMBER | I/O |     | DESCRIPTION                                                     |

|-------------------|------------|-----|-----|-----------------------------------------------------------------|

| DIFFERENTIAL RECE | EIVERS     |     |     |                                                                 |

| RxD               | 36         | 0   | TTL | RxD Receiver Output                                             |

| RD(b) / RD(a)     | 47, 48     | I   | TTL | Differential RXD non-inverting (b) and inverting (a) inputs     |

| RDEN#             | 11         | I   | TTL | RxD Receiver Enable, active low                                 |

| RxC               | 37         | 0   | TTL | RxC Receiver Output                                             |

| RT(b) / RT(a)     | 49, 50     | I   | TTL | Differential RXC non-inverting (b) and inverting (a) inputs     |

| RTEN#             | 12         | I   | TTL | RxC Receiver Enable, active low                                 |

| TxC               | 38         | 0   | TTL | TxC Receiver Output                                             |

| TxC(b) / TxC(a)   | 51, 53     | I   | TTL | Differential TxC non-inverting (b) and inverting (a) inputs     |

| TxCEN#            | 13         | I   | TTL | TxC Receiver Enable, active low                                 |

| CTS               | 39         | 0   | TTL | CTS Receiver Output                                             |

| CS(b) / CS(a)     | 54, 55     | I   | TTL | Differential CTS non-inverting (b) and inverting (a) inputs     |

| CSEN#             | 14         | I   | TTL | CTS Receiver Enable, active low                                 |

| DSR               | 40         | 0   | TTL | DSR Receiver Output                                             |

| DM(b) / DM(a)     | 56, 57     | I   | TTL | Differential DSR non-inverting (b) and inverting (a) inputs     |

| DMEN#             | 15         | I   | TTL | DSR Receiver Enable, active low                                 |

| DCD_DTE           | 41         | 0   | TTL | DCD_DTE Receiver Output                                         |

| RRT(b) / RRT(a)   | 59, 60     | I   | TTL | Differential DCD_DTE non-inverting (b) and inverting (a) inputs |

| RRTEN#            | 16         | I   | TTL | DCD_DTE Receiver Enable, active low                             |

| SINGLE ENDED REC  | EIVERS     |     |     |                                                                 |

| IC                | 61         | I   | TTL | RI Receiver Input                                               |

| RI                | 42         | 0   | TTL | RI Receiver Output                                              |

| ICEN#             | 17         | I   | TTL | RI Receiver Enable, active low                                  |

| TM(a)             | 62         | I   | TTL | TM Receiver Input                                               |

| ТМ                | 43         | 0   | TTL | TM Receiver Output                                              |

| TMEN              | 18         | I   | TTL | TM Receiver Enable                                              |

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

| Pin Name        | PIN NUMBER                                  | I/O  |     | DESCRIPTION                                                                                 |

|-----------------|---------------------------------------------|------|-----|---------------------------------------------------------------------------------------------|

| PROTOCOL & MOD  | E SELECTION PINS                            |      |     |                                                                                             |

| D2, D1, D0      | 21, 20, 19                                  | I    | TTL | Mode Select - Refer to Table 5 and Table 6                                                  |

| CHARGE PUMP PIN | IS                                          |      |     |                                                                                             |

| C1P, C1N        | 72, 69                                      | l    |     | Charge Pump Capacitor 1 +/- inputs. Connect a 1 $\mu F$ capacitor between C1P and C1N pins. |

| C2P, C2N        | 70, 67                                      | I    |     | Charge Pump Capacitor 2 +/- inputs. Connect a 1 $\mu F$ capacitor between C2P and C2N pins. |

| VSS1            | 66                                          | Ι    |     | -2xV <sub>CC</sub> Charge Pump                                                              |

| VDD             | 73                                          | I    |     | 2xV <sub>CC</sub> Charge Pump                                                               |

|                 | -                                           |      |     |                                                                                             |

| LOOPBACK#       | 27                                          | <br> | TTL | Loopback mode enable, active low                                                            |

| D_LATCH#        | 23                                          | I    | -   | Decoder Latch, active low                                                                   |

| TERM_OFF        | 22                                          | I    |     | Termination disable                                                                         |

| Reserved Pins   |                                             |      |     |                                                                                             |

| NC              | 24, 76                                      |      |     | No Connect                                                                                  |

| Power and Grou  | IND <b>P</b> INS                            |      |     |                                                                                             |

| VCC             | 26, 64, 71, 77,<br>80, 84, 88, 98           | I    |     | 5V supply                                                                                   |

| VL              | 1, 45                                       | I    |     | Logic I/O Power Supply Input                                                                |

| GND             | 2, 25, 44, 52,<br>68, 74, 82, 86,<br>91, 96 | I    |     | Ground                                                                                      |

| GNDV10          | 58                                          | I    |     | V.10 Receiver Ground Reference                                                              |

| V35RGND         | 46                                          | 0    |     | Receiver Termination Reference                                                              |

*NOTE:* Pin type: I = Input, O = Output, I/O = Input/output.

## TABLE 4: PIN DESCRIPTIONS BY PIN NUMBER

| Pin D | PIN DESCRIPTIONS BY PIN NUMBER |                               |    |         |                                |  |  |  |  |

|-------|--------------------------------|-------------------------------|----|---------|--------------------------------|--|--|--|--|

| 1     | VL                             | Logic I/O Power Supply Input  | 32 | DTR     | DTR Driver TTL Input           |  |  |  |  |

| 2     | GND                            | Ground                        | 33 | DCD_DCE | DCD_DCE Driver TTL Input       |  |  |  |  |

| 3     | SDEN                           | TxD Driver Enable Input       | 34 | RL      | RL Driver TTL Input            |  |  |  |  |

| 4     | TTEN                           | TxCE Driver Enable Input      | 35 | LL      | LL Driver TTL Input            |  |  |  |  |

| 5     | STEN                           | ST Driver Enable Input        | 36 | RxD     | RxD Receiver TTL Output        |  |  |  |  |

| 6     | RSEN                           | RTS Driver Enable Input       | 37 | RxC     | RxC Receiver TTL Output        |  |  |  |  |

| 7     | TREN                           | DTR Driver Enable Input       | 38 | TxC     | TxC Receiver TTL Output        |  |  |  |  |

| 8     | RRCEN                          | DCD Driver Enable Input       | 39 | CTS     | CTS Receiver TTL Output        |  |  |  |  |

| 9     | RLEN                           | RL Driver Enable Input        | 40 | DSR     | DSR Receiver TTL Output        |  |  |  |  |

| 10    | LLEN#                          | LL Driver Enable Input        | 41 | DCD_DTE | DCD_DTE Receiver TTL Output    |  |  |  |  |

| 11    | RDEN#                          | RxD Receiver Enable Input     | 42 | RI      | RI Receiver TTL Output         |  |  |  |  |

| 12    | RTEN#                          | RxC Receiver Enable Input     | 43 | ТМ      | TM Receiver TTL Output         |  |  |  |  |

| 13    | TxCEN#                         | TxC Receiver Enable Input     | 44 | GND     | Ground                         |  |  |  |  |

| 14    | CSEN#                          | CTS Receiver Enable Input     | 45 | VL      | Logic I/O Power Supply Input   |  |  |  |  |

| 15    | DMEN#                          | DSR Receiver Enable Input     | 46 | V35RGND | Receiver Termination Reference |  |  |  |  |

| 16    | RRTEN#                         | DCD_DTE Receiver Enable Input | 47 | RD(b)   | RXD Non-Inverting Input        |  |  |  |  |

| 17    | ICEN#                          | RI Receiver Enable Input      | 48 | RD(a)   | RXD Inverting Input            |  |  |  |  |

| 18    | TMEN                           | TM Receiver Enable Input      | 49 | RT(b)   | RxC Non-Inverting Input        |  |  |  |  |

| 19    | D0                             | Mode Select Input - Bit 0     | 50 | RT(a)   | RxC Inverting Input            |  |  |  |  |

| 20    | D1                             | Mode Select Input - Bit 1     | 51 | TxC(b)  | TxC Non-Inverting Input        |  |  |  |  |

| 21    | D2                             | Mode Select Input - Bit 2     | 52 | GND     | Ground                         |  |  |  |  |

| 22    | TERM_OFF                       | Termination Disable Input     | 53 | TxC(a)  | TxC Inverting Input            |  |  |  |  |

| 23    | D_LATCH#                       | Decoder Latch Input           | 54 | CS(b)   | CTS Non-Inverting Input        |  |  |  |  |

| 24    | N/C                            | No Connect                    | 55 | CS(a)   | CTS Inverting Input            |  |  |  |  |

| 25    | GND                            | Ground                        | 56 | DM(b)   | DSR Non-Inverting Input        |  |  |  |  |

| 26    | VCC                            | 5V Power Supply Input         | 57 | DM(a)   | DSR Inverting Input            |  |  |  |  |

| 27    | LOOP-<br>BACK#                 | Loopback Mode Enable Input    | 58 | GNDV10  | V.10 Rx Ground Reference       |  |  |  |  |

| 28    | TxD                            | TxD Driver TTL Input          | 59 | RRT(b)  | DCD_DTE Non-Inverting Input    |  |  |  |  |

| 29    | TxCE                           | TxCE Driver TTL Input         | 60 | RRT(a)  | DCD_DTE Inverting Input        |  |  |  |  |

| 30    | ST                             | ST Driver TTL Input           | 61 | IC      | RI Receiver Input              |  |  |  |  |

| 31    | RTS                            | RTS Driver TTL Input          | 62 | TM(a)   | TM Receiver Input              |  |  |  |  |

| Pin D | PIN DESCRIPTIONS BY PIN NUMBER |                                  |     |          |                           |  |  |  |

|-------|--------------------------------|----------------------------------|-----|----------|---------------------------|--|--|--|

| 63    | LL(a)                          | LL Driver Output                 | 82  | GND      | Ground                    |  |  |  |

| 64    | VCC                            | 5V Power Supply Input            | 83  | RS(a)    | RTS Inverting Output      |  |  |  |

| 65    | RL(a)                          | RL Driver Output                 | 84  | VCC      | 5V Power Supply Input     |  |  |  |

| 66    | VSS1                           | -2 x V <sub>CC</sub> Charge Pump | 85  | RS(b)    | RTS Non-Inverting Output  |  |  |  |

| 67    | C2N                            | Charge Pump Capacitor            | 86  | GND      | Ground                    |  |  |  |

| 68    | GND                            | Ground                           | 87  | ST(a)    | ST Inverting Output       |  |  |  |

| 69    | C1N                            | Charge Pump Capacitor            | 88  | VCC      | 5V Power Supply Input     |  |  |  |

| 70    | C2P                            | Charge Pump Capacitor            | 89  | V35TGND3 | ST Termination Reference  |  |  |  |

| 71    | VCC                            | 5V Power Supply Input            | 90  | ST(b)    | ST Non-Inverting Output   |  |  |  |

| 72    | C1P                            | Charge Pump Capacitor            | 91  | GND      | Ground                    |  |  |  |

| 73    | VDD                            | 2 x V <sub>CC</sub> Charge Pump  | 92  | TT(a)    | TxCE Inverting Output     |  |  |  |

| 74    | GND                            | Ground                           | 93  | VCC      | 5V Power Supply Input     |  |  |  |

| 75    | TR(a)                          | DTR Inverting Output             | 94  | V35TGND2 | TT Termination Reference  |  |  |  |

| 76    | NC                             | No Connect                       | 95  | TT(b)    | TxCE Non-Inverting Output |  |  |  |

| 77    | VCC                            | 5V Power Supply Input            | 96  | GND      | Ground                    |  |  |  |

| 78    | TR(b)                          | DTR Non-Inverting Output         | 97  | SD(a)    | TxD Inverting Output      |  |  |  |

| 79    | RRC(b)                         | DCD Non-Inverting Output         | 98  | VCC      | 5V Power Supply Input     |  |  |  |

| 80    | VCC                            | 5V Power Supply Input            | 99  | V35TGND1 | SD Termination Reference  |  |  |  |

| 81    | RRC(a)                         | DCD Inverting Output             | 100 | SD(b)    | TxD Non-Inverting Output  |  |  |  |

## **SP510E**

## TABLE 5: DRIVER MODE SELECTION

| Driver Output Pin     | EIA-530A<br>Mode | EIA-530<br>Mode | X.21<br>Mode<br>(V.11) | V.35<br>Mode | RS-449<br>Mode<br>(V.36) | RS-232<br>Mode<br>(V.28) | Shut-<br>down | Suggested<br>Signal |

|-----------------------|------------------|-----------------|------------------------|--------------|--------------------------|--------------------------|---------------|---------------------|

| Mode (D2, D1, D0)     | 001              | 010             | 011                    | 100          | 101                      | 110                      | 111           |                     |

| T <sub>1</sub> OUT(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxD(a)              |

| T <sub>1</sub> OUT(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxD(b)              |

| T <sub>2</sub> OUT(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxCE(a)             |

| T <sub>2</sub> OUT(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxCE(b)             |

| T <sub>3</sub> OUT(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxC_DCE(a)          |

| T <sub>3</sub> OUT(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxC_DCE(b)          |

| T <sub>4</sub> OUT(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | RTS(a)              |

| T <sub>4</sub> OUT(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | RTS(b)              |

| T <sub>5</sub> OUT(a) | V.10             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DTR(a)              |

| T <sub>5</sub> OUT(b) | High-Z           | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DTR(b)              |

| T <sub>6</sub> OUT(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DCD_DCE(a)          |

| T <sub>6</sub> OUT(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DCD_DCE(b)          |

| T <sub>7</sub> OUT(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | RL                  |

| T <sub>8</sub> OUT(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | LL                  |

## ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

#### TABLE 6: RECEIVER MODE SELECTION

| Receiver Input Pin   | EIA-530A<br>Mode | EIA-530<br>Mode | X.21<br>Mode<br>(V.11) | V.35<br>Mode | RS-449<br>Mode<br>(V.36) | RS-232<br>Mode<br>(V.28) | Shut-<br>down | SUGGESTED<br>SIGNAL |

|----------------------|------------------|-----------------|------------------------|--------------|--------------------------|--------------------------|---------------|---------------------|

| Mode (D2, D1, D0)    | 001              | 010             | 011                    | 100          | 101                      | 110                      | 111           |                     |

| R <sub>1</sub> IN(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | RxD(a)              |

| R <sub>1</sub> IN(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | RxD(b)              |

| R <sub>2</sub> IN(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | RxCE(a)             |

| R <sub>2</sub> IN(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | RxCE(b)             |

| R <sub>3</sub> IN(a) | V.11             | V.11            | V.11                   | V.35         | V.11                     | V.28                     | High-Z        | TxC_DTE(a)          |

| R <sub>3</sub> IN(b) | V.11             | V.11            | V.11                   | V.35         | V.11                     | High-Z                   | High-Z        | TxC_DTE(b)          |

| R <sub>4</sub> IN(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | CTS(a)              |

| R <sub>4</sub> IN(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | CTS(b)              |

| R <sub>5</sub> IN(a) | V.10             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DSR(a)              |

| R <sub>5</sub> IN(b) | High-Z           | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DSR(b)              |

| R <sub>6</sub> IN(a) | V.11             | V.11            | V.11                   | V.28         | V.11                     | V.28                     | High-Z        | DCD_DTE(a)          |

| R <sub>6</sub> IN(b) | V.11             | V.11            | V.11                   | High-Z       | V.11                     | High-Z                   | High-Z        | DCD_DTE(b)          |

| R <sub>7</sub> IN(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | RI                  |

| R <sub>8</sub> IN(a) | V.10             | V.10            | High-Z                 | V.28         | V.10                     | V.28                     | High-Z        | ТМ                  |

#### TABLE 7: V.11 & V.35 DRIVERS

| INP    | UTS   | OUTPUTS |       |  |

|--------|-------|---------|-------|--|

| Tx_EN# | Tx_IN | Tx(A)   | Тх(в) |  |

| 1      | 1     | 0       | 1     |  |

| 1      | 0     | 1       | 0     |  |

TABLE 8: V.28 DRIVERS

| INP    | UTS   | Ουτρυτς |         |  |

|--------|-------|---------|---------|--|

| Tx_EN# | Tx_IN | Tx(A)   | Тх(в)   |  |

| 1      | 1     | < -5V   | > 30 kΩ |  |

| 1      | 0     | > +5V   | > 30 kΩ |  |

#### TABLE 9: V.10 DRIVERS

| INP    | UTS   | OUTPUTS |         |  |

|--------|-------|---------|---------|--|

| Tx_EN# | Tx_IN | Tx(A)   | Тх(в)   |  |

| 1      | 1     | < -4V   | > 30 kΩ |  |

| 1      | 0     | > +4V   | > 30 kΩ |  |

#### TABLE 10: V.11 & V.35 RECEIVERS

| INPUTS         | OUTPUTS |

|----------------|---------|

| Rx(а) - Rx(в)  | RO      |

| $\ge$ 200 mV   | 1       |

| $\leq$ –200 mV | 0       |

| Open / shorted | 1       |

## TABLE 11: V.28 RECEIVERS

| INPUTS        | OUTPUTS |

|---------------|---------|

| Rx(а) - Rx(в) | RO      |

| $\ge$ +3V     | 0       |

| $\leq -3V$    | 1       |

| Open / ground | 1       |

#### TABLE 12: V.10 RECEIVERS

| INPUTS        | OUTPUTS |

|---------------|---------|

| Rx(а) - Rx(в) | RO      |

| $\geq$ +0.3V  | 0       |

| $\leq -0.3V$  | 1       |

| Open / ground | 1       |

## FIGURE 2. V.28 DRIVER OUTPUT OPEN CIRCUIT VOLTAGE

FIGURE 3. V.28 DRIVER OUTPUT LOADED VOLTAGE

FIGURE 4. V.28 DRIVER OUTPUT SLEW RATE

#### FIGURE 5. V.28 DRIVER OUTPUT SHORT CIRCUIT CURRENT

#### FIGURE 6. V.28 DRIVER OUTPUT POWER-OFF IMPEDANCE

FIGURE 7. V.28 DRIVER OUTPUT RISE/FALL TIME

## FIGURE 8. V.28 RECEIVER INPUT IMPEDANCE

FIGURE 9. V.28 RECEIVER INPUT OPEN-CIRCUIT BIAS

FIGURE 10. V.10 DRIVER OUTPUT OPEN-CIRCUIT VOLTAGE

#### FIGURE 11. V.10 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 12. V.10 DRIVER OUTPUT SHORT-CIRCUIT CURRENT

## FIGURE 14. V.10 DRIVER OUTPUT TRANSITION TIME

FIGURE 15. V.10 RECEIVER INPUT CURRENT

FIGURE 16. V.10 RECEIVER INPUT IV GRAPH

#### FIGURE 17. V.11 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 18. V.11 DRIVER OUTPUT TEST TERMINATED VOLTAGE

FIGURE 19. V.11 DRIVER OUTPUT SHORT-CIRCUIT CURRENT